# MC9S12C128 Data Sheet Covers MC9S12C Family And MC9S12GC Family

# HCS12 Microcontrollers

MC9S12C128

01/2006

freescale.com

# MC9S12C128

# also covers MC9S12GC Family

# HCS12 Microcontrollers

MC9S12C128

Rev 01.19 01/2006

To provide the most up-to-date information, the revision of our documents on the World Wide Web will be the most current. Your printed copy may be an earlier revision. To verify you have the latest information available, refer to:

http://freescale.com/

A full list of family members and options is included in the appendices.

The following revision history table summarizes changes contained in this document.

This document contains information for all constituent modules, with the exception of the S12 CPU. For S12 CPU information please refer to the CPU S12 Reference Manual.

# **Revision History**

| Date       | Revision<br>Level | Description                                                                                                          |

|------------|-------------------|----------------------------------------------------------------------------------------------------------------------|

| June, 2005 | 01.14             | New Book                                                                                                             |

| July, 2005 | 01.15             | Removed 16MHz option for 128K, 96K and 64K versions<br>Minor corrections following review                            |

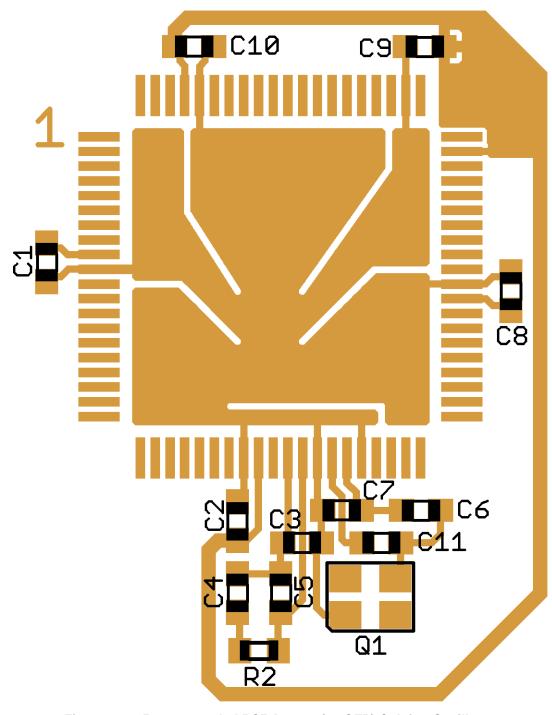

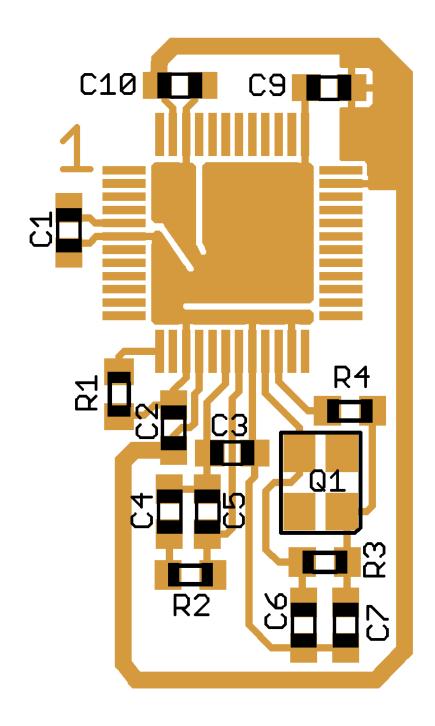

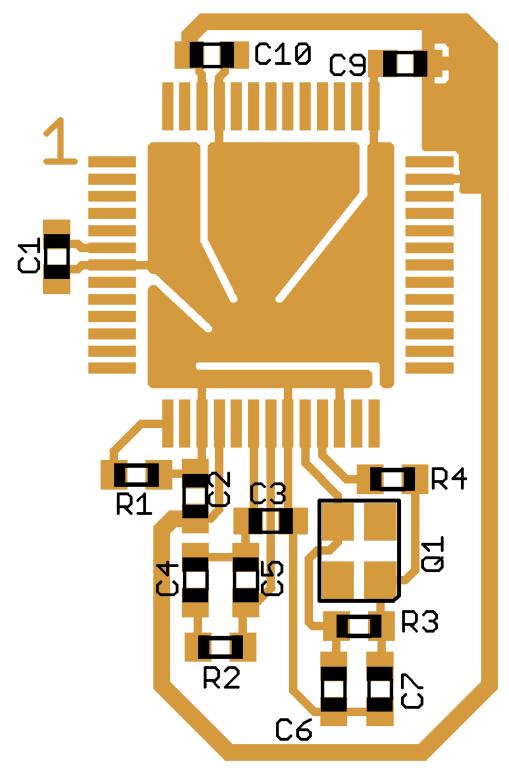

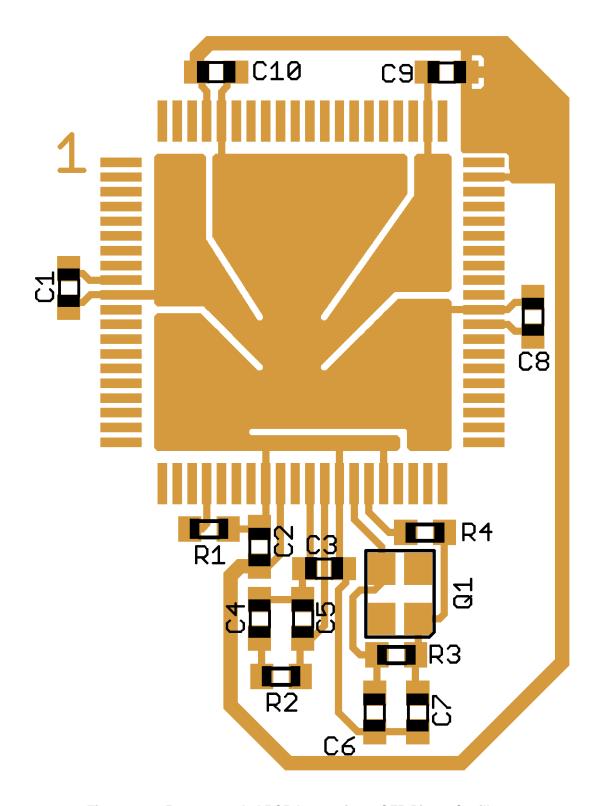

| Oct, 2005  | 01.16             | Added outstanding flash module descriptions Added EPP package options Corrected and Enhanced recommended PCB layouts |

| Dec, 2005  | 01.17             | Added note to PIM block diagram figure                                                                               |

| Dec, 2005  | 01.18             | Added PIM rerouting information to 80-pin package diagram                                                            |

| Jan, 2006  | 01.19             | Modified LVI levels in electrical parameter section Corrected TSCR2 typo in timer register listing                   |

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. This product incorporates SuperFlash® technology licensed from SST.

© Freescale Semiconductor, Inc., 2005. All rights reserved.

| Chapter 1  | MC9S12C and MC9S12GC Device Overview (MC9S12C128)      | .19        |

|------------|--------------------------------------------------------|------------|

| Chapter 2  | Port Integration Module (PIM9C32)                      | <b>77</b>  |

| Chapter 3  | Module Mapping Control (MMCV4)                         | 113        |

| Chapter 4  | Multiplexed External Bus Interface (MEBIV3)            | 133        |

| Chapter 5  | Interrupt (INTV1)                                      | 161        |

| Chapter 6  | Background Debug Module (BDMV4)                        | 169        |

| Chapter 7  | Debug Module (DBGV1)                                   | 195        |

| Chapter 8  | Analog-to-Digital Converter (ATD10B8C)                 | 229        |

| Chapter 9  | Clocks and Reset Generator (CRGV4)                     | <b>255</b> |

| Chapter 10 | Freescale's Scalable Controller Area Network (MSCANV2) | 291        |

| Chapter 11 | Oscillator (OSCV2)                                     | 345        |

| Chapter 12 | Pulse-Width Modulator (PWM8B6CV1)                      | 349        |

| Chapter 13 | Serial Communications Interface (S12SCI)               | 385        |

| Chapter 14 | Serial Peripheral Interface (SPIV3)                    | 415        |

| Chapter 15 | Timer Module (TIM16B8CV1)                              | 437        |

| Chapter 16 | Dual Output Voltage Regulator (VREG3V3V2)              | 463        |

| Chapter 17 | 16 Kbyte Flash Module (S12FTS16KV1)                    | 471        |

| Chapter 18 | 32 Kbyte Flash Module (S12FTS32KV1)                    | 503        |

| Chapter 19 | 64 Kbyte Flash Module (S12FTS64KV4)                    | 537        |

| Chapter 20 | 96 Kbyte Flash Module (S12FTS96KV1)                    | <b>571</b> |

| Chapter 21 | 128 Kbyte Flash Module (S12FTS128K1V1)                 | 605        |

| Appendix A | Electrical Characteristics                             | 639        |

| Appendix B | Emulation Information                                  | 671        |

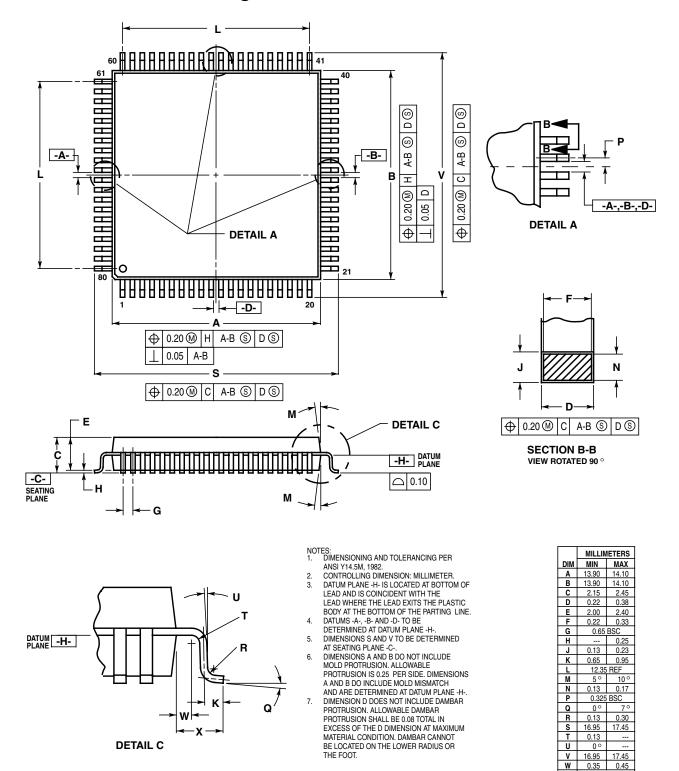

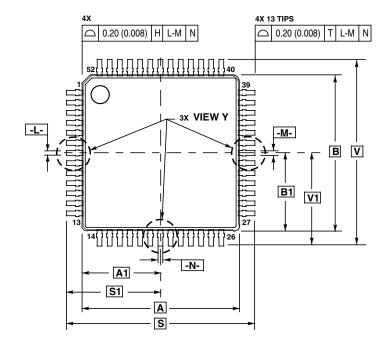

| Appendix C | Package Information                                    | 673        |

| Appendix D | Derivative Differences                                 | 677        |

| Appendix E O | Ordering Information | 678 |

|--------------|----------------------|-----|

|--------------|----------------------|-----|

# Chapter 1

|     | IV       | IC9S12C and MC9S12GC Device Overview (MC9S12C128)                        |   |

|-----|----------|--------------------------------------------------------------------------|---|

| 1.1 |          | etion1                                                                   | 9 |

|     | 1.1.1    | Features                                                                 |   |

|     | 1.1.2    | Modes of Operation                                                       | 1 |

|     | 1.1.3    | Block Diagram                                                            | 2 |

| 1.2 | Memor    | y Map and Registers                                                      | 3 |

|     | 1.2.1    | Device Memory Map                                                        |   |

|     | 1.2.2    | Detailed Register Map                                                    |   |

|     | 1.2.3    | Part ID Assignments                                                      |   |

| 1.3 | Signal I | Description                                                              |   |

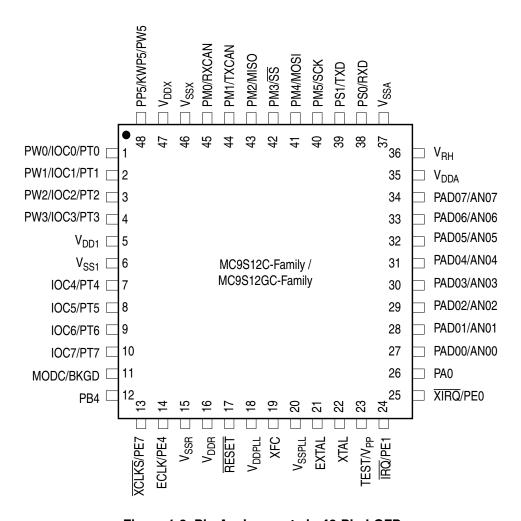

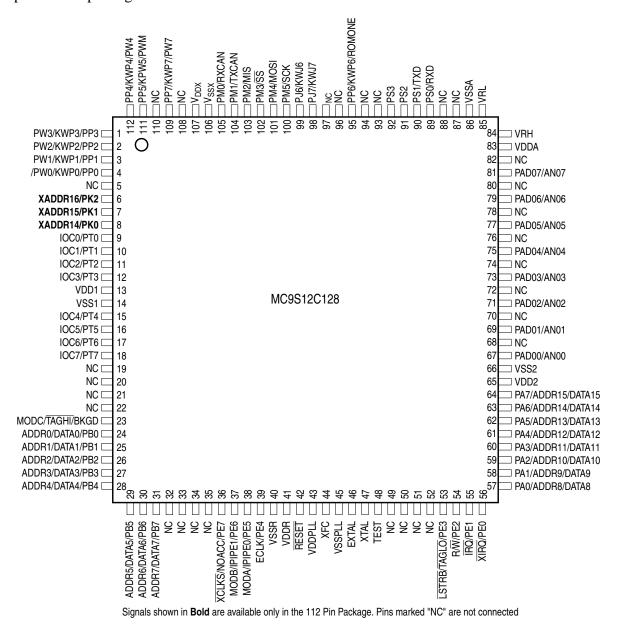

|     | 1.3.1    | Device Pinouts                                                           |   |

|     | 1.3.2    | Signal Properties Summary                                                |   |

|     | 1.3.3    | Pin Initialization for 48- and 52-Pin LQFP Bond Out Versions             |   |

|     | 1.3.4    | Detailed Signal Descriptions                                             |   |

| 1 4 | 1.3.5    | Power Supply Pins                                                        |   |

| 1.4 | •        | Clock Description                                                        |   |

| 1.5 |          | of Operation                                                             |   |

|     | 1.5.1    | Chip Configuration Summary                                               |   |

|     | 1.5.2    | Security                                                                 |   |

| 1.6 | 1.5.3    | Low-Power Modes                                                          |   |

| 1.0 | 1.6.1    | and Interrupts                                                           |   |

|     | 1.6.1    | Resets                                                                   |   |

| 1.7 |          | Specific Information and Module Dependencies                             |   |

| 1./ | 1.7.1    | PPAGE                                                                    |   |

|     | 1.7.1    | BDM Alternate Clock                                                      |   |

|     | 1.7.2    | Extended Address Range Emulation Implications                            |   |

|     | 1.7.4    | VREGEN                                                                   |   |

|     | 1.7.5    | $V_{\mathrm{DD1}}, V_{\mathrm{DD2}}, V_{\mathrm{SS1}}, V_{\mathrm{SS2}}$ |   |

|     | 1.7.6    | Clock Reset Generator And VREG Interface 6                               | 7 |

|     | 1.7.7    | Analog-to-Digital Converter                                              |   |

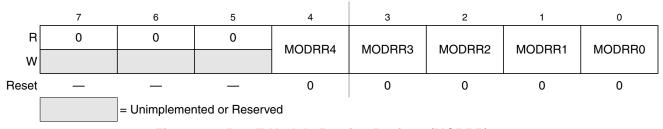

|     | 1.7.8    | MODRR Register Port T And Port P Mapping                                 |   |

|     | 1.7.9    | Port AD Dependency On PIM And ATD Registers                              |   |

| 1.8 |          | mended Printed Circuit Board Layout                                      |   |

|     |          | Chapter 2                                                                |   |

|     |          | Port Integration Module (PIM9C32) Block Description                      |   |

| 2.1 |          | ction7                                                                   |   |

|     | 2.1.1    | Features                                                                 |   |

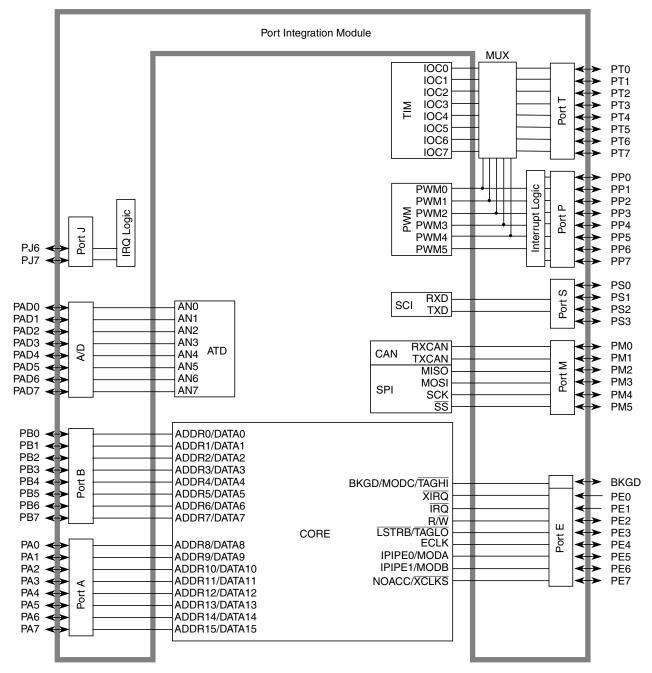

| 2.6 | 2.1.2    | Block Diagram                                                            |   |

| 2.2 | _        | Description                                                              |   |

| 2.3 |          | y Map and Registers                                                      |   |

|     | 2.3.1    | Module Memory Map 8                                                      | 0 |

|     | 2.3.2 Register Descriptions                       | 83    |

|-----|---------------------------------------------------|-------|

| 2.4 | Functional Description                            | . 107 |

|     | 2.4.1 Registers                                   | . 107 |

|     | 2.4.2 Port Descriptions                           | . 108 |

|     | 2.4.3 Port A, B, E and BKGD Pin                   | . 110 |

|     | 2.4.4 External Pin Descriptions                   | . 110 |

|     | 2.4.5 Low Power Options                           |       |

| 2.5 | Initialization Information                        | . 110 |

|     | 2.5.1 Reset Initialization                        | . 110 |

| 2.6 | Interrupts                                        |       |

|     | 2.6.1 Interrupt Sources                           |       |

|     | 2.6.2 Recovery from STOP                          |       |

| 2.7 | Application Information                           |       |

|     |                                                   |       |

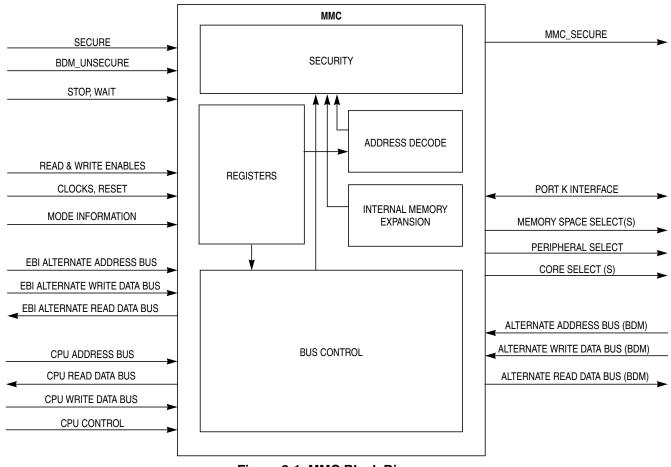

|     | Chapter 3                                         |       |

|     | Module Mapping Control (MMCV4) Block Description  |       |

| 3.1 | Introduction                                      | . 113 |

|     | 3.1.1 Features                                    | . 114 |

|     | 3.1.2 Modes of Operation                          |       |

| 3.2 | External Signal Description                       |       |

| 3.3 | Memory Map and Register Definition                |       |

|     | 3.3.1 Module Memory Map                           |       |

|     | 3.3.2 Register Descriptions                       |       |

| 3.4 | Functional Description                            |       |

|     | 3.4.1 Bus Control                                 |       |

|     | 3.4.2 Address Decoding                            | . 126 |

|     | 3.4.3 Memory Expansion                            | . 128 |

|     |                                                   |       |

|     | Chapter 4                                         |       |

|     | Multiplexed External Bus Interface (MEBIV3)       |       |

| 4.1 | Introduction                                      | . 133 |

|     | 4.1.1 Features                                    |       |

|     | 4.1.2 Modes of Operation                          |       |

| 4.2 | External Signal Description                       | . 135 |

| 4.3 | Memory Map and Register Definition                | . 137 |

|     | 4.3.1 Module Memory Map                           |       |

|     | 4.3.2 Register Descriptions                       | . 138 |

| 4.4 | Functional Description                            |       |

|     | 4.4.1 Detecting Access Type from External Signals |       |

|     | 4.4.2 Stretched Bus Cycles                        |       |

|     | 4.4.3 Modes of Operation                          |       |

|     | 4.4.4 Internal Visibility                         |       |

|     | 4.4.5 Low-Power Options                           | . 160 |

|     |                                                   |       |

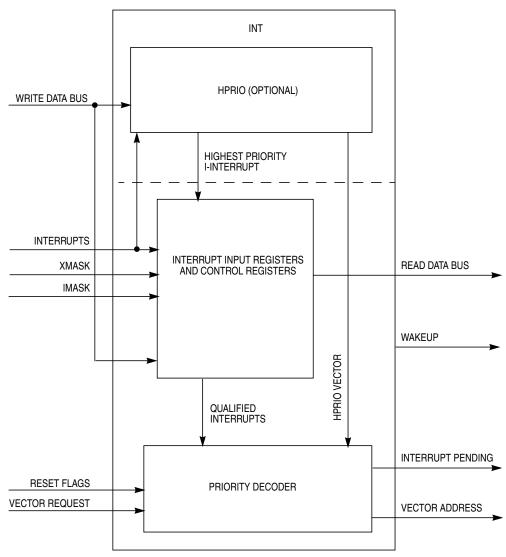

# Chapter 5 Interrupt (INTV1) Block Description

| 5.1        | Introduction                                       | 161  |

|------------|----------------------------------------------------|------|

|            | 5.1.1 Features                                     | 162  |

|            | 5.1.2 Modes of Operation                           | 162  |

| 5.2        | External Signal Description                        | 163  |

| 5.3        | Memory Map and Register Definition                 | 163  |

|            | 5.3.1 Module Memory Map                            | 163  |

|            | 5.3.2 Register Descriptions                        | 163  |

| 5.4        | Functional Description                             | 165  |

|            | 5.4.1 Low-Power Modes                              | 166  |

| 5.5        | Resets                                             | 166  |

| 5.6        | Interrupts                                         |      |

|            | 5.6.1 Interrupt Registers                          |      |

|            | 5.6.2 Highest Priority I-Bit Maskable Interrupt    | 166  |

|            | 5.6.3 Interrupt Priority Decoder                   |      |

| 5.7        | Exception Priority                                 | 167  |

|            | Chapter 6                                          |      |

|            | Chapter 6                                          |      |

|            | Background Debug Module (BDMV4) Block Description  | 4.60 |

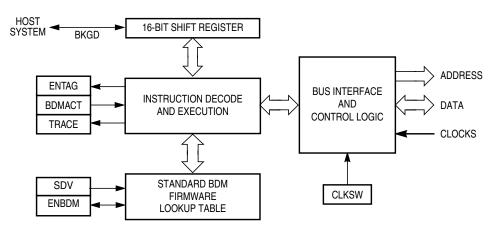

| 6.1        | Introduction                                       |      |

|            | 6.1.1 Features                                     |      |

| <i>(</i> ) | 6.1.2 Modes of Operation                           |      |

| 6.2        | External Signal Description                        |      |

|            | 6.2.1 BKGD — Background Interface Pin              |      |

|            | 6.2.2 TAGHI — High Byte Instruction Tagging Pin    |      |

| ( )        | 6.2.3 TAGLO — Low Byte Instruction Tagging Pin     |      |

| 6.3        | Memory Map and Register Definition                 |      |

|            | 6.3.1 Module Memory Map                            |      |

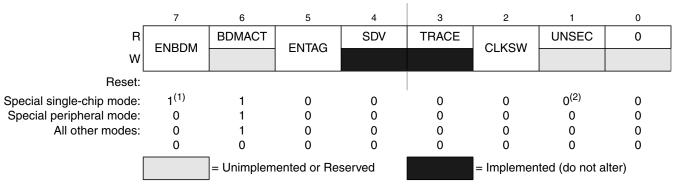

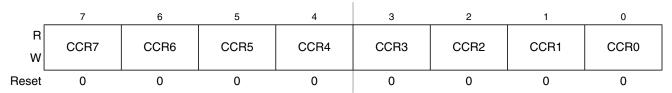

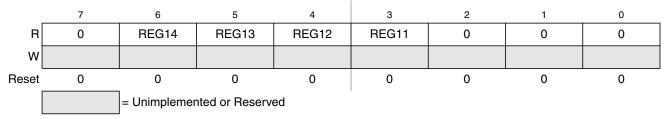

| 6.4        | 6.3.2 Register Descriptions                        |      |

| 0.4        | Functional Description                             |      |

|            | 6.4.2 Enabling and Activating BDM                  |      |

|            |                                                    |      |

|            | 6.4.3 BDM Hardware Commands                        |      |

|            | 6.4.5 BDM Command Structure                        |      |

|            | 6.4.6 BDM Serial Interface                         |      |

|            | 6.4.7 Serial Interface Hardware Handshake Protocol |      |

|            | 6.4.8 Hardware Handshake Abort Procedure           |      |

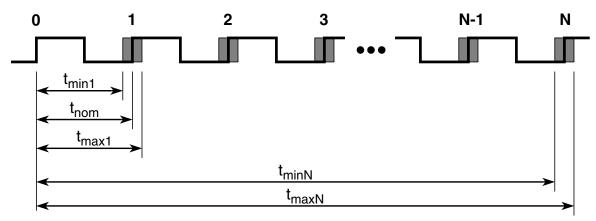

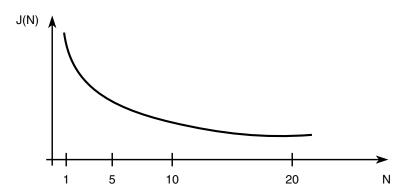

|            | 6.4.9 SYNC — Request Timed Reference Pulse         |      |

|            | 6.4.10 Instruction Tracing                         |      |

|            | 6.4.11 Instruction Tagging                         |      |

|            | 6.4.12 Serial Communication Time-Out               |      |

|            | 6.4.13 Operation in Wait Mode                      |      |

|            | orate operation in materiose                       | 1)   |

|     | 6.4.14 Operation in Stop Mode                                      | 193 |

|-----|--------------------------------------------------------------------|-----|

|     | Chapter 7 Debug Module (DBGV1) Block Description                   |     |

| 7.1 | Introduction                                                       | 195 |

|     | 7.1.1 Features                                                     |     |

|     | 7.1.2 Modes of Operation                                           |     |

|     | 7.1.3 Block Diagram                                                | 197 |

| 7.2 | External Signal Description                                        | 199 |

| 7.3 | Memory Map and Register Definition                                 |     |

|     | 7.3.1 Module Memory Map                                            |     |

|     | 7.3.2 Register Descriptions                                        |     |

| 7.4 | Functional Description                                             |     |

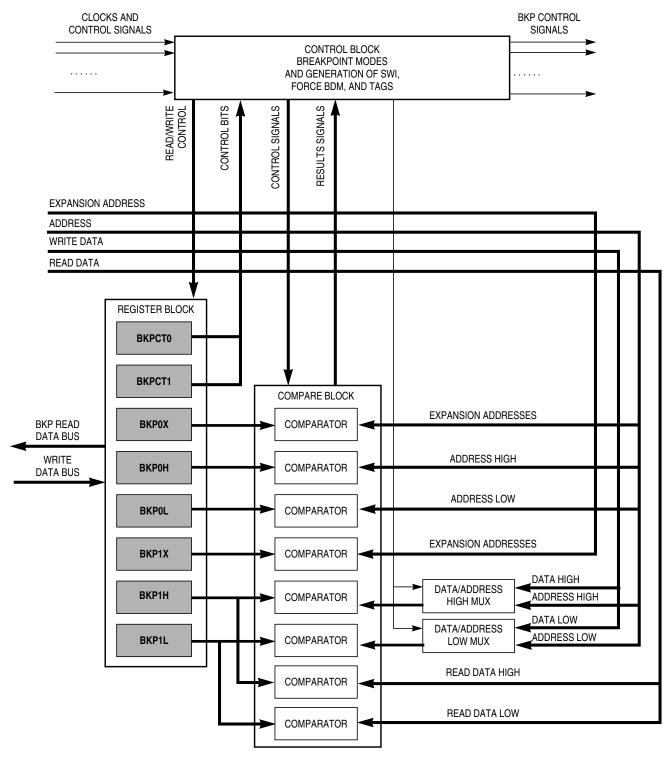

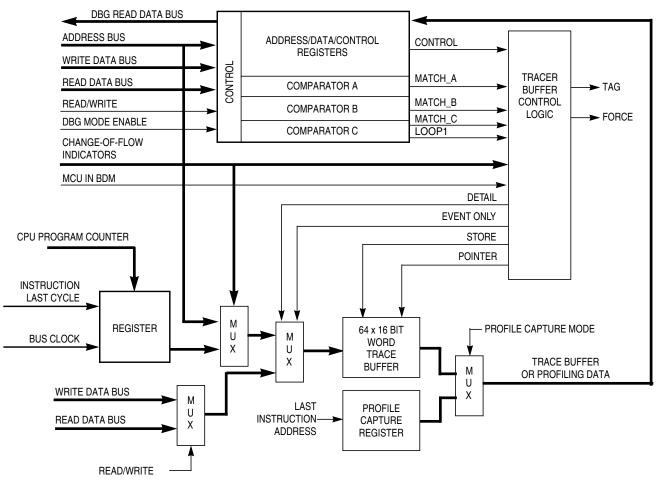

|     | 7.4.1 DBG Operating in BKP Mode                                    |     |

|     | 7.4.2 DBG Operating in DBG Mode                                    |     |

| 7.5 | 7.4.3 Breakpoints                                                  |     |

| 7.5 | Resets                                                             |     |

| 7.6 | Interrupts                                                         | 220 |

|     | Chapter 8 Analog-to-Digital Converter (ATD10B8C) Block Description |     |

| 8.1 | Introduction                                                       |     |

|     | 8.1.1 Features                                                     |     |

|     | 8.1.2 Modes of Operation                                           |     |

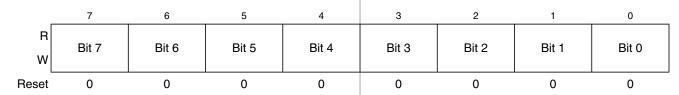

| 0.2 | 8.1.3 Block Diagram                                                |     |

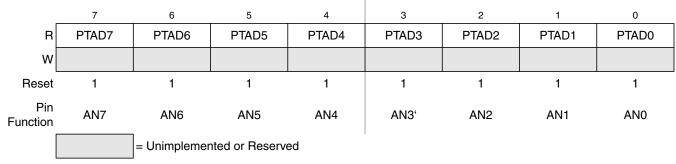

| 8.2 | Signal Description                                                 |     |

|     | 8.2.1 AN7 / ETRIG / PAD7                                           |     |

|     | 8.2.2 AN6 / PAD6                                                   |     |

|     | 8.2.4 AN4 / PAD4                                                   |     |

|     | 8.2.5 AN3 / PAD3                                                   |     |

|     | 8.2.6 AN2 / PAD2                                                   |     |

|     | 8.2.7 AN1 / PAD1                                                   |     |

|     | 8.2.8 ANO / PADO                                                   |     |

|     | 8.2.9 V <sub>RH</sub> , V <sub>RL</sub>                            |     |

|     | 8.2.10 V <sub>DDA</sub> , V <sub>SSA</sub>                         | 221 |

| 8.3 | Memory Map and Registers                                           | 231 |

|     | 8.3.1 Module Memory Map                                            |     |

|     | 8.3.2 Register Descriptions                                        |     |

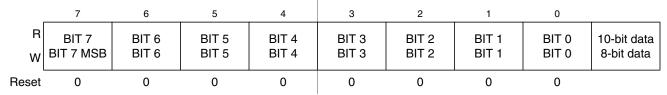

| 8.4 | Functional Description                                             |     |

|     | 8.4.1 Analog Sub-block                                             |     |

|     | 8.4.2 Digital Sub-block                                            |     |

| 8.5 | Resets                                                             | 253 |

| 8.0  | interrupis                                                                        | 233      |

|------|-----------------------------------------------------------------------------------|----------|

|      | Chapter 9                                                                         |          |

|      | Clocks and Reset Generator (CRGV4) Block Description                              |          |

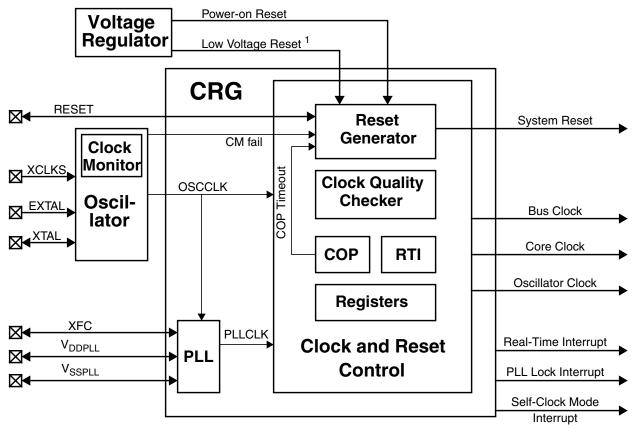

| 9.1  | Introduction                                                                      | 255      |

|      | 9.1.1 Features                                                                    | 255      |

|      | 9.1.2 Modes of Operation                                                          | 256      |

|      | 9.1.3 Block Diagram                                                               | 256      |

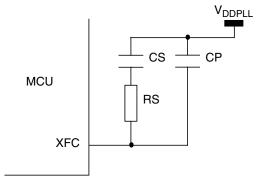

| 9.2  | External Signal Description                                                       | 257      |

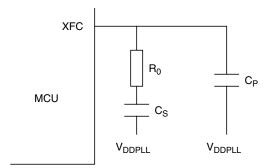

|      | 9.2.1 V <sub>DDPLL</sub> , V <sub>SSPLL</sub> — PLL Operating Voltage, PLL Ground | 257      |

|      | 9.2.2 XFC — PLL Loop Filter Pin                                                   |          |

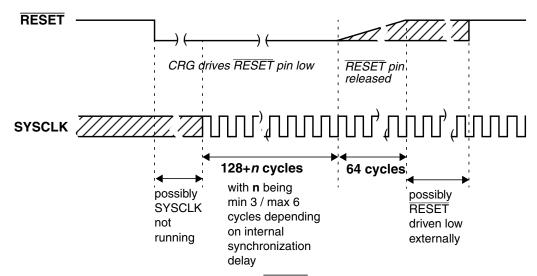

|      | 9.2.3 <u>RESET</u> — Reset Pin                                                    | 258      |

| 9.3  | Memory Map and Register Definition                                                |          |

|      | 9.3.1 Module Memory Map                                                           |          |

|      | 9.3.2 Register Descriptions                                                       |          |

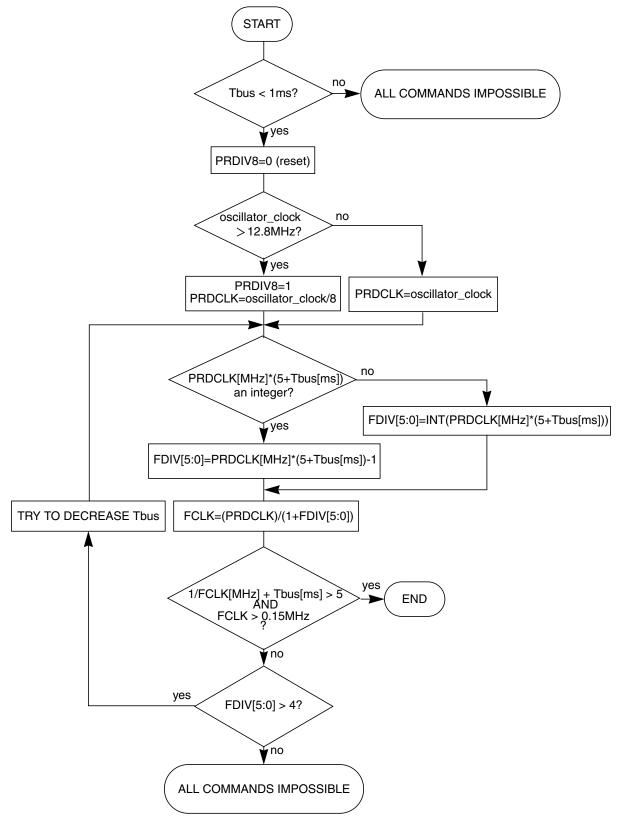

| 9.4  | Functional Description                                                            |          |

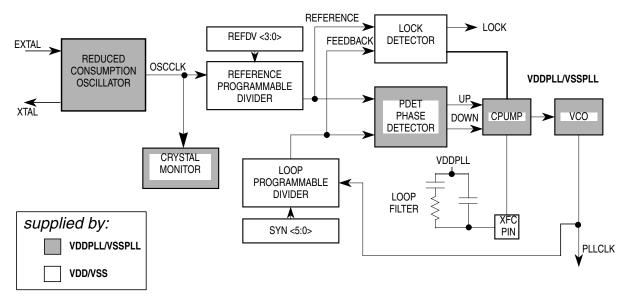

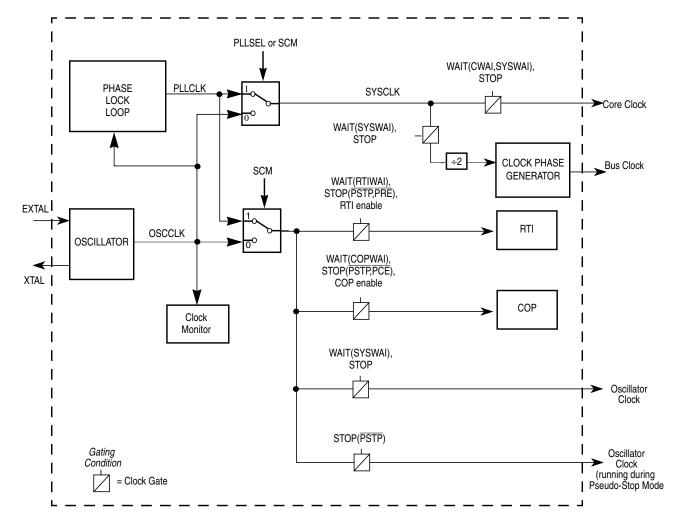

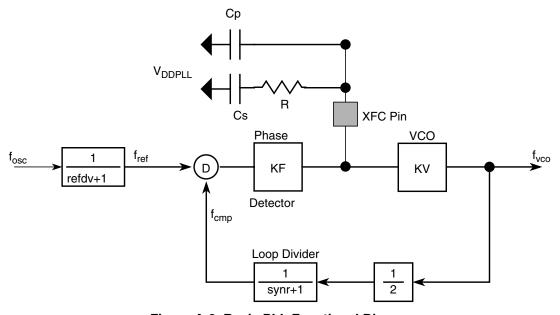

|      | 9.4.1 Phase Locked Loop (PLL)                                                     |          |

|      | 9.4.2 System Clocks Generator                                                     |          |

|      | 9.4.3 Clock Monitor (CM)                                                          |          |

|      | 9.4.4 Clock Quality Checker                                                       |          |

|      | 9.4.5 Computer Operating Properly Watchdog (COP)                                  |          |

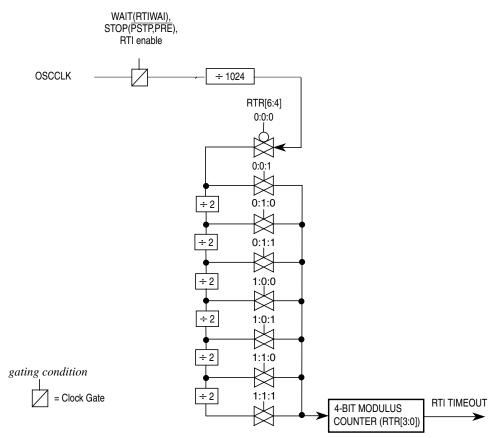

|      | 9.4.6 Real-Time Interrupt (RTI)                                                   |          |

|      | 9.4.7 Modes of Operation                                                          |          |

|      | 9.4.8 Low-Power Operation in Run Mode                                             |          |

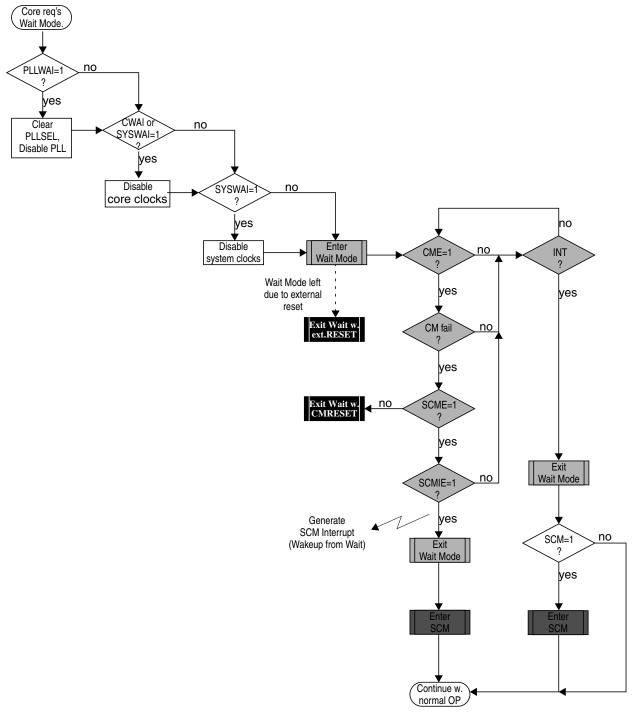

|      | 9.4.9 Low-Power Operation in Wait Mode                                            |          |

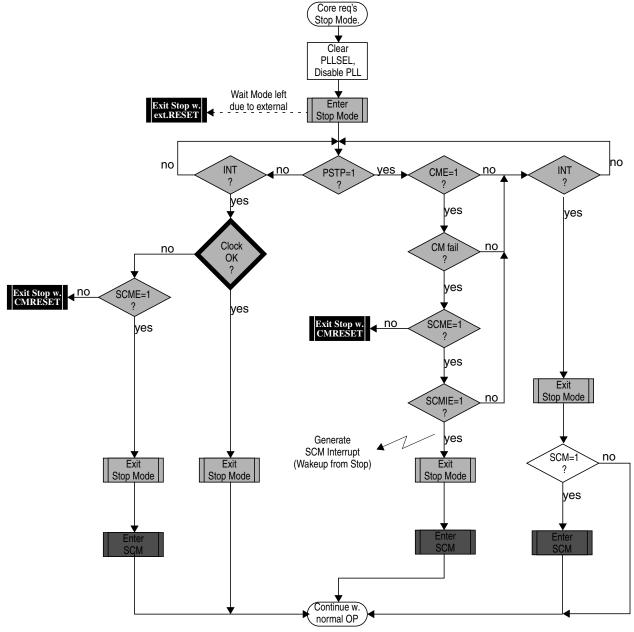

| 0.5  | 9.4.10 Low-Power Operation in Stop Mode                                           |          |

| 9.5  | Resets                                                                            |          |

|      | 9.5.1 Clock Monitor Reset                                                         |          |

|      | <ul><li>9.5.2 Computer Operating Properly Watchdog (COP) Reset</li></ul>          |          |

| 9.6  | Interrupts                                                                        |          |

| 9.0  | 9.6.1 Real-Time Interrupt                                                         |          |

|      | 9.6.2 PLL Lock Interrupt                                                          |          |

|      | 9.6.3 Self-Clock Mode Interrupt                                                   |          |

|      | 3.0.5 Sen-Clock Wode Interrupt                                                    |          |

|      | Chapter 10                                                                        |          |

| Fro  | escale's Scalable Controller Area Network (MSCANV2) Block Des                     | crintion |

|      |                                                                                   | =        |

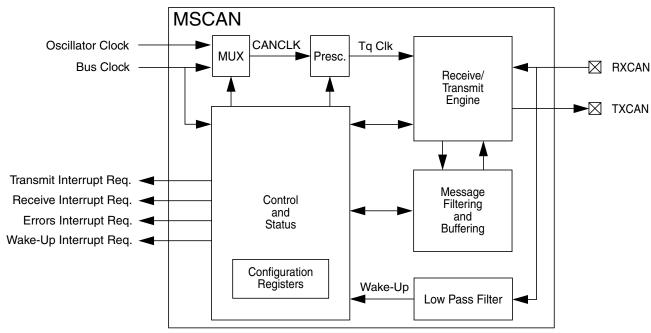

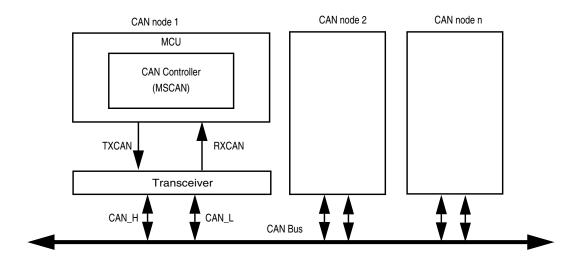

| 10.1 | Introduction                                                                      |          |

|      | 10.1.1 Block Diagram                                                              |          |

|      |                                                                                   |          |

| 10.2 | 10.1.3 Modes of Operation                                                         |          |

| 10.2 | 10.2.1 RXCAN — CAN Receiver Input Pin                                             |          |

|      | 10.2.1 RACAN — CAN Receiver input Pin  10.2.2 TXCAN — CAN Transmitter Output Pin  |          |

|      | 10.2.2 TACAIN — CAN Transmitter Output Fill                                       |          |

|      | 10.2.3 CAN System                                                                    | . 293 |

|------|--------------------------------------------------------------------------------------|-------|

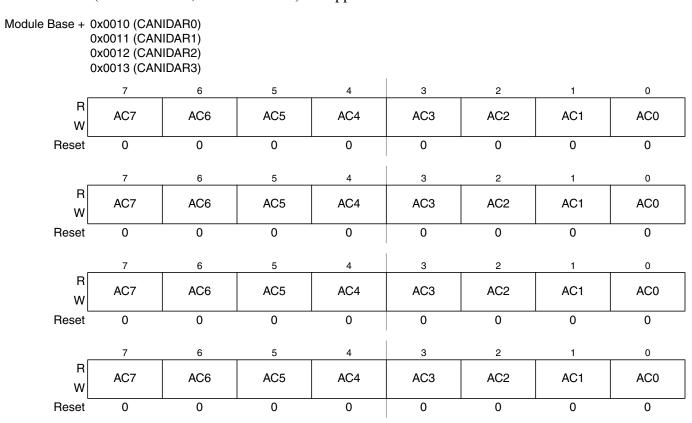

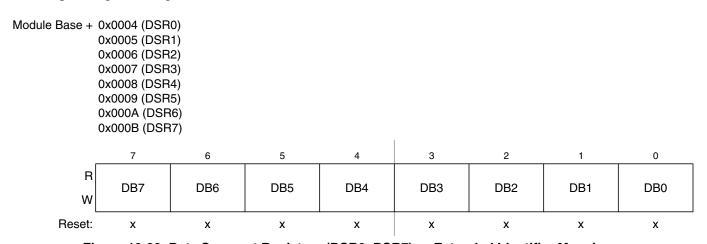

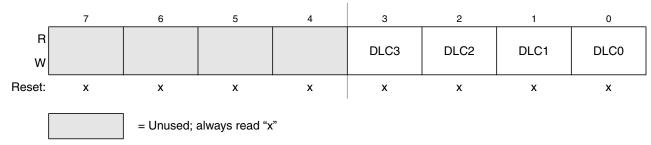

| 10.3 | Memory Map and Register Definition                                                   | . 294 |

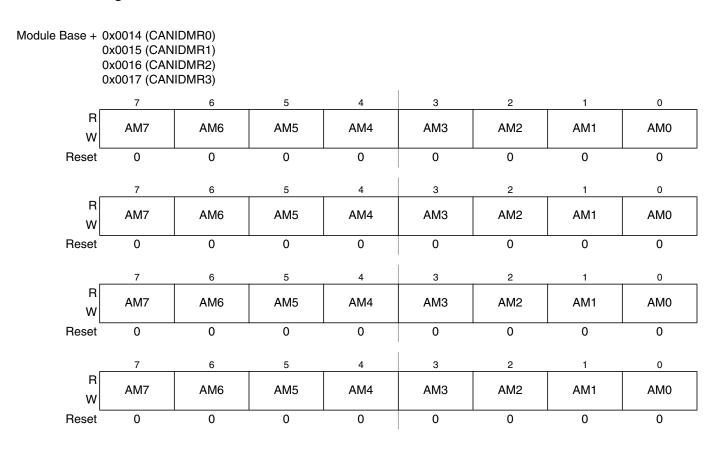

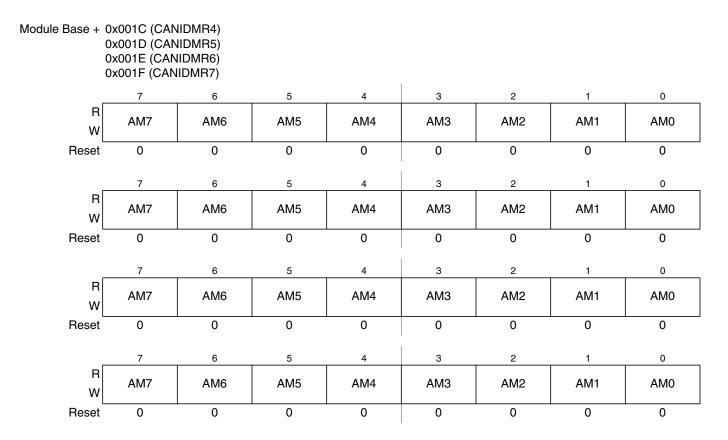

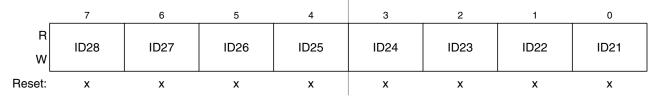

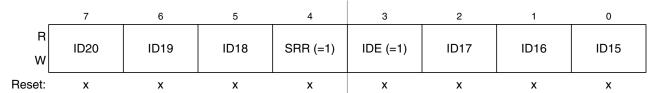

|      | 10.3.1 Module Memory Map                                                             | . 294 |

|      | 10.3.2 Register Descriptions                                                         | . 296 |

|      | 10.3.3 Programmer's Model of Message Storage                                         | . 317 |

| 10.4 | Functional Description                                                               | . 326 |

|      | 10.4.1 General                                                                       | . 326 |

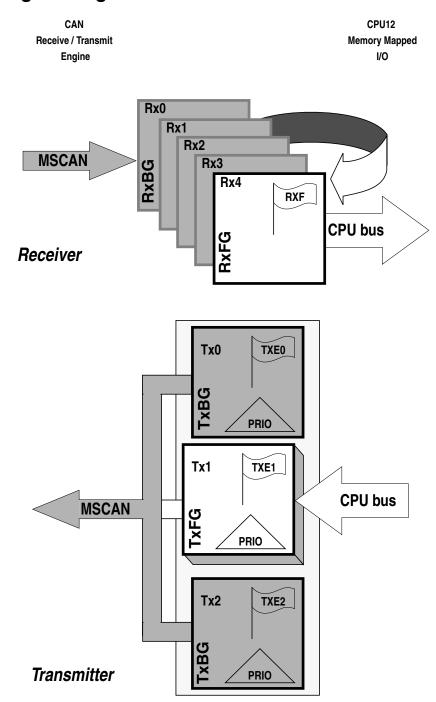

|      | 10.4.2 Message Storage                                                               | . 327 |

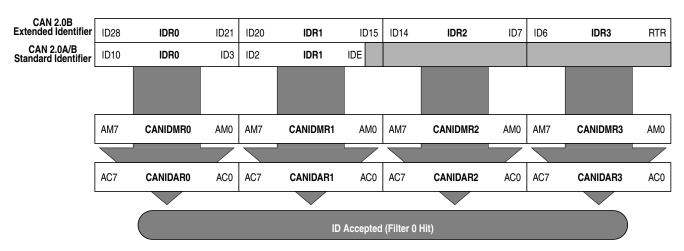

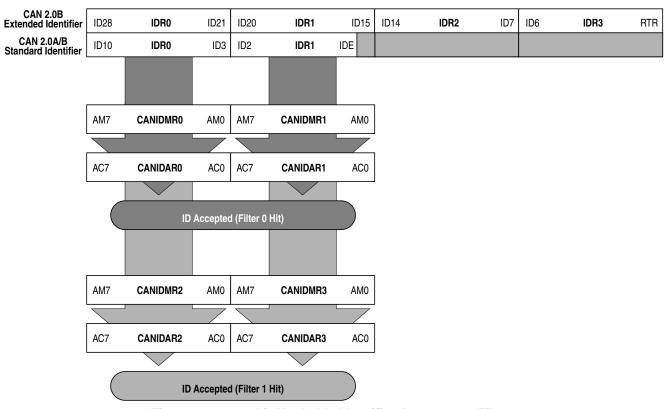

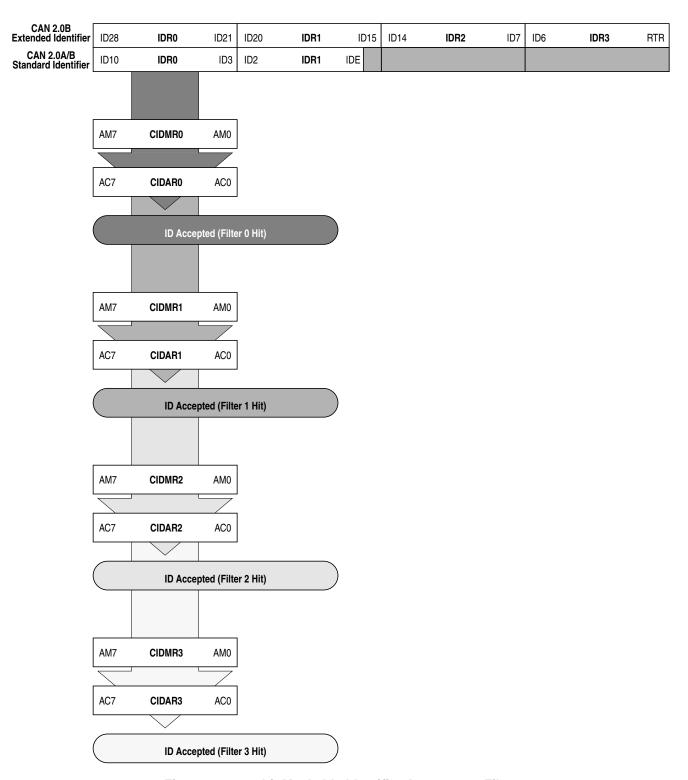

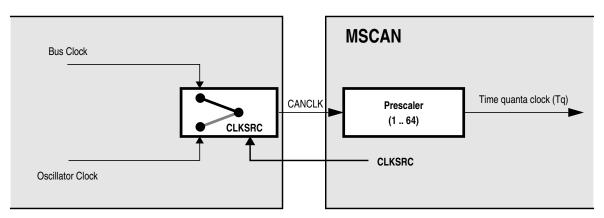

|      | 10.4.3 Identifier Acceptance Filter                                                  | . 330 |

|      | 10.4.4 Timer Link                                                                    | . 336 |

|      | 10.4.5 Modes of Operation                                                            | . 337 |

|      | 10.4.6 Low-Power Options                                                             | . 337 |

|      | 10.4.7 Reset Initialization                                                          | . 342 |

|      | 10.4.8 Interrupts                                                                    | . 342 |

| 10.5 | Initialization/Application Information                                               | . 344 |

|      | 10.5.1 MSCAN initialization                                                          | . 344 |

|      |                                                                                      |       |

|      | Chapter 11                                                                           |       |

|      | Oscillator (OSCV2) Block Description                                                 |       |

| 11.1 | Introduction                                                                         | . 345 |

|      | 11.1.1 Features                                                                      | . 345 |

|      | 11.1.2 Modes of Operation                                                            | . 345 |

| 11.2 | External Signal Description                                                          | . 346 |

|      | 11.2.1 V <sub>DDPLL</sub> and V <sub>SSPLL</sub> — PLL Operating Voltage, PLL Ground | . 346 |

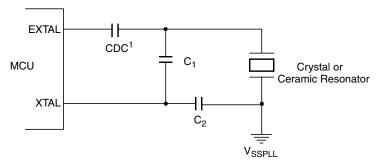

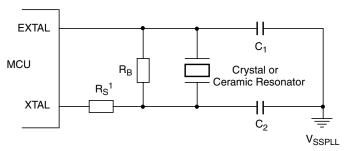

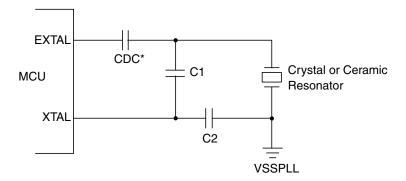

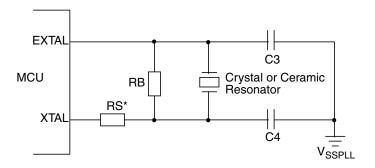

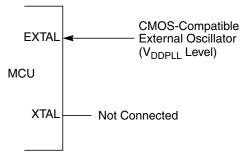

|      | 11.2.2 EXTAL and XTAL — Clock/Crystal Source Pins                                    | . 346 |

|      | 11.2.3 XCLKS — Colpitts/Pierce Oscillator Selection Signal                           | . 347 |

| 11.3 | Memory Map and Register Definition                                                   | . 348 |

| 11.4 | Functional Description                                                               | . 348 |

|      | 11.4.1 Amplitude Limitation Control (ALC)                                            | . 348 |

|      | 11.4.2 Clock Monitor (CM)                                                            | . 348 |

| 11.5 | Interrupts                                                                           | . 348 |

|      |                                                                                      |       |

|      | Chapter 12                                                                           |       |

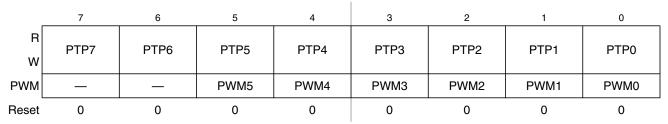

|      | Pulse-Width Modulator (PWM8B6CV1) Block Description                                  |       |

| 12.1 | Introduction                                                                         | . 349 |

|      | 12.1.1 Features                                                                      | . 349 |

|      | 12.1.2 Modes of Operation                                                            | . 349 |

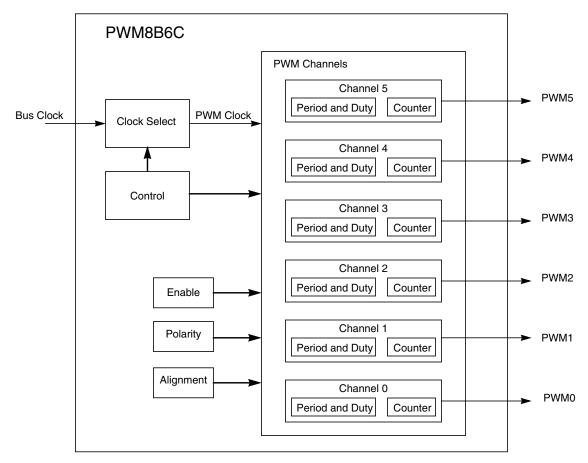

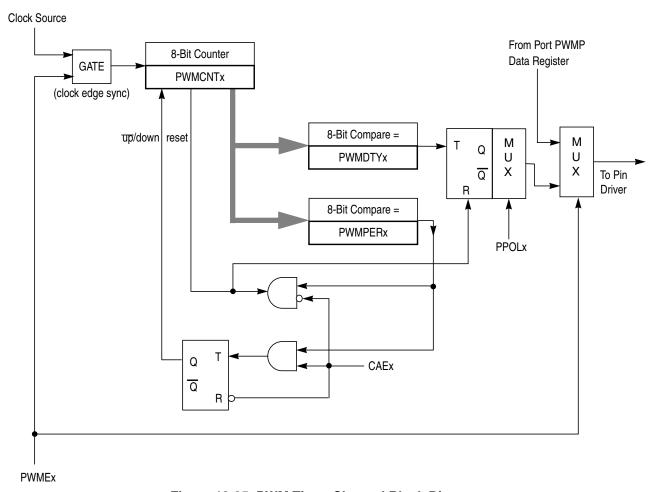

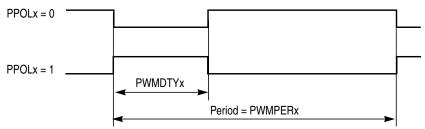

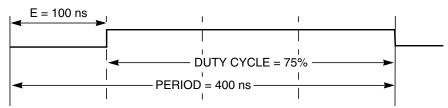

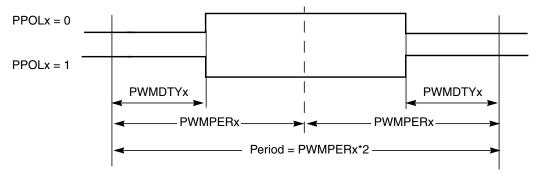

|      | 12.1.3 Block Diagram                                                                 |       |

| 12.2 | External Signal Description                                                          |       |

|      | 12.2.1 PWM5 — Pulse Width Modulator Channel 5 Pin                                    |       |

|      | 12.2.2 PWM4 — Pulse Width Modulator Channel 4 Pin                                    |       |

|      | 12.2.3 PWM3 — Pulse Width Modulator Channel 3 Pin                                    | . 350 |

|      | 12.2.4 PWM2 — Pulse Width Modulator Channel 2 Pin                                    |       |

|      | 12.2.5 PWM1 — Pulse Width Modulator Channel 1 Pin                                    | . 351 |

|      |                                                                                      |       |

|      | 12.2.6 PWM0 — Pulse Width Modulator Channel 0 Pin     |     |

|------|-------------------------------------------------------|-----|

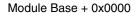

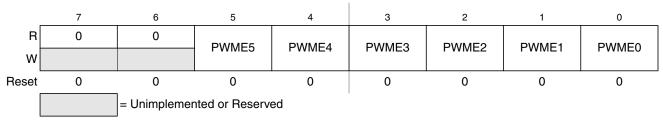

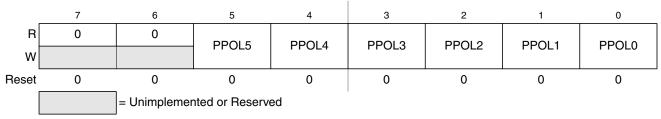

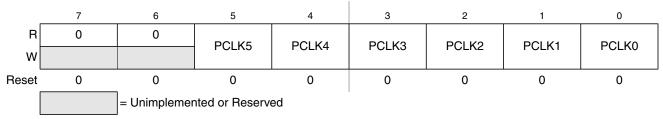

| 12.3 | Memory Map and Register Definition                    | 351 |

|      | 12.3.1 Module Memory Map                              | 351 |

|      | 12.3.2 Register Descriptions                          | 353 |

| 12.4 | Functional Description                                | 373 |

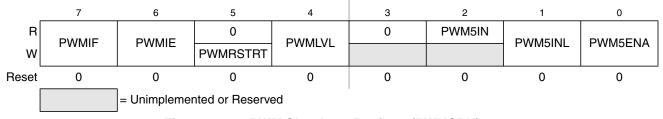

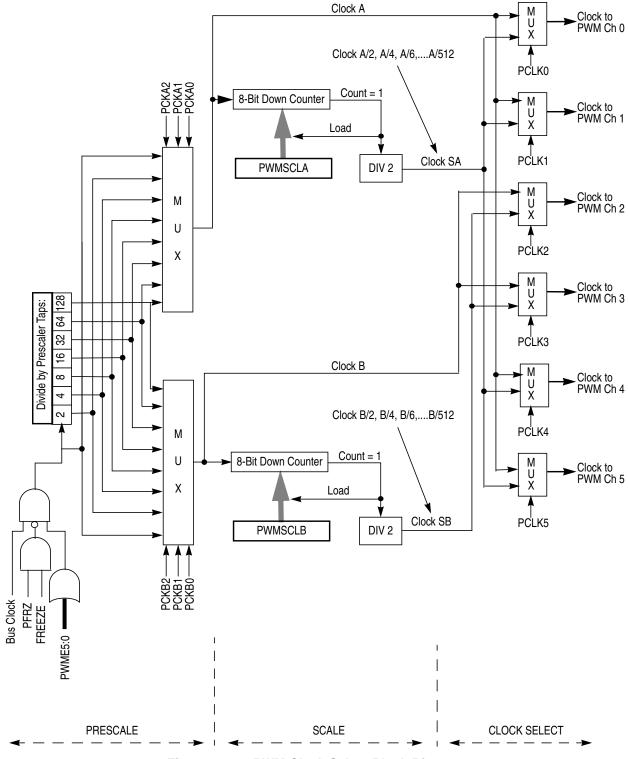

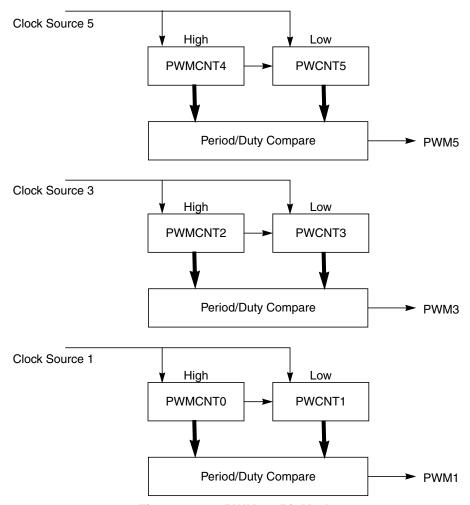

|      | 12.4.1 PWM Clock Select                               | 373 |

|      | 12.4.2 PWM Channel Timers                             | 376 |

| 12.5 | Resets                                                | 383 |

| 12.6 | Interrupts                                            | 383 |

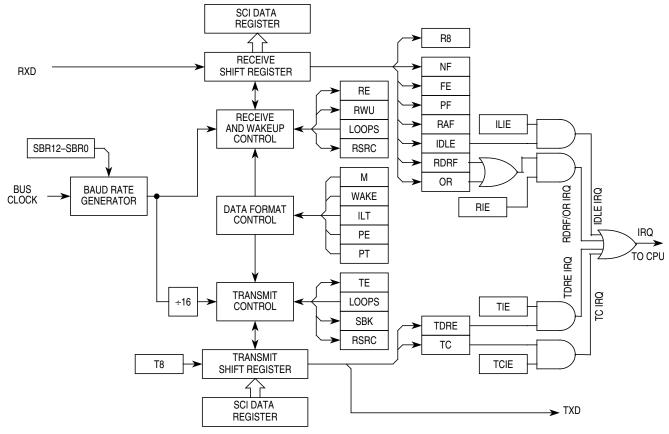

|      | Chapter 13                                            |     |

|      | Serial Communications Interface (S12SCI)              |     |

|      | Block Description                                     |     |

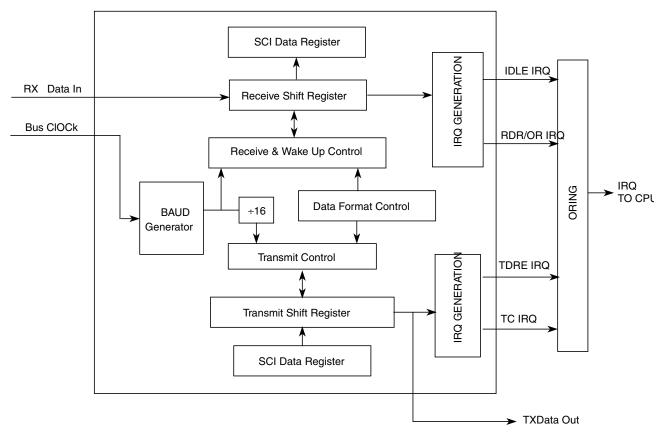

| 13.1 | Introduction                                          | 385 |

|      | 13.1.1 Glossary                                       |     |

|      | 13.1.2 Features                                       |     |

|      | 13.1.3 Modes of Operation                             | 386 |

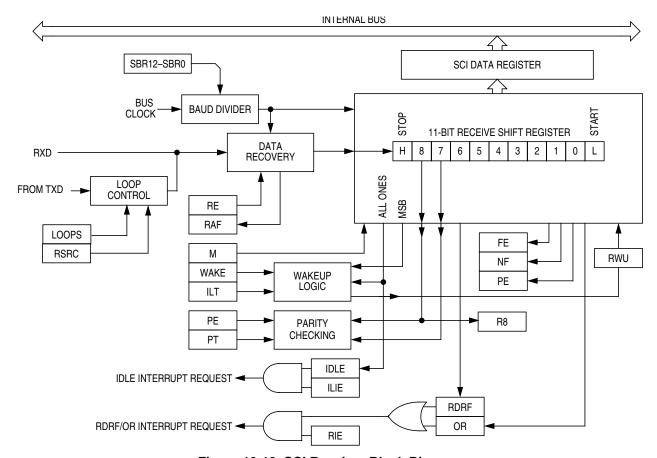

|      | 13.1.4 Block Diagram                                  |     |

| 13.2 | External Signal Description                           |     |

|      | 13.2.1 TXD-SCI Transmit Pin                           |     |

|      | 13.2.2 RXD-SCI Receive Pin                            | 387 |

| 13.3 | Memory Map and Registers                              | 388 |

|      | 13.3.1 Module Memory Map                              | 388 |

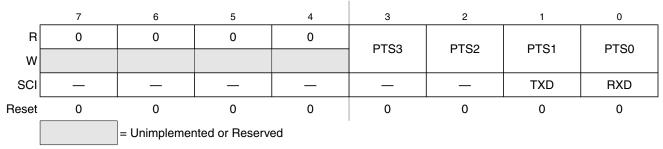

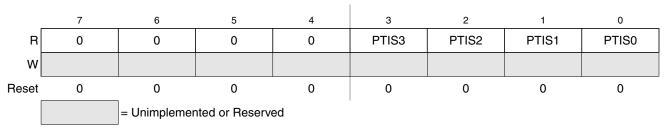

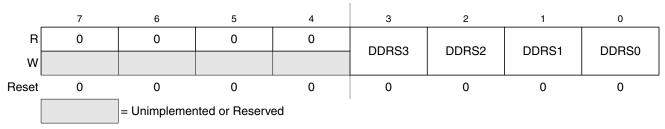

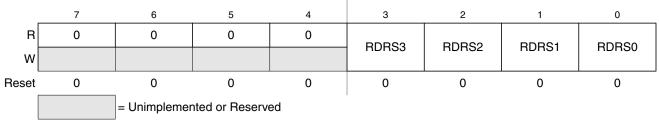

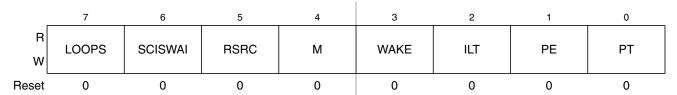

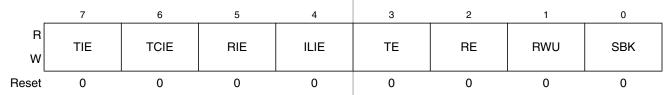

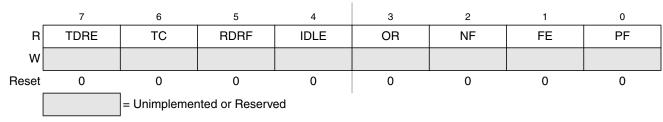

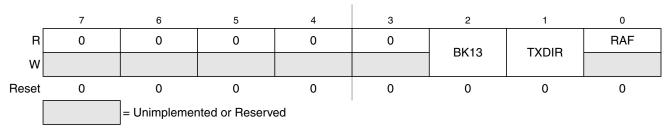

|      | 13.3.2 Register Descriptions                          | 388 |

| 13.4 | Functional Description                                | 396 |

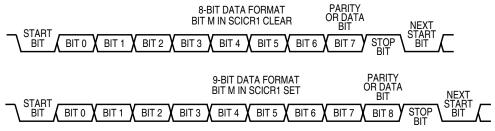

|      | 13.4.1 Data Format                                    | 397 |

|      | 13.4.2 Baud Rate Generation                           | 398 |

|      | 13.4.3 Transmitter                                    | 399 |

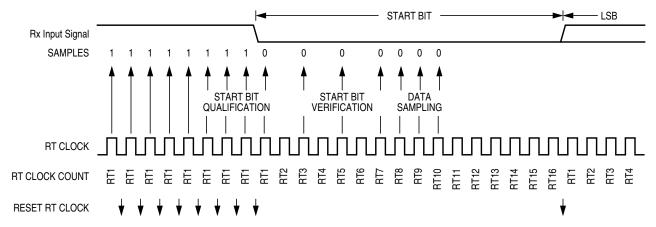

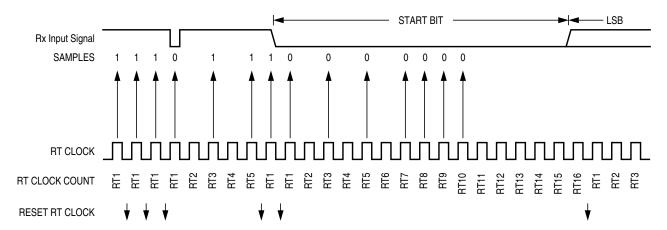

|      | 13.4.4 Receiver                                       | 402 |

|      | 13.4.5 Single-Wire Operation                          | 411 |

|      | 13.4.6 Loop Operation                                 | 411 |

| 13.5 | Initialization Information                            | 411 |

|      | 13.5.1 Reset Initialization                           | 411 |

|      | 13.5.2 Interrupt Operation                            | 412 |

|      | 13.5.3 Recovery from Wait Mode                        | 413 |

|      | Chapter 14                                            |     |

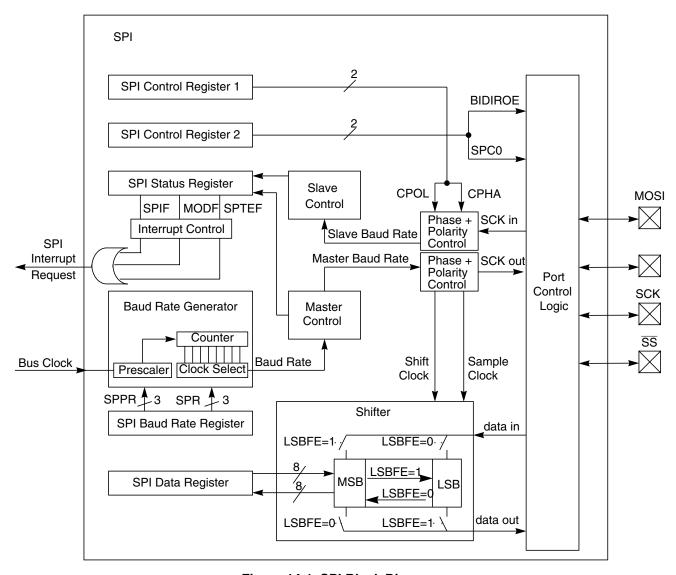

|      | Serial Peripheral Interface (SPIV3) Block Description |     |

| 14.1 | Introduction                                          | 415 |

|      | 14.1.1 Features                                       |     |

|      | 14.1.2 Modes of Operation                             | 415 |

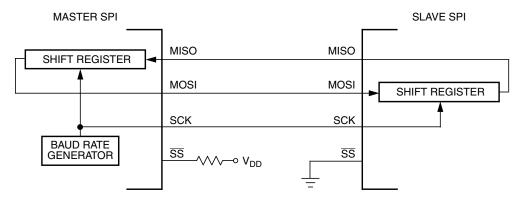

|      | 14.1.3 Block Diagram                                  | 416 |

| 14.2 | External Signal Description                           |     |

|      | 14.2.1 MOSI — Master Out/Slave In Pin                 | 416 |

|      | 14.2.2 MISO — Master In/Slave Out Pin                        |            |

|------|--------------------------------------------------------------|------------|

|      | 14.2.3 <del>SS</del> — Slave Select Pin                      |            |

|      | 14.2.4 SCK — Serial Clock Pin                                | 417        |

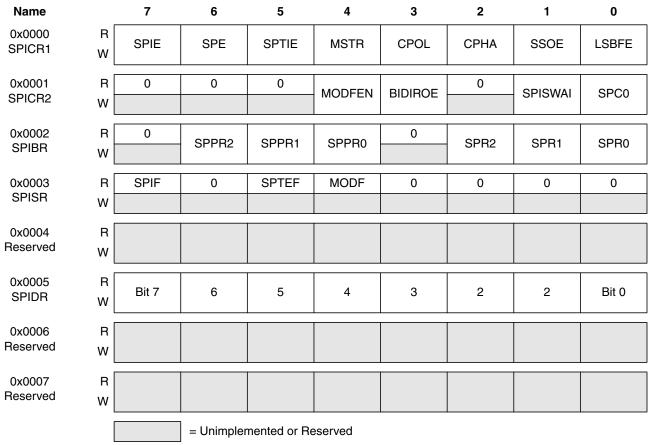

| 14.3 | Memory Map and Register Definition                           | 417        |

|      | 14.3.1 Module Memory Map                                     | 417        |

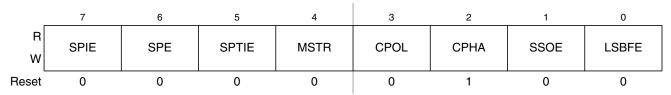

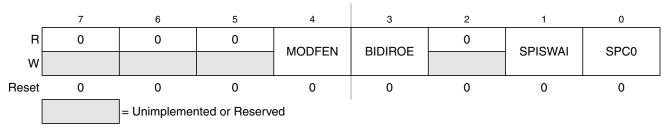

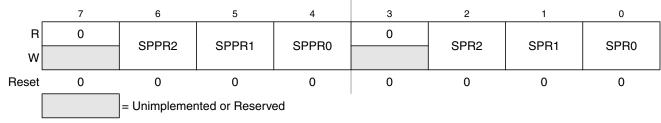

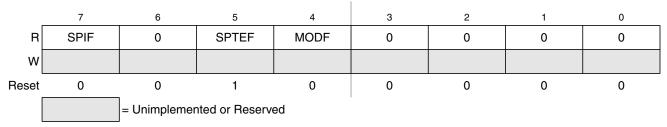

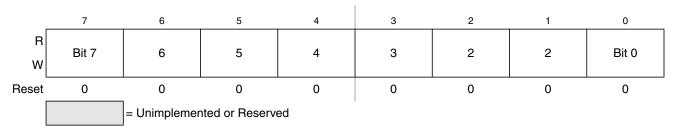

|      | 14.3.2 Register Descriptions                                 | 418        |

| 14.4 | Functional Description                                       | 425        |

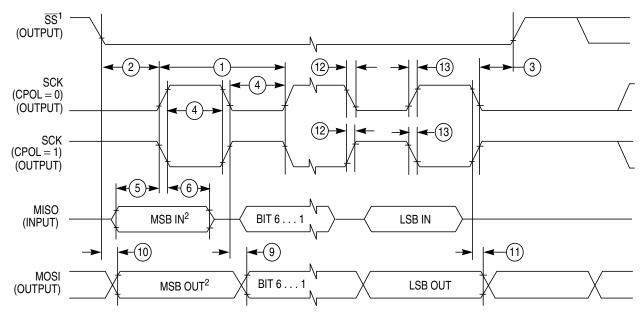

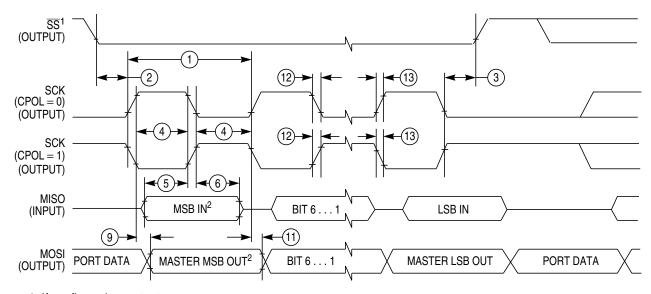

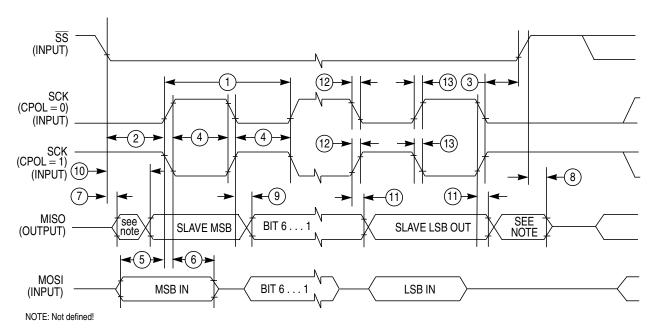

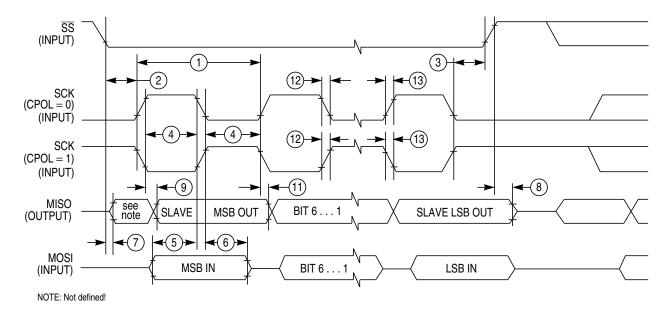

|      | 14.4.1 Master Mode                                           | 426        |

|      | 14.4.2 Slave Mode                                            | 427        |

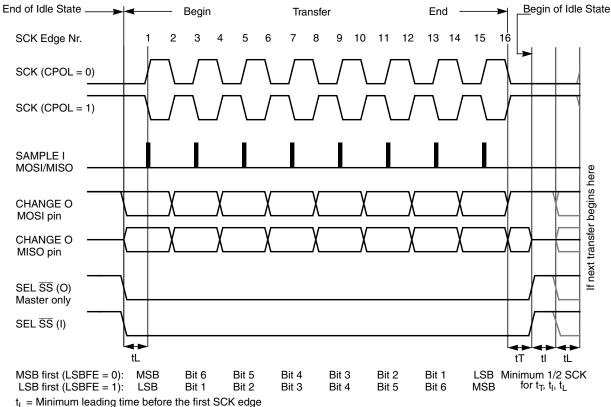

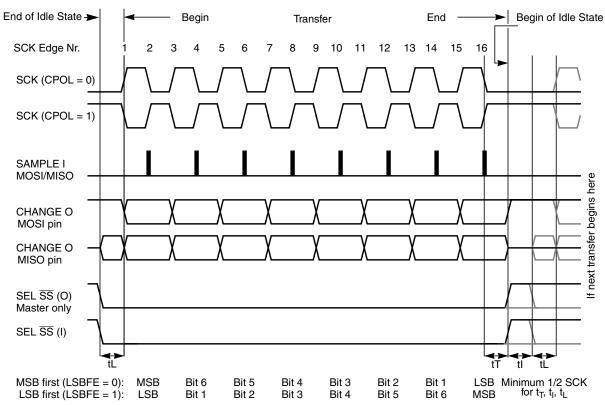

|      | 14.4.3 Transmission Formats                                  | 428        |

|      | 14.4.4 SPI Baud Rate Generation                              | 431        |

|      | 14.4.5 Special Features                                      | 432        |

|      | 14.4.6 Error Conditions                                      |            |

|      | 14.4.7 Operation in Run Mode                                 |            |

|      | 14.4.8 Operation in Wait Mode                                |            |

|      | 14.4.9 Operation in Stop Mode                                |            |

|      | Reset                                                        |            |

| 14.6 | Interrupts                                                   |            |

|      | 14.6.1 MODF                                                  |            |

|      | 14.6.2 SPIF                                                  |            |

|      | 14.6.3 SPTEF                                                 | 435        |

|      | Chantor 15                                                   |            |

|      | Chapter 15                                                   |            |

|      | Timer Module (TIM16B8CV1) Block Description                  |            |

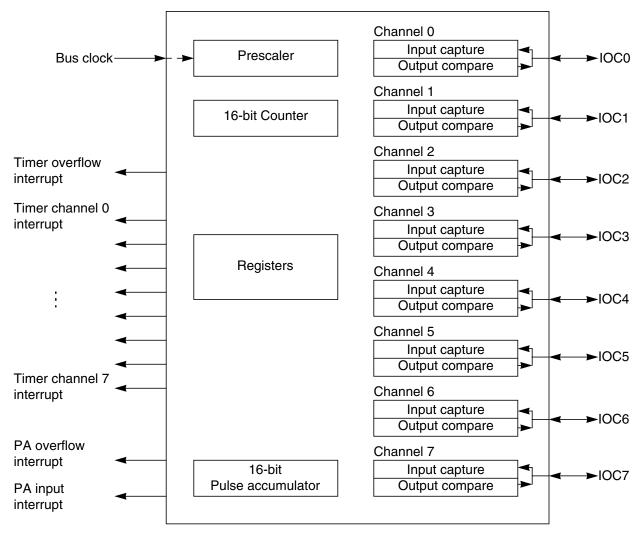

| 15.1 | Introduction                                                 |            |

|      | 15.1.1 Features                                              |            |

|      | 15.1.2 Modes of Operation                                    |            |

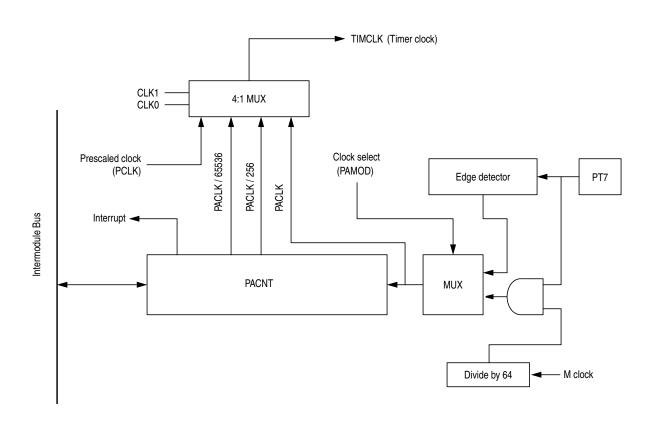

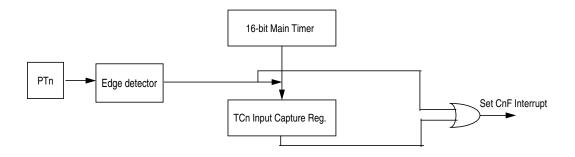

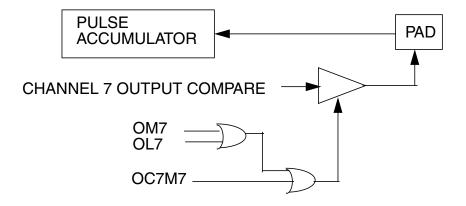

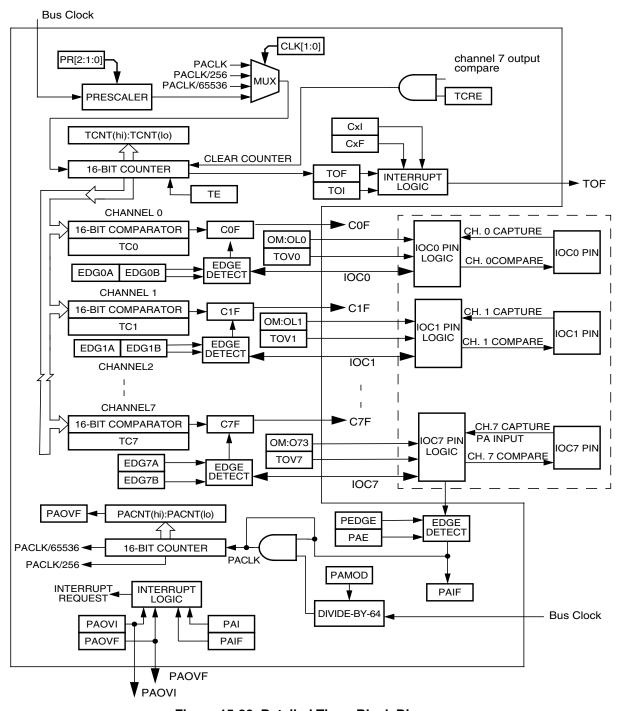

|      | 15.1.3 Block Diagrams                                        |            |

| 15.2 | External Signal Description                                  |            |

|      | 15.2.1 IOC7 — Input Capture and Output Compare Channel 7 Pin |            |

|      | 15.2.2 IOC6 — Input Capture and Output Compare Channel 6 Pin |            |

|      | 15.2.3 IOC5 — Input Capture and Output Compare Channel 5 Pin |            |

|      | 15.2.4 IOC4 — Input Capture and Output Compare Channel 4 Pin |            |

|      | 15.2.5 IOC3 — Input Capture and Output Compare Channel 3 Pin |            |

|      | 15.2.6 IOC2 — Input Capture and Output Compare Channel 2 Pin |            |

|      | 15.2.7 IOC1 — Input Capture and Output Compare Channel 1 Pin |            |

|      | 15.2.8 IOC0 — Input Capture and Output Compare Channel 0 Pin |            |

| 15.3 | Memory Map and Register Definition                           |            |

|      | 15.3.1 Module Memory Map                                     |            |

|      | 15.3.2 Register Descriptions                                 |            |

| 15.4 | Functional Description                                       |            |

|      |                                                              | 4 = 0      |

|      | 15.4.1 Prescaler                                             |            |

|      | 15.4.2 Input Capture                                         | 459        |

|      |                                                              | 459<br>459 |

|      | 13.4.3 Event Counter Mode                                                 |     |

|------|---------------------------------------------------------------------------|-----|

|      | 15.4.6 Gated Time Accumulation Mode                                       |     |

| 15.5 | Resets                                                                    | 460 |

| 15.6 | Interrupts                                                                | 460 |

|      | 15.6.1 Channel [7:0] Interrupt (C[7:0]F)                                  |     |

|      | 15.6.2 Pulse Accumulator Input Interrupt (PAOVI)                          |     |

|      | 15.6.3 Pulse Accumulator Overflow Interrupt (PAOVF)                       | 461 |

|      | 15.6.4 Timer Overflow Interrupt (TOF)                                     | 461 |

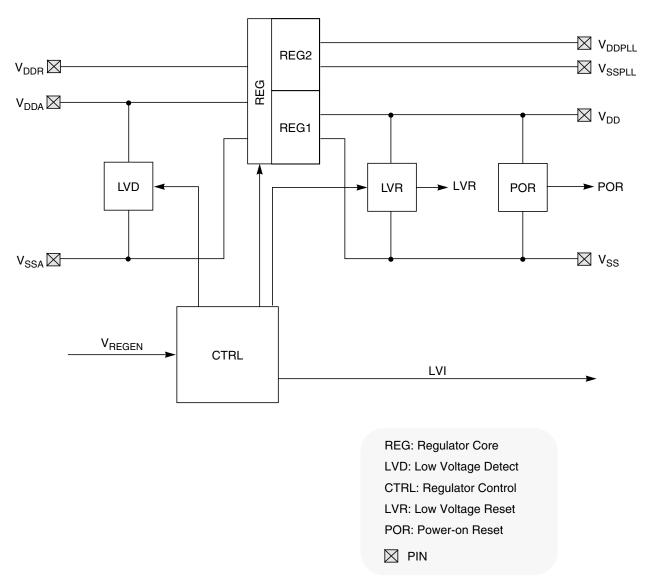

|      | Chapter 16                                                                |     |

|      | Dual Output Voltage Regulator (VREG3V3V2)                                 |     |

|      | Block Description                                                         |     |

| 16 1 | • • • • • • • • • • • • • • • • • • •                                     | 162 |

| 10.1 | Introduction                                                              |     |

|      | 16.1.1 Features                                                           |     |

|      | 16.1.2 Modes of Operation                                                 |     |

| 16.0 | 16.1.3 Block Diagram                                                      |     |

| 10.2 | External Signal Description                                               |     |

|      | 16.2.1 V <sub>DDR</sub> — Regulator Power Input                           |     |

|      | 16.2.2 V <sub>DDA</sub> , V <sub>SSA</sub> — Regulator Reference Supply   |     |

|      | 16.2.3 V <sub>DD</sub> , V <sub>SS</sub> — Regulator Output1 (Core Logic) |     |

|      | 16.2.4 V <sub>DDPLL</sub> , V <sub>SSPLL</sub> — Regulator Output2 (PLL)  |     |

| 16.2 | 16.2.5 V <sub>REGEN</sub> — Optional Regulator Enable                     |     |

| 10.5 |                                                                           |     |

|      | 16.3.1 Module Memory Map                                                  |     |

| 16.4 |                                                                           |     |

| 10.4 | Functional Description                                                    |     |

|      | 16.4.2 Full-Performance Mode                                              |     |

|      | 16.4.3 Reduced-Power Mode                                                 |     |

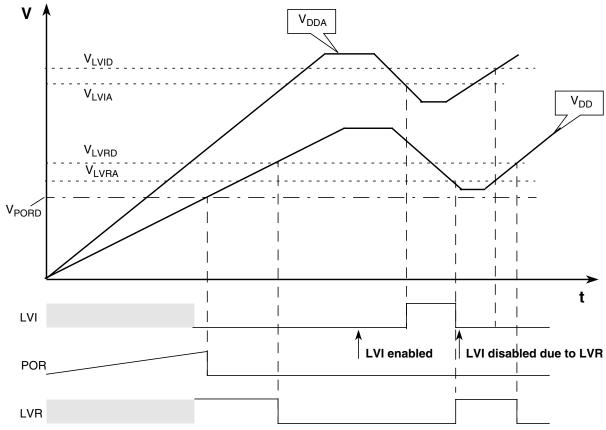

|      | 16.4.4 LVD — Low-Voltage Detect                                           |     |

|      | 16.4.5 POR — Power-On Reset                                               |     |

|      | 16.4.6 LVR — Low-Voltage Reset                                            |     |

|      | 16.4.7 CTRL — Regulator Control                                           |     |

| 16.5 | Resets                                                                    |     |

| 10.5 | 16.5.1 Power-On Reset                                                     |     |

|      | 16.5.2 Low-Voltage Reset                                                  |     |

| 16.6 | Interrupts                                                                |     |

| 10.0 | 16.6.1 LVI — Low-Voltage Interrupt                                        |     |

|      | Chapter 17                                                                |     |

|      | 16 Kbyte Flash Module (S12FTS16KV1)                                       |     |

| 17.1 | Introduction                                                              | 471 |

| -/   | 17.1.1 Glossary                                                           |     |

|      | 17.1.2 Features                                                           |     |

|      |                                                                           |     |

|      | 17.1.3 Modes of Operation           | . 472 |

|------|-------------------------------------|-------|

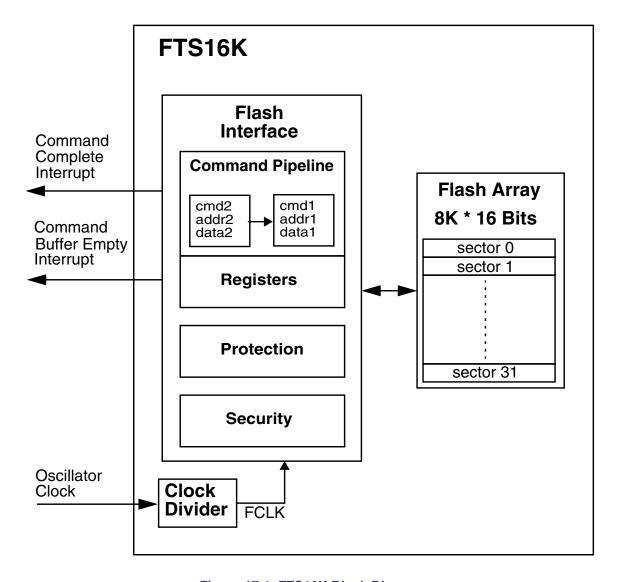

|      | 17.1.4 Block Diagram                | . 472 |

| 17.2 | External Signal Description         | . 472 |

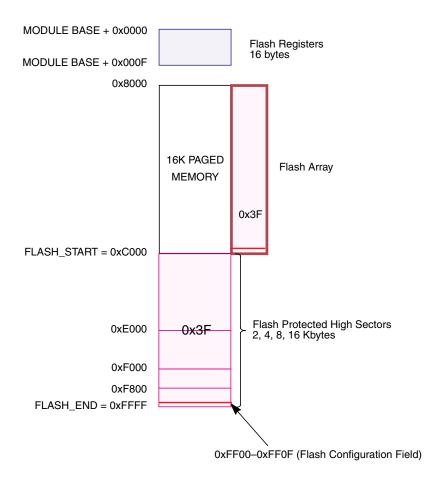

| 17.3 | Memory Map and Registers            | . 473 |

|      | 17.3.1 Module Memory Map            | . 473 |

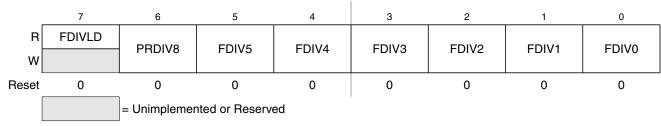

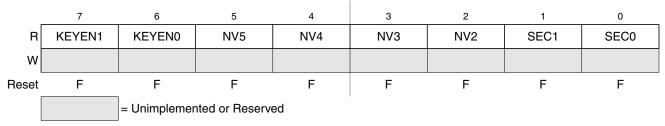

|      | 17.3.2 Register Descriptions        | . 475 |

| 17.4 | Functional Description              | . 486 |

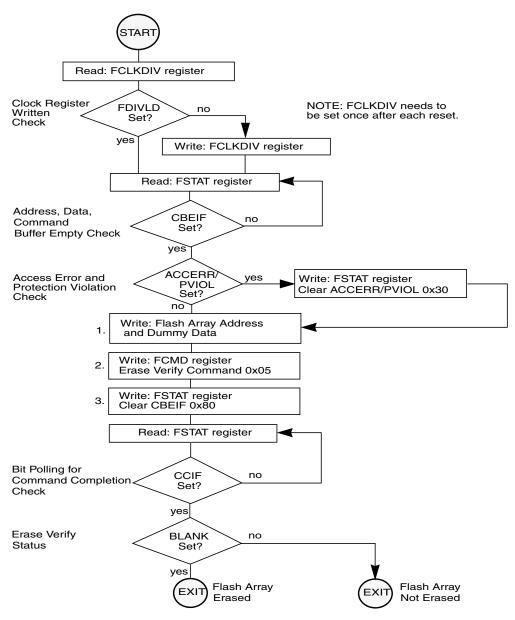

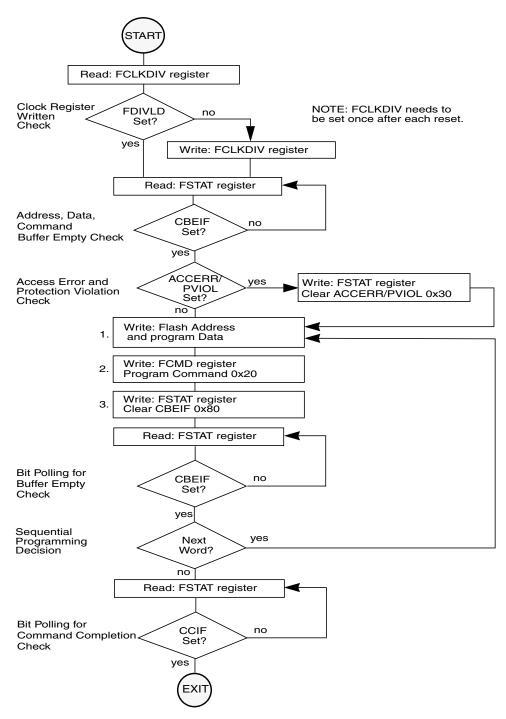

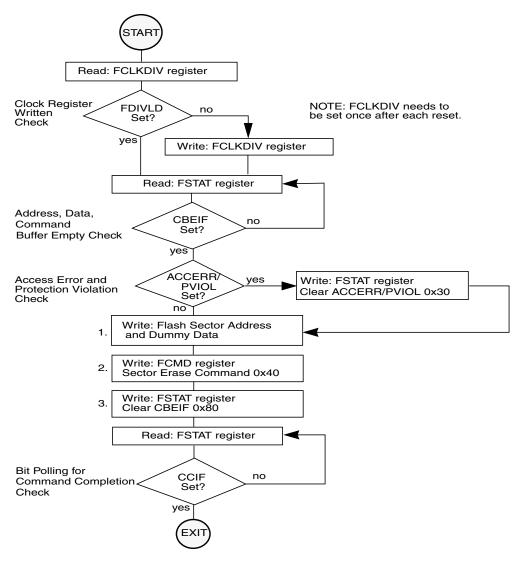

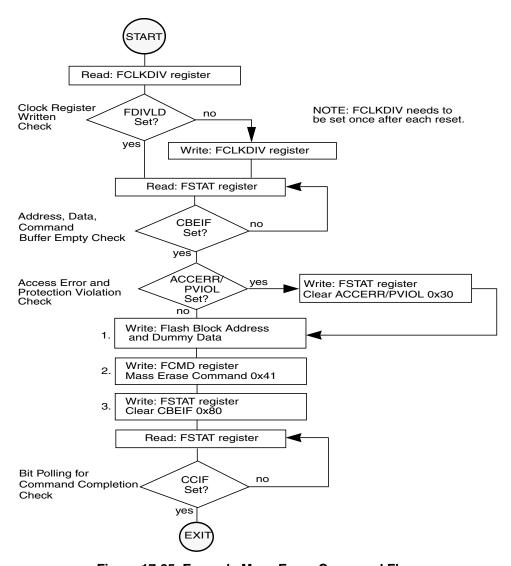

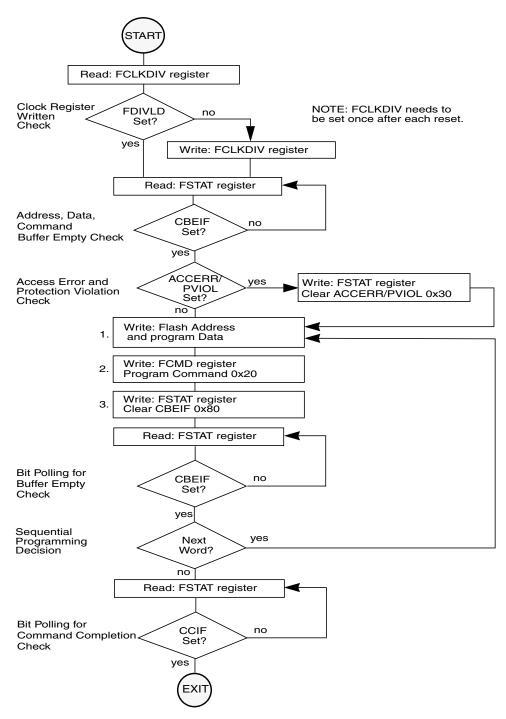

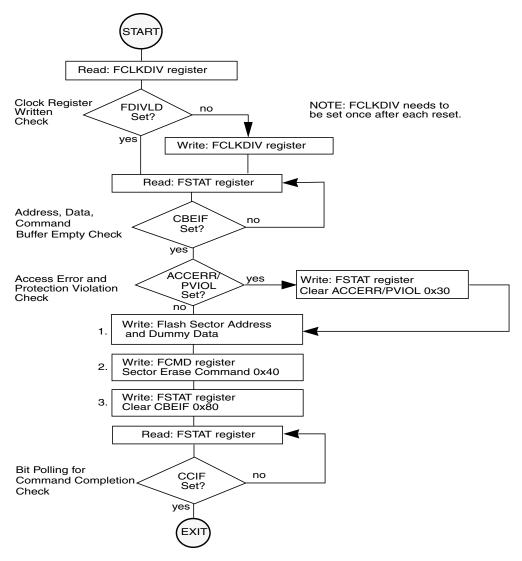

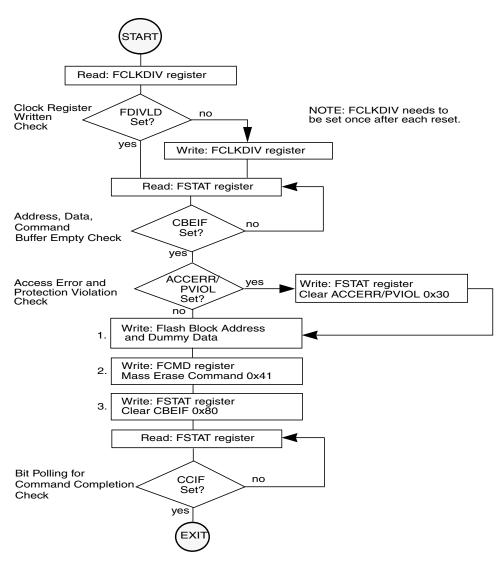

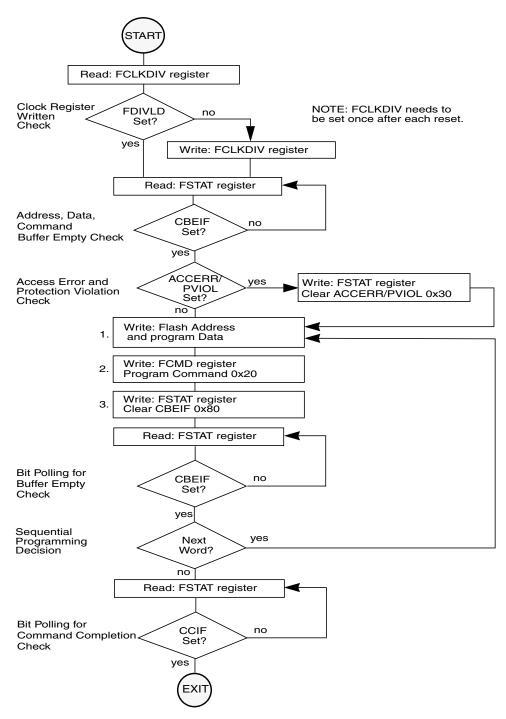

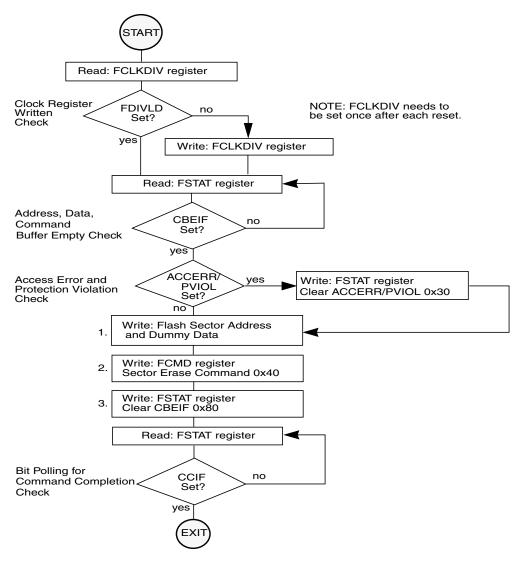

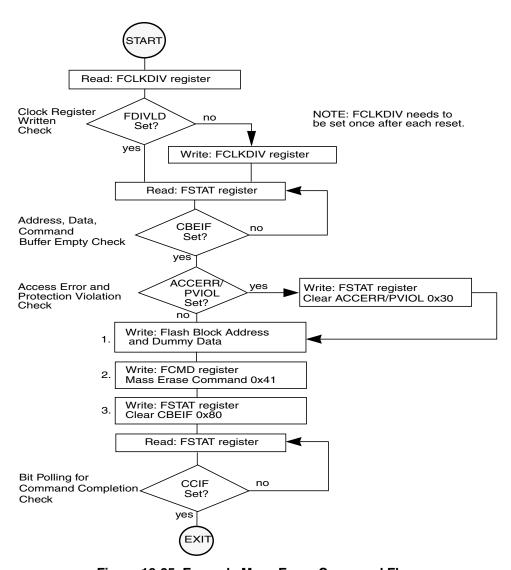

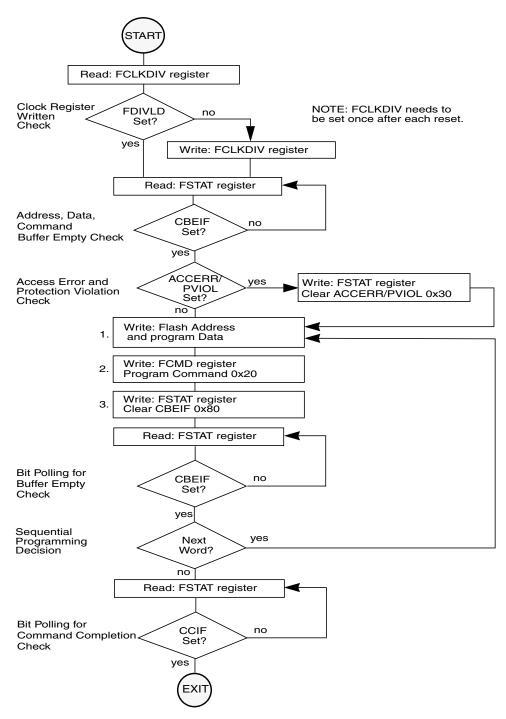

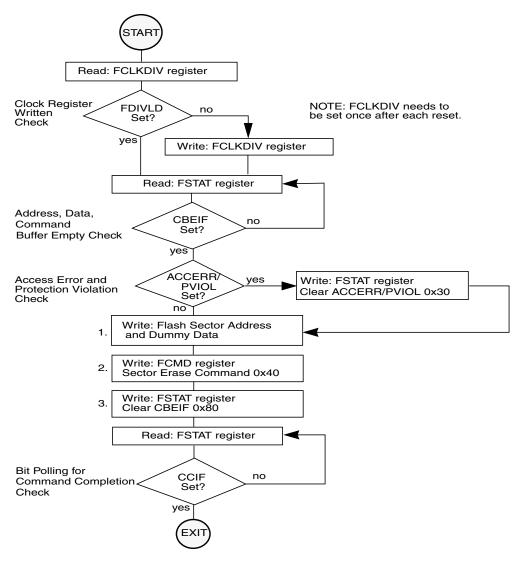

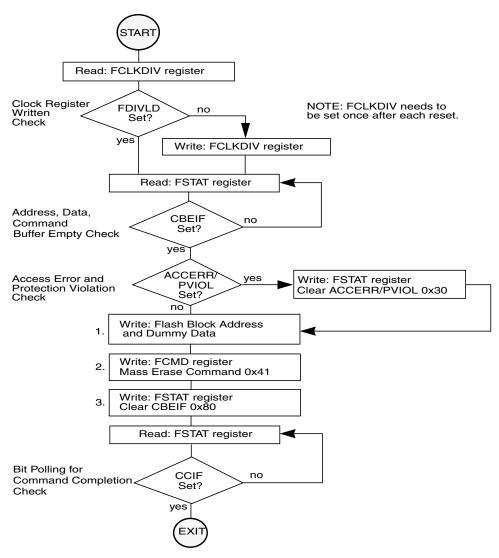

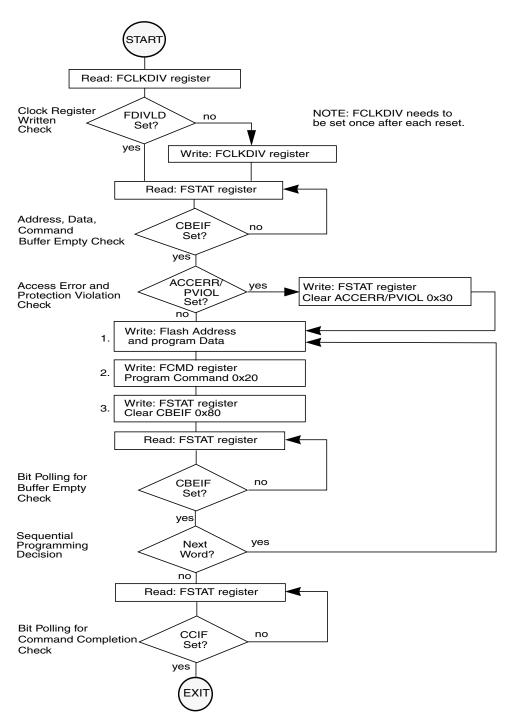

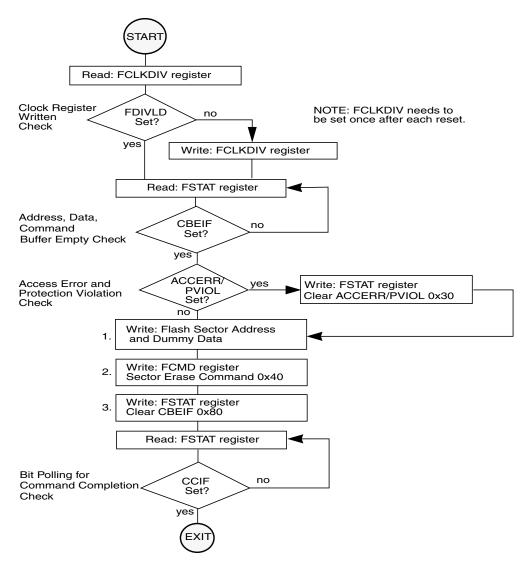

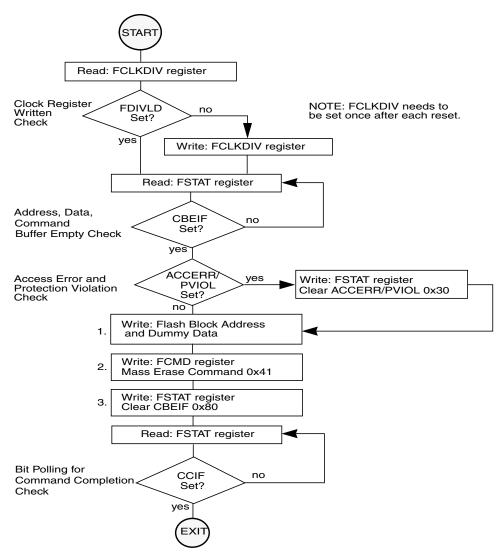

|      | 17.4.1 Flash Command Operations     | . 486 |

|      | 17.4.2 Operating Modes              | . 500 |

|      | 17.4.3 Flash Module Security        | . 500 |

|      | 17.4.4 Flash Reset Sequence         | . 502 |

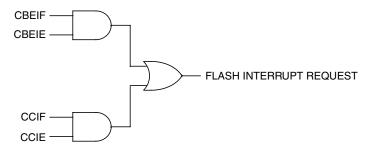

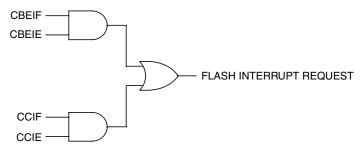

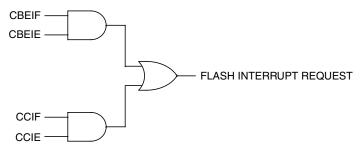

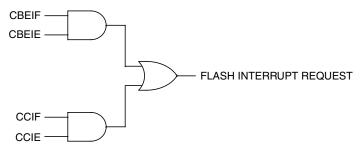

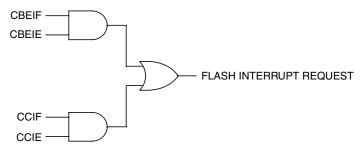

|      | 17.4.5 Interrupts                   | . 502 |

|      |                                     |       |

|      | Chapter 18                          |       |

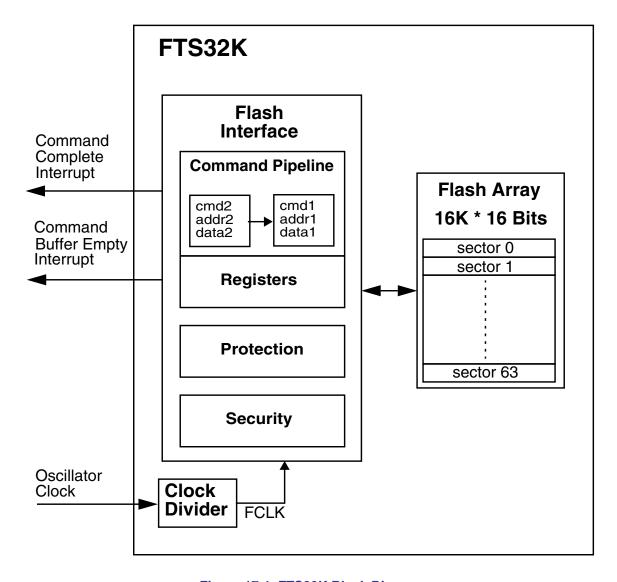

|      | 32 Kbyte Flash Module (S12FTS32KV1) |       |

| 18.1 | Introduction                        |       |

|      | 18.1.1 Glossary                     | . 503 |

|      | 18.1.2 Features                     |       |

|      | 18.1.3 Modes of Operation           |       |

|      | 18.1.4 Block Diagram                |       |

|      | External Signal Description         |       |

| 18.3 | Memory Map and Registers            |       |

|      | 18.3.1 Module Memory Map            |       |

|      | 18.3.2 Register Descriptions        |       |

| 18.4 | Functional Description              |       |

|      | 18.4.1 Flash Command Operations     |       |

|      | 18.4.2 Operating Modes              |       |

|      | 18.4.3 Flash Module Security        |       |

|      | 18.4.4 Flash Reset Sequence         | . 536 |

|      | 18.4.5 Interrupts                   | . 536 |

|      | Chaptar 10                          |       |

|      | Chapter 19                          |       |

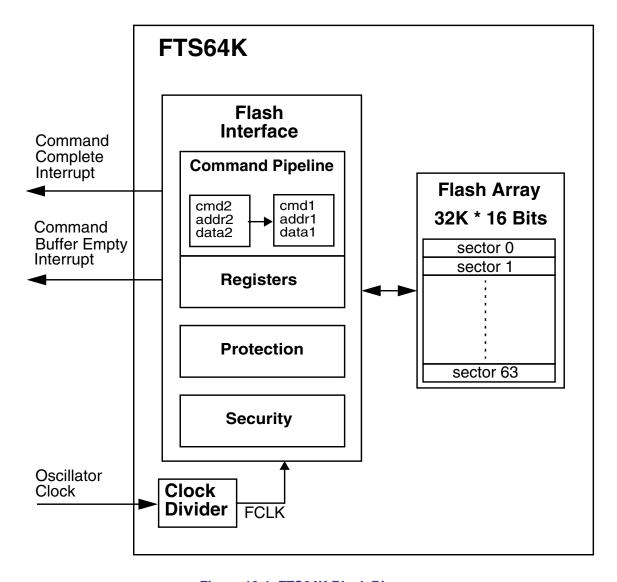

| 10.1 | 64 Kbyte Flash Module (S12FTS64KV4) | 507   |

| 19.1 | Introduction                        |       |

|      | 19.1.1 Glossary                     |       |

|      | 19.1.2 Features                     |       |

|      | 19.1.3 Modes of Operation           |       |

| 10.0 | 19.1.4 Block Diagram                |       |

|      | External Signal Description         |       |

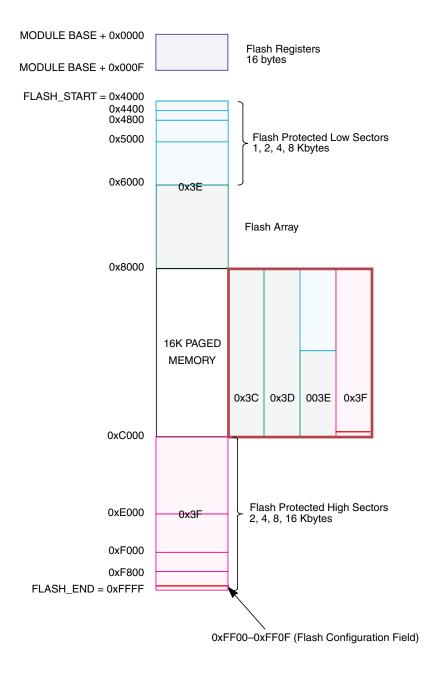

| 19.3 | Memory Map and Registers            |       |

|      | 19.3.1 Module Memory Map            |       |

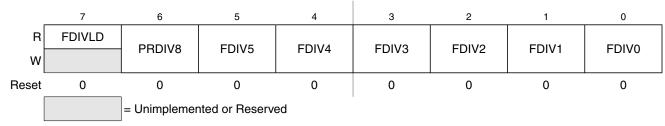

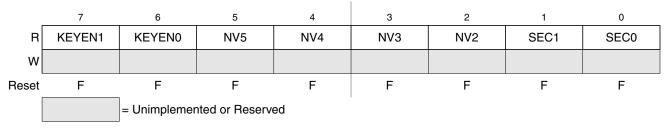

| 10.4 | 19.3.2 Register Descriptions        |       |

| 19.4 | Functional Description              |       |

|      | 19.4.1 Flash Command Operations     | . 554 |

|             | 19.4.2 Operating Modes                     | 568 |

|-------------|--------------------------------------------|-----|

|             | 19.4.3 Flash Module Security               | 568 |

|             | 19.4.4 Flash Reset Sequence                | 570 |

|             | 19.4.5 Interrupts                          | 570 |

|             | Chapter 20                                 |     |

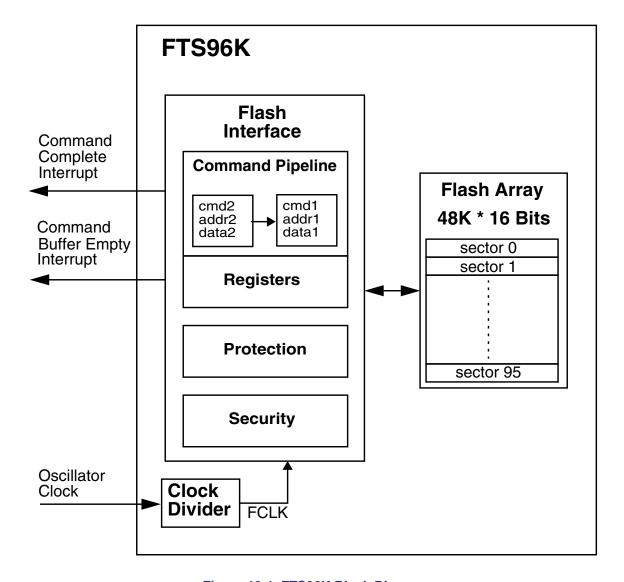

|             | 96 Kbyte Flash Module (S12FTS96KV1)        |     |

| 20.1        | Introduction                               | 571 |

| 20.1        | 20.1.1 Glossary                            |     |

|             | 20.1.1 Glossary                            |     |

|             | 20.1.2 Peatures  20.1.3 Modes of Operation |     |

|             | 20.1.4 Block Diagram                       |     |

| 20.2        | External Signal Description                |     |

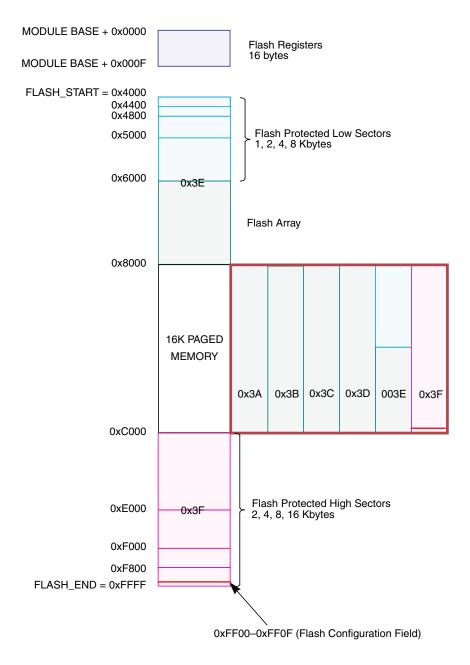

|             | Memory Map and Registers                   |     |

| 20.5        | 20.3.1 Module Memory Map                   |     |

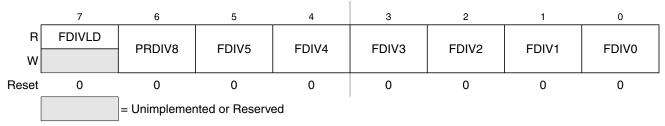

|             | 20.3.2 Register Descriptions               |     |

| 20.4        | Functional Description                     |     |

| 20.1        | 20.4.1 Flash Command Operations            |     |

|             | 20.4.2 Operating Modes                     |     |

|             | 20.4.3 Flash Module Security               |     |

|             | 20.4.4 Flash Reset Sequence                |     |

|             | 20.4.5 Interrupts                          |     |

|             |                                            |     |

|             | Chapter 21                                 |     |

|             | 128 Kbyte Flash Module (S12FTS128K1V1)     |     |

| 21.1        | Introduction                               |     |

|             | 21.1.1 Glossary                            |     |

|             | 21.1.2 Features                            |     |

|             | 21.1.3 Modes of Operation                  |     |

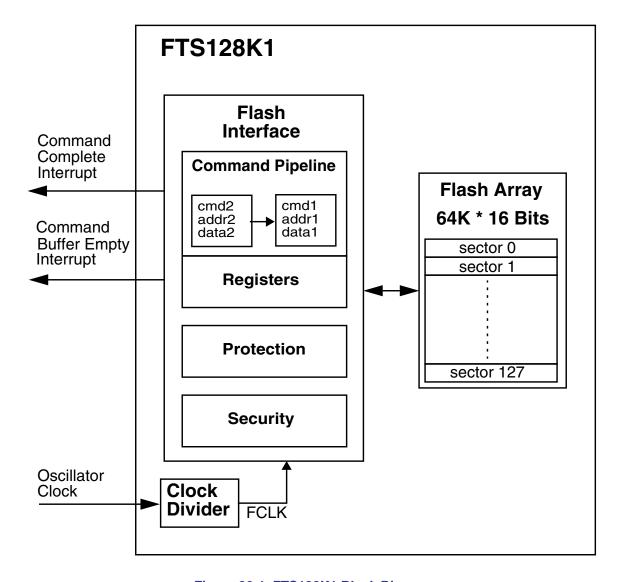

|             | 21.1.4 Block Diagram                       |     |

|             | External Signal Description                |     |

| 21.3        | Memory Map and Registers                   |     |

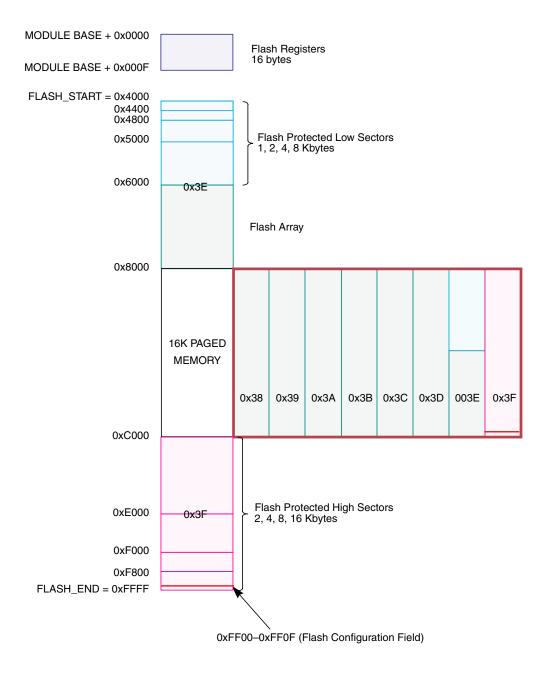

|             | 21.3.1 Module Memory Map                   |     |

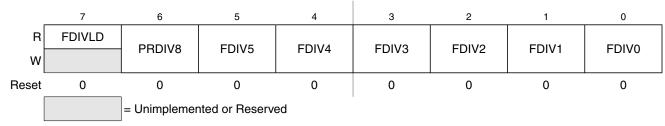

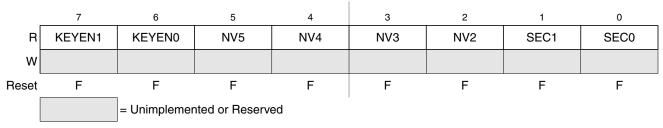

|             | 21.3.2 Register Descriptions               |     |

| 21.4        | Functional Description                     |     |

|             | 21.4.1 Flash Command Operations            |     |

|             | 21.4.2 Operating Modes                     |     |

|             | 21.4.3 Flash Module Security               |     |

|             | 21.4.4 Flash Reset Sequence                |     |

|             | 21.4.5 Interrupts                          | 638 |

|             | Appendix A                                 |     |

|             | Electrical Characteristics                 |     |

| <b>A</b> .1 |                                            | 639 |

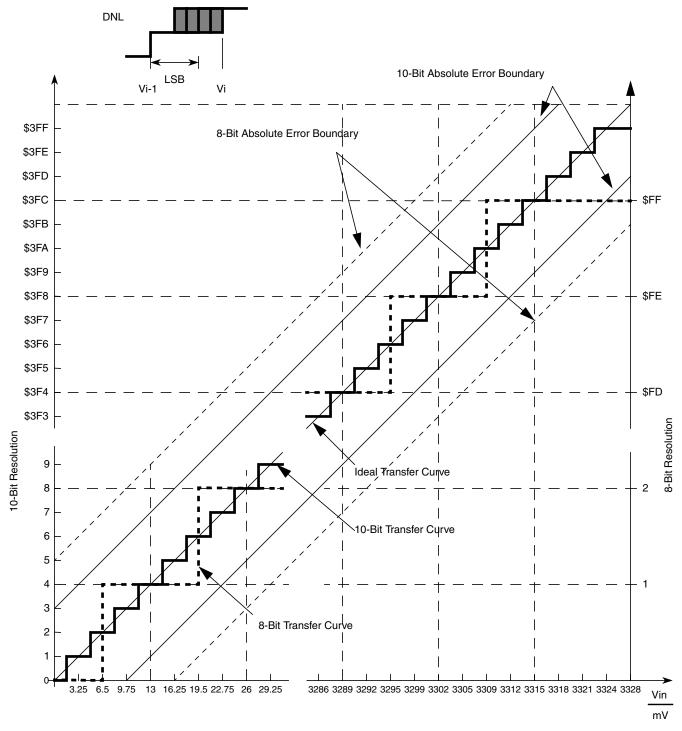

| A.2         | ATD Characteristics       |

|-------------|---------------------------|

| A.3         | MSCAN                     |

| A.4         | Reset, Oscillator and PLL |

| A.5         | NVM, Flash, and EEPROM    |

| A.6         | SPI                       |

| A.7         | Voltage Regulator         |

|             | Appendix B                |

|             | Emulation Information     |

| D 1         |                           |

| B.1         | General                   |

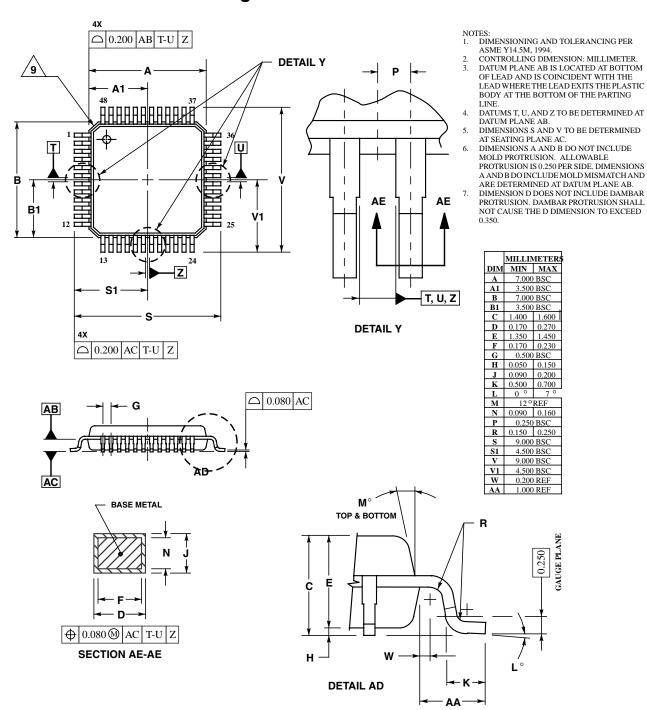

|             | Appendix C                |

|             | Package Information       |

| <b>C</b> .1 | General                   |

|             | Appendix D                |

|             | Derivative Differences    |

|             |                           |

|             | Appendix E                |

|             | Ordering Information      |

# Chapter 1 MC9S12GC Device Overview (MC9S12C128)

#### 1.1 Introduction

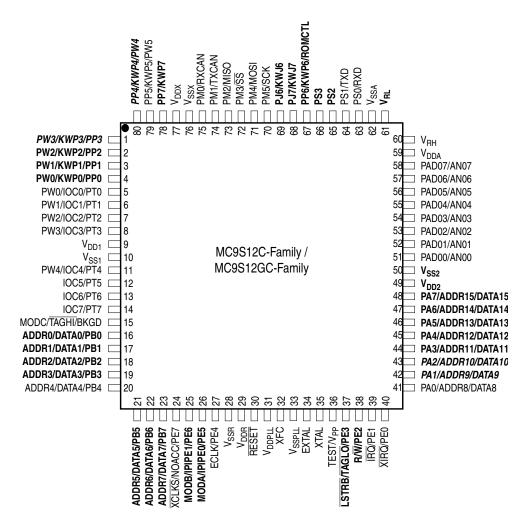

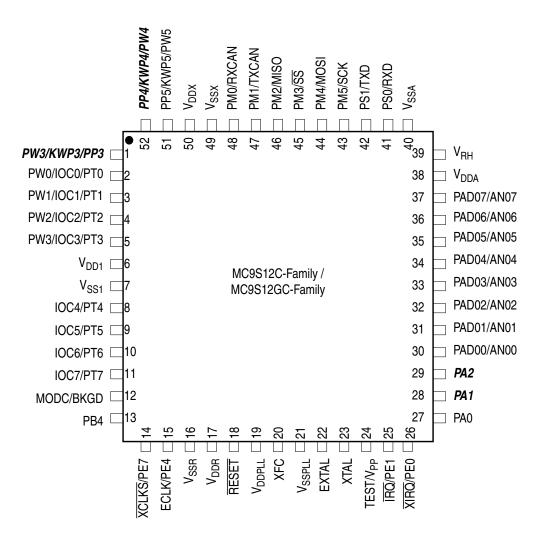

The MC9S12C-Family / MC9S12GC-Family and the MC9S12GC Family are 48/52/80 pin Flash-based industrial/automotive network control MCU families, which deliver the power and flexibility of the 16-bit core (CPU12) family to a whole new range of cost and space sensitive, general purpose industrial and automotive network applications. All MC9S12C-Family / MC9S12GC-Family and MC9S12GC Family members are comprised of standard on-chip peripherals including a 16-bit central processing unit (CPU12), up to 128K bytes of Flash EEPROM, up to 4K bytes of RAM, an asynchronous serial communications interface (SCI), a serial peripheral interface (SPI), an 8-channel 16-bit timer module (TIM), a 6-channel 8-bit pulse width modulator (PWM), an 8-channel, 10-bit analog-to-digital converter (ADC). The MC9S12C-Family / MC9S12GC-Family members also feature a CAN 2.0 A, B software compatible module (MSCAN12). All family members feature full 16-bit data paths throughout. The inclusion of a PLL circuit allows power consumption and performance to be adjusted to suit operational requirements. In addition to the I/O ports available in each module, up to 10 dedicated I/O port bits are available with wake-up capability from stop or wait mode. The devices are available in 48-, 52-, and 80-pin QFP packages, with the 80-pin version pin compatible to the HCS12 A, B, and D Family derivatives.

#### 1.1.1 Features

- 16-bit HCS12 core:

- HCS12 CPU

- Upward compatible with M68HC11 instruction set

- Interrupt stacking and programmer's model identical to M68HC11

- Instruction queue

- Enhanced indexed addressing

- MMC (memory map and interface)

- INT (interrupt control)

- BDM (background debug mode)

- DBG12 (enhanced debug12 module, including breakpoints and change-of-flow trace buffer)

- MEBI (multiplexed expansion bus interface) available only in 80-pin package version

- Wake-up interrupt inputs:

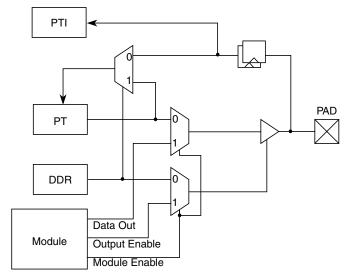

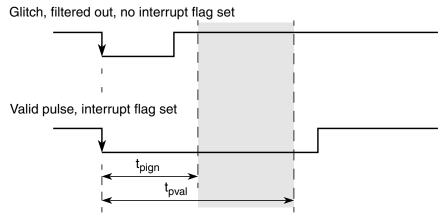

- Up to 12 port bits available for wake up interrupt function with digital filtering

Rev 01.19

#### Chapter 1 MC9S12C and MC9S12GC Device Overview (MC9S12C128)

- Memory options:

- 16K or 32Kbyte Flash EEPROM (erasable in 512-byte sectors)

64K, 96K, or 128Kbyte Flash EEPROM (erasable in 1024-byte sectors)

- 1K, 2K, or 4K Byte RAM

- Analog-to-digital converters:

- One 8-channel module with 10-bit resolution

- External conversion trigger capability

- Available on MC9S12C Family:

- One 1M bit per second, CAN 2.0 A, B software compatible module

- Five receive and three transmit buffers

- Flexible identifier filter programmable as 2 x 32 bit, 4 x 16 bit, or 8 x 8 bit

- Four separate interrupt channels for Rx, Tx, error, and wake-up

- Low-pass filter wake-up function

- Loop-back for self test operation

- Timer module (TIM):

- 8-channel timer

- Each channel configurable as either input capture or output compare

- Simple PWM mode

- Modulo reset of timer counter

- 16-bit pulse accumulator

- External event counting

- Gated time accumulation

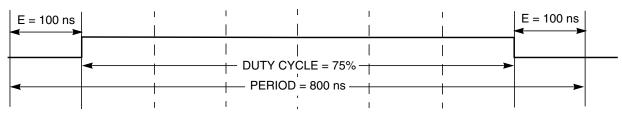

- PWM module:

- Programmable period and duty cycle

- 8-bit 6-channel or 16-bit 3-channel

- Separate control for each pulse width and duty cycle

- Center-aligned or left-aligned outputs

- Programmable clock select logic with a wide range of frequencies

- Fast emergency shutdown input

- Serial interfaces:

- One asynchronous serial communications interface (SCI)

- One synchronous serial peripheral interface (SPI)

- CRG (clock reset generator module)

- Windowed COP watchdog

- Real time interrupt

- Clock monitor

- Pierce or low current Colpitts oscillator

- Phase-locked loop clock frequency multiplier

- Limp home mode in absence of external clock

- Low power 0.5MHz to 16MHz crystal oscillator reference clock

- Operating frequency:

- 32MHz equivalent to 16MHz bus speed for single chip

- 32MHz equivalent to 16MHz bus speed in expanded bus modes

- Option of 9S12C Family: 50MHz equivalent to 25MHz bus speed

- All 9S12GC Family members allow a 50MHz operating frequency.

- Internal 2.5V regulator:

- Supports an input voltage range from 2.97V to 5.5V

- Low power mode capability

- Includes low voltage reset (LVR) circuitry

- Includes low voltage interrupt (LVI) circuitry

- 48-pin LQFP, 52-pin LQFP, or 80-pin QFP package:

- Up to 58 I/O lines with 5V input and drive capability (80-pin package)

- Up to 2 dedicated 5V input only lines (IRQ, XIRQ)

- 5V 8 A/D converter inputs and 5V I/O

- Development support:

- Single-wire background debug<sup>TM</sup> mode (BDM)

- On-chip hardware breakpoints

- Enhanced DBG12 debug features

# 1.1.2 Modes of Operation

User modes (expanded modes are only available in the 80-pin package version).

- Normal and emulation operating modes:

- Normal single-chip mode

- Normal expanded wide mode

- Normal expanded narrow mode

- Emulation expanded wide mode

- Emulation expanded narrow mode

- Special operating modes:

- Special single-chip mode with active background debug mode

- Special test mode (Freescale use only)

- Special peripheral mode (Freescale use only)

- Low power modes:

- Stop mode

- Pseudo stop mode

- Wait mode

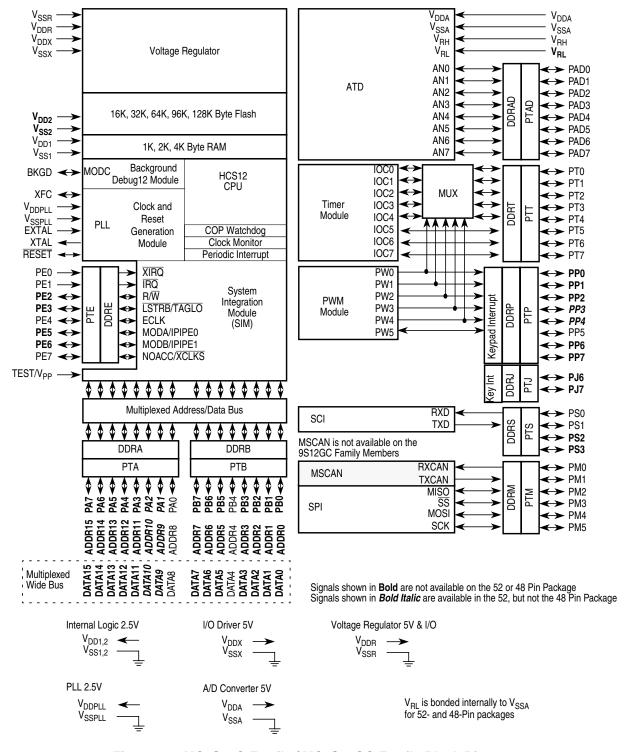

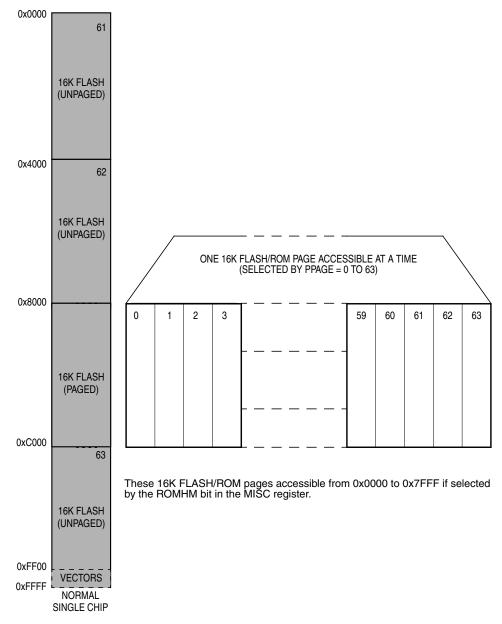

# 1.1.3 Block Diagram

Figure 1-1. MC9S12C-Family / MC9S12GC-Family Block Diagram

#### 1.2 **Memory Map and Registers**

#### 1.2.1 **Device Memory Map**

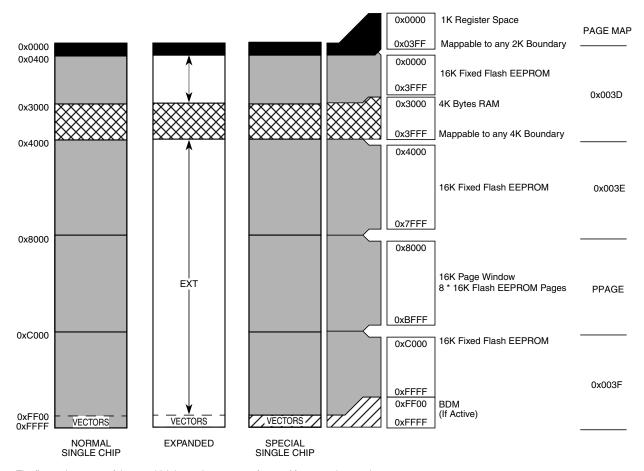

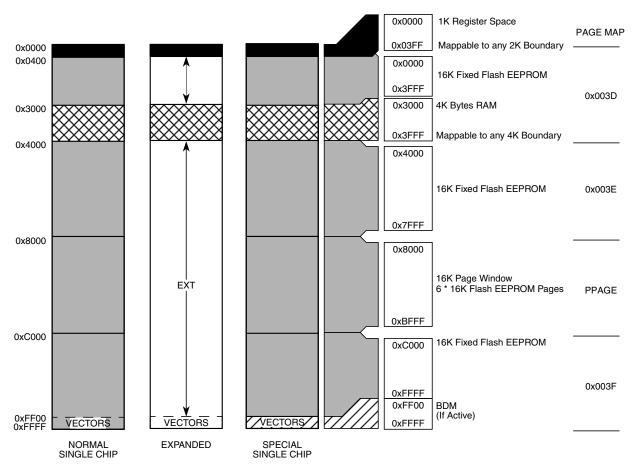

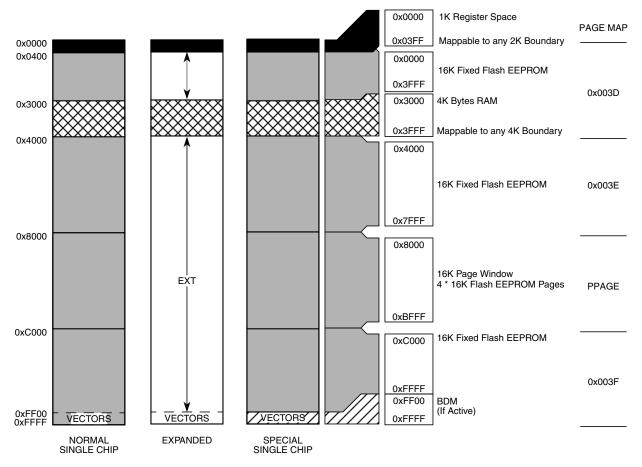

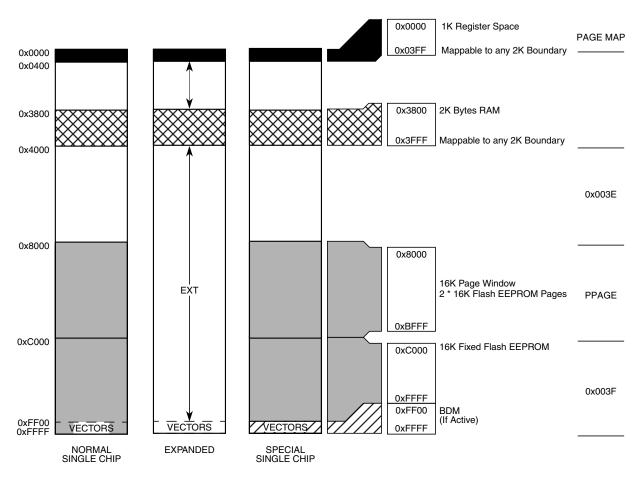

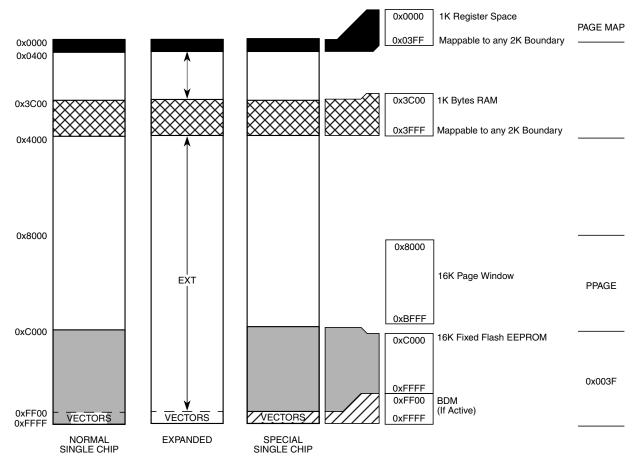

Table 1-1 shows the device register map after reset. Figure 1-2 through Figure 1-5 illustrate the full device memory map.

**Table 1-1. Device Register Map Overview**

| Address       | Module                                                  | Size |

|---------------|---------------------------------------------------------|------|

| 0x0000-0x0017 | Core (ports A, B, E, modes, inits, test)                | 24   |

| 0x0018        | Reserved                                                | 1    |

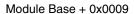

| 0x0019        | Voltage regulator (VREG)                                | 1    |

| 0x001A-0x001B | Device ID register                                      | 2    |

| 0x001C-0x001F | Core (MEMSIZ, IRQ, HPRIO)                               | 4    |

| 0x0020-0x002F | Core (DBG)                                              | 16   |

| 0x0030-0x0033 | Core (PPAGE <sup>(1)</sup> )                            | 4    |

| 0x0034-0x003F | Clock and reset generator (CRG)                         | 12   |

| 0x0040-0x006F | Standard timer module (TIM)                             | 48   |

| 0x0070-0x007F | Reserved                                                | 16   |

| 0x0080-0x009F | Analog-to-digital converter (ATD)                       | 32   |

| 0x00A0-0x00C7 | Reserved                                                | 40   |

| 0x00C8-0x00CF | Serial communications interface (SCI)                   | 8    |

| 0x00D0-0x00D7 | Reserved                                                | 8    |

| 0x00D8-0x00DF | Serial peripheral interface (SPI)                       | 8    |

| 0x00E0-0x00FF | Pulse width modulator (PWM)                             | 32   |

| 0x0100-0x010F | Flash control register                                  | 16   |

| 0x0110-0x013F | Reserved                                                | 48   |

| 0x0140-0x017F | Scalable controller area network (MSCAN) <sup>(2)</sup> | 64   |

| 0x0180-0x023F | Reserved                                                | 192  |

| 0x0240-0x027F | Port integration module (PIM)                           | 64   |

| 0x0280-0x03FF | Reserved                                                | 384  |

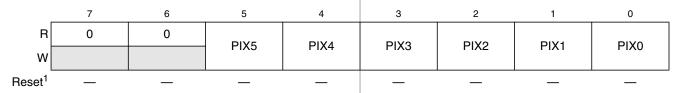

External memory paging is not supported on this device (Section 1.7.1, "PPAGE").

Not available on MC9S12GC Family devices

0x0000-0x03FF: Register Space

0x0000-0x0FFF: 4K RAM (only 3K visible 0x0400-0x0FFF)

Flash erase sector size is 1024 bytes

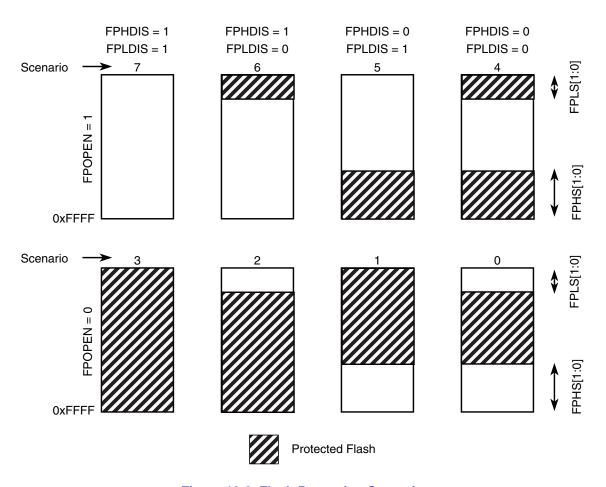

Figure 1-2. MC9S12C128 and MC9S12GC128 User Configurable Memory Map

0x0000-0x03FF: Register Space

0x0000-0x0FFF: 4K RAM (only 3K visible 0x0400-0x0FFF)

Flash erase sector size is 1024 bytes

Figure 1-3. MC9S12C96 and MC9S12GC96 User Configurable Memory Map

0x0000-0x03FF: Register space

$0x0000-0x0FFF: 4K\ RAM\ (only\ 3K\ visible\ 0x0400-0x0FFF)$

Flash erase sector size is 1024 Bytes

Figure 1-4. MC9S12C64 and MC9S12GC64 User Configurable Memory Map

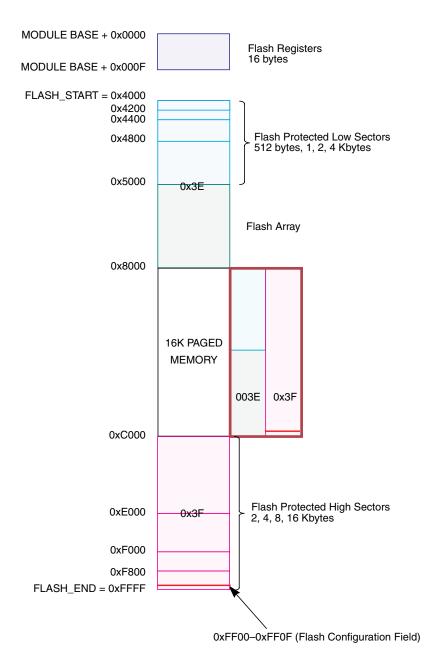

0x0000-0x03FF: Register space 0x0800-0x0FFF: 2K RAM

Flash erase sector size is 512 bytes

The flash page 0x003E is visible at 0x4000-0x7FFF in the memory map if ROMHM = 0.

In the figure ROMHM = 1 removing page 0x003E from 0x4000-0x7FFF.

Figure 1-5. MC9S12C32 and MC9S12GC32 User Configurable Memory Map

0x0000-0x03FF: Register Space 0x0C00-0x0FFF: 1K RAM

The 16K flash array page 0x003F is also visible in the PPAGE window when PPAGE register contents are odd. Flash Erase Sector Size is 512 Bytes

Figure 1-6. MC9S12GC16 User Configurable Memory Map

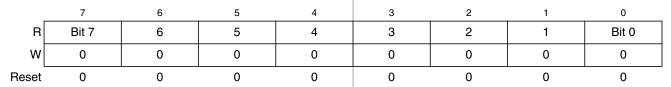

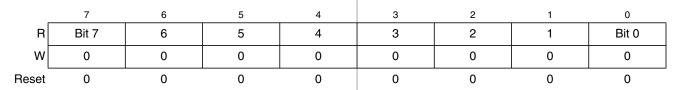

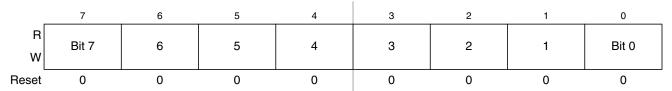

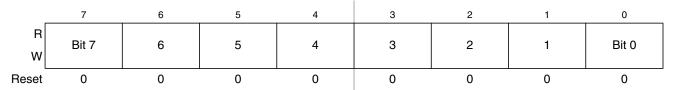

# 1.2.2 Detailed Register Map

The detailed register map of the MC9S12C128 is listed in address order below.

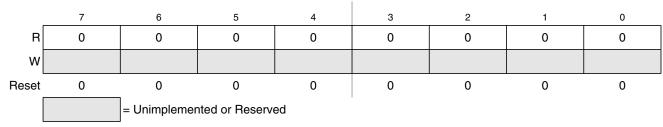

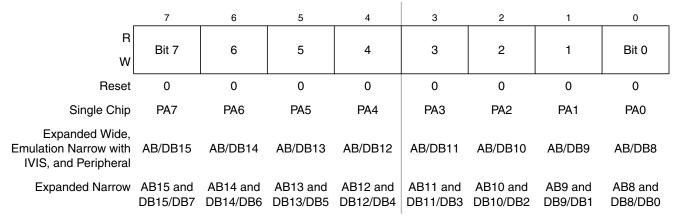

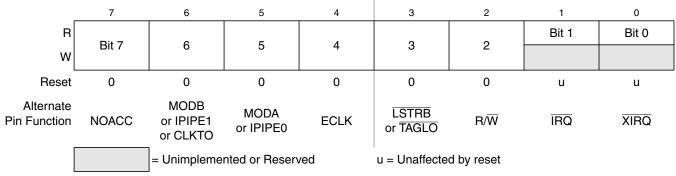

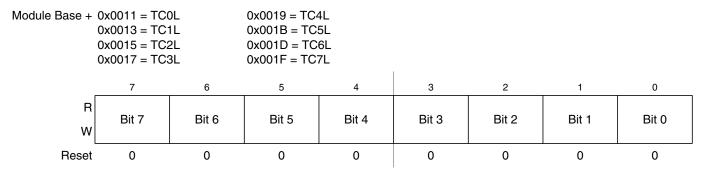

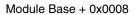

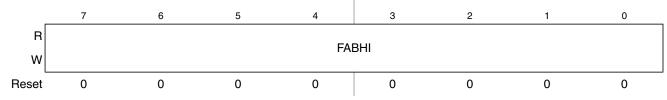

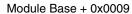

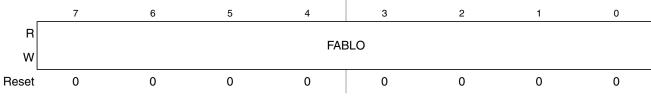

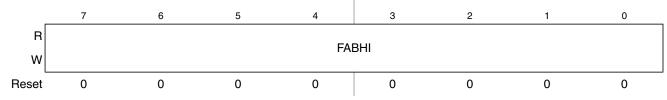

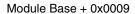

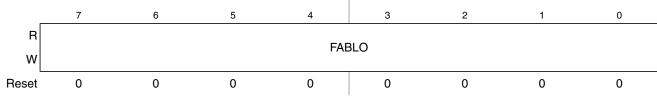

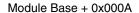

# 0x0000-0x000F MEBI Map 1 of 3 (HCS12 Multiplexed External Bus Interface)

| Address | Name     |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

| 0x0000  | PORTA    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0001  | PORTB    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0002  | DDRA     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0003  | DDRB     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

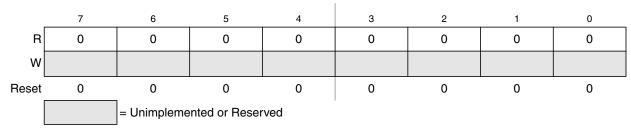

| 0x0004  | Reserved | Read:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          | Write:          |        | •     |       |       |       | •     |       | •     |

| 0x0005  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          | Read:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0006  | Reserved | Write:          | 0      | U     | 0     | 0     | 0     | 0     | 0     | U     |

|         |          | Read:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0007  | Reserved | Write:          |        |       |       |       |       |       |       |       |

| 0x0008  | PORTE    | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | Bit 1 | Bit 0 |

| 0x0009  | DDRE     | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | Bit 2 | 0     | 0     |

| 0x000A  | PEAR     | Read:<br>Write: | NOACCE | 0     | PIPOE | NECLK | LSTRE | RDWE  | 0     | 0     |

| 0x000B  | MODE     | Read:<br>Write: | MODC   | MODB  | MODA  | 0     | IVIS  | 0     | EMK   | EME   |

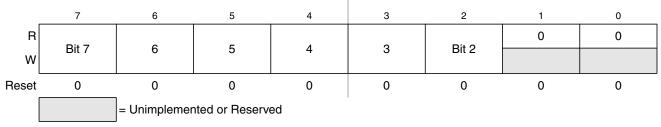

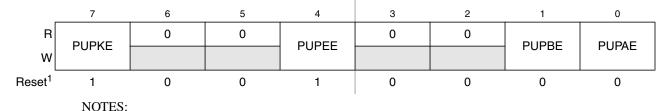

| 0x000C  | PUCR     | Read:           | PUPKE  | 0     | 0     | PUPEE | 0     | 0     | PUPBE | PUPAE |

| 0,0000  | 1 0011   | Write:          | TOTAL  |       |       | TOTEL |       |       | TOTBL | IOIAL |

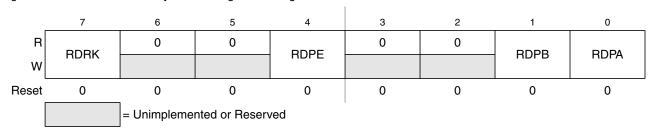

| 0x000D  | RDRIV    | Read:<br>Write: | RDPK   | 0     | 0     | RDPE  | 0     | 0     | RDPB  | RDPA  |

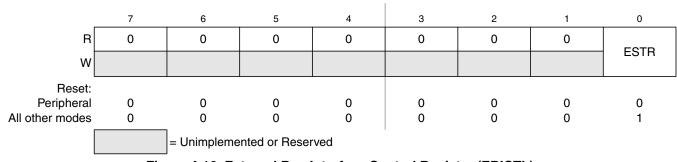

| 0x000E  | EBICTL   | Read:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | ESTR  |

| ONOUL   | LDIOIL   | Write:          |        |       |       |       |       |       |       |       |

| 0x000F  | Reserved | Read:<br>Write: | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

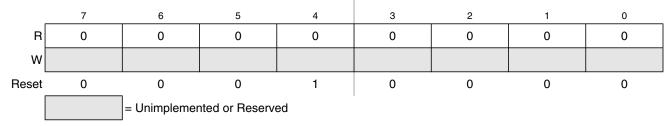

# 0x0010-0x0014 MMC Map 1 of 4 (HCS12 Module Mapping Control)

| Address | Name     |        | Bit 7    | Bit 6    | Bit 5      | Bit 4      | Bit 3      | Bit 2  | Bit 1  | Bit 0  |

|---------|----------|--------|----------|----------|------------|------------|------------|--------|--------|--------|

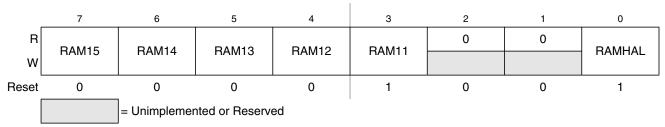

| 0x0010  | INITRM   | Read:  | RAM15    | RAM14    | RAM13      | RAM12 RAM1 | RAM11      | 0      | 0      | RAMHAL |

|         |          | Write: | 10/10/13 | T U WITH | 117 (17110 | TU WIVITZ  | I D WIVI I |        |        |        |

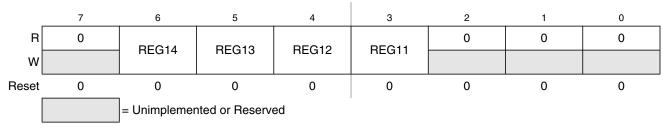

| 0x0011  | INITRG   | Read:  | 0        | REG14    | REG13      | REG12      | REG11      | 0      | 0      | 0      |

|         | INITAG   | Write: |          | ILC 14   | ILLUIS     | ILLUIZ     |            |        |        |        |

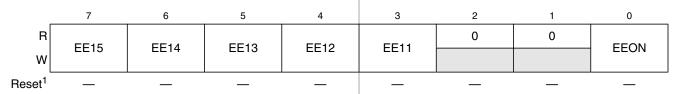

| 0x0012  | INITEE   | Read:  | EE15     | EE14     | EE13       | EE12       | EE11       | 0      | 0      | EEON   |

| 00012   |          | Write: | EE13     | CC 14    | LEIS       | LE 12      |            |        |        | LLON   |

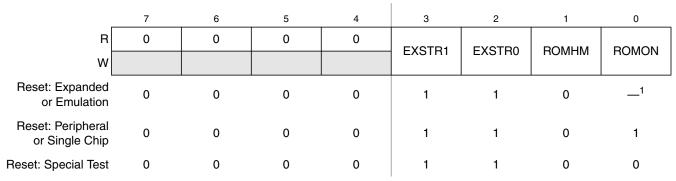

| 0.0010  | MICC     | Read:  | 0        | 0        | 0          | 0          | EXSTR1     | EXSTR0 | DOMENA | ROMON  |

| 0x0013  | MISC     | Write: |          |          |            |            | EXSIRI     | EXSINU | ROMHM  | ROWON  |

| 00044   | Reserved | Read:  | 0        | 0        | 0          | 0          | 0          | 0      | 0      | 0      |

| 0x0014  |          | Write: |          |          |            |            |            |        |        |        |

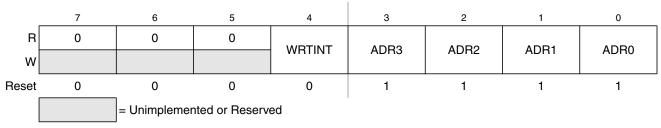

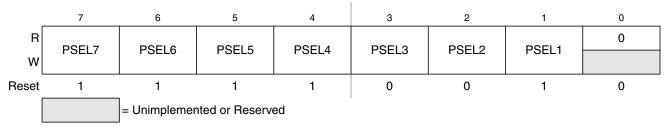

# 0x0015-0x0016 INT Map 1 of 2 (HCS12 Interrupt)

| Address | Name  |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0015  | ITCR  | Read:           | 0     | 0     | 0     | WRINT | ADR3  | ADR2  | ADR1  | ADR0  |

| 0,0015  |       | Write:          |       |       |       |       |       |       |       | ADITO |

| 0x0016  | ITEST | Read:<br>Write: | INTE  | INTC  | INTA  | INT8  | INT6  | INT4  | INT2  | INT0  |

## 0x0017-0x0017 MMC Map 2 of 4 (HCS12 Module Mapping Control)

| Address | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0017  | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          | Write: |       |       |       |       |       |       |       |       |

# 0x0018-0x0018 Miscellaneous Peripherals (Device User Guide)

| Address | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| 0x0018  | Reserved | Read:  | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

|         |          | Write: |       |       |       |       |       |       |       |       |

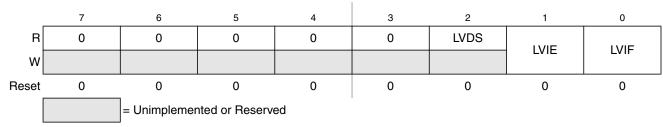

# 0x0019-0x0019 VREG3V3 (Voltage Regulator)

| Address | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

| \$0019  | VREGCTRL | Read:  | 0     | 0     | 0     | 0     | 0     | LVDS  | LVIE  | LVIF  |

|         |          | Write: |       |       |       |       |       |       | LVIL  | LVII  |

# 0x001A-0x001B Miscellaneous Peripherals (Device User Guide)

| Address | Name    |        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|--------|-------|-------|-------|-------|-------|-------|-------|-------|

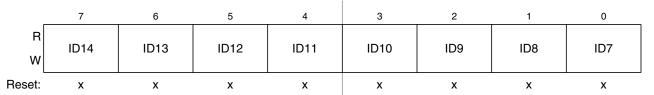

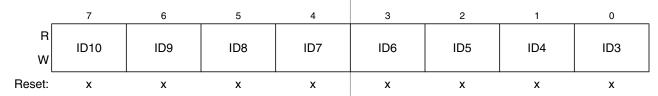

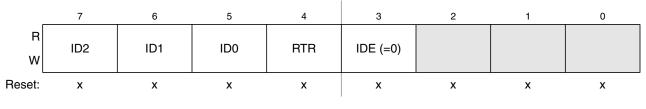

| 0x001A  | PARTIDH | Read:  | ID15  | ID14  | ID13  | ID12  | ID11  | ID10  | ID9   | ID8   |

|         |         | Write: |       |       |       |       |       |       |       |       |

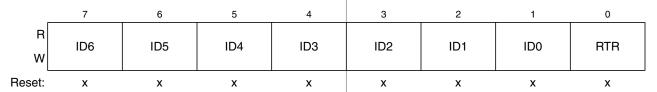

| 0x001B  | PARTIDL | Read:  | ID7   | ID6   | ID5   | ID4   | ID3   | ID2   | ID1   | ID0   |

|         | FANTIDL | Write: |       |       |       |       |       |       |       |       |

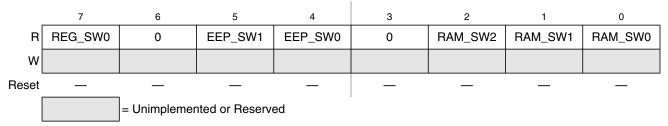

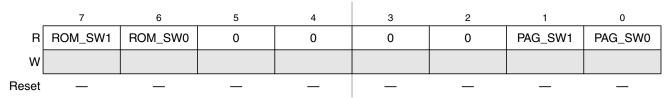

### 0x001C-0x001D MMC Map 3 of 4 (HCS12 Module Mapping Control, Device User Guide)

| Address | Name        |        | Bit 7   | Bit 6   | Bit 5   | Bit 4   | Bit 3 | Bit 2   | Bit 1   | Bit 0   |

|---------|-------------|--------|---------|---------|---------|---------|-------|---------|---------|---------|

| 0x001C  | MEMSIZ0     | Read:  | reg_sw0 | 0       | eep_sw1 | eep_sw0 | 0     | ram_sw2 | ram_sw1 | ram_sw0 |

| 0,0010  | IVILIVISIZO | Write: |         |         |         |         |       |         |         |         |

| 0x001D  | MEMSIZ1     | Read:  | rom_sw1 | rom_sw0 | 0       | 0       | 0     | 0       | pag_sw1 | pag_sw0 |

| OXOUTD  | IVILIVISIZI | Write: |         |         |         |         |       |         |         |         |

# 0x001E-0x001E MEBI Map 2 of 3 (HCS12 Multiplexed External Bus Interface)

| Address | Name    |        | Bit 7 | Bit 6   | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|---------|--------|-------|---------|-------|-------|-------|-------|-------|-------|

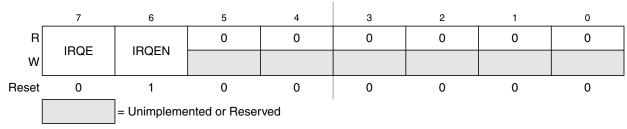

| 0x001E  | INTCR   | Read:  | IRQE  | IRQEN   | 0     | 0     | 0     | 0     | 0     | 0     |

| OXOUTE  | IIVIOII | Write: | IIIQL | IIIQLIV |       |       |       |       |       |       |

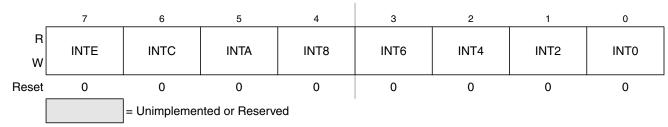

# 0x001F-0x001F INT Map 2 of 2 (HCS12 Interrupt)

| Address | Name   |        | Bit 7 | Bit 6 | Bit 5 | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|--------|--------|-------|-------|-------|--------|-------|-------|-------|-------|

| 0x001F  | HPRIO  | Read:  | PSEL7 | PSEL6 | PSEL5 | PSEL4  | PSEL3 | PSEL2 | PSEL1 | 0     |

| UXUUTI  | TIFNIO | Write: | FJELI | FOLLO | FSELS | F JLL4 | FOLLS | FOLLZ | FOLLI |       |

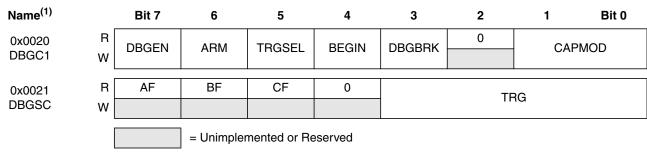

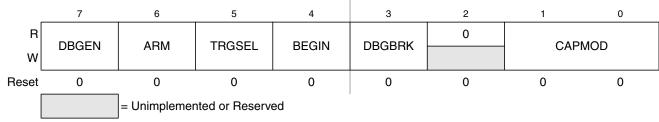

# 0x0020-0x002F DBG (Including BKP) Map 1 of 1 (HCS12 Debug)

| Address | Name    |                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1 | Bit 0 |  |

|---------|---------|-----------------|--------|--------|--------|--------|--------|-----------|-------|-------|--|

| 0x0020  | DBGC1   | Read:<br>Write: | DBGEN  | ARM    | TRGSEL | BEGIN  | DBGBRK | 0         | CAP   | MOD   |  |

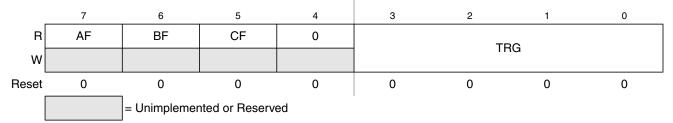

| 0x0021  | DBGSC   | Read:           | AF     | BF     | CF     | 0      |        | TF        | 26    |       |  |

| 0,0021  | DBGGC   | Write:          |        |        |        |        |        |           |       |       |  |

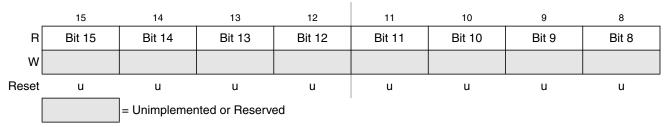

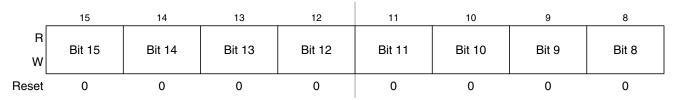

| 0x0022  | DBGTBH  | Read:           | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10    | Bit 9 | Bit 8 |  |

| 000022  | DBGTBIT | Write:          |        |        |        |        |        |           |       |       |  |

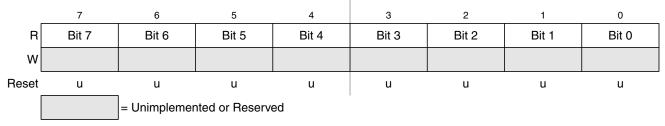

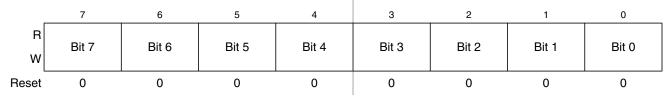

| 0x0023  | DBGTBL  | Read:           | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3  | Bit 2     | Bit 1 | Bit 0 |  |

| 00025   | DBGTBL  | Write:          |        |        |        |        |        |           |       |       |  |

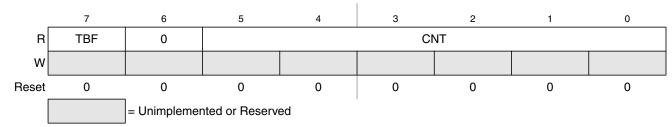

| 0x0024  | DBGCNT  | Read:           | TBF    | 0      |        |        | CI     | <b>IT</b> |       |       |  |

| 00024   | DBGCIVI | Write:          |        |        |        |        |        |           |       |       |  |

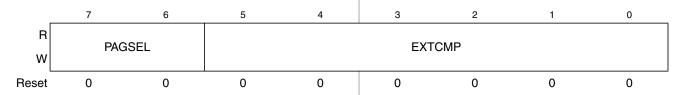

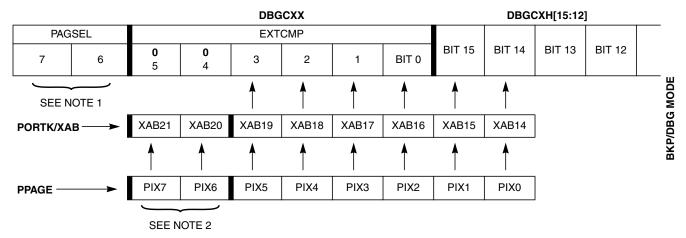

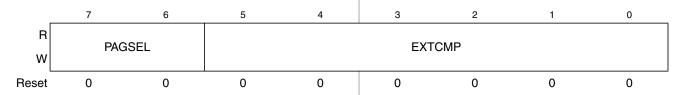

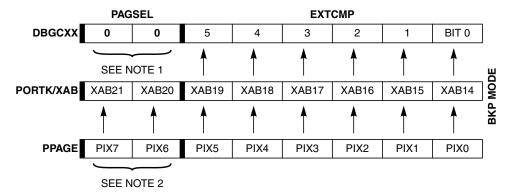

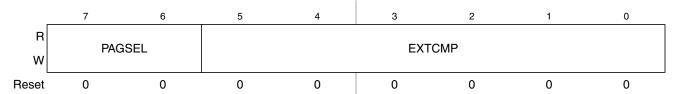

| 0x0025  | DBGCCX  | Read:<br>Write: | PAG    | SEL    |        |        | EXT    | CMP       |       |       |  |

# 0x0020-0x002F DBG (Including BKP) Map 1 of 1 (HCS12 Debug) (continued)

| Address | Name            |                 | Bit 7  | Bit 6  | Bit 5  | Bit 4  | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|-----------------|-----------------|--------|--------|--------|--------|-------|-------|-------|-------|

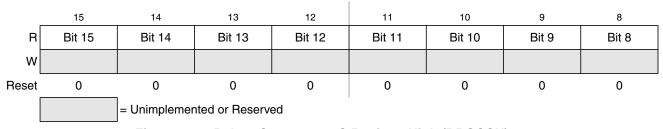

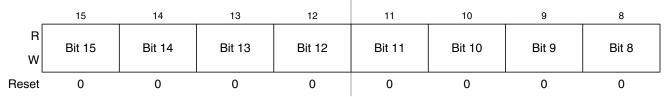

| 0x0026  | DBGCCH          | Read:<br>Write: | Bit 15 | 14     | 13     | 12     | 11    | 10    | 9     | Bit 8 |

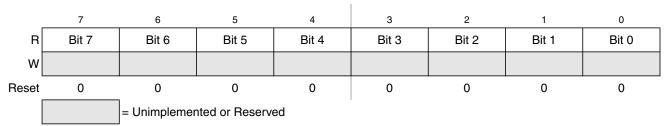

| 0x0027  | DBGCCL          | Read:<br>Write: | Bit 7  | 6      | 5      | 4      | 3     | 2     | 1     | Bit 0 |

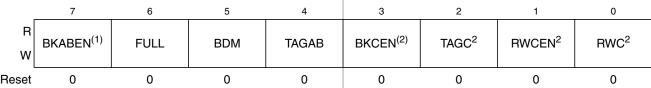

| 0x0028  | DBGC2<br>BKPCT0 | Read:<br>Write: | BKABEN | FULL   | BDM    | TAGAB  | BKCEN | TAGC  | RWCEN | RWC   |

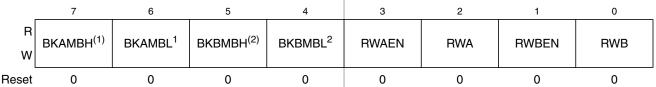

| 0x0029  | DBGC3<br>BKPCT1 | Read:<br>Write: | BKAMBH | BKAMBL | ВКВМВН | BKBMBL | RWAEN | RWA   | RWBEN | RWB   |

| 0x002A  | DBGCAX<br>BKP0X | Read:<br>Write: | PAG    | SEL    |        |        | EXT   | CMP   |       |       |

| 0x002B  | DBGCAH<br>BKP0H | Read:<br>Write: | Bit 15 | 14     | 13     | 12     | 11    | 10    | 9     | Bit 8 |

| 0x002C  | DBGCAL<br>BKP0L | Read:<br>Write: | Bit 7  | 6      | 5      | 4      | 3     | 2     | 1     | Bit 0 |

| 0x002D  | DBGCBX<br>BKP1X | Read:<br>Write: | PAG    | SEL    |        |        | EXT   | CMP   |       |       |

| 0x002E  | DBGCBH<br>BKP1H | Read:<br>Write: | Bit 15 | 14     | 13     | 12     | 11    | 10    | 9     | Bit 8 |

| 0x002F  | DBGCBL<br>BKP1L | Read:<br>Write: | Bit 7  | 6      | 5      | 4      | 3     | 2     | 1     | Bit 0 |

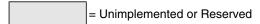

# 0x0030-0x0031 MMC Map 4 of 4 (HCS12 Module Mapping Control)

| Address | Name     |        | Bit 7 | Bit 6 | Bit 5 | Bit 4            | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|--------|-------|-------|-------|------------------|-------|-------|-------|-------|

| 0x0030  | PPAGE    | Read:  | 0     | 0     | PIX5  | PIX4             | PIX3  | PIX2  | PIX1  | PIX0  |

| 0x0030  | FFAGE    | Write: |       |       | FIXS  | Γ1Λ <del>4</del> | FIXS  | ΓIΛΔ  | LIVI  | FIXU  |

| 0x0031  | Reserved | Read:  | 0     | 0     | 0     | 0                | 0     | 0     | 0     | 0     |

| 0x0031  | neserveu | Write: |       |       |       |                  |       |       |       |       |

# 0x0032-0x0033 MEBI Map 3 of 3 (HCS12 Multiplexed External Bus Interface)

| Address | Name                 |                 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------------------|-----------------|-------|-------|-------|-------|-------|-------|-------|-------|

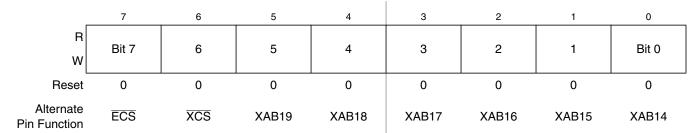

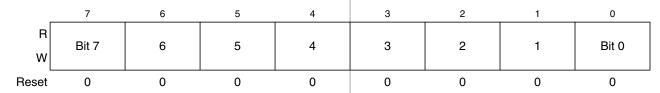

| 0x0032  | PORTK <sup>(1)</sup> | Read:<br>Write: | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0033  | DDRK <sup>1</sup>    | Read:<br>Write: | Bit 7 | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

<sup>1.</sup> Only applicable in special emulation-only bond outs, for emulation of extended memory map.

####

| Address | Name      |        | Bit 7   | Bit 6  | Bit 5  | Bit 4            | Bit 3    | Bit 2  | Bit 1    | Bit 0  |

|---------|-----------|--------|---------|--------|--------|------------------|----------|--------|----------|--------|

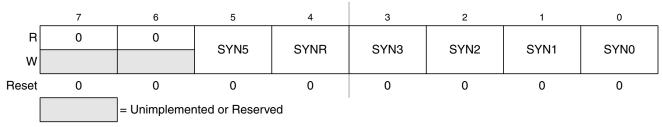

| 0x0034  | SYNR      | Read:  | 0       | 0      | SYN5   | SYN4             | SYN3     | SYN2   | SYN1     | SYN0   |

|         |           | Write: |         |        |        |                  |          |        |          |        |

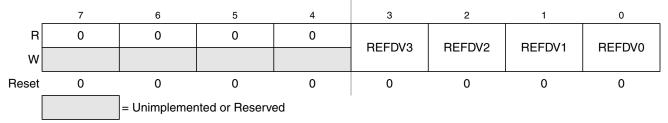

| 0x0035  | REFDV     | Read:  | 0       | 0      | 0      | 0                | REFDV3   | REFDV2 | REFDV1   | REFDV0 |

| one co  |           | Write: |         |        |        |                  |          |        |          |        |

| 0x0036  | CTFLG     | Read:  | TOUT7   | TOUT6  | TOUT5  | TOUT4            | TOUT3    | TOUT2  | TOUT1    | TOUT0  |

| 0,0000  | TEST ONLY | Write: |         |        |        |                  |          |        |          |        |

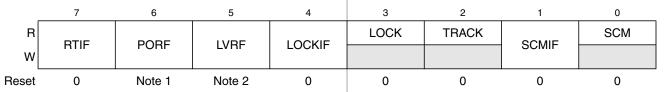

| 0x0037  | CRGFLG    | Read:  | RTIF    | PROF   | 0      | LOCKIF           | LOCK     | TRACK  | SCMIF    | SCM    |

| 0,0007  | Orial La  | Write: | 11111   | 11101  |        |                  |          |        | OOWIII   |        |

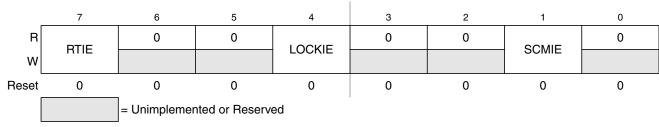

| 0x0038  | CRGINT    | Read:  | RTIE    | 0      | 0      | LOCKIE           | 0        | 0      | SCMIE    | 0      |

| 0,0000  | CHAINT    | Write: | IIIIL   |        |        | LOCKIL           |          |        | SOIVIL   |        |

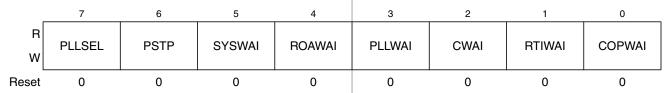

| 0x0039  | CLKSEL    | Read:  | PLLSEL  | PSTP   | SYSWAI | ROAWAI           | PLLWAI   | CWAI   | RTIWAI   | COPWAI |

| 0,0003  | OLNOLL    | Write: | I LLOLL | 1 311  | SISWAI | HOAWAI           | I LLVVAI | CVVAI  | 11110071 | COLWAI |

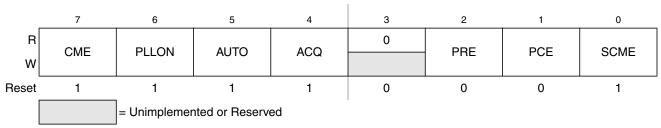

| 0x003A  | PLLCTL    | Read:  | CME     | PLLON  | AUTO   | ACQ              | 0        | PRE    | PCE      | SCME   |

| UXUUSA  | FLLOTL    | Write: | CIVIL   | FLLON  | AUTO   | ACQ              |          | FNE    | FOE      | SCIVIE |

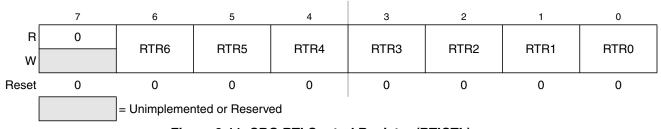

| 0x003B  | RTICTL    | Read:  | 0       | RTR6   | RTR5   | RTR4             | RTR3     | RTR2   | RTR1     | RTR0   |

| UXUUSD  | HIICIL    | Write: |         | חוחט   | כחוח   | nin <del>4</del> | חוחט     | ninz   | nini     | וחוחט  |

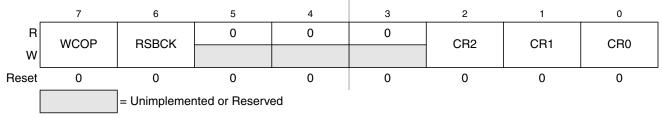

| 0x003C  | COPCTL    | Read:  | WCOP    | RSBCK  | 0      | 0                | 0        | CR2    | CR1      | CR0    |

| UXUUSC  | COPCIL    | Write: | WCOP    | NODUK  |        |                  |          | Unz    | Chi      | Chu    |

| 0000    | FORBYP    | Read:  | DTIDVD  | CODDVD | 0      |                  | 0        | 0      | ECM.     | 0      |

| 0x003D  | TEST ONLY | Write: | RTIBYP  | COPBYP |        | PLLBYP           |          |        | FCM      |        |

| 0000    | CTCTL     | Read:  | TCTL7   | TCTL6  | TCTL5  | TCTL4            | TCLT3    | TCTL2  | TCTL1    | TCTL0  |

| 0x003E  | TEST ONLY | Write: |         |        |        |                  |          |        |          |        |

| 0000    | ADMOOD    | Read:  | 0       | 0      | 0      | 0                | 0        | 0      | 0        | 0      |

| 0x003F  | ARMCOP    | Write: | Bit 7   | 6      | 5      | 4                | 3        | 2      | 1        | Bit 0  |

# 0x0040-0x006F TIM (Sheet 1 of 3)

| Address  | Name       |                 | Bit 7   | Bit 6 | Bit 5  | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|----------|------------|-----------------|---------|-------|--------|-------|-------|-------|-------|-------|

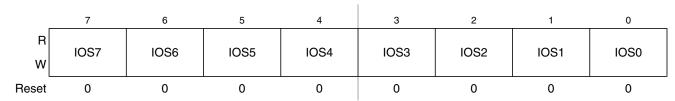

| 0x0040   | TIOS       | Read:<br>Write: | IOS7    | IOS6  | IOS5   | IOS4  | IOS3  | IOS2  | IOS1  | IOS0  |

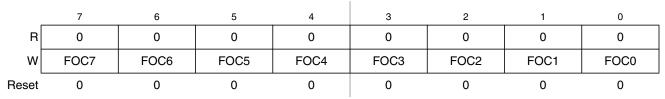

| 0x0041   | CFORC      | Read:           | 0       | 0     | 0      | 0     | 0     | 0     | 0     | 0     |

| 00041    | CFORC      | Write:          | FOC7    | FOC6  | FOC5   | FOC4  | FOC3  | FOC2  | FOC1  | FOC0  |

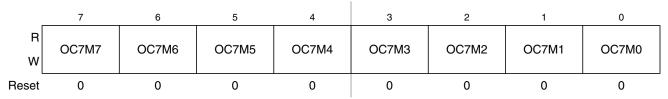

| 0x0042   | OC7M       | Read:<br>Write: | OC7M7   | ОС7М6 | OC7M5  | OC7M4 | ОС7М3 | OC7M2 | OC7M1 | ОС7М0 |

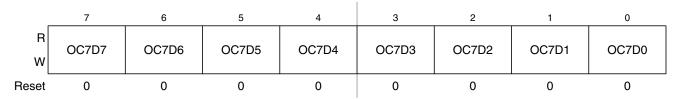

| 0x0043   | OC7D       | Read:<br>Write: | OC7D7   | OC7D6 | OC7D5  | OC7D4 | OC7D3 | OC7D2 | OC7D1 | OC7D0 |

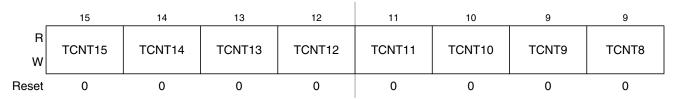

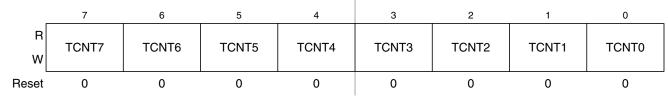

| 0x0044   | TCNT (hi)  | Read:           | Bit 15  | 14    | 13     | 12    | 11    | 10    | 9     | Bit 8 |

| 00044    | TONT (III) | Write:          |         |       |        |       |       |       |       |       |

| 0x0045   | TCNT (lo)  | Read:           | Bit 7   | 6     | 5      | 4     | 3     | 2     | 1     | Bit 0 |

| 0,0043   | 10111 (10) | Write:          |         |       |        |       |       |       |       |       |

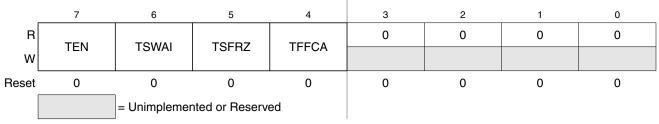

| 0x0046   | TSCR1      | Read:           | TEN     | TSWAI | TSFRZ  | TFFCA | 0     | 0     | 0     | 0     |

| 0,000-10 | 100111     | Write:          | 1 = 1 \ | 1000  | 101112 | 1110/ |       |       |       |       |

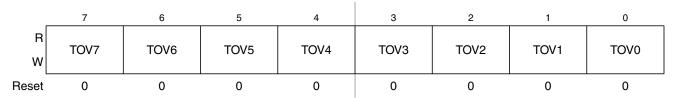

| 0x0047   | TTOV       | Read:<br>Write: | TOV7    | TOV6  | TOV5   | TOV4  | TOV3  | TOV2  | TOV1  | TOV0  |

# 0x0040-0x006F TIM (Sheet 2 of 3)

| Address | Name     |                 | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|----------|-----------------|--------|-------|-------|-------|-------|-------|-------|-------|

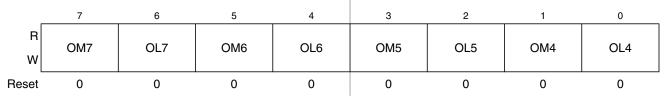

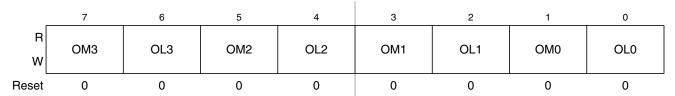

| 0x0048  | TCTL1    | Read:<br>Write: | ОМ7    | OL7   | OM6   | OL6   | OM5   | OL5   | OM4   | OL4   |

| 0x0049  | TCTL2    | Read:<br>Write: | ОМЗ    | OL3   | OM2   | OL2   | OM1   | OL1   | ОМО   | OL0   |

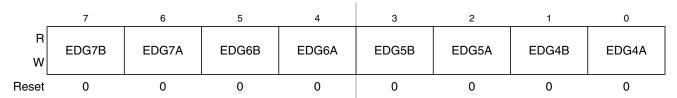

| 0x004A  | TCTL3    | Read:<br>Write: | EDG7B  | EDG7A | EDG6B | EDG6A | EDG5B | EDG5A | EDG4B | EDG4A |

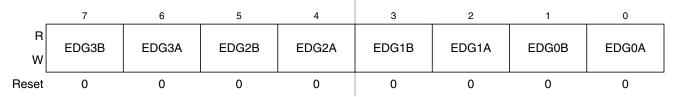

| 0x004B  | TCTL4    | Read:<br>Write: | EDG3B  | EDG3A | EDG2B | EDG2A | EDG1B | EDG1A | EDG0B | EDG0A |

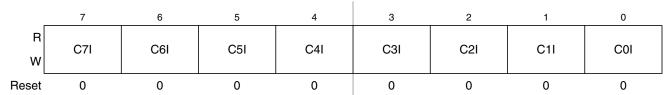

| 0x004C  | TIE      | Read:<br>Write: | C7I    | C6I   | C5I   | C4I   | C3I   | C2I   | C1I   | COI   |

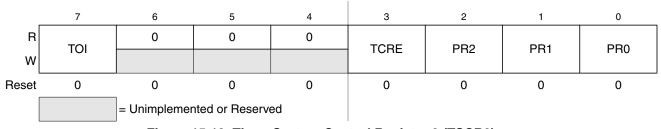

| 0x004D  | TSCR2    | Read:<br>Write: | TOI    | 0     | 0     | 0     | TCRE  | PR2   | PR1   | PR0   |

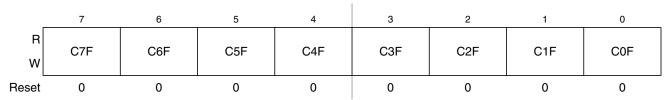

| 0x004E  | TFLG1    | Read:<br>Write: | C7F    | C6F   | C5F   | C4F   | C3F   | C2F   | C1F   | C0F   |

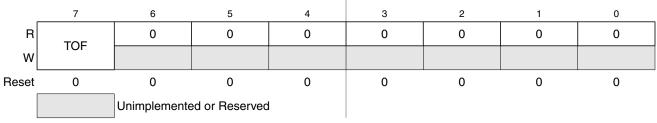

| 0x004F  | TFLG2    | Read:<br>Write: | TOF    | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

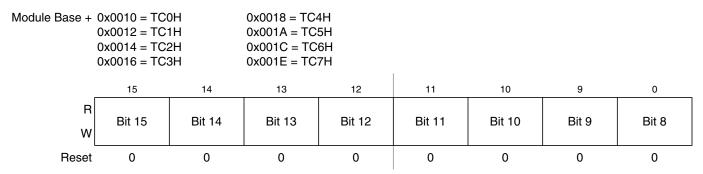

| 0x0050  | TC0 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0051  | TC0 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0052  | TC1 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0053  | TC1 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0054  | TC2 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0055  | TC2 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0056  | TC3 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0057  | TC3 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0058  | TC4 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0059  | TC4 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x005A  | TC5 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x005B  | TC5 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x005C  | TC6 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x005D  | TC6 (lo) | Read:<br>Write: | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x005E  | TC7 (hi) | Read:<br>Write: | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

# 0x0040-0x006F TIM (Sheet 3 of 3)

| Address | Name       |                           | Bit 7  | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|---------|------------|---------------------------|--------|-------|-------|-------|-------|-------|-------|-------|

| 0x005F  | TC7 (lo)   | Read:<br>Write:           | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

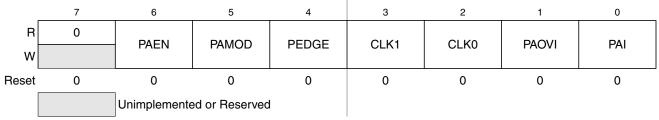

| 0x0060  | PACTL      | Read:<br>Write:           | 0      | PAEN  | PAMOD | PEDGE | CLK1  | CLK0  | PAOVI | PAI   |

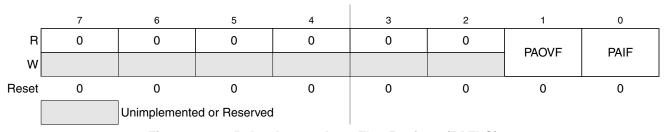

| 0x0061  | PAFLG      | Read:<br>Write:           | 0      | 0     | 0     | 0     | 0     | 0     | PAOVF | PAIF  |

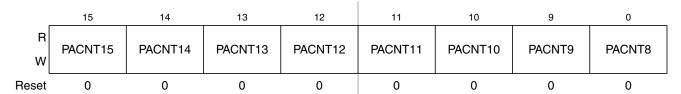

| 0x0062  | PACNT (hi) | Read:<br>Write:           | Bit 15 | 14    | 13    | 12    | 11    | 10    | 9     | Bit 8 |

| 0x0063  | PACNT (Io) | Read:<br>Write:           | Bit 7  | 6     | 5     | 4     | 3     | 2     | 1     | Bit 0 |

| 0x0064  | Reserved   | Read:<br>Write:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| 0x0065  | Reserved   | Read:<br>Write:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

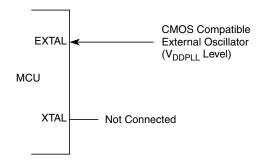

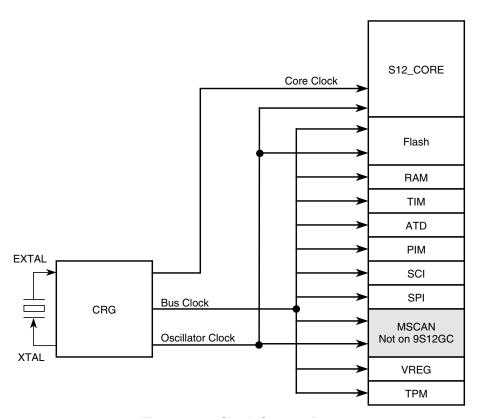

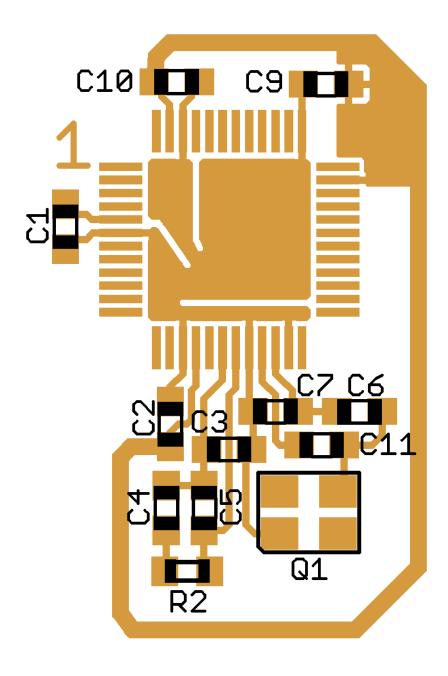

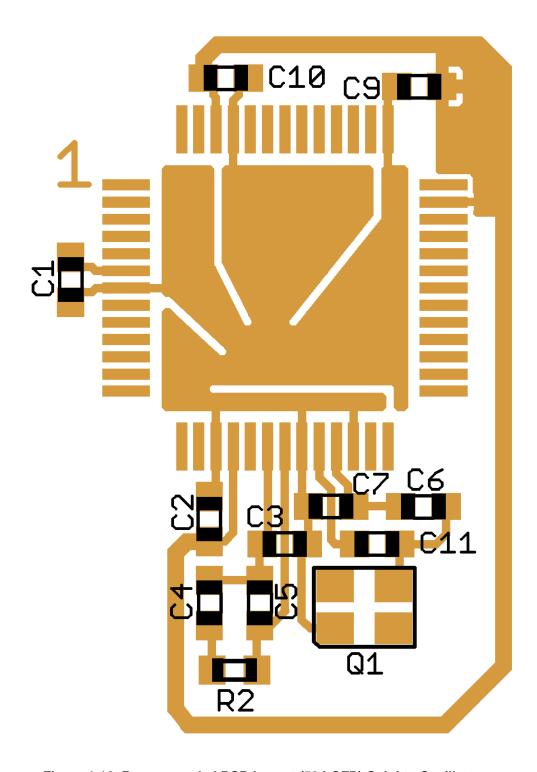

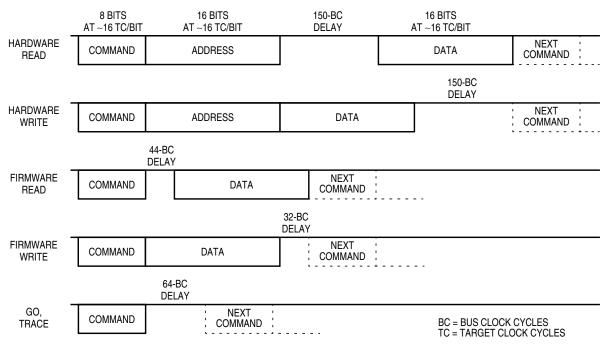

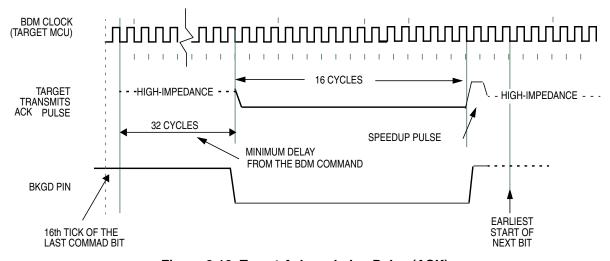

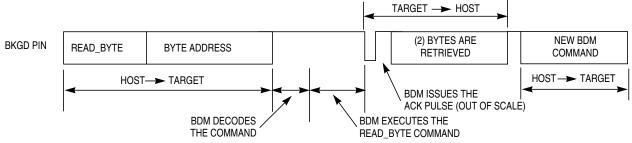

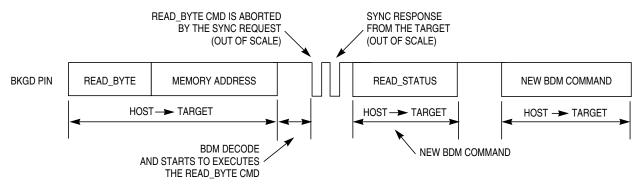

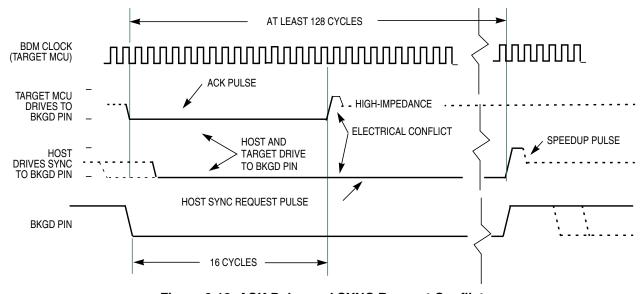

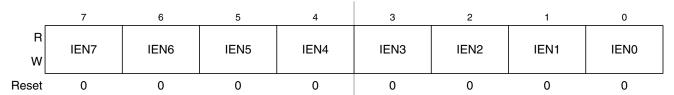

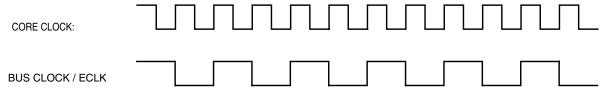

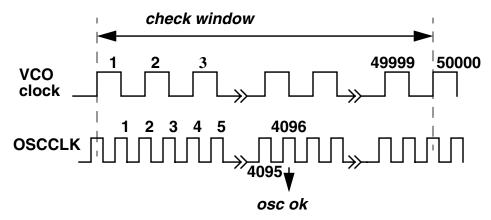

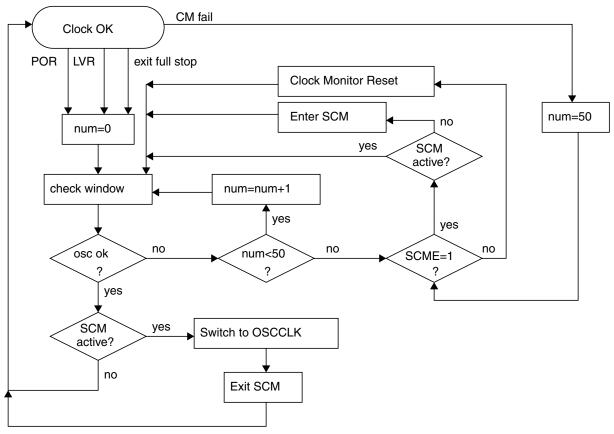

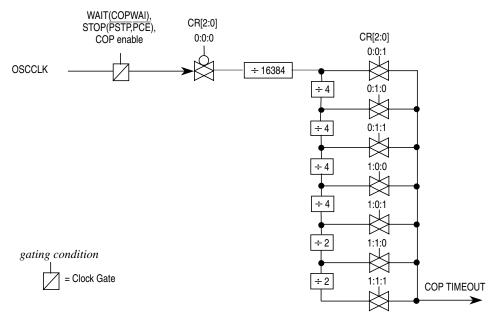

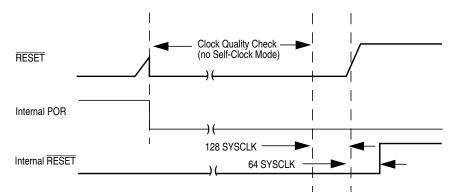

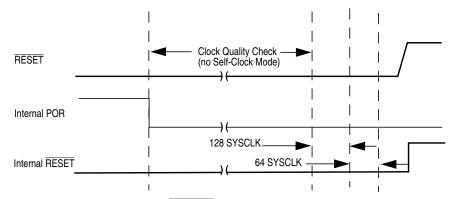

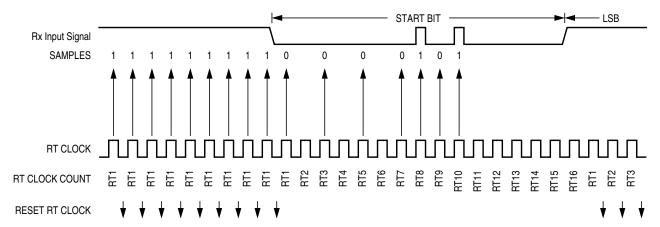

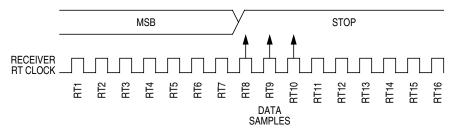

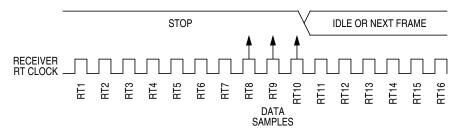

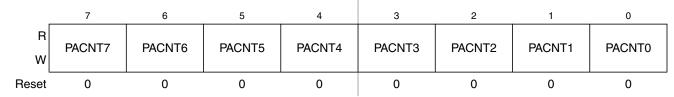

| 0x0066  | Reserved   | Read:<br>Write:           | 0      | 0     | 0     | 0     | 0     | 0     | 0     | 0     |