## **Evaluation Board User Guide UG-042**

One Technology Way • P.O. Box 9106 • Norwood, MA 02062-9106, U.S.A. • Tel: 781.329.4700 • Fax: 781.461.3113 • www.analog.com

## **Evaluating 16-Lead SOIC and 16-Lead QSOP Digital Isolators**

| FEATURES                                                               | SUPPORTED $i$ Coupler MODELS |

|------------------------------------------------------------------------|------------------------------|

| Convenient connections for power through screw                         | ADuM130x                     |

| terminal blocks                                                        | ADuM131x                     |

| Add-on BNC connector for 50 Ω signal sources                           | ADuM140x                     |

| On-board signal routing                                                | ADuM141x                     |

| Support for signal wrap back                                           | ADuM1510                     |

| Simple signal paths to reduce transmission line effects                | ADuM240x                     |

| Pull-up and pull-down provided for control lines                       | ADuM330x                     |

| Support for iso Power                                                  | ADuM340x                     |

| Project area that supports surface-mount and                           | ADuM344x                     |

| through-hole devices                                                   | ADuM440x                     |

| GENERAL DESCRIPTION                                                    | ADuM5000                     |

|                                                                        | ADuM520x                     |

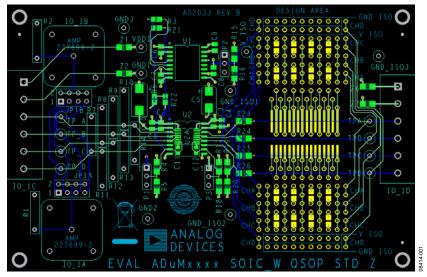

| The EVAL-ADuMQSEBZ can be used with most <i>i</i> Coupler <sup>®</sup> | ADuM540x                     |

| isolation products in the 16-lead, wide-body SOIC and QSOP             | ADuM6000                     |

| packages. The evaluation board supports the common pad                 | ADuM620x                     |

| positions for power, ground, and I/O pins found in nearly all of       | ADuM640x                     |

| the <i>i</i> Coupler products and is a configurable board that can be  | ADuM744x                     |

| adapted to many <i>i</i> Coupler products.                             | ADuM7510                     |

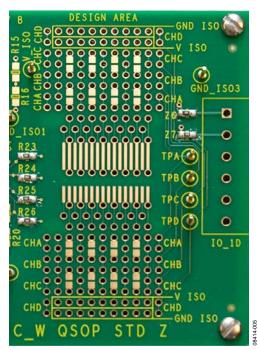

#### **EVALUATION BOARD**

Figure 1.

## **UG-042**

## **Evaluation Board User Guide**

## **TABLE OF CONTENTS**

| REVISION HISTORY          |   |

|---------------------------|---|

| Pad Layout for the DUT    | 3 |

| Evaluation Board Hardware |   |

| Revision History          | 2 |

| Evaluation Board          | 1 |

| Supported iCoupler models | 1 |

| General Description       | 1 |

| Features                  | 1 |

| Terminals                              |  |

|----------------------------------------|--|

| Data I/O Connections                   |  |

| Design Area                            |  |

| Evaluation Board Schematics and Layout |  |

| Ordering Information                   |  |

| ·                                      |  |

| 12/10—Rev. 0 to Rev. A                               |

|------------------------------------------------------|

| Changes to Supported <i>i</i> Coupler Models Section |

| 1/10—Revision 0: Initial Version                     |

# EVALUATION BOARD HARDWARE PAD LAYOUT FOR THE DUT

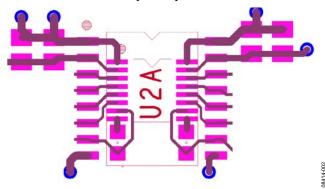

The evaluation board has a pad layout in U2 that accommodates 16-lead, wide-body SOIC devices, as well as QSOP miniature packages, as shown in Figure 2. Power and ground connections connect to capacitor pads for Side 1 and Side 2.

Figure 2. DUT Pad Layout Component U2

Three low inductance, surface-mount bypass capacitors are provided for each side. A 100 nF capacitor is installed on each side in Capacitor C2 and Capacitor C3. Additional bypass capacitors required for QSOP packages are below the QSOP pads and within the pad layout of the SOIC package. They cannot be installed if the SOIC is used.

In addition, there are 10  $\mu F$  ceramic X7R capacitors, C1 on Side 1 and C4 on Side 2, that provide high frequency bypassing and ripple reduction. For further ripple reduction in <code>isoPower\*</code> devices like the ADuM540x, tantalum capacitors are added to C10 as a 68  $\mu F$  value on Side 1 and to C5 as a 22  $\mu F$  value on Side 2. These large value ceramic and tantalum bypass capacitors are not necessary for non-<code>isoPower</code> devices.

Many of the *i*Coupler devices have configuration pins that allow outputs to be disabled or default levels to be set. These pins are usually located at Pin 7 and Pin 10 in the wide-body package. Pullup 0  $\Omega$  resistors on SM Pad R4 and SM Pad R17 are provided to pull these pins high. These pull-up resistors can be removed, and pull-down resistors can be installed on R5 and R18.

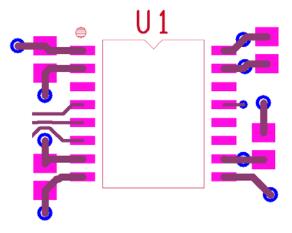

In addition to the U2 DUT space, an additional pad layout is provided at U1, specifically to accommodate an ADuM5000 *iso*Power device, as shown in Figure 3. This is a power supply only device that can be used to provide secondary power for any *i*Coupler in standalone mode or as a slave to boost power to the ADuM520x or ADuM540x devices. The surface-mount resistor pads that are used to control these functions are not populated.

An ADuM5000 is not installed at Position U1; it is left to the user to obtain and install this device if required. As shown in Figure 3, the power and ground connections for this device are different from the rest of the iCoupler components. The C6 to C9 pad positions for bypass capacitors are provided but not populated (0.1  $\mu$ F X7R ceramic capacitors are recommended).

Pull-up, pull-down, and connecting resistor pads are provided (but not populated) to connect the ADuM5000 in master or slave mode, as well as to set the output voltage. See the ADuM5000 data sheet for descriptions of the pin functions.

Figure 3. ADuM5000 Pad Layout Component U1

#### **Grounding Scheme**

The board consists of two separate ground and power systems. Each side of the DUT can be operated from an independent power and ground reference. This allows simulation of conditions similar to the target application. The board provides for board creepage and clearance typical of most 2.5 kV circuit boards. It is not recommended for use above 2.5 kV rms transient voltages or for isolation voltage testing above 2500 V rms.

#### **EMI and EMC Measurements**

The signal path has been made as simple as possible while still providing flexibility. The board is not intended for detailed characterization of system noise, EMI, or EMC. It may be useful for initial bench work in these areas, but Analog Devices, Inc., does not guarantee that board results will be indicative of the final system performance in these areas. The board includes some of the structures discussed in the AN-0971 Application Note for radiated EMI mitigation.

#### **TERMINALS**

### **Side 1 Power Supply Inputs**

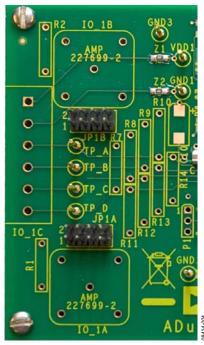

Power is supplied to the board via a set of terminal block connectors labeled IO\_1C, as shown in Figure 4. Power is connected to the Pin 1 top terminal, and ground is connected to the Pin 2 top terminal. Provisions for adding in-line inductors for noise isolation have been made with the inclusion of Z1 and Z2, which are 1206 size surface-mount components. These positions are populated with 0  $\Omega$  resistors to connect power to the board. If ferrite inductors are required for noise control, these components should be removed and replaced with appropriate inductors.

Figure 4. Side 1 Terminal Block Connector

The power and ground from the screw terminal block (if installed) are connected to the Side 1 power and ground pads of the DUT and provide power and ground to pull-up and pull-down resistors and terminations.

The ADuM640x devices differ from the rest of the *iso* Power devices in that they have an additional power supply input on Pin 7. This replaces the RC<sub>OUT</sub> pin present on the ADuM5401, ADuM5402, ADuM5403, and ADuM5404. This pin must be bypassed and connected to VDD1 for proper operation of the ADuM640x. It is recommended that a 0.1  $\mu$ F capacitor be installed at R5 and a 0 W resistor at R4. The ADuM640x devices are not compatible with power sharing; therefore, an ADuM5000 should not be installed at U1 when using the ADuM640x.

#### **Side 2 Power Supply Connections**

The Side 2 connections are different from those on Side 1. With standard *i*Coupler devices, these connections are power supply inputs for Side 2. However, with *iso*Power devices such as the ADuM540x, these same connections can be power outputs for off-board circuits. In addition, they can be configured as an independent power supply for the project area.

Figure 5. Side 2 Terminal Block Connector

Power is connected to the terminal block connector (if installed) labeled IO\_1D, as shown in Figure 5. Power is connected to IO\_1D Pin 1 at the top, and ground is connected to Pin 2. Provisions for adding in-line inductors for noise isolation or for isolating the jacks from the on-board power connections have been made with the inclusion of Z6 and Z7. These positions are populated with 0  $\Omega$  resistors to connect power from the ADuM540x to the IO\_1D terminal block.

When standard *i*Coupler isolators are installed, the Z6 and Z7 pads should be populated with 0  $\Omega$  resistors to connect the power jacks to the power pins of the DUT. Replace these resistors with inductors if noise isolation is required.

When *iso* Power devices are installed on the board, the power configuration required can vary greatly, depending on the demands of the application. With 0  $\Omega$  resistors or inductors installed at Z6 and Z7, the power jacks can provide power from the *iso* Power device to an external device.

#### **DATA I/O CONNECTIONS**

#### Side 1 Data I/O

Signals can be provided to the board and routed to the required input pins through the IO\_1C terminal block connector, as shown in Figure 4. Four channel inputs/outputs can be connected from IO\_1C Pin 3 through IO\_1C Pin 6 to the respective A, B, C, and D channels of the ADuM540x.

Signals from the IO\_1C terminal block connector channels can also be routed to some of the other data lines through the JP1A and JP1B jumper blocks (these jumper blocks correspond to BNC Channel A and Channel B, if you populate them). Each jumper block allows a channel signal from the IO\_1C terminal block to be connected to additional data input lines by configuring the jumpers. The jumper blocks can also be used to wrap signals from an *i*Coupler output back to an input by using the JP1A or JP1B block to cross-connect inputs and outputs.

A common way to provide signals is with a function generator through 50  $\Omega$  coax cables. The ADuM540x board has a layout position at IO\_1A and IO\_1B for adding two BNC connectors, but these are not provided with the board. You can purchase the coax cables (Tyco AMP 227699-2) and populate these BNC connectors. In addition, to have 50  $\Omega$  terminations on the board for the added BNC connectors, a 50  $\Omega$  through-hole resistor should be added at the R1 and R2 positions. It is possible to route data outputs to this connector as well, but it is not recommended because proper termination is not possible for logic level signals, and improper termination can cause severe ringing on the output lines.

The Side 1 I/O structure also includes pull-up/pull-down/load positions, R7 through R14. Discrete through-hole resistors and capacitors can be installed at these positions to simulate most loading conditions or to provide pull-ups for open collector outputs.

#### Side 2 Data I/O

Signals can be provided to the board and routed to the required input pins through the  $IO_1D$  terminal block connector, as shown in Figure 5. It consists of terminal block connections that operate like the Side 1 structures. The terminal block connections can also be used to wrap signals from an iCoupler output back to an input.

In addition to the off-board I/O connections, each data channel is provided with through-hole connections to the design area.

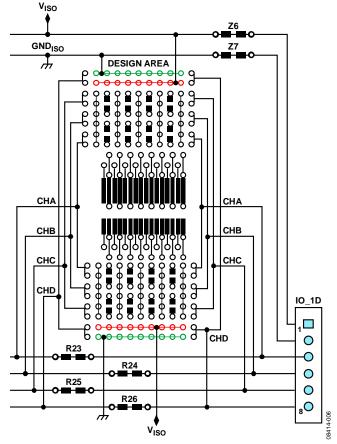

#### **DESIGN AREA**

The design area of the evaluation board is provided to allow breadboarding of application components such as RS-485 and CAN transceivers, ADC or DAC components with direct interconnects. The design area, as shown in Figure 6, accepts most surface-mount narrow- and wide-body components with 50 mil and 100 mil pitch, as well as narrow- and wide-body 300 mil DIP through-hole devices. These surface-mount discrete components and jumper wires can be used to complete a wide variety of circuits.

The design area has convenient connection points to the primary data path, CHA to CHD, of the *i*Coupler, as well as power connections for  $V_{\rm ISO}$  and  $GND_{\rm ISO}$ . To allow signals from the design area to be routed to the IO\_1D terminal block, remove the 0  $\Omega$  resistors for R23 through R26. Note that no ground plane is provided in the design area.

Figure 6. Design Area

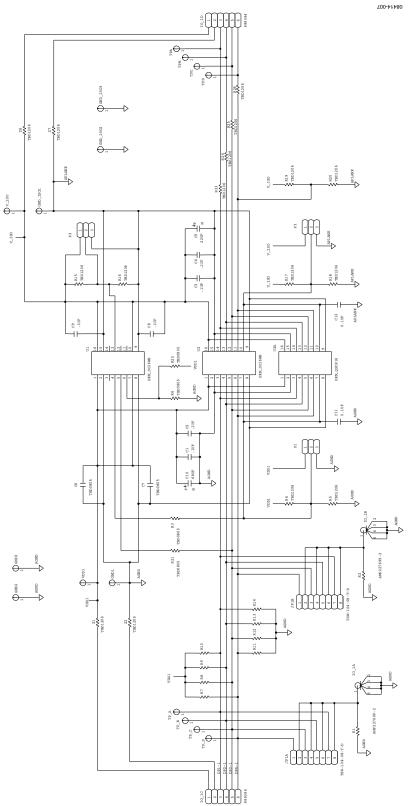

## **EVALUATION BOARD SCHEMATICS AND LAYOUT**

Figure 7. Schematic of ADuM540x Evaluation Board

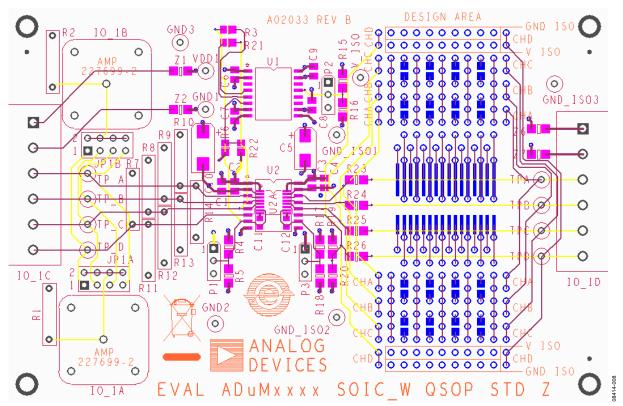

Figure 8. Evaluation Board Layout

## ORDERING INFORMATION

#### **BILL OF MATERIALS**

#### Table 1.

| Qty | Reference Designator                                                                                                      | Description                                     | Supplier/Part Number      |

|-----|---------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------|---------------------------|

| 2   | IO_1C, IO_1D                                                                                                              | CONN-PCB terminal; not populated                | Weidmuller/999394         |

| 0   | U1                                                                                                                        | ADuM5000; not populated                         | N/A                       |

| 0   | U2                                                                                                                        | Supported iCoupler models SO16WB; not populated | N/A                       |

| 1   | C10                                                                                                                       | CAP TANT chip 68 μF; not populated              | KEMET/T495X686K020AS      |

| 1   | C5                                                                                                                        | CAP TANT chip 22 μF; not populated              | AVX/TAJC226K020R          |

| 2   | C1, C4                                                                                                                    | CAP CER X5R 10 μF; not populated                | Panasonic/ECJ-2FB0J106M   |

| 2   | C2, C3                                                                                                                    | CAP CER X7R 0.1 μF                              | Murata/GRM21BR71E104KA01L |

| 0   | C6 to C9, C11, C12                                                                                                        | CAP CER SMD 0805; not populated                 | N/A                       |

| 0   | IO_1A, IO_1B                                                                                                              | CONN-PCB coax BNC; not populated                | Tyco AMP/227699-2         |

| 2   | JP1A, JP1B                                                                                                                | CONN-PCB header, 8-pin double row               | SAMTEC/TSW-104-08-T-D     |

| 17  | TP_A, TP_B, TP_C, TP_D, TPA, TPB,<br>TPC, TPD, GND3, GND2, GND1,<br>GND_ISO, GND_ISO1, GND_ISO2,<br>GND_ISO3, VDD1, V_ISO | Test points                                     | VECTOR/K24A/M             |

| 2   | P1, P2                                                                                                                    | Jumper                                          | FCI/65474-001LF           |

| 0   | R3 to R6, R21, R22                                                                                                        | RES chip SMD 0805; not populated                | N/A                       |

| 6   | R17, R23 to R26                                                                                                           | RES chip SMD 0805; 0 Ω                          | Panasonic/ERJ-6GEY0R00V   |

| 4   | Z1, Z2, Z6, Z7                                                                                                            | RES chip SMD 0805; 0 Ω                          | Panasonic/ERJ-6GEY0R00V   |

| 0   | R15, R16, R18 to R20                                                                                                      | RES chip SMD 0805; not populated                | N/A                       |

| 0   | R1, R2, R7 to R14                                                                                                         | RES SPACER_400; not populated                   | N/A                       |

#### ESD Caution

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

#### Legal Terms and Conditions

By using the evaluation board discussed herein (together with any tools, components documentation or support materials, the "Evaluation Board"), you are agreeing to be bound by the terms and conditions set forth below ("Agreement") unless you have purchased the Evaluation Board, in which case the Analog Devices Standard Terms and Conditions of Sale shall govern. Do not use the Evaluation Board until you have read and agreed to the Agreement. Your use of the Evaluation Board shall signify your acceptance of the Agreement. This Agreement is made by and between you ("Customer") and Analog Devices, Inc. ("ADI"), with its principal place of business at One Technology Way, Norwood, MA 02062, USA. Subject to the terms and conditions of the Agreement, ADI hereby grants to Customer a free, limited, personal, temporary, non-exclusive, non-sublicensable, non-transferable license to use the Evaluation Board FOR EVALUATION PURPOSES ONLY. Customer understands and agrees that the Evaluation Board is provided for the sole and exclusive purpose referenced above, and agrees not to use the Evaluation Board for any other purpose. Furthermore, the license granted is expressly made subject to the following additional limitations: Customer shall not (i) rent, lease, display, sell, transfer, assign, sublicense, or distribute the Evaluation Board; and (ii) permit any Third Party to access the Evaluation Board. As used herein, the term "Third Party" includes any entity other than ADI, Customer, their employees, affiliates and in-house consultants. The Evaluation Board is NOT sold to Customer, all rights not expressly granted herein, including ownership of the Evaluation Board, are reserved by ADI. CONFIDENTIALITY. This Agreement and the Evaluation Board shall all be considered the confidential and proprietary information of ADI. Customer may not disclose or transfer any portion of the Evaluation Board to any other party for any reason. Upon discontinuation of use of the Evaluation Board or termination of this Agreement, Customer agrees to promptly return the Evaluation Board to ADI. ADDITIONAL RESTRICTIONS. Customer may not disassemble, decompile or reverse engineer chips on the Evaluation Board. Customer shall inform ADI of any occurred damages or any modifications or alterations it makes to the Evaluation Board, including but not limited to soldering or any other activity that affects the material content of the Evaluation Board. Modifications to the Evaluation Board must comply with applicable law, including but not limited to the ROHS Directive. TERMINATION. ADI may terminate this Agreement at any time upon giving written notice to Customer. Customer agrees to return to ADI the Evaluation Board at that time. LIMITATION OF LIABILITY. THE EVALUATION BOARD PROVIDED HEREUNDER IS PROVIDED "AS IS" AND ADI MAKES NO WARRANTIES OR REPRESENTATIONS OF ANY KIND WITH RESPECT TO IT. ADI SPECIFICALLY DISCLAIMS ANY REPRESENTATIONS, ENDORSEMENTS, GUARANTEES, OR WARRANTIES, EXPRESS OR IMPLIED, RELATED TO THE EVALUATION BOARD INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, TITLE, FITNESS FOR A PARTICULAR PURPOSE OR NONINFRINGEMENT OF INTELLECTUAL PROPERTY RIGHTS. IN NO EVENT WILL ADI AND ITS LICENSORS BE LIABLE FOR ANY INCIDENTAL. SPECIAL, INDIRECT, OR CONSEQUENTIAL DAMAGES RESULTING FROM CUSTOMER'S POSSESSION OR USE OF THE EVALUATION BOARD, INCLUDING BUT NOT LIMITED TO LOST PROFITS, DELAY COSTS, LABOR COSTS OR LOSS OF GOODWILL. ADI'S TOTAL LIABILITY FROM ANY AND ALL CAUSES SHALL BE LIMITED TO THE AMOUNT OF ONE HUNDRED US DOLLARS (\$100.00). EXPORT. Customer agrees that it will not directly or indirectly export the Evaluation Board to another country, and that it will comply with all applicable United States federal laws and regulations relating to exports. GOVERNING LAW. This Agreement shall be governed by and construed in accordance with the substantive laws of the Commonwealth of Massachusetts (excluding conflict of law rules). Any legal action regarding this Agreement will be heard in the state or federal courts having jurisdiction in Suffolk County, Massachusetts, and Customer hereby submits to the personal jurisdiction and venue of such courts. The United Nations Convention on Contracts for the International Sale of Goods shall not apply to this Agreement and is expressly disclaimed.

©2010 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners.

UG08414-0-12/10(A)

www.analog.com