## ADUC7128 EVALUATION BOARD REFERENCE GUIDE

# MICROCONVERTER® ADUC7128 DEVELOPMENT SYSTEM

## **ADuC7128 Evaluation Board Reference Guide**

## **CONTENTS:**

### **Evaluation Board Reference Guide:**

| 1) | Evaluation Board Overview |

|----|---------------------------|

| 2) | Evaluation Board Features |

| 3) | DIP Switch link Options   |

| 4) | External Connectors       |

| 5) | Demonstration Circuit     |

| 6) | Parts List                |

## **ADuC7128 Evaluation Board Reference Guide**

1) Evaluation Board Overview

#### (1) EVALUATION BOARD OVERVIEW

The ADuC7128 Evaluation board has the following features:

- 2 Layer PCB (4" X 5" Form Factor)

- 9V power supply regulated to 3.3V on board

- 4 pin UART header to connect to RS232 Interface Cable

- 20-pin standard JTAG connector to connect to JTAG emulator

- Demonstration Circuit

- 32.768kHz Watch Crystal to drive the PLL clock

- ADR291 2.5V External Reference Chip

- Reset/Download/IRQ0 Push Buttons

- Power Indicator/General Purpose LEDs

- Access to all ADC inputs and DAC output from external header. All device Ports are brought out to external header pins.

- Surface mount and through hole general purpose prototype area

#### THIS DOCUMENT REFERS TO THE MICROCONVERTER ADUC7128 EVAL BOARD REV 0

#### Notes:

- 1. All references in this document to physical orientation of components on the board are made with respect to a component side view of the board with the prototype area appearing in the bottom of the board.

- 2. The board is laid out to minimize coupling between the analog and digital sections of the board. To this end the analog section on the left hand side and digital section on the right hand side of the board. The regulated 3.3V power supply is routed directly to the digital section and is filtered before being routed into the analog section of the board. Note: There is one ground plane for both digital and analog components.

(2) Evaluation Board Features

## (2) EVALUATION BOARD FEATURES

#### **Power Supply:**

The user should connect the 9V power supply via the 2.1mm input power socket (J5). The input connector is configured as 'CENTER NEGATIVE' i.e. GND on the center pin and +9V on the outer shield.

This 9V supply is regulated via a linear voltage regulator (U5). The 3.3V regulator output is used to drive the digital side of the board directly. The 3.3V supply is also filtered and then used to supply the analog side of the board.

When on, the LED (D3) indicates that a valid 3.3V supply is being driven from the regulator circuit. All active components are decoupled with 0.1uF at device supply pins to ground.

#### **RS232 Interface:**

The ADuC7128 (U1) P1.1 and P1.0 lines are connected to the RS232 Interface Cable via connector (J1). The Interface Cable generates the required level shifting to allow direct connection to a PC serial port. Ensure that the cable supplied is connected to the board correctly i.e. DVDD is connected to DVDD and DGND is connected to DGND.

#### **Emulation Interface:**

Non-intrusive emulation and download are possible on the ADuC7128 via JTAG by connecting a JTAG emulator to the J4 connector.

#### **Crystal Circuit:**

The board is fitted with a 32.768kHz crystal, from which the on-chip PLL circuit can generate a 41.78MHz clock.

#### External Reference (ADR291)

The external 2.5V reference chip (U2) has two functions. It is provided on the evaluation board to demonstrate the external reference option of the ADuC7128 but its main purpose is to generate the  $V_{OCM}$  voltage of the differential amplifier if required.

#### Reset/Download/IRQ0 Push Buttons:

A RESET push button is provided to allow the user to manually reset the part. When inserted the RESET pin of the ADuC7128 will be pulled to DGND. Because the RESET pin on the ADuC7128 is Schmidt triggered internally there is no need to use an external Schmidt trigger on this pin.

When inserted the IRQ0 push button switch drives P0.4/IRQ0 high. This can be used to initiate an external interrupt 0.

(2) Evaluation Board Features

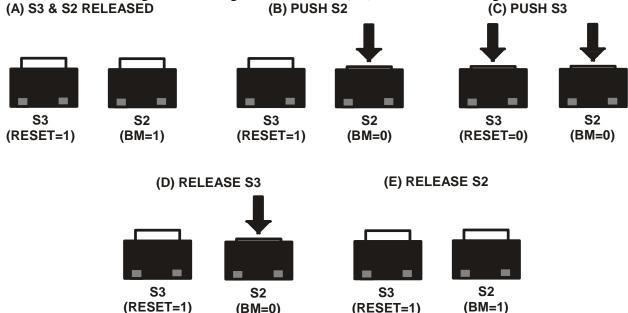

To enter serial download mode the user must pull the P0.0/BM pin low while reset is toggled. On the evaluation board serial download mode can be easily initiated by holding down the serial download push button (S2) while inserting and releasing the reset button (S3) as illustrated in Figure 1.

Figure 1: Entering Serial Download Mode on the Evaluation Board.

#### Power Indicator/General Purpose LEDs:

A power LED (D3) is used to indicate that a sufficient supply is available on the board. A general purpose LED (D2) is directly connected to P4.2 of the ADuC7128. When P4.2 is cleared the LED will be turned ON and when P4.2 is set the LED will be turned off.

#### **Analog I/O Connections:**

All analog I/O are brought out on header J3.

ADC0 and ADC1 are buffered using a AD8606 to evaluate single-ended and pseudo differential mode. A potentiometer can be connected to ADC0 buffered.

ADC3 and ADC4 can be buffered with a single-ended to differential op-amp on board, the AD8132 used to evaluate the ADC in fully differential mode.

ADC2 is not buffered. Be sure to follow the datasheet recommendation when connecting signals to this input.

TheDAC can be used to controlled the brightness of the green LED D1, when connected via the S1 switch.

#### General Purpose prototype area

General Purpose prototype areas are provided at the bottom of the evaluation board for adding external components as required in the users application. As can be seen from the layout  $AV_{DD}$ , AGND,  $V_{DDIO}$  and DGND tracks are provided in this prototype area.

(3) Link Options

## (3) DIP SWITCH LINK OPTIONS

#### **S1-1 VREF**

Function: Connects the output of the 2.5V external reference (ADR291) to the VREF pin of the

ADuC7128.

**Use:** *Slide S1-1 to the ON position* to connect the external reference to the ADuC7128.

Slide S1-1 to the OFF position to use the internal 2.5V reference or a different external

reference on VREF pin of J3 header.

#### S1-2 $V_{OCM}$

Function: Connects 1.67V to the V<sub>OCM</sub> pin of the AD8132. No extra DC voltage is required on the

board to use the ADC in differential mode.

Use: Slide S1-2 to the ON position to connect V<sub>OCM</sub> of the differential amplifier to 1.67V, divided

output of the ADR291 reference.

*Slide S1-2 to the OFF position* to use a different voltage for  $V_{OCM}$  by connecting a DC voltage to the  $V_{OCM}$  pin of J3 header. Note that  $V_{OCM}$  value is dependant on reference value as

shown in Table 1:

| $V_{REF}$ | V <sub>OCM</sub> min | V <sub>OCM</sub> max |

|-----------|----------------------|----------------------|

| 2.5V      | 1.25V                | 2.05V                |

| 2.048V    | 1.024V               | 2.276V               |

| 1.25V     | 0.75V                | 2.55V                |

Table 1: V<sub>OCM</sub> range

#### **S1-3 POT**

Function: Connects the potentiometer output to ADC0. This input is buffered by an AD8606. This is for

demonstration purposes.

Use: Slide S1-3 to the ON position to connect the potentiometer to the op-amp of ADC0 input

channel.

*Slide S1-3 to the OFF position* to use ADC0 input on J3 header.

#### **S1-4 ADC3**

**Function:** Brings out ADC3 (pin #1) on J3 header.

**Use:** Slide S1-6 to the ON Position to connect directly ADC3 of J3 header to ADC3 pin (pin #1) of

the ADuC7128.

Slide S1-6 to the OFF Position to disconnect ADC3 of J3 header from ADC3 pin (pin #1) of

the ADuC7128.

#### ADuC7128 Evaluation Board Reference Guide

(3) Link Options

#### **S1-5 VIN-**

Function: Connects -OUT of the single-ended to differential op-amp (AD8132) to ADC3. S1-5 and S1-

6 must be used together, when VIN- is in the ON position, VIN+ must also be in the ON

position to use the differential op-amp on channel ADC3 and ADC4.

**Use:** *Slide S1-5 to the ON Position* to connect –OUT of the AD8132 to ADC3.

*Slide S1-5 to the OFF Position* to use ADC3 without the AD8132.

#### S1-6 VIN+

Function: Connects +OUT of the single-ended to differential op-amp (AD8132) to ADC4. When VIN+

is in the ON position, VIN- must also be in the ON position to use the differential op-amp on

channel ADC3 and ADC4.

**Use:** *Slide S1-6 to the ON Position* to connect +OUT of AD8132 to ADC4.

*Slide S1-6 to the OFF Position* to use ADC4 without the AD8132.

#### **S1-7 ADC4**

Use: Slide S1-6 to the ON Position to connect directly ADC4 of J3 header to ADC4 pin (pin #2) of

the ADuC7128.

Slide S1-6 to the OFF Position to disconnect ADC4 of J3 header from ADC4 pin (pin #2) of

the ADuC7128.

#### **S1-8 LED**

**Function:** Connects the DAC output to the green LED of the demo circuit, D1.

**Use:** *Slide S1-7 to the ON position* to connect the DAC1 output to D1.

*Slide s1-7 to the OFF position* to use DAC1 output on J3 header.

(4) External Junctions (Connectors)

## (4) EXTERNAL CONNECTORS:

#### J3 Analog I/O Connector

The analog I/O connector J3 provides external connections for all ADC inputs, reference inputs and DAC outputs. The pinout of the connector is shown below in Table 2.

| Pin#  | Pin Description             |

|-------|-----------------------------|

| J3-1  | $\mathrm{AV}_{\mathrm{DD}}$ |

| J3-2  | AGND                        |

| J3-3  | $ m V_{REF}$                |

| J3-4  | ADC0                        |

| J3-5  | ADC1                        |

| J3-6  | ADC2                        |

| J3-7  | ADC3                        |

| J3-8  | ADC4                        |

| J3-9  | ADC5                        |

| J3-10 | ADC9                        |

| J3-11 | ADC10                       |

| J3-12 | ADC12                       |

| J3-13 | ADC13                       |

| J3-14 | $ m V_{DIFF}$               |

| J3-15 | $ m V_{OCM}$                |

| J3-16 | VDAC                        |

| J3-17 | ADCNEG                      |

| J3-18 | AGND                        |

Table 2: Pin functions for Analog I/O connector J3

#### **J5 Power Supply Connections**

J5 allows for the connection between the evaluation board and the 9V power supply provided in the ADuC7128 Development System.

#### **J4 Emulation Connector**

J4 provides a connection of the evaluation board to the PC via a USB cable and mIdas Link provided in the ADuC7128 Development System.

#### J1 Serial Interface Connector

J1 provides a simple connection of the evaluation board to the PC via a PC serial port cable provided with the ADuC7128 Development System.

(4) External Junctions (Connectors)

#### J2 Digital I/O Connector

The digital I/O connector J2 provides external connections for all GPIOs. The pinout of the connector is shown below in Table 3.

| Pin#  | Pin Description |

|-------|-----------------|

| J2-1  | DGND            |

| J2-2  | P4.6            |

| J2-3  | P4.7            |

| J2-4  | P0.0            |

| J2-5  | P0.6            |

| J2-6  | P3.0            |

| J2-7  | P3.1            |

| J2-8  | P3.2            |

| J2-9  | P3.3            |

| J2-10 | P0.3            |

| J2-11 | P3.4            |

| J2-12 | P3.5            |

| J2-13 | P0.4            |

| J2-14 | P0.5            |

| J2-15 | P2.0 |

|-------|------|

| J2-16 | P0.7 |

| J2-17 | P1.7 |

| J2-18 | P1.6 |

| J2-19 | P4.0 |

| J2-20 | P4.1 |

| J2-21 | P1.5 |

| J2-22 | P1.4 |

| J2-23 | P1.3 |

| J2-24 | P1.2 |

| J2-25 | P1.1 |

| J2-26 | P1.0 |

| J2-27 | P4.2 |

| J2-28 | P4.3 |

| J2-29 | P4.4 |

| J2-30 | P4.5 |

Table 3: Pin functions for digital I/O connector J2

5) Demonstration Circuit

## (5) POTENTIOMETER DEMONSTRATION CIRCUIT

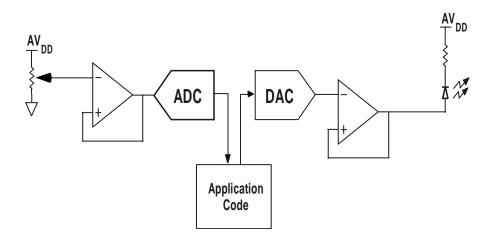

Figure 2: Circuit diagram of the RTD Circuit

Using the sample code in \code\adc\pot.c the variation in the potentiometer resistance can be seen on the output LED.

Note that the internal and external reference are 2.5V, which gives an ADC input range of 0V to 2.5V in single-ended mode. The potentiometer can give a voltage between 0V and  $AV_{DD} = 3.3V$ .

## (6) ADUC7128 EVALUATION BOARD PARTS LIST

Please refer to ADuC7128.xls for part numbers.