# **GS2965 Multi-Rate SDI Reclocker with Equalization & De-emphasis**

#### Features

- SMPTE 424M, SMPTE 292M and SMPTE 259M-C compliant

- Supports DVB-ASI at 270Mb/s

- Single supply operation at 3.3V or 2.5V

- 180mW typical power consumption (213mW with RCO enabled) at 2.5V

- Input signal equalization and output-signal de-emphasis settings to compensate for board-trace dielectric losses

- 2:1 input multiplexer patented technology

- Choice of dual reclocked data outputs or one reclocked data

output and one clock output

- Uses standard 27MHz crystal

- Differential inputs and outputs

- support DC coupling to industry-standard differential logic

- on-chip 100  $\Omega$  differential data input/output termination

- selectable 400mVppd or 800mVppd output swing on each output

- seamless interface to other Gennum products

- 4 wire SPI host interface for device configuration and monitoring

- Standard logic control and status signal levels

- Auto and Manual modes for rate selection

- Standards indication in Auto mode

- Lock Detect Output

- Mute, Bypass and Autobypass functions

- SD/HD indication output to control GS2978 or GS2988 dual slew-rate cable drivers

- Operating temperature range: -40°C to +85°C

- 32 pin 5mm x 5mm QFN package

- Pb-free and RoHS compliant

## Applications

• SMPTE 424M, SMPTE 292M and SMPTE 259M-C coaxial cable serial digital interfaces

#### Description

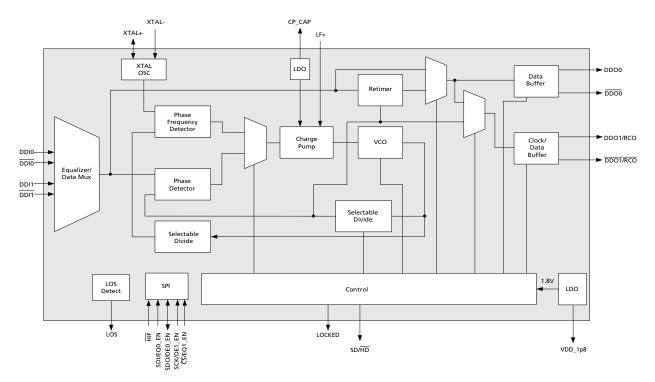

The GS2965 is a multi-rate serial digital reclocker designed to automatically recover the embedded clock from a digital video signal and retime the incoming video data. It will recover the embedded clock signal and retime the data from a SMPTE 424M, SMPTE 292M, or SMPTE 259M-C compliant digital video signal.

A serial host interface provides the ability to configure and monitor multiple GS2965 devices in a daisy-chain configuration.

Adjustable input trace equalization (EQ) for up to 40" of FR4 trace losses, and adjustable output de-emphasis (DE) for up to 20" of FR4 trace losses, can be configured via the host interface.

The GS2965 can operate in either auto or manual rate selection mode. In Auto mode, the device will automatically detect and lock onto incoming SMPTE SDI data signals at any supported rate. For single rate data systems, the GS2965 can be configured to operate in Manual mode. In both modes, the device requires only one external crystal to set the VCO frequency when not locked and provides adjustment free operation.

The GS2965 accepts industry-standard differential input levels including LVPECL and CML. The differential data and clock outputs feature selectable output swing via the host interface, ensuring compatibility with most industry-standard, terminated differential receivers.

The GS2965 features dual differential outputs. The second output can be configured to emit either the recovered clock signal or the re-timed video data. This output can also be disabled to save power.

In systems which require passing of non-SMPTE data rates, the GS2965 can be configured to either automatically or manually enter a bypass mode in order to pass the signal without reclocking.

The GS2965 is Pb-free, and the encapsulation compound does not contain halogenated flame retardant. This component and all homogeneous sub-components are RoHS compliant.

#### **GS2965** Functional Block Diagram

### **Revision History**

| Version | ECR    | PCN | Date              | Changes and/or Modifications                                                                                                                                                             |

|---------|--------|-----|-------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | 153705 | -   | March 2010        | Converted to Data Sheet. Updated<br>Power numbers in Table 2-1: DC<br>Electrical Characteristics. Added Table<br>4-5: Suggested LOS Threshold Settings.                                  |

| 0       | 152589 | -   | September<br>2009 | Converted to Preliminary Data Sheet.<br>Updates to Electrical Characteristics.<br>Updates to Section 4.15 Host Interface.                                                                |

| С       | 151996 | -   | July 2009         | Added Section 4.15 Host Interface.<br>Updated Power numbers in Table 2-1:<br>DC Electrical Characteristics and Loop<br>Bandwidth numbers in Table 2-2: AC<br>Electrical Characteristics. |

|         |        |     |                   | Added Table 1-2: GS2965 Default<br>Start-up Settings and Figure 4-2:<br>De-emphasis Waveform.                                                                                            |

| В       | 151955 | -   | May 2009          | Changed 6.1 Package Dimensions, 6.2<br>Recommended PCB Footprint.                                                                                                                        |

| А       | 151772 | _   | April 2009        | New document.                                                                                                                                                                            |

# Contents

| Features                                              | 1 |

|-------------------------------------------------------|---|

| Applications                                          | 1 |

| Description                                           | 1 |

| Revision History                                      | 2 |

| 1. Pin Out                                            | 5 |

| 1.1 Pin Assignment                                    | 5 |

| 1.2 Pin Descriptions                                  | 6 |

| 1.3 Default Start-up Settings                         | 8 |

| 2. Electrical Characteristics                         | 9 |

| 2.1 Absolute Maximum Ratings                          | 9 |

| 2.2 DC Electrical Characteristics                     | 9 |

| 2.3 AC Electrical Characteristics                     |   |

| 3. Input/Output Circuits                              |   |

| 4. Detailed Description                               |   |

| 4.1 Serial Data Input                                 |   |

| 4.2 Modes of Operation                                |   |

| 4.3 Input Trace Equalization                          |   |

| 4.4 2:1 Input Mux                                     |   |

| 4.5 Crystal Buffer                                    |   |

| 4.6 LOS (Loss Of Signal) Detection                    |   |

| 4.7 Serial Digital Reclocker                          |   |

| 4.8 Lock Detection                                    |   |

| 4.8.1 Lock Detect and Asynchronous Lock               |   |

| 4.9 Serial Data Output                                |   |

| 4.9.1 Output Signal Interface Levels                  |   |

| 4.9.2 Adjustable Output Swing                         |   |

| 4.9.3 Output De-emphasis                              |   |

| 4.10 Automatic and Manual Data Rate Selection         |   |

| 4.11 SD/HD Indication                                 |   |

| 4.12 Bypass Mode                                      |   |

| 4.13 DVB-ASI                                          |   |

| 4.14 Output Mute and Data/Clock Output Selection      |   |

| 4.15 Host Interface                                   |   |

| 4.15.1 Introduction                                   |   |

| 4.15.2 Legacy Mode & Start-up                         |   |

| 4.15.3 Host Interface Mode & Start-up                 |   |

| 4.15.4 Clock & Data Timing                            |   |

| 4.15.5 Single Device Operation                        |   |

| 4.15.6 Write Operation - Single Device                |   |

| 4.15.7 Read Operation - Single Device                 |   |

| 4.15.8 Daisy Chain Operation                          |   |

| 4.15.9 Read & Write Operation - Daisy Chained Devices |   |

| 4.15.10 Writing to all Devices                        |   |

GS2965 Multi-Rate SDI Reclocker with Equalization & De-emphasis Data Sheet 52462 - 1 March 2010

3 of 41

| 4.15.11 Writing to a Single Device in the Chain   |    |

|---------------------------------------------------|----|

| 4.15.12 Reading from all Devices                  |    |

| 4.15.13 Reading from a Single Device in the Chain |    |

| 4.15.14 Host Register Map                         | 33 |

| 4.16 Device Power Up                              |    |

| 4.17 Standby                                      |    |

| 5. Typical Application Circuit                    | 37 |

| 6. Package and Ordering Information               | 38 |

| 6.1 Package Dimensions                            | 38 |

| 6.2 Recommended PCB Footprint                     | 38 |

| 6.3 Packaging Data                                | 39 |

| 6.4 Marking Diagram                               | 39 |

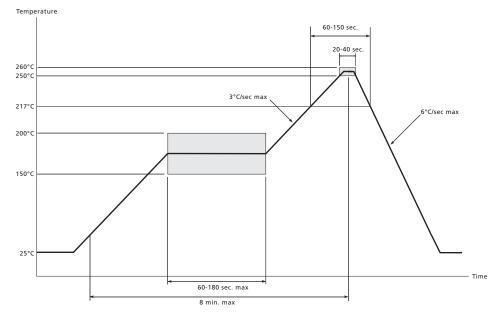

| 6.5 Solder Reflow Profile                         | 40 |

| 6.6 Ordering Information                          | 41 |

# 1. Pin Out

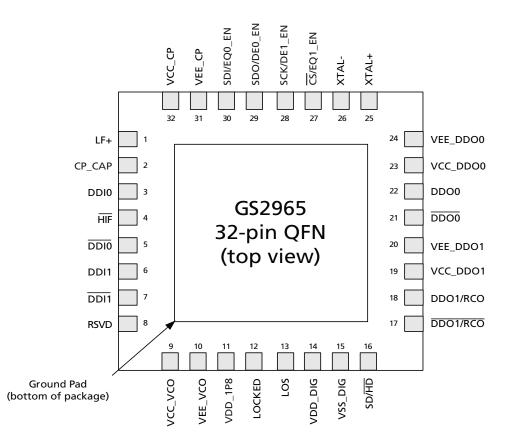

# **1.1 Pin Assignment**

Figure 1-1: GS2965 Pin Out

# **1.2 Pin Descriptions**

#### Table 1-1: GS2965 Pin Descriptions

| Pin Number | Name                  | Туре        | Description                                                                                                                                                      |

|------------|-----------------------|-------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | LF+                   | Passive     | Loop Filter capacitor connection. (CLF = 47nF). Connect as shown in Typica<br>Application Circuit on page 37.                                                    |

| 2          | CP_CAP                | Power       | External capacitor for internal LDO regulator supplying the charge pump circuit.                                                                                 |

| 3, 5       | DDI0, DDI0            | Input       | Serial Digital Differential Input 0.                                                                                                                             |

| 4          | HIF                   | Logic Input | Host interface selection pin. Active-low input. See Section 4.15.1.                                                                                              |

| 6, 7       | DDI1, DDI1            | Input       | Serial Digital Differential Input 1.                                                                                                                             |

| 8          | RSVD                  | Reserved    | Reserved pin. Do not connect to this pin.                                                                                                                        |

| 9          | VCC_VCO               | Power       | Most positive power supply connection for the internal VCO section. Connect to a 3.3V supply with a $422\Omega$ resistor, or a 2.5V supply with a 267W resistor. |

| 10         | VEE_VCO               | Power       | Most negative power supply connection for the internal VCO section. Connect to GND.                                                                              |

| 11         | VDD_1P8               | Power       | External capacitor for internal 1.8V digital supply.                                                                                                             |

| 12         | LOCKED                | Output      | Lock Detect status signal. HIGH when the PLL is locked.                                                                                                          |

| 13         | LOS                   | Output      | Loss Of Signal status. HIGH when the input signal is invalid.                                                                                                    |

| 14         | VDD_DIG               | Power       | Most positive power supply connection for the digital core.<br>Connect to 3.3V or 2.5V.                                                                          |

| 15         | VSS_DIG               | Power       | Most negative power supply for the digital core.<br>Connect to GND.                                                                                              |

| 16         | SD/HD                 | Output      | This signal will be LOW for all rates other than 270Mb/s.<br>This signal is HIGH for 270Mb/s.                                                                    |

| 17, 18     | DDO1/RCO,<br>DDO1/RCO | Output      | Differential serial clock or data outputs.                                                                                                                       |

| 19         | VCC_DDO1              | Power       | Most positive power supply connection for the DDO1/DDO1 output driver<br>Connect to 3.3V or 2.5V.                                                                |

| 20         | VEE_DDO1              | Power       | Most negative power supply connection for the DDO1/DDO1 output driver. Connect to GND.                                                                           |

| 21, 22     | DD00, DD00            | Output      | Differential Serial Digital Outputs.                                                                                                                             |

| 23         | VCC_DDO0              | Power       | Most positive power supply connection for the DDO0/DDO0 output drive Connect to 3.3V or 2.5V.                                                                    |

| 24         | VEE_DDO0              | Power       | Most negative power supply connection for the DDO0/DDO0 output driver.                                                                                           |

|            |                       |             | Connect to GND.                                                                                                                                                  |

| Pin Number | Name       | Туре                                                        | Description                                                                                  |

|------------|------------|-------------------------------------------------------------|----------------------------------------------------------------------------------------------|

| 26         | XTAL-      | Input                                                       | Reference crystal input.                                                                     |

| 27         | CS/EQ1_EN  | Input/Logic                                                 | In host mode (HIF set LOW):                                                                  |

|            |            | Input                                                       | Chip select input for SPI serial host interface. Active-low input.                           |

|            |            |                                                             | In non-host mode (HIF set HIGH):                                                             |

|            |            |                                                             | Trace equalization on/off pin for Serial Digital Differential Input 1.<br>Active-high input. |

| 28         | SCK/DE1_EN | Input/Logic                                                 | In host mode (HIF set LOW):                                                                  |

|            |            | Input                                                       | Burst-mode clock input for SPI serial host interface.                                        |

|            |            |                                                             | In non-host mode (HIF set HIGH):                                                             |

|            |            |                                                             | De-emphasis on/off pin for Serial Digital Differential Output 1. Active-high input.          |

| 29         | SDO/DE0_EN | Input/Logic                                                 | In host mode (HIF set LOW):                                                                  |

|            |            | Input Serial digital data output for SPI serial host interf | Serial digital data output for SPI serial host interface. Active-high output.                |

|            |            |                                                             | In non-host mode (HIF set HIGH):                                                             |

|            |            |                                                             | De-emphasis on/off pin for Serial Digital Differential Output 0. Active-high<br>input.       |

| 30         | SDI/EQ0_EN | Input/Logic                                                 | In host mode (HIF set LOW):                                                                  |

|            |            | Input                                                       | Serial digital data input for SPI serial host interface. Active-high input.                  |

|            |            |                                                             | In non-host mode (HIF set HIGH):                                                             |

|            |            |                                                             | Trace equalization on/off pin for Serial Digital Differential Input 0.<br>Active-high input. |

| 31         | VEE_CP     | Power                                                       | Most negative power supply connection for the internal                                       |

|            |            |                                                             | charge pump. Connect to GND.                                                                 |

| 32         | VCC_CP     | Power                                                       | Most positive power supply connection for the internal charge pump.                          |

|            |            |                                                             | Connect to 3.3V or 2.5V                                                                      |

| _          | Center Pad |                                                             | Ground pad on bottom of package. Connect to GND.                                             |

### Table 1-1: GS2965 Pin Descriptions (Continued)

# **1.3 Default Start-up Settings**

The GS2965 has some functions that are not accessible via direct pin control, and are only accessible through the host interface registers. These functions have an internal pull-up or pull-down resistor that sets the default logic level or start-up state, if it is not already set by a pin.

If the user wishes to override these logic levels, the associated bit should be programmed within the PIN\_OR\_1 register (pin override register) at address 0x0C. The logic values within the PIN\_OR\_1 register become active when the user sets the Pin Override Enable bit to HIGH within that same register.

Table 1-2 shows:

- 1. The default logic state set by the internal pull up or pull down resistors.

- 2. The default values within the Pin Override register upon reset.

More details are given in Section 4.15.

| Name         | Description                                                                                                                                              | Default State set by<br>Internal Resistors | Default State within<br>the Pin Override<br>Register |

|--------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------|------------------------------------------------------|

| DDI_SEL[0:1] | Selects one of two serial digital input signals for processing. DDI0 is selected by default.                                                             | 0:0                                        | 0:0                                                  |

| BYPASS       | Bypasses the reclocker stage when set HIGH.                                                                                                              | 0                                          | 0                                                    |

| AUTOBYPASS   | When set HIGH, this bit automatically bypasses the reclocker stage when the PLL is not locked to a supported rate.                                       | 0                                          | 0                                                    |

| AUTO/MAN     | When set HIGH, the standard is automatically detected from the input data rate.                                                                          | 1                                          | 0                                                    |

| SSO, SS1     | When AUTO/MAN is set HIGH, SS[1:0] are outputs<br>displaying the data rate to which the PLL has locked.<br>Therefore, they will not have default values. | None                                       | 0:0                                                  |

| KBB          | Controls the loop bandwidth of the PLL.                                                                                                                  | Floating                                   | Ground                                               |

| DATA_MUTE    | Mutes the DDO0/DDO0 and DDO1/DDO1 (if data is selected) outputs when LOW.                                                                                | 1                                          | 0                                                    |

| DDO1_DISABLE | Disables the DDO1/RCO and $\overline{\text{DDO1}/\text{RCO}}$ outputs when LOW.                                                                          | 0                                          | 0                                                    |

| DATA/CLOCK   | HIGH = DATA<br>LOW = CLOCK                                                                                                                               | 0                                          | 0                                                    |

#### Table 1-2: GS2965 Default Start-up Settings

# 2. Electrical Characteristics

# 2.1 Absolute Maximum Ratings

| Parameter                   | Value                               |  |  |

|-----------------------------|-------------------------------------|--|--|

| Supply Voltage              | -0.5 to +3.6V <sub>DC</sub>         |  |  |

| Input ESD Voltage           | 4kV                                 |  |  |

| Storage Temperature Range   | -50°C < T <sub>A</sub> < 125°C      |  |  |

| Operating Temperature Range | -40°C to 85°C                       |  |  |

| Input Voltage Range         | -0.3 to (VCC + 0.3) V <sub>DC</sub> |  |  |

| Solder Reflow Temperature   | 260°C                               |  |  |

# 2.2 DC Electrical Characteristics

#### **Table 2-1: DC Electrical Characteristics**

| Parameter                         | Symbol | Conditions    | Min   | Тур                  | Max   | Units |

|-----------------------------------|--------|---------------|-------|----------------------|-------|-------|

| Supply Voltage                    | VDD    | 3.3V          | 3.135 | 3.3                  | 3.465 | V     |

|                                   |        | 2.5V          | 2.375 | 2.5                  | 2.625 | V     |

| Power (DDO1/RCO disabled, minimum | Р      | VDD = 3.3V    | -     | 250                  | 325   | mW    |

| output swing)                     |        | VDD = 2.5V    | -     | 180                  | 235   | mW    |

| Power (DDO1/RCO enabled, minimum  | _      | VDD = 3.3V    | -     | 290                  | 390   | mW    |

| output swing)                     |        | VDD = 2.5V    | -     | 210                  | 275   | mW    |

| Power in Power-down mode          | _      | VDD = 3.3V    | -     | 48                   | 60    | mW    |

|                                   |        | VDD = 2.5V    |       | 30                   | 40    | mW    |

| Serial Input Termination          | -      | Differential  | 80    | 100                  | 120   | Ω     |

| Serial Output Termination         | -      | Differential  | 80    | 100                  | 120   | Ω     |

| Serial Input Common Mode Voltage  | -      | _             | 1.6   | _                    | VDD   | V     |

| Serial Output Common Mode Voltage | _      | _             | -     | VCC-<br>(∆VOD<br>/2) | _     | V     |

| VIL (2.5V operation)              | _      | VOUT≤VOL, max | -0.3  | -                    | 0.7   | V     |

| VIL (3.3V operation)              | _      | VOUT≤VOL, max | -0.3  | -                    | 0.8   | V     |

| Parameter                       | Symbol | Conditions                   | Min         | Тур   | Max         | Units |

|---------------------------------|--------|------------------------------|-------------|-------|-------------|-------|

| VIH (2.5V operation)            | _      | VOUT≥VOH, min                | 1.7         | -     | VDD<br>+0.3 | V     |

| VIH (3.3V operation)            | _      | VOUT≥VOH, min                | 2           | -     | VDD<br>+0.3 | V     |

| lin                             | _      | VIN = 0V or VIN = VDD        | _           | +/-10 | +/-20       | μA    |

| VOL (2.5V operation)            | _      | VDD = min, IOL = $100\mu A$  | _           | -     | 0.4         | V     |

| VOL (3.3V operation)            | -      | VDD = min, IOL = 100µA       | _           | -     | 0.4         | V     |

| VOH (2.5V operation)            | -      | VDD = min, IOH = $-100\mu$ A | 2.1         | -     | -           | V     |

| VOH (3.3V operation)            | _      | VDD = min, IOH = -100µA      | VDD<br>-0.4 | -     | _           | V     |

| Hysteresis Voltage (SPI inputs) | _      | 2.5V operation               | _           | 350   | _           | mV    |

| NOTE: guaranteed by simulation. |        | 3.3V operation               | _           | 350   | -           | mV    |

# **2.3 AC Electrical Characteristics**

#### **Table 2-2: AC Electrical Characteristics**

| Parameter                                  | Symbol            | Conditions                                                                          | Min    | Тур | Max                     | Units              | Notes |

|--------------------------------------------|-------------------|-------------------------------------------------------------------------------------|--------|-----|-------------------------|--------------------|-------|

| Serial Input Data Rate<br>(for reclocking) | DR <sub>SDO</sub> | -                                                                                   | 0.27   | -   | 2.97                    | Gb/s               | _     |

| Serial Input Data Rate<br>(bypass)         |                   | -                                                                                   | DC     | -   | 2.97                    | Gb/s               | _     |

| SPI Operating Speed                        | _                 | _                                                                                   | _      | _   | 10                      | MHz                | _     |

| Input Voltage Swing                        | ∆VSDI             | Set ATTEN_EN = 1 for<br>\Delta VSDI>1V <sub>pp</sub>                                | 100    |     | 2000                    | mV <sub>p-pd</sub> | _     |

| Output Voltage Swing                       | ΔVOD              | default                                                                             | 300    | 400 | 500                     | mV <sub>p-pd</sub> | -     |

|                                            |                   | see DRIVER_1 register<br>(0x01) addresses 8 & 9 in<br>4.15.14 Host Register<br>Map. | 600    | 800 | 1000                    | mV <sub>p-pd</sub> | -     |

| Input Trace Equalization                   | -                 | LOW                                                                                 | Recom  |     | setting for<br>s of FR4 | 0 to 10            | _     |

|                                            |                   | MED                                                                                 | Recom  |     | etting for<br>s of FR4  | 10 to 20           | _     |

|                                            |                   | HIGH                                                                                | Recomm |     | tting for ><br>FR4      | 20 inches          | -     |

| Parameter                                     | Symbol                           | Conditions                             | Min | Тур   | Max | Units | Notes |

|-----------------------------------------------|----------------------------------|----------------------------------------|-----|-------|-----|-------|-------|

| Output De-Emphasis                            | _                                | OFF - 0                                | -   | 0     | -   | dB    | _     |

|                                               |                                  | ON - 0                                 | -   | 0     | -   | dB    | _     |

|                                               |                                  | ON - 1                                 | -   | 0.7   | _   | dB    | -     |

|                                               |                                  | ON - 2                                 | _   | 1.3   | -   | dB    | _     |

|                                               |                                  | ON - 3                                 | _   | 2     | -   | dB    | _     |

|                                               |                                  | ON - 4                                 | -   | 2.6   | _   | dB    | -     |

|                                               |                                  | ON - 5                                 | -   | 3.3   | -   | dB    | _     |

|                                               |                                  | ON - 6                                 | -   | 4     | _   | dB    | -     |

|                                               |                                  | ON - 7                                 | -   | 4.7   | _   | dB    | -     |

| Input Jitter Tolerance                        | _                                | square-wave modulated<br>jitter        | 0.8 | -     | -   | UI    | -     |

| Loop Bandwidth                                | BW <sub>LOOP</sub>               | KBB = VCC                              | -   | 170   | _   | kHz   | -     |

|                                               | (270Mb/s)                        | KBB = FLOAT                            | -   | 340   | -   | kHz   | -     |

|                                               |                                  | KBB = GND                              | -   | 680   | -   | kHz   | -     |

|                                               | BW <sub>LOOP</sub><br>(1485Mb/s) | KBB = VCC                              | -   | 0.875 | -   | MHz   | -     |

|                                               |                                  | KBB = FLOAT                            | -   | 1.75  | -   | MHz   | -     |

|                                               |                                  | KBB = GND                              | -   | 3.5   | -   | MHz   | -     |

|                                               | BW <sub>LOOP</sub><br>(2970Mb/s) | KBB = VCC                              | -   | 1.75  | -   | MHz   | -     |

|                                               |                                  | KBB = FLOAT                            | -   | 3.5   | _   | MHz   | -     |

|                                               |                                  | KBB = GND                              | -   | 7.0   | -   | MHz   | -     |

| PLL Lock Time (asynchronous)                  | t <sub>alock</sub>               | -                                      | -   | 0.5   | 1   | ms    | -     |

| PLL Lock Time (synchronous)                   | t <sub>slock</sub>               | CLF = 47nF, SD/HD = 0                  | -   | 0.5   | 4   | μs    | -     |

|                                               |                                  | CLF = 47nF, SD/HD = 1                  | -   | 5     | 10  | μs    | _     |

| Serial Data Output Jitter Intrinsic<br>(DDO0) | t <sub>OJ(270MB/s)</sub>         | KBB = FLOAT<br>PRN 2^23-1 test pattern | -   | 0.01  | -   | UI    | -     |

|                                               | t <sub>OJ(1485MB/s)</sub>        | KBB = FLOAT<br>PRN 2^23-1 test pattern | -   | 0.03  | -   | UI    | -     |

|                                               | t <sub>OJ(2970MB/s)</sub>        | KBB = FLOAT<br>PRN 2^23-1 test pattern | -   | 0.05  | -   | UI    | _     |

| Output Rise/Fall Time                         | tr/f                             | 20% to 80% (400mV<br>swing)            | -   | 65    | -   | ps    | _     |

|                                               |                                  | 20% to 80% (800mV<br>swing)            | -   | 80    | -   | ps    | -     |

| Output Rise/Fall Time Mismatch                | _                                | -                                      | _   | _     | 15  | ps    | _     |

| Parameter                    | Symbol | Conditions                        | Min | Тур | Max | Units             | Notes |

|------------------------------|--------|-----------------------------------|-----|-----|-----|-------------------|-------|

| Eye Cross Shift              | _      | percentage of signal<br>amplitude | _   | -   | 5   | %                 | _     |

| Power Supply Noise Rejection | -      | 50 - 100Hz                        | _   | 100 | _   | mV <sub>p-p</sub> | -     |

|                              |        | 100Hz - 10MHz                     | _   | 40  | _   | mV <sub>p-p</sub> | -     |

|                              |        | 10MHz - 1.485GHz                  | _   | 10  | _   | mV <sub>p-p</sub> | _     |

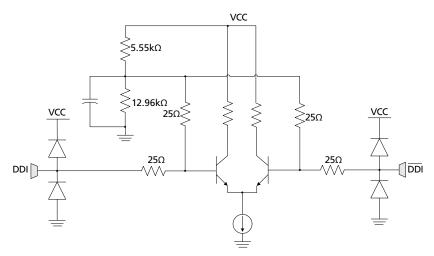

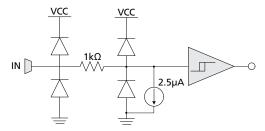

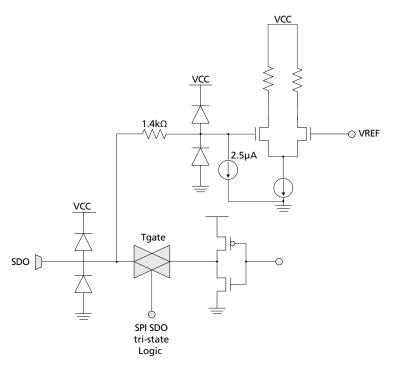

# 3. Input/Output Circuits

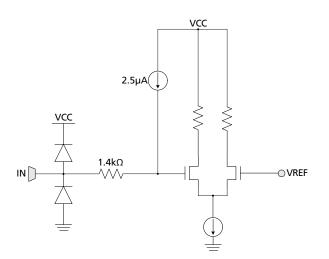

Figure 3-1: High-speed Inputs (DDI0, DDI0, DDI1, DDI1)

Figure 3-2: Low-speed Input with weak internal pull-up (HIF)

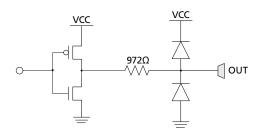

Figure 3-3: Low-speed Outputs (LOCKED, LOS, SD/HD)

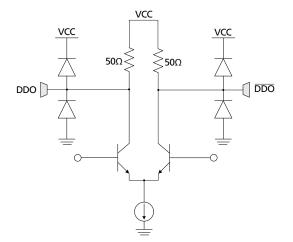

Figure 3-4: High-speed Outputs (DDO1/RCO, DDO1/RCO, DDO0)

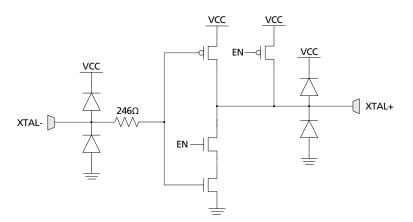

Figure 3-5: High-speed Crystal Oscillator I/O (XTAL-, XTAL+)

Figure 3-6: SPI Inputs, EQ/De-Emphasis Control (CS/EQ1\_EN, SCK/DE1\_EN, SDI/EQ0\_EN)

Figure 3-7: SPI Output, De-Emphasis Control (SDO/DE0\_EN)

# 4. Detailed Description

The GS2965 is a multi-standard reclocker for serial digital SDTV signals operating at 270Mb/s, and HDTV signals operating at 1.485Gb/s, 1.485/1.001Gb/s, 2.97Gb/s and 2.97/1.001Gb/s.

# 4.1 Serial Data Input

The GS2965 features two differential input buffers.

The serial data input signal is connected to the DDI0/DDI0 and DDI1/DDI1 input pins of the device.

Input signals can be single-ended or differential, DC or AC-coupled.

The input circuit is self-biasing, to allow for simple AC or DC-coupling of input signals to the device.

The serial digital data inputs are also compatible when DC-coupled with LVPECL or CML differential outputs from crosspoint switches which operate from 3.3V or 2.5V supplies. This includes but is not limited to: GS2974A, GS2974B, and GS2984 equalizers.

# 4.2 Modes of Operation

The GS2965 has two modes of operation: Legacy Mode ( $\overline{\text{HIF}}$  = HIGH) and SPI Mode ( $\overline{\text{HIF}}$  = LOW).

In Legacy Mode, chip functions are controlled via pins only, and offers limited control of input equalization.

In SPI mode, access is gained to extended digital controls like: Bypass, Autobypass, Auto/Manual selection, Control status inputs or outputs, changes to KBB settings, additional EQ and DE settings as well as access to additional features such as LOS adjustment, polarity invert, auto-mute, etc.

# 4.3 Input Trace Equalization

The GS2965 features adjustable trace equalization to compensate for PCB trace dielectric losses at 1.5GHz.

The trace equalization has three peak-gain settings. The maximum peak gain value is optimized for compensating the high-frequency losses associated with 25 inches of 5-mil stripline in FR4 material. For boards with different striplines or materials, users can experiment to find the EQ setting which optimizes their system performance.

These settings are accessible via the serial host interface.

Each serial digital input, DDI, DDI, includes a pin EQn\_EN to turn its trace equalizer on or off. When a pin EQn\_EN is tied LOW or left unconnected, the trace equalization for input n is set to the Low Range.

When an EQn\_EN pin is tied HIGH, and input n is selected, the trace equalization for input n is set to the Medium Range.

| Table 4-1: Input Trace | Equalization | Operation |

|------------------------|--------------|-----------|

|------------------------|--------------|-----------|

| EQn_EN Setting | Trace Equalization<br>Range |

|----------------|-----------------------------|

| LOW            | Low                         |

| HIGH           | Medium                      |

The default peak-gain setting upon power-up is optimized for compensating the high-frequency losses associated with approximately 10 inches of 5-mil stripline in FR4 material.

The EQn\_EN pins are multiplexed with the serial host interface pins. The EQn\_EN functionality is enabled when pin HIF is tied high, as shown in Table 4-2:

Table 4-2: EQn\_EN Pins Multiplexed

| Pin        | Function                                                                             |

|------------|--------------------------------------------------------------------------------------|

| SDI/EQ0_EN | Active-high logic input to enable trace-equalization for high-speed input channel 0. |

| CS/EQ1_EN  | Active-high logic input to enable trace-equalization for high-speed input channel 1. |

## 4.4 2:1 Input Mux

The GS2965 incorporates a 2:1 input mux, which allows the connection of two independent streams of video/data. There are two differential inputs (DDI[1:0] /  $\overline{\text{DDI}[1:0]}$ ). The active channel can be selected via the DDI\_SEL[1:0] registers as shown in Table 4-3.

#### Table 4-3: Input Selection Table

| DDI_SEL[1:0] | Selected Input |

|--------------|----------------|

| 00           | DDI0*          |

| 01           | NOT VALID      |

| 10           | NOT VALID      |

| 11           | DDI1           |

\* - Power up default

Active circuitry associated with the input buffers and trace EQ can only be turned on for the selected input. Inputs which are not selected have their input buffers and trace EQs turned OFF to save power. Unused inputs can be either left floating, or tied to VCC.

# 4.5 Crystal Buffer

The GS2965 features a crystal buffer supporting a Gennum recommended external 27MHz crystal. The GS2965 requires an external 27MHz reference clock for correct operation. This reference clock is generated by connecting a crystal to the XTAL- and XTAL+ pins of the device.

Alternately, a 27MHz external clock source can be connected to the XTAL- pin of the device, while the XTAL+ pin should be left floating.

# 4.6 LOS (Loss Of Signal) Detection

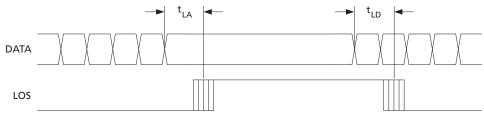

The LOS (Loss Of Signal) status pin is an active-high output that indicates when the serial digital input signal selected at the 2:1 input mux is invalid. In order for this output to be asserted, transitions must not be present for a period of  $t_{LA} = 5 - 10\mu s$ . After this output has been asserted, LOS will de-assert within  $t_{LD} = 0 - 5\mu s$  after the appearance of a transition at the DDIx input. See Figure 4-1.

This signal is HIGH (signal lost), when the number of data edges within a window is below a defined threshold. The output is automatically muted when LOS is detected.

This signal is LOW (signal valid), when the number of data edges within a window is above a defined threshold. See Table 4-4.

#### Table 4-4: LOS Operation

| LOS  | Signal  |

|------|---------|

| HIGH | Invalid |

| LOW  | Valid   |

The LOS function is operational for all operating modes of the device.

The LOS mode can be selected using the host interface, in register TOP\_1. The LOS detector has two major modes. In legacy mode, a simple edge-based detector is used to monitor the received signal at the output of the data slicer. Since the incoming signal has undergone considerable gain by this point, the legacy detector can be more susceptible

GS2965 Multi-Rate SDI Reclocker with Equalization & De-emphasis Data Sheet 52462 - 1 March 2010 to false de-assertion of LOS for unused channels which experience significant cross-talk from adjacent active channels.

The new LOS detector uses a measure of both signal amplitude and duration to minimize false detection of the impulse like signals that are characteristic of cross-talk. In this mode, the signal is tapped off at the output of the equalizer stage, prior to the high gain buffers.

The threshold setting within the detector can be adjusted to increase or decrease its sensitivity. Gennum recommends using the least sensitive threshold level. This provides the most margin against false de-assertion of LOS.

|              |                | LOS Detection<br>Method Select | LOS Threshold<br>Adjust |

|--------------|----------------|--------------------------------|-------------------------|

|              | >250mV         | 0x1                            | 0x0                     |

| Input Signal | 200mV to 250mV | 0x1                            | 0x1                     |

| Amplitude    | 150mV to 200mV | 0x1                            | 0x2                     |

|              | <150mV         | 0x1 or 0x0                     | 0x3                     |

Table 4-5: Suggested LOS Threshold Settings

The LOS mode can be selected by using the host interface, in register TOP\_1 (address 0x02).

# 4.7 Serial Digital Reclocker

The output of the Equalizer is fed to the reclocker. The function of the reclocker is to re-time the input signal and to generate system clocks.

The reclocker operates at three data rates; 2.97Gb/s, 1.485Gb/s and 270Mb/s, and provides a minimum input jitter tolerance of 0.8UI to square-wave-modulated jitter at these rates.

When there is no serial input signal, the internal clock maintains a frequency close to the expected incoming data rate by locking to the external reference crystal.

# 4.8 Lock Detection

The lock detect block indicates, via the active-high LOCKED signal, when the device has achieved lock to the incoming data stream.

The lock logic within the GS2965 includes a system that monitors the frequency and the phase of the incoming data, as well as a monitor to detect harmonic lock.

| LOCKED | Status     |

|--------|------------|

| HIGH   | Locked     |

| LOW    | Not locked |

The LOCKED output signal is also available via the host interface.

### 4.8.1 Lock Detect and Asynchronous Lock

The reference crystal is used to assist the PLL in achieving a short lock time. The lock detection algorithm is a continuous process, which begins at device power up or after a system reset, and continues until the device is powered down.

The asynchronous lock time is defined as the time it takes the device to lock when a video signal is first applied to the serial digital inputs, or when the digital video signal rate changes.

The synchronous lock time is defined as the time it takes the device to lock to a signal which has been momentarily interrupted.

# 4.9 Serial Data Output

The GS2965 features two current-mode differential output drivers, each capable of driving a maximum of  $800 \text{mV}_{pp}$ , differential, into an external  $100\Omega$  differential load.

Each of the GS2965's output buffers include two on-chip,  $50\Omega$  termination resistors.

#### 4.9.1 Output Signal Interface Levels

The serial digital outputs of the GS2965 are compatible when DC-coupled with all Gennum serial digital interface products that feature a differential LVPECL or CML receiver designed for SDI applications and operate from 3.3V or 2.5V supplies. This includes but is not limited to: GS2978, GS2988, and GS2989.

The serial digital data inputs are also compatible when DC-coupled with LVPECL or CML differential outputs from crosspoint switches which operate from 3.3V or 2.5V supplies. This includes but is not limited to: GS2974A, GS2974B, and GS2984 equalizers.

## 4.9.2 Adjustable Output Swing

It is possible, via the host interface, to force the output swing to  $400 mV_{pp}$  or  $800 mV_{pp}$  differential, when the outputs are terminated with  $50\Omega$  loads.

The default output swing upon power-up is  $400 \text{mV}_{pp}$  differential.

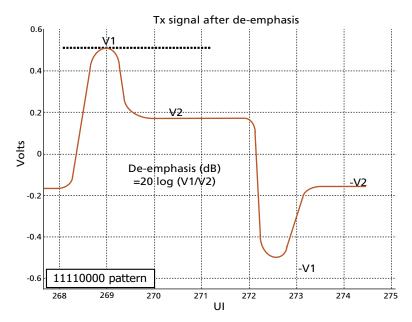

## 4.9.3 Output De-emphasis

The GS2965 features adjustable output de-emphasis to compensate for PCB trace dielectric losses.

The output de-emphasis has eight settings, evenly distributed from a minimum of 0dB (output de-emphasis OFF) to a peak de-emphasis setting that is optimized for compensating the high-frequency losses associated with approximately 20 inches of 5-mil stripline in FR4 material. These settings are accessible via the serial host interface.

The action of the de-emphasis settings is to attenuate the trailing edge of the output data waveform relative to the output swings set through the host interface.

De-emphasis is turned OFF when in Bypass mode.

The default de-emphasis setting upon power-up is 0dB (OFF).

NOTE: Changing the de-emphasis setting will vary both V1 & V2 (see Figure 4-2).

The DEn\_EN pins are multiplexed with the serial host interface pins. The DEn\_EN functionality is enabled when pin HIF is tied HIGH, as shown in Table 4-7:

Table 4-7: DEn\_EN Pins Multiplexed

| Pin        | Function                                                                      |

|------------|-------------------------------------------------------------------------------|

| SDO/DE0_EN | Active-high logic input to enable de-emphasis for high-speed input channel 0. |

| SCK/DE1_EN | Active-high logic input to enable de-emphasis for high-speed input channel 1. |

Figure 4-2: De-emphasis Waveform

# 4.10 Automatic and Manual Data Rate Selection

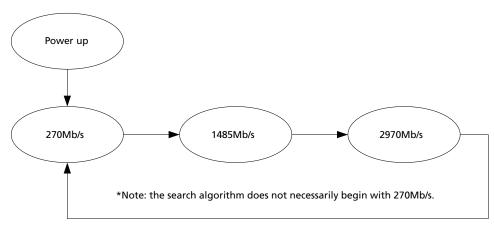

The GS2965 can be configured to manually lock to a specific data rate or automatically search for and lock to the incoming data rate. The default configuration is AUTO mode. This can be changed via the host interface.

In AUTO mode, the SS[1:0] registers become read only, and the bit pattern indicates the data rate at which the PLL is currently locked to (or previously locked to). The search algorithm cycles through the data rates and starts over if that data rate is not found (see Figure 4-3).

A "search algorithm" cycles through the supported data rates until lock is achieved, as shown in Figure 4-3 below.

#### Figure 4-3: GS2965 Automatic Mode Search Algorithm

In MANUAL mode, the SS[1:0] registers become read or write accessible, and the data rate can be programmed. In this mode, the search algorithm is disabled and the GS2965's PLL will only lock to the data rate selected in accordance with Table 4-8.

#### Table 4-8: Data Rate Indication/Selection Bit Pattern

| SS[1:0] | Data Rate (Mb/s)   |

|---------|--------------------|

| 0       | Reserved           |

| 1       | 270                |

| 2       | 1485 or 1485/1.001 |

| 3       | 2970 or 2970/1.001 |

# 4.11 SD/HD Indication

The SD/HD signal indicates the output data rate of the device and can be connected to the SD/HD input pin of dual slew rate cable drivers such as the GS2988.

When this signal is HIGH, the data rate is 270Mb/s. This signal is LOW for all other data rates.

This signal is also LOW when the device is operating in bypass mode (Auto-bypass and User-bypass).

The SD/ $\overline{\text{HD}}$  signal is LOW when the device is not locked.

# 4.12 Bypass Mode

In bypass mode, the GS2965 passes the data at the inputs, directly to the output. There are two register bits that control the bypass function: BYPASS and AUTOBYPASS.

The BYPASS bit is an active-high signal which forces the GS2965 into bypass mode for as long as the bit is asserted HIGH.

The AUTOBYPASS bit is an active-high signal that places the GS2965 into bypass mode only when the PLL has not locked to a data rate.

| Bypass | Autobypass | Device Operation                                                                                    |

|--------|------------|-----------------------------------------------------------------------------------------------------|

| HIGH   | Х          | Bypass Mode                                                                                         |

| LOW    | HIGH       | Bypass Mode if the PLL has not<br>locked to a data rate                                             |

| LOW    | LOW        | Power-up default. Normal<br>Operation, part always tries to<br>lock to the incoming data<br>stream. |

#### Table 4-9: Bypass Modes

Note that if BYPASS is HIGH, this will override the AUTOBYPASS functionality.

When the GS2965's PLL is not locked and BYPASS = LOW and AUTOBYPASS = LOW, the serial digital output DDO/DDO will produce invalid data.

The AUTOBYPASS function will bypass unsupported (non-reclocked) SMPTE SDI signal rates without producing bit errors: 143Mb/s, 177Mb/s, 360Mb/s, 540Mb/s.

# 4.13 DVB-ASI

The GS2965 also reclocks DVB-ASI signals at 270Mb/s. In auto mode, the device will automatically lock to the incoming 270Mb/s signal. In manual mode, the SS[1:0] bits must be set to 01 (270Mb/s) to ensure proper operation.

# 4.14 Output Mute and Data/Clock Output Selection

The DATA\_MUTE register is provided to allow muting of the serial digital data output.

Setting  $\overline{DATA}$ \_MUTE = LOW will force the serial digital outputs DDO/ $\overline{DDO}$  to mute (statically latch HIGH) under all conditions and operating modes.

The DDO1\_DISABLE register is provided to allow the second data/clock output to be powered down.

When DDO1\_DISABLE is set LOW, the serial digital clock outputs DDO1/RCO and DDO1/RCO are muted and the driver is powered-down.

The DATA/CLOCK register is provided to allow the second output to emit a copy of the reclocked serial data or the recovered clock. By default, this output will be set as DATA.

| DATA_MUTE | DDO1_DISABLE | DATA/CLOCK | DDO0 | DDO1/RCO   |

|-----------|--------------|------------|------|------------|

| 1         | 1            | 0          | DATA | CLOCK      |

| 1         | 1            | 1          | DATA | DATA       |

| 0         | 1            | 0          | MUTE | CLOCK      |

| 0         | 1            | 1          | MUTE | MUTE       |

| 1         | 0            | х          | DATA | Power down |

| 0         | 0            | х          | MUTE | Power down |

Table 4-10: Configuration of GS2965 Output Drivers and Mute/Disable Pins

# 4.15 Host Interface

#### 4.15.1 Introduction

The GS2965 offers a Serial Peripheral Interface (SPI) to access advanced features and programmability. The polarity of the  $\overline{\text{HIF}}$  pin tells the GS2965 whether or not the host interface is active ( $\overline{\text{HIF}} = 0$ ) or in legacy mode ( $\overline{\text{HIF}} = 1$ ).

Using the host interface, it is possible to override the control pin settings, and such settings will persist until the device has been powered-down and/or reset. The host interface is capable of reading hard-wired pin configuration, pin override settings and the values of all status monitoring pins.

There is an optional 3-state feature available in the Control Status Registers (CSR) that puts the SPI SDO to high-impedance when it's not being used (Register: TOP\_1, bit: 2).

## 4.15.2 Legacy Mode & Start-up

In legacy mode, basic configuration of the device (including a subset of equalizer and de-emphasis settings) are available at the pin level. In this mode, register settings are automatically set to default so that the GS2965 is live at power-up.

## 4.15.3 Host Interface Mode & Start-up

In host interface mode, the user gains access to Control and Status Registers (CSRs) that manage advanced features. In this mode, equalizer and de-emphasis settings are set through the CSR.

The SPI control is functional at start-up without the need for a reset signal. However, to clear the registers to their default state, a reset command is recommended via the SPI.

This is done by setting the  $\overline{R}$  bit (reset) LOW in the command word. This will guarantee the CSR will not start up in a random state.

The maximum operating speed of the SPI is 10MHz.

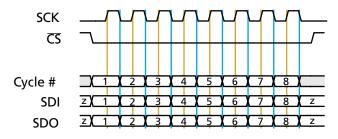

## 4.15.4 Clock & Data Timing

The SPI signals are Serial Data Input (SDI), Serial Data Output (SDO), active-low Chip Select ( $\overline{\text{CS}}$ ), and Serial Clock Input (SCK). The host interface operates in SPI Mode 0, i.e. the SDI input will latch data in on the rising edge of SCK. The SDO data output will transition on falling edges of SCK. Data is transmitted or received on the SPI port MSB first LSB last.

Figure 4-4: Data Clock Alignment

## 4.15.5 Single Device Operation

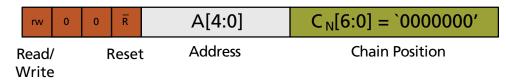

For applications with a single device or applications with multiple devices where daisy chaining is not desired, the chain position bits C[6:0] should always be set to 0. As a by-product of the daisy chaining feature, Read and Write operations experience a 32 SCK cycle latency from SDI to SDO. For more details on daisy-chaining, refer to Section 4.15.8 on page 29.

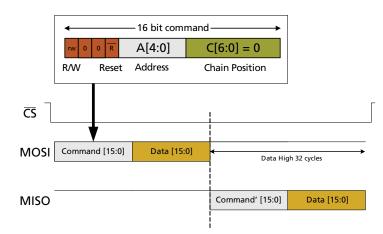

Figure 4-5: 16-bit Command Format

### 4.15.6 Write Operation - Single Device

A Write operation consists of a 16-bit command word and a 16-bit data word, followed by 32 cycles with the slave SDI held HIGH. When writing to a single non-daisy chained device, the following format should be used:

Figure 4-6: Single Device Write

- 1. At power-up, the device should be reset by setting the  $\overline{R}$  bit LOW. A simple way to accomplish a reset is to hold the slave SDI line LOW for an entire 64 cycle communication.

- 2. For a Write operation, the r/w bit should be set to 0.

- 3. The 2nd and 3rd bits are reserved, and should be set to 0.

- 4. The  $\overline{R}$  bit should always be set HIGH for a normal Write operation.

- 5. Refer to the Register Map for information on Address and Data bits.

- 6. The slave SDI line should be held HIGH for 32 cycles before de-asserting  $\overline{CS}$ .

### 4.15.7 Read Operation - Single Device

For Reading from a device the following format should be used:

#### Figure 4-7: Single Device Read

- 1. For a Read operation, the r/w bit should be set to 1.

- 2. The 2nd and 3rd bits are reserved and should be set to 0.

- 3. The  $\overline{R}$  bit should always be set HIGH for a normal Read Operation.

- 4. Data Out at the slave SDO will appear after holding the slave SDI line HIGH for 32 cycles.

- 5. The 16-bit data is now available on the slave SDO line.

Detailed timing diagrams for Write and Read can be seen in Figure 4-8 and Figure 4-9.

| Input data hold time t <sub>8</sub> 1.5 – – ns                                              |

|---------------------------------------------------------------------------------------------|

|                                                                                             |

| CS_n HIGH after last HOST_CLK rising edge  t_7  75% of  -  ns    HOST_CLK  HOST_CLK  neriod |

| t <sub>6</sub> 1.5                                                                          |

| t <sub>3</sub> 1.5                                                                          |

| t2 40 50 60<br>t3 1.5<br>t6 1.5<br>t7 75% of                                                |

| $\begin{array}{cccccccccccccccccccccccccccccccccccc$                                        |

| $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                       |

|                                                                                             |

| t <sub>8</sub> 1.5                                                                          |

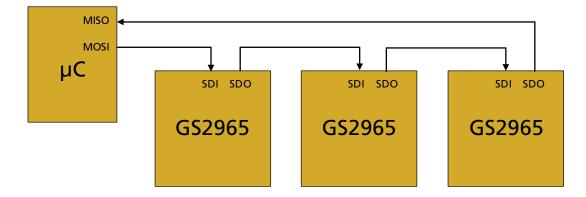

## 4.15.8 Daisy Chain Operation

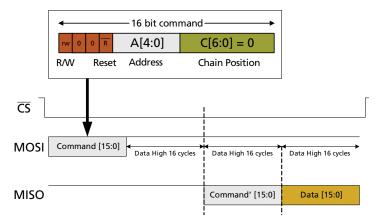

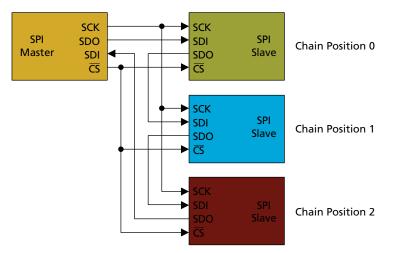

For applications with multiple GS2965 devices, it is possible to daisy-chain up to 127 parts in serial. In this configuration, the first device SDI should be connected to the SPI Master SDO. The serial data output of each device is then connected to the serial data input of the following device, and so on. The last device's SDO connects to the Master's SDI. Connecting devices in serial reduces the number of I/O ports required by the master by removing the need for additional chip select lines.

Figure 4-10: Daisy Chained SPI Bus

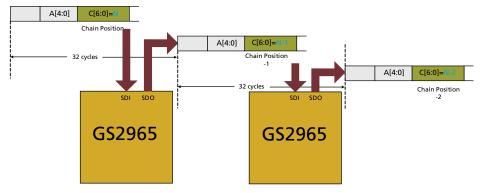

The position of each GS2965 device in the serial chain is referred to as its Chain Position, with 0 corresponding to the first device. The Chain Position in the SPI command word is decoded by each slave to know which device the master is talking to.

Each GS2965 slave is designed to output a replica of what it receives at its input after a delay of 32 cycles. The Chain Position part of the command is decremented by one in the duplicated command word at the output. Each device in the chain will only execute the issued command if it verifies that the current chain position is set to 0.

Figure 4-11: Chain Position Decoding

### 4.15.9 Read & Write Operation - Daisy Chained Devices

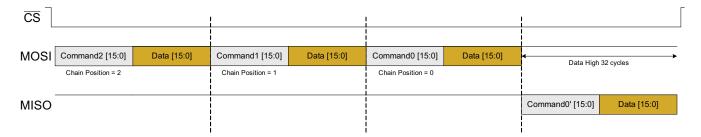

In a serial daisy chain configuration, Read and/or Write operations can be performed to multiple devices in the chain via consecutive operations. Figure 4-12 below shows a simple 3 device configuration.

Figure 4-12: Three Devices in Daisy Chain Configuration

#### 4.15.10 Writing to all Devices

When writing to all devices in the chain, a Write Command and corresponding Data is required for each device. When the devices are being configured in the same way, all of them will have the same command and data with the exception of the Chain Position bits. This example assumes a 3-device daisy chain. A command is issued to the last device in the chain first, although it is possible to talk to the devices in any order.

#### Figure 4-13: Daisy Chain Write

- 1. The first command issued in time is the command for the last device in the chain (chain position = 2). When the first device receives this command it will recognize that the Chain Position is 2 and will not execute the command. It will duplicate the command and data word at its output and decrement the Chain Position by one.

- 2. Consecutive commands are issued for each device in the chain as shown.

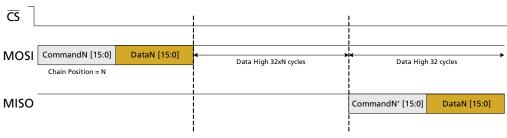

### 4.15.11 Writing to a Single Device in the Chain

The following example shows how to write to a single device in a chain:

Chain Position = N (N = 0 for first device in chain)

#### Figure 4-14: Daisy Chain Write to a Single Device

- 1. The command is issued to Chain Position N.

- 2. 32xN cycles are required to shift the command through N devices. The device at chain position N executes the command.

- 3. 32 additional cycles are needed to complete the communication.

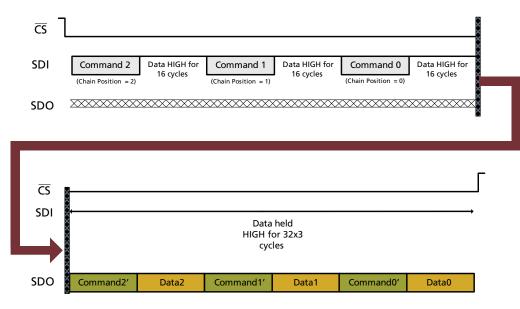

## 4.15.12 Reading from all Devices

To read from all devices in the chain, a Read command is issued for each device consecutively. After each command, the data is held HIGH for 16 cycles. Once a device recognizes it is being talked to, it will output data from the register requested. Clock needs to be applied to cycle the output data through all devices in the chain.

Figure 4-15: Daisy Chain Read

- 1. Read command is issued to the last device in the chain, followed by Read commands to the lower chain positions.

- 2. Clock is applied to cycle the output data through the chain.

- 3. Command2' refers to the altered or decremented Command2.

## 4.15.13 Reading from a Single Device in the Chain

The following example shows how to read from a single device in a chain:

$\label{eq:Chain Position = N (N = 0 for first device in chain) \qquad Chain Length = K (K \ge 1)$

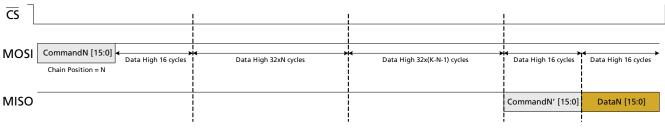

#### Figure 4-16: Daisy Chain Read from a Single Device

- 1. Read command and 16 cycles of data held HIGH are issued to chain position N.

- 2. 32xN cycles are applied with data HIGH to cycle the command through N devices in the chain (NOTE: N is 0 for first device in chain). Device N executes the command.

- 3. With K representing the total number of devices in the chain, 32x(K-N-1) cycles are applied to bring the return data through the rest of the chain.

- 4. 16 additional cycles are applied until the data from device N is available on the Master SDI.

# 4.15.14 Host Register Map

#### Table 4-12: Host Register Map

| Register<br>Name | Register<br>Address | Bit<br>Position | Access  | Function                                        | Default<br>Value | Valid<br>Range | Comments                                               |

|------------------|---------------------|-----------------|---------|-------------------------------------------------|------------------|----------------|--------------------------------------------------------|

| EQ_1             | EQ_1 0x00 —         |                 | RW      | Reserved.                                       |                  |                |                                                        |

|                  |                     |                 | RW      | Input Attenuation Enable<br>(ATTEN_EN)          | 0x0              | 0 or 1         | Enable for input<br>signals above<br>1Vpp differential |

|                  |                     | 8               | RW      | Equalizer Offset Correction Enable              | 0x1              | 0 or 1         | Recommend<br>always on                                 |

|                  |                     | 7               | RW      | Equalizer Gain Setting for DDI1                 | 0x0              | 0 or 1         | See<br>supplementary<br>table below                    |

|                  |                     | 6 - 5           | RW      | Unused                                          | 0x0              | 0 or 1         | _                                                      |

|                  |                     | 4               | RW      | Equalizer Gain Setting for DDI0                 | 0x00             | 0 or 1         | See<br>supplementary<br>table below                    |

|                  |                     | 3               | RW      | Equalizer Enable for DDI1                       | 0x00             | 0 or 1         | See<br>supplementary<br>table below                    |

|                  |                     | 2 - 1           | RW      | Unused                                          | 0x00             | 0 or 1         | -                                                      |

|                  |                     | 0               | RW      | Equalizer Enable for DDI0                       | 0x00             | 0 or 1         | See<br>supplementary<br>table below                    |

|                  |                     |                 |         | Equalizer Decode Lo                             | gic              |                |                                                        |

|                  |                     | EQ_EN           | EQ_GAIN | EQ Setting                                      | Recommended 1    |                | Trace Lengths                                          |

|                  |                     | 0               | 0       | LOW                                             |                  | 0 to 10 inc    | hes of FR4                                             |

|                  |                     | 0               | 1       | LOW                                             |                  | 0 to 10 inc    | hes of FR4                                             |

|                  |                     | 1               | 0       | MED                                             |                  | 10 to 20 in    | ches of FR4                                            |

|                  |                     | 1               | 1       | HIGH                                            | 20               | ) or more i    | nches of FR4                                           |

| DRIVER_1         | 0x01                | 15:10           | RW      | Unused                                          | 0x0              | 0 or 1         | _                                                      |

|                  |                     | 9               | RW      | Amplitude Control for DDO1                      | 0x1              | 0 or 1         | 0 = 800mV swing<br>1 = 400mV swing                     |

|                  |                     | 8               | RW      | Amplitude Control for DDO0                      | 0x1              | 0 or 1         | 0 = 800mV swing<br>1 = 400mV swing                     |

|                  |                     | 7:5             | RW      | De-Emphasis Boost Amplitude<br>Control for DDO1 | 0x2              | 0x0 to<br>0x7  | 0x0 = Lowest<br>Setting<br>0x7 = Highest<br>Setting    |

| Register<br>Name | Register<br>Address | Bit<br>Position | Access | Function                                        | Default<br>Value | Valid<br>Range | Comments                                                                                                                                                                                 |

|------------------|---------------------|-----------------|--------|-------------------------------------------------|------------------|----------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DRIVER_1         | 0x01                | 4:2             | RW     | De-Emphasis Boost Amplitude<br>Control for DDO0 | 0x2              | 0x0 to<br>0x7  | 0x0 = Lowest<br>Setting<br>0x7 = Highest<br>Setting                                                                                                                                      |

|                  |                     | 1               | RW     | De-Emphasis Enable for DDO1                     | 0x0              | 0 or 1         | _                                                                                                                                                                                        |

|                  |                     | 0               | RW     | De-Emphasis Enable for DDO0                     | 0x0              | 0 or 1         | _                                                                                                                                                                                        |

| TOP_1            | 0x02                | 15:9            | RW     | Reserved.                                       |                  |                |                                                                                                                                                                                          |

|                  |                     | 8:7             | RW     | LOS Threshold Adjust                            | 0x0              | 0x0 to<br>0x3  | 0x0 = least<br>sensitive<br>0x3 = most<br>sensitive                                                                                                                                      |

|                  |                     | 6:5             | RW     | LOS Detection Method Select                     | 0x0              | 0x0 to<br>0x2  | 0x0 = legacy edge<br>detectionmethod<br>0x1 = new signal<br>strength<br>detectionmethod<br>0x2 = dual<br>detection<br>method: both<br>must detect signal<br>present for LOS to<br>be LOW |

|                  |                     | 4               | RW     | LOS Mute Enable                                 | 0x0              | 0 or 1         | When enabled<br>the output will<br>automatically<br>mute if LOS is<br>HIGH                                                                                                               |

|                  |                     | 3               | RW     | Power Down                                      | 0x0              | 0 or 1         | Chip powers<br>down when<br>asserted                                                                                                                                                     |

|                  |                     | 2               | RW     | Tri-State Enable for SPI Output                 | 0x0              | 0 or 1         | When enabled<br>the SPI SDO will<br>be high Z when<br>CS is not selected                                                                                                                 |

|                  |                     | 1               | RW     | Crystal Buffer Disable                          | 0x0              | 0 or 1         | 0 = Enabled<br>1 = Disabled                                                                                                                                                              |

|                  |                     | 0               | RW     | Data Polarity Invert                            | 0x0              | 0 or 1         | 0 = Not Inverted<br>1 = Inverted                                                                                                                                                         |

### Table 4-12: Host Register Map (Continued)

0X03 to 0X0B

B Reserved.

| Register<br>Name | Register<br>Address | Bit<br>Position | Access | Function            | Default<br>Value | Valid<br>Range        | Comments                                                                                        |

|------------------|---------------------|-----------------|--------|---------------------|------------------|-----------------------|-------------------------------------------------------------------------------------------------|

| PIN_OR_1 0x0C    | 0x0C                | 15:13           | RW     | Unused              | 0x0              | 0 or 1                |                                                                                                 |

|                  |                     | 12              | RW     | DATA/CLOCK          | 0x0              | 0 or 1                | _                                                                                               |

|                  |                     | 11              | RW     | DDO1_DISABLE        | 0x0              | 0 or 1                | _                                                                                               |

|                  |                     | 10              | RW     | DATA_MUTE           | 0x0              | 0 or 1                | _                                                                                               |

|                  |                     | 9:8             | RW     | КВВ                 | 0x0              | 0x0,<br>0x2 or<br>0x3 | Equivalent<br>settings:<br>0x0 = KBB to<br>ground<br>0x2 = KBB<br>floating<br>0x3 = KBB to VCC  |

|                  |                     | 7               | RW     | SS1                 | 0x0              | 0 or 1                | _                                                                                               |

|                  |                     | 6               | RW     | SS0                 | 0x0              | 0 or 1                | _                                                                                               |

|                  |                     | 5               | RW     | AUTO/MAN            | 0x0              | 0 or 1                | _                                                                                               |

|                  |                     | 4               | RW     | AUTOBYPASS          | 0x0              | 0 or 1                | _                                                                                               |

|                  |                     | 3               | RW     | BYPASS              | 0x0              | 0 or 1                | _                                                                                               |

|                  |                     | 2               | RW     | DDI_SEL1            | 0x0              |                       | -See Table 4-3 for                                                                              |

|                  |                     | 1               | RW     | DDI_SEL0            | 0x0              | 0 or 1                | - valid values                                                                                  |

|                  |                     | 0               | RW     | Pin Override Enable | 0x0              | 0 or 1                | When enabled,<br>input values will<br>be taken from this<br>register instead of<br>package pins |

| STATUS_1         | 0X0D                | 15:4            | RO     | Reserved.           | -                | -                     | _                                                                                               |

|                  |                     | 3               | RO     | SD/HD               | -                | -                     | -                                                                                               |

|                  |                     | 2               | RO     | LOCKED              | -                | _                     | _                                                                                               |

|                  |                     | 1               | RO     | SS1                 | -                | -                     | _                                                                                               |

|                  |                     | 0               | RO     | SSO                 | -                | -                     | _                                                                                               |

| 0X0E to          | o 0X11              | Reserved.       |        |                     |                  |                       |                                                                                                 |

### Table 4-12: Host Register Map (Continued)

# 4.16 Device Power Up

In host mode ( $\overline{\text{HIF}}$  pin tied LOW), control & status registers (CSRs) may start up in a random state. There is a bit in the command word  $\overline{R}$  which will reset the CSR when set LOW.

In non-host mode (HIF pin tied HIGH), the HIF pin is used to trigger an internal reset signal to place all registers in a deterministic, default state upon power-up.

In either host mode or non-host mode, other internal state machines (e.g. offset correction and PLL) automatically recover from any state at start-up with no reset required. It takes ~10 $\mu$ s for the device to lock after start-up.

# 4.17 Standby

The purpose of Standby mode is to allow operating power to be reduced when the device's functionality is not required, and to have a rapid and simple transition to full operation when the device is required.

In order to achieve this, the device can be powered-down by writing a '1' to the 'Power Down' bit located in register address 0x02.

# **5. Typical Application Circuit**

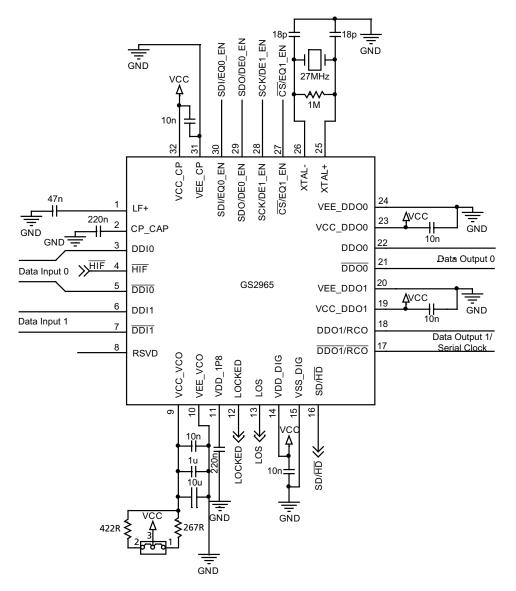

Figure 5-1: GS2965 Typical Application Circuit

# 6. Package and Ordering Information

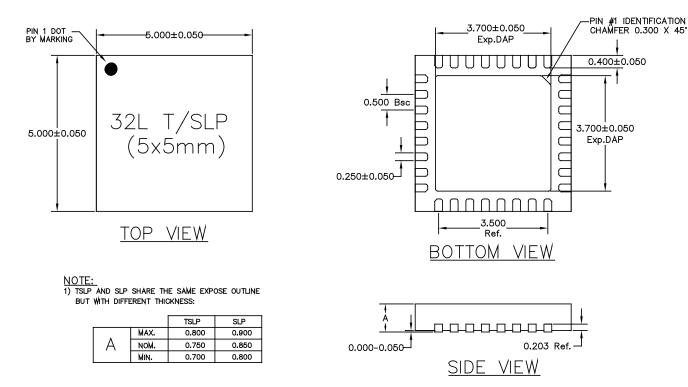

# 6.1 Package Dimensions

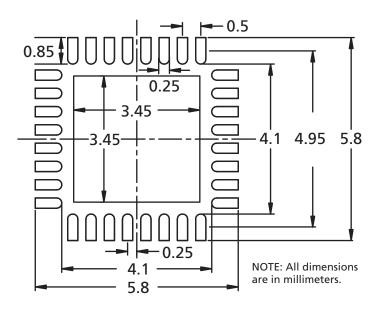

# **6.2 Recommended PCB Footprint**

GS2965 Multi-Rate SDI Reclocker with Equalization & De-emphasis Data Sheet 52462 - 1 March 2010

# 6.3 Packaging Data

| Parameter                                                                   | Value                |

|-----------------------------------------------------------------------------|----------------------|

| Package Type                                                                | 5mm x 5mm 32-pin QFN |

| Moisture Sensitivity Level                                                  | 3                    |

| Junction to Case Thermal Resistance, $\theta_{j\text{-}c}$                  | 19.9°C/W             |

| Junction to Air Thermal Resistance, $\theta_{j\text{-}a}$ (at zero airflow) | 34.9°C/W             |

| Junction to Board Thermal Resistance, $\theta_{\text{j-b}}$                 | 12.5°C/W             |