# Circuit Note CN-0217

| Circuits              |

|-----------------------|

| from the <b>Lab</b> ™ |

| Reference Circuits    |

Circuits from the Lab™ reference circuits are engineered and tested for quick and easy system integration to help solve today's analog, mixed-signal, and RF design challenges. For more information and/or support, visit www.analog.com/CN0217.

| Devices Connected/Referenced |                                                          |  |

|------------------------------|----------------------------------------------------------|--|

| AD5933                       | 1 MSPS, 12-Bit Impedance Converter,<br>Network Analyzer  |  |

| AD5934                       | 250kSPS, 12-Bit Impedance Converter,<br>Network Analyzer |  |

| AD8606                       | Precision Low Noise Dual CMOS Op Amp                     |  |

# **High Accuracy Impedance Measurements Using 12-Bit Impedance Converters**

#### **EVALUATION AND DESIGN SUPPORT**

Circuit Evaluation Boards

CN-0217 Circuit Evaluation Board

(EVAL-CN0217-EB1Z)

Design and Integration Files

Schematics, Layout Files, Bill of Materials

# **CIRCUIT FUNCTION AND BENEFITS**

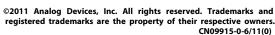

The AD5933 and AD5934 are high precision impedance converter system solutions that combine an on-chip programmable frequency generator with a 12-bit, 1 MSPS (AD5933) or 250 kSPS (AD5934) analog-to-digital converter (ADC). The tunable frequency generator allows an external complex impedance to be excited with a known frequency.

The circuit shown in Figure 1 yields accurate impedance measurements extending from the low ohm range to several hundred  $k\Omega$  and also optimizes the overall accuracy of the AD5933/AD5934.

$Figure\ 1.\ Optimized\ Signal\ Chain\ for\ Impedance\ Measurement\ Accuracy\ (Simplified\ Schematic,\ All\ Connections\ and\ Decoupling\ Not\ Shown)$

#### Rev.0

Circuits from the Lab™ circuits from Analog Devices have been designed and built by Analog Devices engineers. Standard engineering practices have been employed in the design and construction of each circuit, and their function and performance have been tested and verified in a lab environment room temperature. However, you are solely responsible for testing the circuit and determing its suitability and applicability for your use and application. Accordingly, in no event shall Analog Devices be liable for direct, indirect, special, incidental, consequential or punitive damages due to any cause whatsoever connected to the use of any Circuits from the Lab circuits. (Continued on last page)

CN-0217 Circuit Note

#### CIRCUIT DESCRIPTION

The AD5933 and AD5934 have four programmable output voltage ranges; each range has an output impedance associated with it. For example, the output impedance for a 1.98 V p-p output voltage is typically 200  $\Omega$  (see Table 1).

Table 1. Output Series Resistance, R<sub>OUT</sub>, vs. Excitation Range for VDD = 3.3 V Supply Voltage,

|         | Output Excitation | Output Resistance, |

|---------|-------------------|--------------------|

| Range   | Amplitude         | R <sub>оит</sub>   |

| Range 1 | 1.98 V p-p        | 200 Ω typ          |

| Range 2 | 0.97 V p-p        | 2.4 kΩ typ         |

| Range 3 | 0.383 V p-p       | 1.0 kΩ typ         |

| Range 4 | 0.198 V p-p       | 600 Ω typ          |

This output impedance impacts the impedance measurement accuracy, particularly in the low  $k\Omega$  range, and should be taken into account when calculating the gain factor. Please refer to the AD5933 or AD5934 data sheets for more details on gain factor calculation.

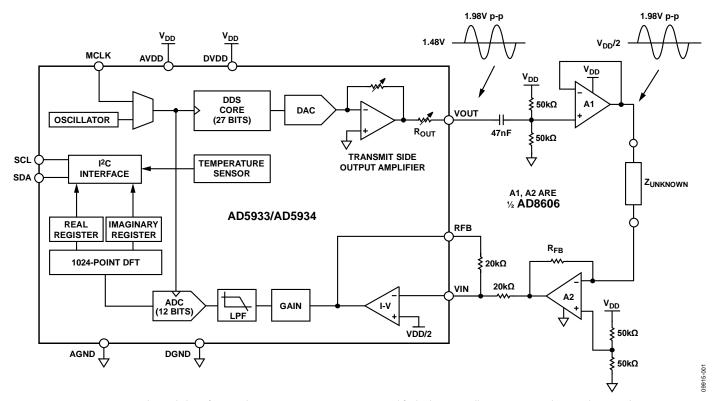

A simple buffer in the signal chain prevents the output impedance from affecting the unknown impedance measurement. A low output impedance amplifier should be selected with sufficient bandwidth to accommodate the AD5933/AD5934 excitation frequency. An example of the low output impedance achievable is shown in Figure 2 for the AD8605/AD8606/AD8608 family of CMOS op amps. The output impedance for this amplifier for an  $A_{\rm V}$  of 1 is less than 1  $\Omega$  up to 100 kHz, which is the maximum operating range of the AD5933/AD5934.

Figure 2. Output Impedance of AD8605/AD8606/AD8608

#### Matching the DC Bias of Transmit Stage to Receive Stage

The four programmable output voltage ranges in the AD5933/AD5934 have four associated bias voltages (Table 2). For example, the 1.98 V p-p excitation voltage has a bias of 1.48 V. However, the current-to-voltage (I-V) receive stage of the AD5933/AD5934 is set to a fixed bias of VDD/2 as shown in Figure 1. Thus, for a 3.3 V supply, the transmit bias voltage is 1.48 V, while the receive bias voltage is 3.3 V/2 = 1.65 V. This potential difference polarizes the impedance under test and can cause inaccuracies in the impedance measurement.

One solution is to add a simple high-pass filter with a corner frequency in the low Hz range. Removing the dc bias from the transmit stage and re-biasing the ac signal to VDD/2 keeps the dc level constant throughout the signal chain.

Table 2. Output Levels and Respective DC Bias for VDD = 3.3 V Supply Voltage

|       | Output Excitation |                      |

|-------|-------------------|----------------------|

| Range | Amplitude         | Output DC Bias Level |

| 1     | 1.98 V p-p        | 1.48 V               |

| 2     | 0.97 V p-p        | 0.76 V               |

| 3     | 0.383V p-p        | 0.31 V               |

| 4     | 0.198 V p-p       | 0.173 V              |

### Selecting an Optimized I-V Buffer for the Receive Stage

The current-to-voltage (I-V) amplifier stage of the AD5933/AD5934 can also add minor inaccuracies to the signal chain. The I-V conversion stage is sensitive to the amplifier's bias current, offset voltage, and CMRR. By selecting the proper external discrete amplifier to perform the I-V conversion, the user can choose an amplifier with lower bias current and offset voltage specifications along with excellent CMRR, making the I-V conversion more accurate. The internal amplifier can then be configured as a simple inverting gain stage.

Selection of resistor  $R_{FB}$  still depends on the gain through the system as described in the AD5933/AD5934 data sheet.

# Optimized Signal Chain for High Accuracy Impedance Measurements

Figure 1 shows a proposed configuration for measuring low impedance sensors. The ac signal is high-pass filtered and rebiased before buffering with a very low output impedance amplifier. The I-V conversion is completed externally before the signal returns to the AD5933/AD5934 receive stage. Key specifications that determine the required buffer are very low output impedance, single-supply capability, low bias current, low offset voltage, and excellent CMRR performance. Some suggested parts are the AD4528-1, AD8628/AD8629, AD8605, and AD8606. Depending on board layout, use a single-channel or dual-channel amplifier. Use precision 0.1% resistors for both the biasing resistors (50 k $\Omega$ ) and gain resistors (20 k $\Omega$  and RFB) to reduce inaccuracies.

Circuit Note CN-0217

#### **CIRCUIT EVALUATION AND TEST**

The schematic in Figure 1 was developed to improve impedance measurement accuracy, and some example measurements were taken. The AD8606 dual channel amplifier buffers the signal on the transmit path and converts the receive signal from current to voltage. For the three examples shown, the gain factor is calculated for each frequency increment to remove frequency dependent errors. A complete design package including schematics, bill of materials, layout, and Gerber files is available for this solution at <a href="http://www.analog.com/CN0217-DesignSupport">http://www.analog.com/CN0217-DesignSupport</a>. The software used is the same software that is available with evaluation boards and is accessible from the AD5933 and AD5934 product pages.

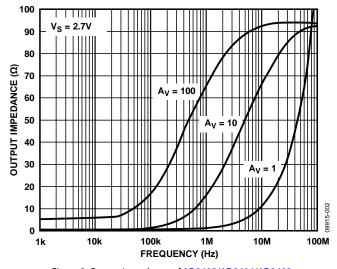

#### Example 1: Low Impedance Range

Table 1. Low Impedance Range Setup for VDD = 3.3 V Supply Voltage

| Parameter                      | Value                                    |

|--------------------------------|------------------------------------------|

| V p-p                          | 1.98 V (Range 1)                         |

| Number of Settling Time Cycles | 15                                       |

| MCLK                           | 16 MHz                                   |

| R <sub>CAL</sub>               | 20.1 Ω                                   |

| $R_{FB}$                       | 20.0 Ω                                   |

| Excitation Frequency Range     | 30 kHz to 30.2 kHz                       |

| Unknown Impedances             | $R1 = 10.3 \Omega$ ,                     |

|                                | $R2 = 30.0 \Omega$ ,                     |

|                                | C3 = 1 $\mu$ F ( $Z_C$ = 5.3 $\Omega$ at |

|                                | 30 kHz)                                  |

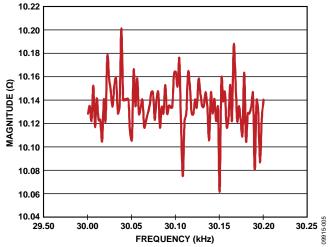

The results of the low impedance measurements are shown in Figure 3, Figure 4, and Figure 5. Figure 5 is for the 10.3  $\Omega$  measurement and is shown on an expanded vertical scale.

The accuracy achieved is very much dependent on how large the unknown impedance range is relative to the calibration resistor,  $R_{\rm CAL}$ . Therefore, in this example, the unknown impedance of 10.3  $\Omega$  measured 10.13  $\Omega$ , an approximate 2% error. Choosing an  $R_{\rm CAL}$  closer to the unknown impedance achieves a more accurate measurement; that is, the smaller the unknown impedance range is centered around  $R_{\rm CAL}$  is, the more accurate the measurement. Consequently, for large unknown impedance ranges, it is possible to switch in various  $R_{\rm CAL}$  resistors to break up the unknown impedance range using external switches. The  $R_{\rm ON}$  error of the switch is removed by calibration during the  $R_{\rm CAL}$  gain factor calculation. Using a switch to select various  $R_{\rm FB}$  values can optimize the dynamic range of the signal seen by the ADC.

Also note that to achieve a wider range of measurements a 200 mV p-p range was used. If the unknown Z is a small range, a larger output voltage range can be used to optimize the ADC dynamic range.

Figure 3. Measured Low Impedance Magnitude Results

Figure 4. Measured Low Impedance Phase Results

Figure 5. Measured 10.3 Ω Magnitude Results (Expanded Scale)

CN-0217 Circuit Note

# Example 2: $k\Omega$ Impedance Range

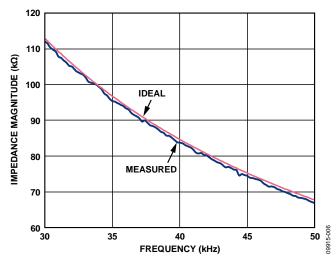

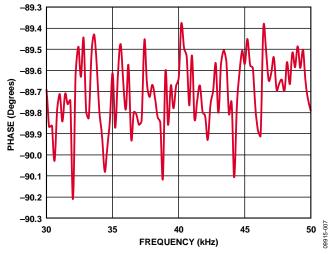

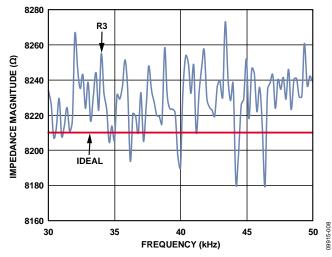

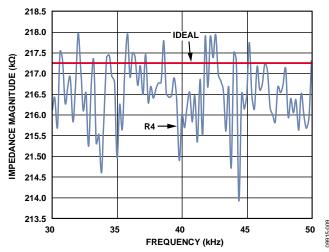

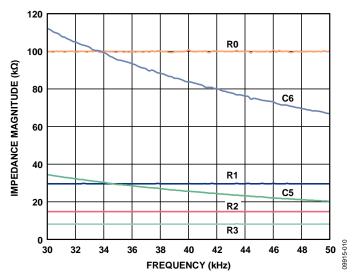

Using an  $R_{CAL}$  of 99.85  $k\Omega$ , a wide range of unknown impedances were measured according to the setup conditions listed in Table 2. Figure 6 to Figure 10 document accuracy results. To improve the overall accuracy, select an  $R_{CAL}$  value closer to the unknown impedance. For example, in Figure 9, an  $R_{CAL}$  closer to the  $Z_C$  value of 217.5  $k\Omega$  is required. If the unknown impedance range is large, use more than one  $R_{CAL}$  resistor.

Table 2.  $k\Omega$  Impedance Range Setup for VDD = 3.3 V Supply Voltage

| ·8-                            |                                                         |  |

|--------------------------------|---------------------------------------------------------|--|

| Parameter                      | Value                                                   |  |

| V p-p                          | 0.198 V (Range 4)                                       |  |

| Number of Settling Time Cycles | 15                                                      |  |

| MCLK                           | 16 MHz                                                  |  |

| Rcal                           | 99.85 kΩ                                                |  |

| $R_{FB}$                       | 100 kΩ                                                  |  |

| Excitation Frequency Range     | 30 kHz to 50 kHz                                        |  |

| Unknown Impedances             | $R0 = 99.85 \text{ k}\Omega$                            |  |

|                                | R1 = 29.88 kΩ                                           |  |

|                                | $R2 = 14.95 \text{ k}\Omega$                            |  |

|                                | $R3 = 8.21 \text{ k}\Omega$                             |  |

|                                | $R4 = 217.25 \text{ k}\Omega$                           |  |

|                                | $C5 = 150 \text{ pF}$ ( $Z_C = 26.5 \text{ k}\Omega$ at |  |

|                                | 40 kHz)                                                 |  |

|                                | $C6 = 47 pF (Z_C = 84.6 k\Omega at$                     |  |

|                                | 40 kHz)                                                 |  |

Figure 6. Magnitude Result for  $Z_C = 47$  pF,  $R_{CAL} = 99.85$  k $\Omega$

Figure 7. Phase Result for  $Z_C$  = 47 pF,  $R_{CAL}$  = 99.85 k $\Omega$

Figure 8.  $Z_C$  = 8.21  $k\Omega$ ,  $R_{CAL}$  = 99.85  $k\Omega$

Figure 9.  $Z_C$  = 217.25 kΩ,  $R_{CAL}$  = 99.85 kΩ

Circuit Note CN-0217

Figure 10. Magnitude Results for Example 2: R1, R2, R3, C5, C6

# Example 3: Parallel R-C (R||C) Measurement

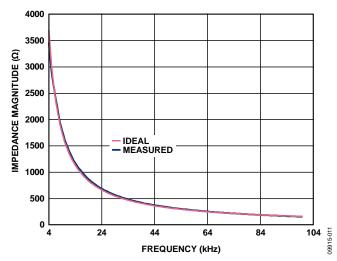

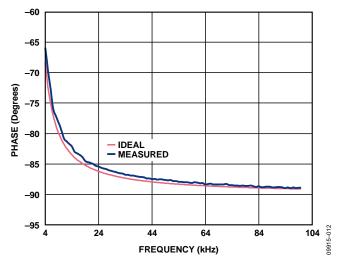

An R||C type measurement was also made using the configuration, using an  $R_{\text{CAL}}$  of 1 k $\Omega$ , an R of 10 k $\Omega$ , and a C of 10 nF, measured across a frequency range of 4 kHz to 100 kHz. The magnitude and phase results versus ideal are plotted in Figure 11 and Figure 12.

Table 3. R||C Impedance Range Setup for VDD = 3.3 V Supply Voltage

| ouppry vortage                 |                          |  |

|--------------------------------|--------------------------|--|

| Parameter                      | Value                    |  |

| V p-p                          | 0.383 V (Range 3)        |  |

| Number of Settling Time Cycles | 15                       |  |

| MCLK                           | 16 MHz                   |  |

| R <sub>CAL</sub>               | 1 kΩ                     |  |

| $R_{FB}$                       | 1 kΩ                     |  |

| Excitation Frequency Range     | 4 kHz to 100 kHz         |  |

| Unknown Impedance R  C         | $R = 10 \text{ k}\Omega$ |  |

|                                | C = 10 nF                |  |

Figure 11. Magnitude Results for  $Z_C = 10 \text{ k}\Omega || 10 \text{ nF}$ ,  $R_{CAL} = 1 \text{ k}\Omega$

Figure 12. Phase Results for  $Z_C = 10 \text{ k}\Omega || 10 \text{ nF}$ ,  $R_{CAL} = 1 \text{ k}\Omega$

#### **Setup and Test**

The EVAL-CN0217-EB1Z software is the same as that used on the EVAL-AD5933EBZ application board. Please refer to the technical note available on the CD provided for details on the board setup. Note that there are alterations to the schematic. Link connections on the EVAL-CN0217-EB1Z board are listed below in Table 4. Also note that the location for RFB is located at R3 on the evaluation board, and the location for Z<sub>UNKNOWN</sub> is C4.

Table 4. Link Connections for EVAL-CN0217-EB1Z

| Link Number | Default Position |

|-------------|------------------|

| LK1         | Open             |

| LK2         | Open             |

| LK3         | Open             |

| LK4         | Insert           |

| LK5         | Insert           |

| LK6         | А                |

#### **COMMON VARIATIONS**

Other op amps can be used in the circuit, such as the AD4528-1, AD8628, AD8629, AD8605, and the AD8608.

# **Switching Options for System Applications**

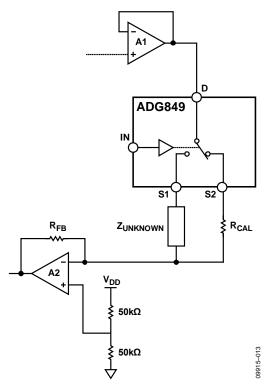

For this particular circuit, the  $Z_{\rm UNKNOWN}$  and  $R_{\rm CAL}$  were interchanged manually. However, in production, a low onresistance switch should be used. The choice of the switch depends on how large the unknown impedance range is and how accurate the measurement result needs to be. The examples in this document use just one calibration resistor, and so a low on-resistance switch such as the ADG849 can be used as shown in Figure 13. Multichannel switch solutions such as the quad

CN-0217 Circuit Note

ADG812 can also be used. The errors caused by the switch resistance on the  $Z_{\rm UNKNOWN}$  are removed during calibration, but by choosing a very low  $R_{\rm ON}$  switch, the effects can be further minimized.

Figure 13. Switching Between R<sub>CAL</sub> and Unknown Z Using the ADG849 UltraLow R<sub>ON</sub> SPDT Switch (Simplified Schematic, All Connections and Decoupling Not Shown)

#### **LEARN MORE**

CN-0217 Design Support Package: http://www.analog.com/CN0217-DesignSupport

MT-085 Tutorial, "Fundamentals of Direct Digital Synthesis (DDS)," Analog Devices.

Riordan, Liam, "AD5933 Evaluation Board Example Measurement," AN-1053 Application Note, Analog Devices.

Buchanan, David, "Choosing DACs for Direct Digital Synthesis," AN-237 Application Note, Analog Devices.

ADIsimDDS Design and Evaluation Tool

AD5933/AD5934 Demonstration and Design Tool

#### **Data Sheets and Evaluation Boards**

AD5933 Data Sheet

AD5933 Evaluation Board

AD5934 Data Sheet

AD5934 Evaluation Board

AD8606 Data Sheet

ADG849 Data Sheet

ADG812 Data Sheet

#### **REVISION HISTORY**

6/11—Revision 0: Initial Version

(Continued from first page) Circuits from the Lab circuits are intended only for use with Analog Devices products and are the intellectual property of Analog Devices or its licensors. While you may use the Circuits from the Lab circuits in the design of your product, no other license is granted by implication or otherwise under any patents or other intellectual property by application or use of the Circuits from the Lab circuits. Information furnished by Analog Devices is believed to be accurate and reliable. However, "Circuits from the Lab" are supplied "as is" and without warranties of any kind, express, implied, or statutory including, but not limited to, any implied warranty of merchantability, noninfringement or fitness for a particular purpose and no responsibility is assumed by Analog Devices for their use, nor for any infringements of patents or other rights of third parties that may result from their use. Analog Devices reserves the right to change any Circuits from the Lab circuits at any time without notice but is under no obligation to do so.