# Two-stage, dual-output, opto-coupled gate driver evaluation board

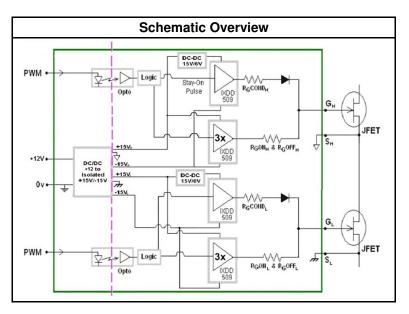

The SGDR2500P2 is an opto-isolated, two-stage gate driver optimized for high-speed hard switching of Microsemi's APTJC120AM13VCT1AG SiC JFET half-bridge power module. The SGDR2500P2 gate driver provides isolated high-side & low-side drivers with peak output currents of +20/-10 A for fast turn-on transients, yielding record-low switching energy losses.

#### **Features:**

- Suitable for driving Microsemi APTJC120AM13VCT1AG

- Isolated high-side and low-side outputs

- On-board derivation of isolated +/- 15 V supply voltages

- Two-stage driver switching & conduction

- Peak gate current of +20/-10 A

- Switching frequency up to 100 kHz

- Duty cycle: 0 to 100%

### **Applications:**

- Hard Switched Bridge Topologies

- Inverters/Converters

- Product Evaluation

- Research

- For operation principles and intended use, refer to Application note AN-SS5.

| 1100            | r roduct Summary |     |  |  |  |  |  |  |  |

|-----------------|------------------|-----|--|--|--|--|--|--|--|

| $V_{DD}$        | +12              | V   |  |  |  |  |  |  |  |

| I <sub>PK</sub> | +20/-10          | A   |  |  |  |  |  |  |  |

| $F_{SW(MAX)}$   | 100              | kHz |  |  |  |  |  |  |  |

| Duty Cycle      | 0-100            | %   |  |  |  |  |  |  |  |

|                 |                  |     |  |  |  |  |  |  |  |

Product Summary

#### **MAXIMUM RATINGS**

| Parameter                | Symbol             | Conditions                                                  | Value | Unit |

|--------------------------|--------------------|-------------------------------------------------------------|-------|------|

| Positive supply voltage  | V <sub>CC</sub>    | to GND                                                      | + 12  | V    |

| Input current logic HIGH | I <sub>F(ON)</sub> | (high and low side inputs)                                  | 10    | mA   |

| Pack Output Ourrant      |                    | Not connected to the JFET,<br>output shorted to GND or pure | + 27  | ٨    |

| Peak Output Current      | I <sub>O</sub>     | capacitive load                                             | - 27  | A    |

| Operating temperature    | T <sub>OP</sub>    |                                                             | + 85  | °C   |

| Storage temperature      | T <sub>ST</sub>    |                                                             | + 100 | °C   |

SGDR2500P2 Rev 1.3

#### **ELECTRICAL CHARACTERISTICS**

| Parameter                                                                     | Symbol          | Symbol Conditions -                           |        | Value       |       |      |  |

|-------------------------------------------------------------------------------|-----------------|-----------------------------------------------|--------|-------------|-------|------|--|

| Farameter                                                                     | Symbol          |                                               |        | Min Typ Max |       | Unit |  |

| External Power Supplies                                                       |                 |                                               |        |             |       |      |  |

| Positive supply voltage                                                       | V <sub>CC</sub> | to GND                                        | + 11.5 |             | +12.5 | V    |  |

| Depitive gupply gurrent                                                       |                 | without load                                  |        | 0.2         |       | m (  |  |

| Positive supply current                                                       | ICC             | V <sub>CC</sub> = +12 V, f = 100 kHz, D = 50% |        | 1400        |       | mA   |  |

| Positive supply current $I_{CC}$ $V_{CC} = +12 V$ , f = 100 kHz, D = 50% 1400 |                 |                                               |        |             |       |      |  |

| Input (characteristics same for b                                             | ooth inputs)    |                                               |        |             |       |      |  |

| Input forward voltage | V <sub>F</sub>      | I <sub>F</sub> = 5 mA, T <sub>A</sub> = 25 °C | 1.4 | 1.60 | 1.70 | V  |

|-----------------------|---------------------|-----------------------------------------------|-----|------|------|----|

| Input voltage, OFF    | V <sub>F(OFF)</sub> |                                               | 0   | -    | 0.8  | V  |

| Input current, ON     | I <sub>F(ON)</sub>  |                                               | 4.5 | -    | 10   | mA |

| Input capacitance     | C <sub>in</sub>     | $V=0V,f=1~MHz,T_A=25~^{o}C$                   | -   | 45   | -    | pF |

#### **Timing Characteristics**

| Delay time input to output | t <sub>d(ON)</sub>         | - | 130 | - | ns |

|----------------------------|----------------------------|---|-----|---|----|

| Delay time input to output | $t_{\text{d}(\text{OFF})}$ | - | 130 | - | ns |

#### Output (characteristics same for both outputs)

| Output voltage                               | Vo                                   | Peak positive voltage clamped by<br>JFET gate-source diode | - 15                        | -    | + 5V | V  |  |

|----------------------------------------------|--------------------------------------|------------------------------------------------------------|-----------------------------|------|------|----|--|

| Deals autout aumont (1)                      | 1                                    | $R_{GON} = 0.17 \ \Omega$                                  | $R_{GON} = 0.17 \ \Omega$ - |      |      | ^  |  |

| Peak output current <sup>(1)</sup>           | IO                                   | $R_{GOFF} = 0.17 \ \Omega$                                 |                             | - 10 | -    | A  |  |

| Steady-state output current I <sub>ODC</sub> |                                      | limited by R <sub>GCOND</sub>                              | -                           | 500  |      | mA |  |

| Output voltage rise time                     | t <sub>ro</sub>                      |                                                            | -                           | -    | 20   | ns |  |

| Output voltage fall time                     | ut voltage fall time t <sub>fo</sub> |                                                            | -                           | -    | 20   | ns |  |

#### **Electrical Isolation**

| Creep path input-output                     |                         | 7.6 | -   | - | mm    |

|---------------------------------------------|-------------------------|-----|-----|---|-------|

| Max $\Delta V/\Delta t$ at $\Delta V = TBD$ | 10 kV used at 1000 Vp-p |     | TBD |   | kV/μs |

#### **Operating Conditions**

| Operating Temperature | T <sub>OP</sub> | 0 | - | + 85  | °C |

|-----------------------|-----------------|---|---|-------|----|

| Storage Temperature   | T <sub>ST</sub> | 0 | - | + 100 | °C |

#### Notes:

(1) IPK is limited by the JFET gate-source voltage (VGS) and gate resistor (RG). Pulse width is fixed at 100 ns. Connected to APTJC120AM13VCT1AG.

Preliminary

## Demo Board SGDR2500P2

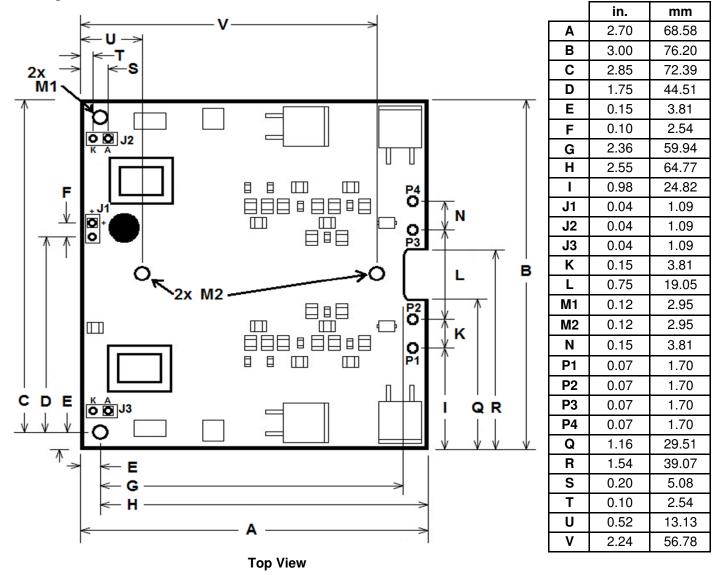

#### Package Pinout

|    | Pin Descriptions |                                    |            |                |                             |  |  |  |  |

|----|------------------|------------------------------------|------------|----------------|-----------------------------|--|--|--|--|

| J1 | VCC              | Voltage supply                     | P1         | SL             | Low side source connection  |  |  |  |  |

| J2 | V <sub>H</sub>   | High side PWM (opto-coupler input) | P2         | GL             | Low side gate connection    |  |  |  |  |

| J3 | VL               | Low side PWM (opto-coupler input)  | P3         | G <sub>H</sub> | High side gate connection   |  |  |  |  |

|    |                  |                                    | <b>P</b> 4 | S <sub>H</sub> | High side source connection |  |  |  |  |

#### **Package Dimensions**

Preliminary

## Demo Board SGDR2500P2

Published by SemiSouth Laboratories, Inc. 201 Research Boulevard Starkville, MS 39759 USA © SemiSouth Laboratories, Inc. 2011

Information in this document supersedes and replaces all information previously supplied.

Information in this document is provided solely in connection with SemiSouth products. SemiSouth Laboratories, Inc. reserves the right to make changes, corrections, modifications or improvements, to this document without notice.

No license, express or implied to any intellectual property rights is granted under this document.

Unless expressly approved in writing by an authorized representative of SemiSouth, SemiSouth products are not designed, authorized or warranted for use in military, aircraft, space, life saving, or life sustaining applications, nor in products or systems