# **Micron StrataFlash Embedded Memory**

- P/N PC28F128G18xx

- P/N PC28F256G18xx

- P/N PC28F512G18xx

- **P/N PC28F00AG18xx**

### **Features**

- · High-Performance Read, Program and Erase

- 96 ns initial read access

- 108 MHz with zero wait-state synchronous burst reads: 7 ns clock-to-data output

- 133 MHz with zero wait-state synchronous burst reads: 5.5 ns clock-to-data output

- 8-, 16-, and continuous-word synchronous-burst Reads

- Programmable WAIT configuration

- Customer-configurable output driver impedance

- Buffered Programming: 2.0 µs/Word (typ), 512-Mbit 65 nm

- Block Erase: 0.9 s per block (typ)

- 20 µs (typ) program/erase suspend

- Architecture

- 16-bit wide data bus

- Multi-Level Cell Technology

- Symmetrically-Blocked Array Architecture

- 256-Kbyte Erase Blocks

- 1-Gbit device: Eight 128-Mbit partitions

- 512-Mbit device: Eight 64-Mbit partitions

- 256-Mbit device: Eight 32-Mbit partitions

- 128-Mbit device: Eight 16-Mbit partitions

- Read-While-Program and Read-While-Erase

- Status Register for partition/device status

- Blank Check feature

- Quality and Reliability

- Expanded temperature: -30 °C to +85 °C

- Minimum 100,000 erase cycles per block

- 65nm Process Technology

- Power

- Core voltage: 1.7 V 2.0 V

- I/O voltage: 1.7 V 2.0 V

- Standby current: 60 µA (typ) for 512-Mbit, 65 nm

- Deep Power-Down mode: 2 µA (typ)

- Automatic Power Savings mode

- 16-word synchronous-burst read current: 23 mA (typ) @ 108 MHz; 24 mA (typ) @ 133 MHz

- Software

- Micron<sup>®</sup> Flash data integrator (FDI) optimized

- Basic command set (BCS) and extended command set (ECS) compatible

- Common Flash interface (CFI) capable

- Security

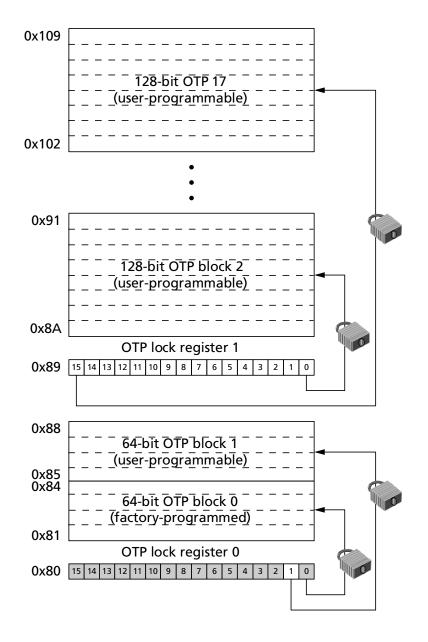

- One-time programmable (OTP) space 64 unique factory device identifier bits 2112 user-programmable OTP bits

- Absolute write protection:  $V_{PP}$  = GND

- Power-transition erase/program lockout

- Individual zero latency block locking

- Individual block lock-down

- Density and packaging

- 128Mb, 256Mb, 512Mbit, and 1-Gbit

- Address-data multiplexed and non-multiplexed interfaces

- 64-Ball Easy BGA

1

### Contents

| General Description                             |    |

|-------------------------------------------------|----|

| Functional Overview                             | 8  |

| Configuration and Memory Map                    | 9  |

| Device ID                                       | 12 |

| Package Dimensions                              | 13 |

| Signal Assignments                              | 14 |

| Signal Descriptions                             | 15 |

| Bus Interface                                   | 17 |

| Reset                                           | 17 |

| Standby                                         | 17 |

| Output Disable                                  | 17 |

| Asynchronous Read                               | 18 |

| Synchronous Read                                | 18 |

| Burst Wrapping                                  | 18 |

| End-of-Wordline Delay                           | 19 |

| Write                                           | 20 |

| Command Definitions                             |    |

| Status Register                                 | 24 |

| Clear Status Register                           | 25 |

| Read Configuration Register                     | 26 |

| Programming the Read Configuration Register     | 27 |

| Extended Configuration Register                 | 28 |

| Output Driver Control                           | 28 |

| Programming the Extended Configuration Register | 29 |

| Read Operations                                 |    |

| Read Array                                      | 30 |

| Read ID                                         | 30 |

| Read CFI                                        | 31 |

| Read Status Register                            | 31 |

| WAIT Operation                                  | 32 |

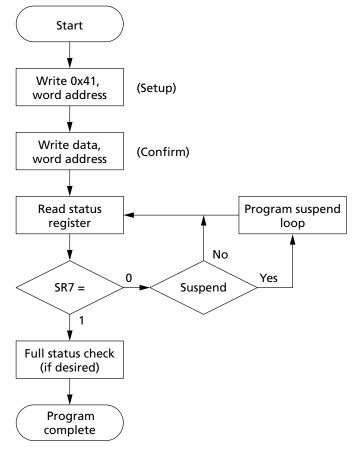

| Programming Modes                               | 33 |

| Control Mode                                    | 33 |

| Object Mode                                     | 34 |

| Program Operations                              | 38 |

| Single-Word Programming                         | 38 |

| Buffered Programming                            |    |

| Buffered Enhanced Factory Programming           |    |

| Erase Operations                                |    |

| BLOCK ERASE                                     | 42 |

| SUSPEND and RESUME Operations                   | 43 |

| SUSPEND Operation                               | 43 |

| RESUME Operation                                |    |

| BLANK CHECK Operation                           |    |

| Block Lock                                      |    |

| One-Time Programmable Operations                |    |

| Programming OTP Area                            |    |

| Reading OTP Area                                |    |

| Global Main-Array Protection                    |    |

| Dual Operation                                  |    |

| Power and Reset Specifications                  |    |

#### 128Mb, 256Mb, 512Mb, 1Gb StrataFlash Memory Features

| The second se | 50    |

|-----------------------------------------------------------------------------------------------------------------|-------|

| Initialization                                                                                                  |       |

| Power-Up and Down                                                                                               |       |

| Reset                                                                                                           |       |

| Automatic Power Saving                                                                                          |       |

| Power Supply Decoupling                                                                                         | . 55  |

| Electrical Specifications                                                                                       | . 56  |

| Electrical Specifications – DC Current and Voltage Characteristics and Operating Conditions                     | . 57  |

| Electrical Specifications – AC Characteristics and Operating Conditions                                         |       |

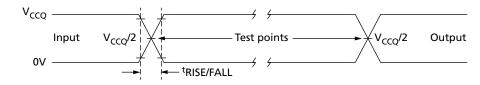

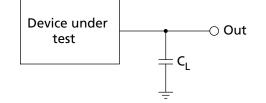

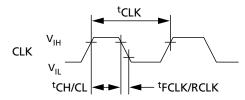

| AC Test Conditions                                                                                              |       |

| AC Read Specifications                                                                                          |       |

| AC Read Specifications (CLK-Latching, 133 MHz)                                                                  |       |

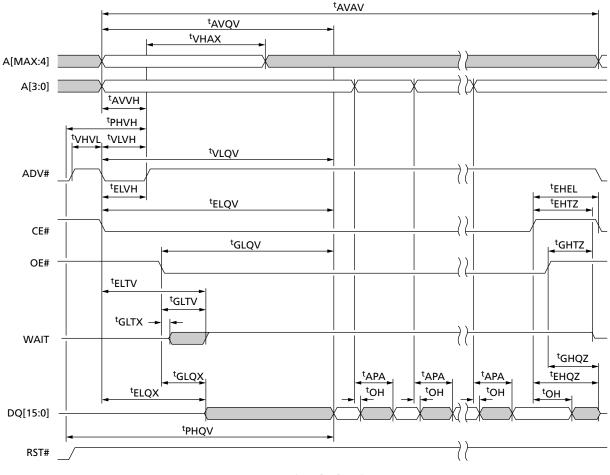

| AC Read Timing                                                                                                  |       |

| AC Write Specifications                                                                                         | . 73  |

| Electrical Specifications – Program/Erase Characteristics                                                       |       |

| Common Flash Interface                                                                                          |       |

| READ CFI Structure Output                                                                                       |       |

| CFI ID String                                                                                                   |       |

| System Interface Information                                                                                    |       |

| Device Geometry Definition                                                                                      |       |

| Primary Micron-Specific Extended Query                                                                          |       |

| Flowcharts                                                                                                      |       |

| AADM Mode                                                                                                       |       |

| AADM Feature Overview                                                                                           |       |

| AADM Mode Enable (RCR[4] = 1)                                                                                   |       |

| Bus Cycles and Address Capture                                                                                  | . 109 |

| WAIT Behavior                                                                                                   |       |

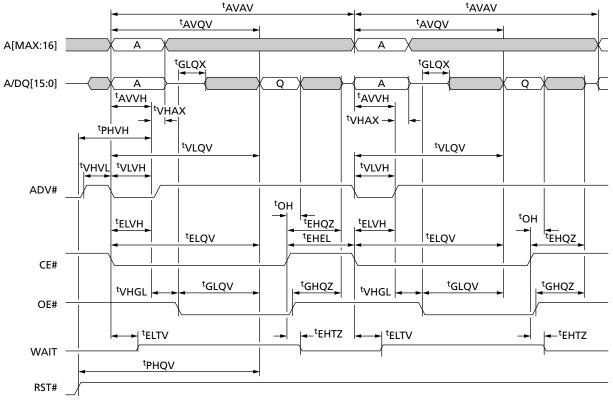

| Asynchronous READ and WRITE Cycles                                                                              |       |

| Asynchronous READ Cycles                                                                                        |       |

| Asynchronous WRITE Cycles                                                                                       | . 112 |

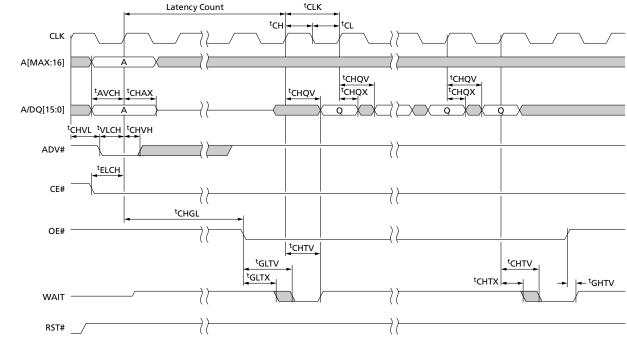

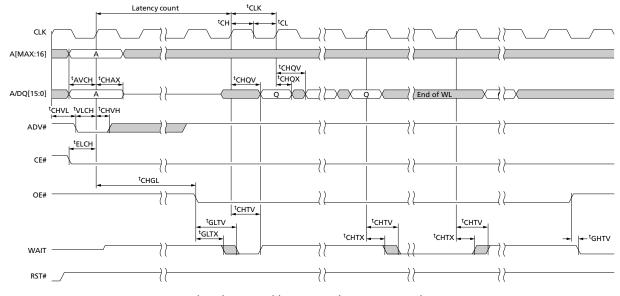

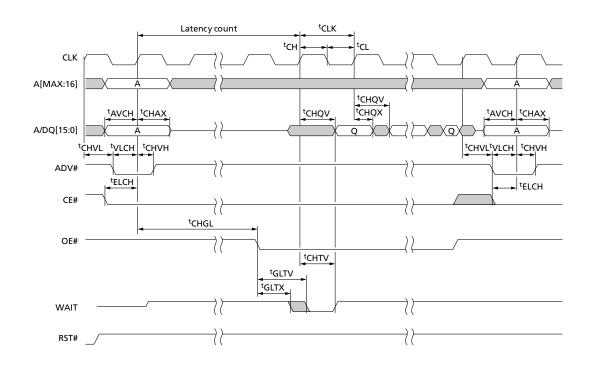

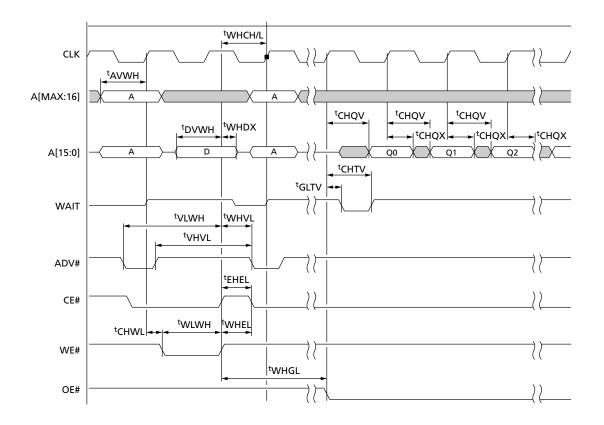

| Synchronous READ and WRITE Cycles                                                                               |       |

| Synchronous READ Cycles                                                                                         |       |

| Synchronous WRITE Cycles                                                                                        | . 116 |

| System Boot                                                                                                     | . 116 |

| Ordering Information                                                                                            | . 117 |

| Revision History                                                                                                | . 118 |

| Rev. F – 8/11                                                                                                   | . 118 |

| Rev. E – 8/11                                                                                                   | . 118 |

| Rev. D – 5/11                                                                                                   | . 118 |

| Rev. C – 2/11                                                                                                   | . 118 |

| Rev. B – 12/10                                                                                                  | . 118 |

| Rev. A – 12/10                                                                                                  | . 118 |

|                                                                                                                 |       |

### **List of Figures**

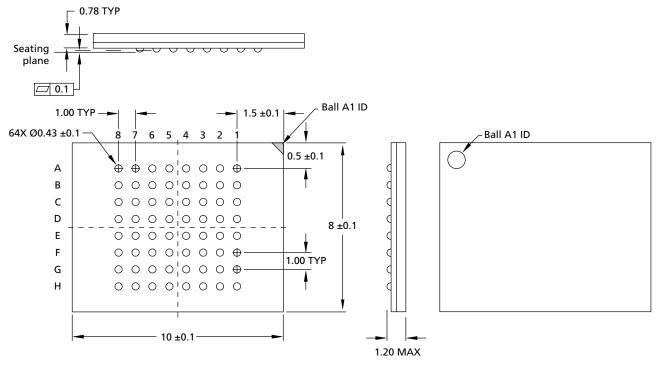

| Figure 1:  | 64-Ball Easy BGA (8mm x 10mm x 1.2mm)                                   | 13  |

|------------|-------------------------------------------------------------------------|-----|

|            | 64-Ball Easy BGA (Top View, Balls Down)                                 |     |

|            | Main Array Word Lines                                                   |     |

|            | Wrap/No-Wrap Example                                                    |     |

|            | End-of-Wordline Delay                                                   |     |

|            | Two-Cycle Command Sequence                                              |     |

| Figure 7:  | Single-Cycle Command Sequence                                           | 21  |

|            | READ Cycle Between WRITE Cycles                                         |     |

|            | Illegal Command Sequence                                                |     |

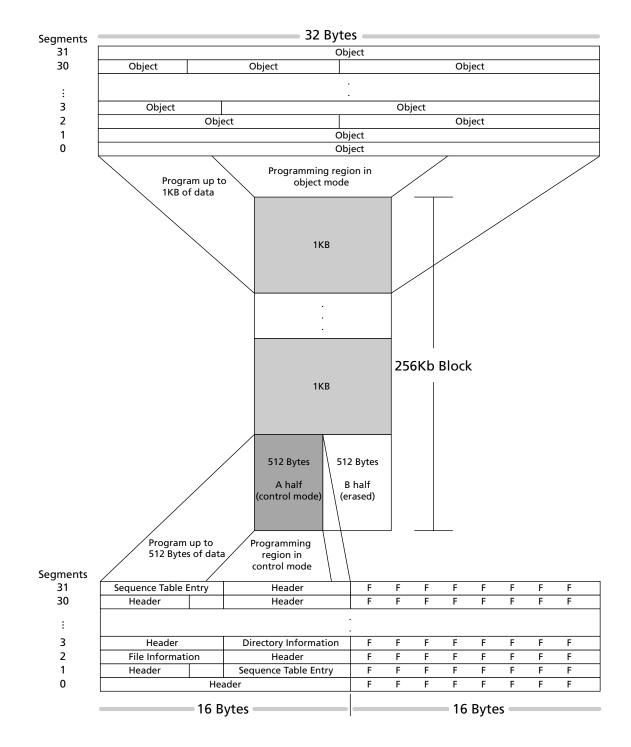

| Figure 10: | Configurable Programming Regions: Control Mode and Object Mode          | 34  |

|            | Configurable Programming Regions: Control Mode and Object Mode Segments |     |

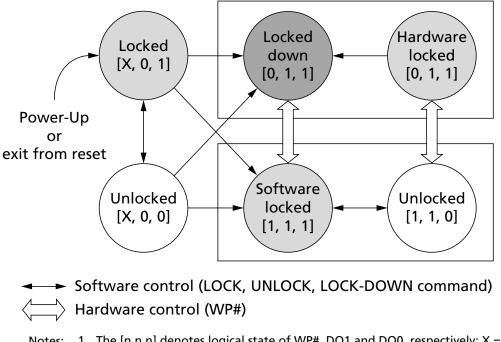

|            | BLOCK LOCK Operations                                                   |     |

| 0          | OTP Area Map                                                            |     |

|            | V <sub>PP</sub> Supply Connection Example                               |     |

| Figure 15: | RESET Operation Waveforms                                               | 54  |

|            | AC Input/Output Reference Waveform                                      |     |

|            | Transient Equivalent Testing Load Circuit                               |     |

|            | Clock Input AC Waveform                                                 |     |

|            | Asynchronous Page-Mode Read (Non-MUX)                                   |     |

|            | Synchronous 8- or 16-Word Burst Read (Non-MUX)                          |     |

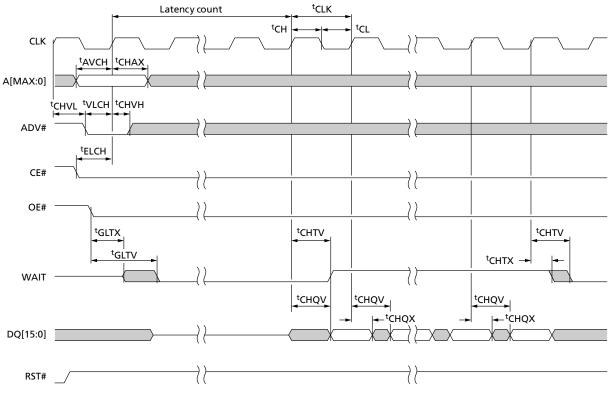

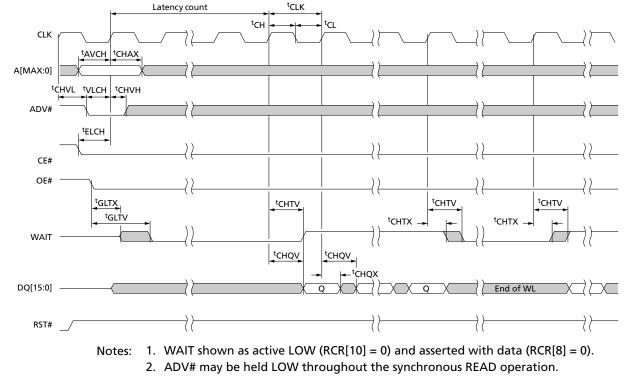

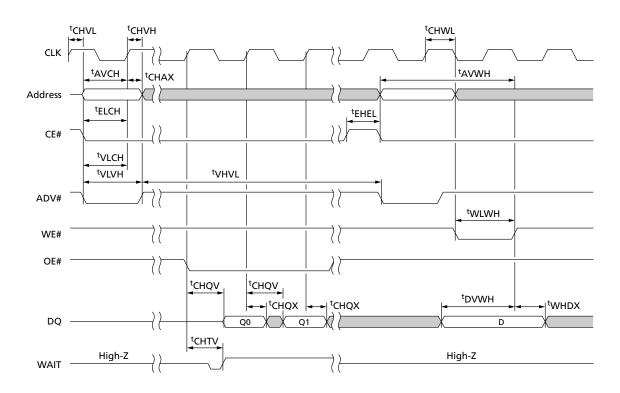

|            | Synchronous Continuous Misaligned Burst Read (Non-MUX)                  |     |

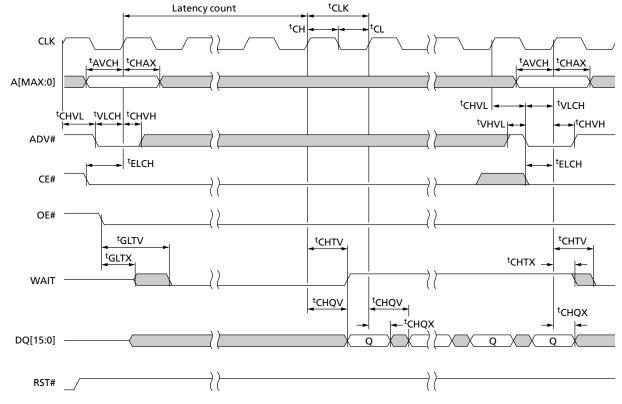

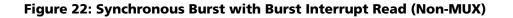

|            | Synchronous Burst with Burst Interrupt Read (Non-MUX)                   |     |

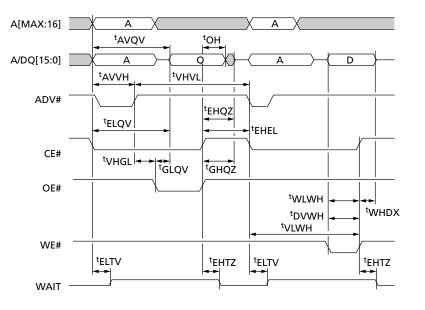

|            | Asynchronous Single-Word Read                                           |     |

|            | Synchronous 8- or 16-Word Burst Read (A/D MUX)                          |     |

|            | Synchronous Continuous Misaligned Burst Read (A/D MUX)                  |     |

|            | Synchronous Burst with Burst-Interrupt (AD-Mux)                         |     |

|            | Write Timing                                                            |     |

| Figure 28: | Write to Write (Non-Mux)                                                | 75  |

| Figure 29: | Async Read to Write (Non-Mux)                                           | 75  |

|            | Write to Async Read (Non-Mux)                                           |     |

| Figure 31: | Sync Read to Write (Non-Mux)                                            | 76  |

| Figure 32: | Write to Sync Read (Non-Mux)                                            | 77  |

| Figure 33: | Write to Write (AD-Mux)                                                 | 77  |

| Figure 34: | Async Read to Write (AD-Mux)                                            | 78  |

| Figure 35: | Write to Async Read (AD-Mux)                                            | 78  |

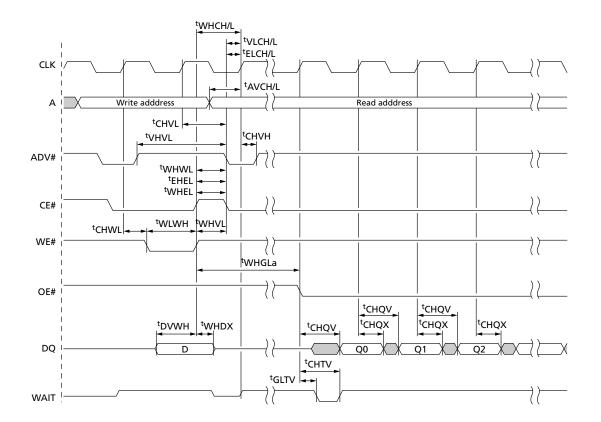

|            | Sync Read to Write (AD-Mux)                                             |     |

| Figure 37: | Write to Sync Read (AD-Mux)                                             | 79  |

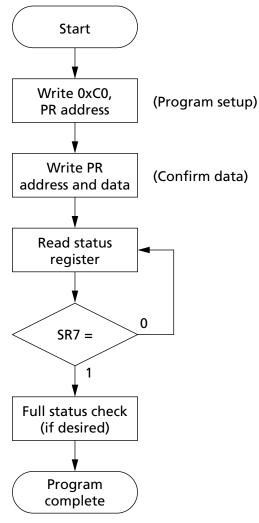

|            | Word Program Procedure                                                  |     |

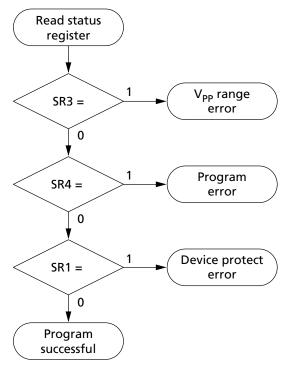

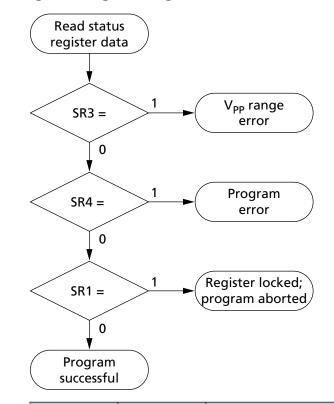

|            | Word Program Full Status Check Procedure                                |     |

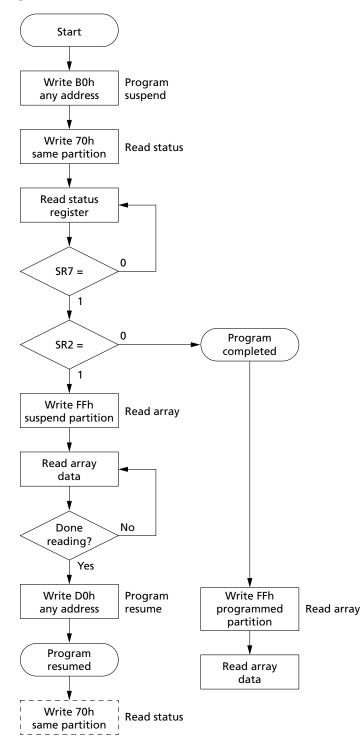

| Figure 40: | Program Suspend/Resume Procedure                                        | 94  |

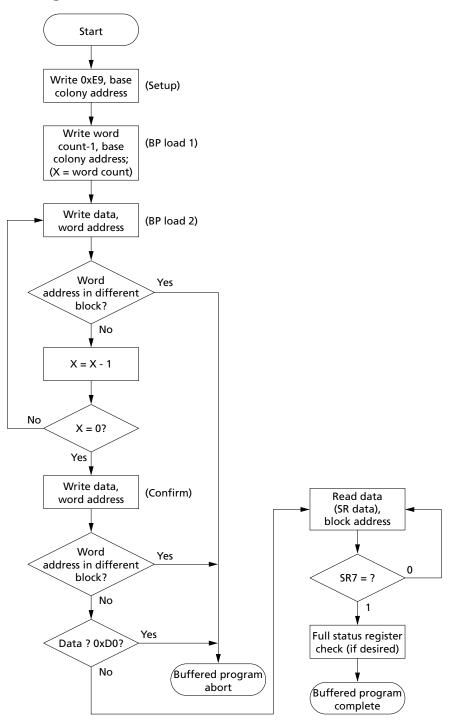

|            | Buffer Programming Procedure                                            |     |

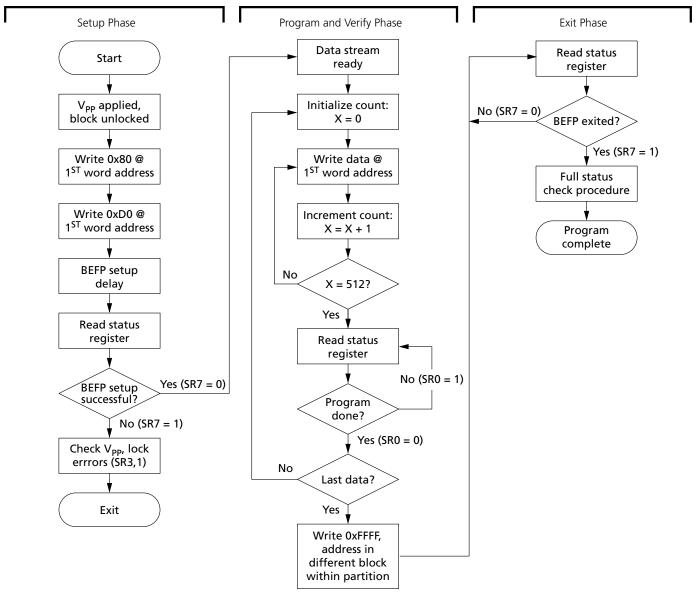

| Figure 42: | Buffered Enhanced Factory Programming (BEFP) Procedure                  | 98  |

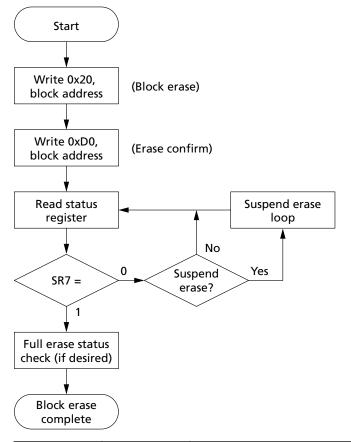

| Figure 43: | Block Erase Procedure                                                   | 100 |

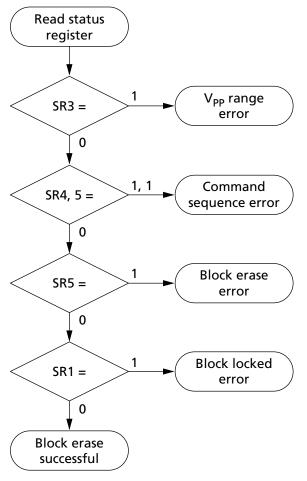

|            | Block Erase Full Status Check Procedure                                 |     |

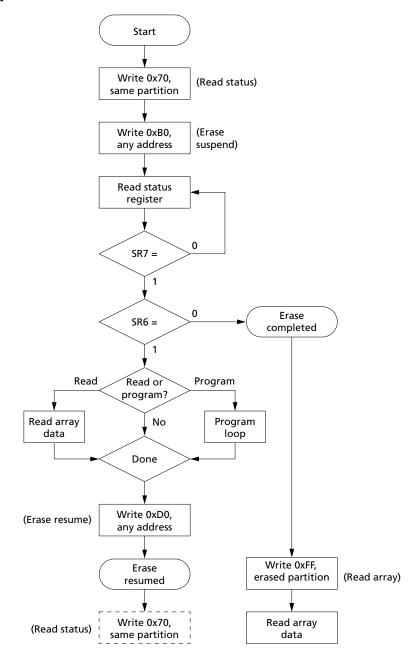

| Figure 45: | Erase Suspend/Resume Procedure                                          | 102 |

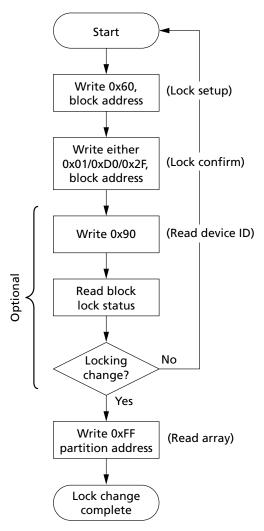

| Figure 46: | Block Lock Operations Procedure                                         | 104 |

|            | Protection Register Programming Procedure                               |     |

|            | Protection Register Programming Full Status Check Procedure             |     |

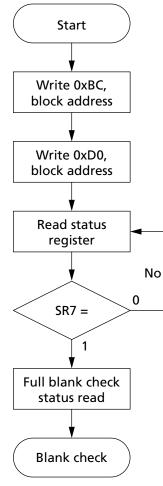

| Figure 49: | Blank Check Procedure                                                   | 107 |

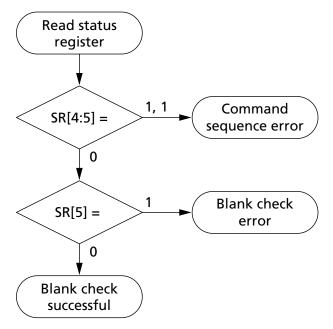

| Figure 50: | Blank Check Full Status Check Procedure                                 | 108 |

#### 128Mb, 256Mb, 512Mb, 1Gb StrataFlash Memory Features

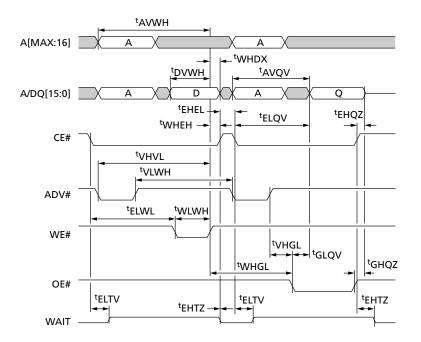

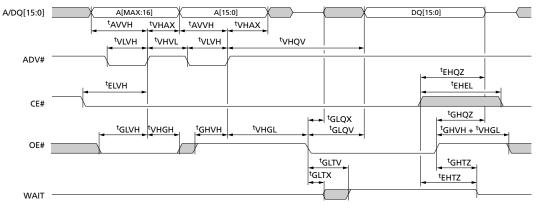

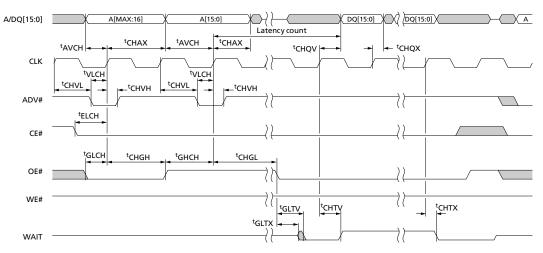

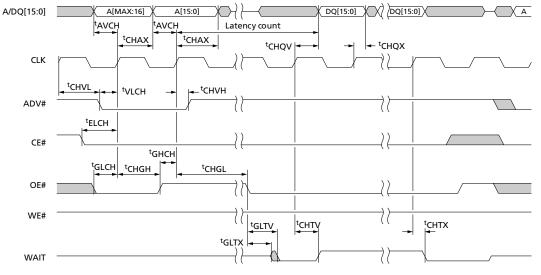

| Figure 51: | AADM Asynchronous READ Cycle (Latching A[MAX:0])                                | 111 |

|------------|---------------------------------------------------------------------------------|-----|

| Figure 52: | AADM Asynchronous READ Cycle (Latching A[15:0] only)                            | 111 |

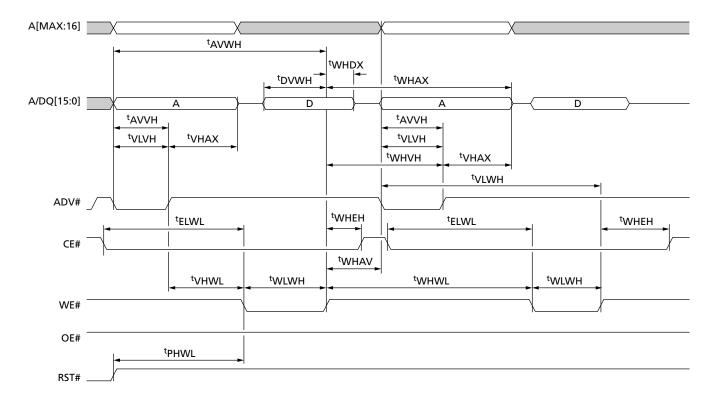

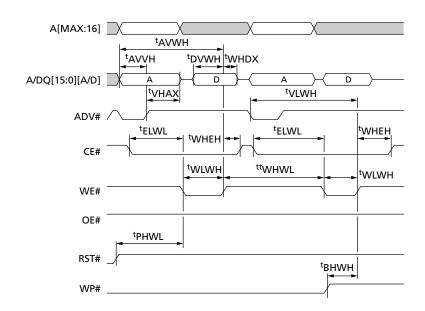

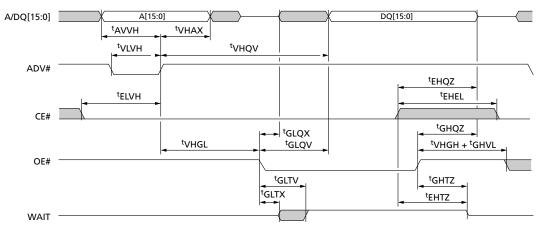

| Figure 53: | AADM Asynchronous WRITE Cycle (Latching A[MAX:0])                               | 112 |

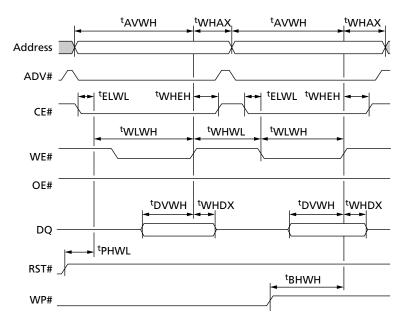

| Figure 54: | AADM Asynchronous WRITE Cycle (Latching A[15:0] only)                           | 113 |

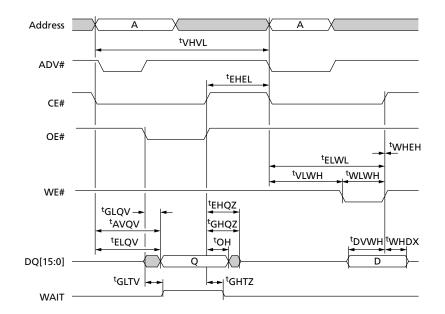

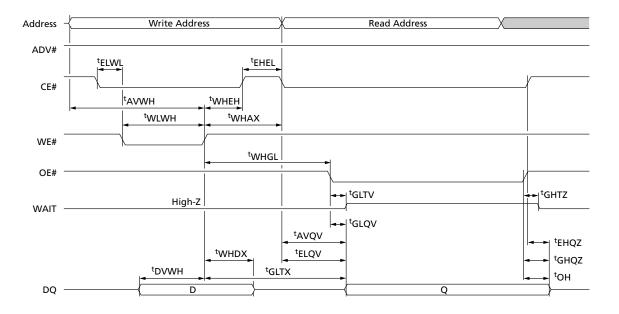

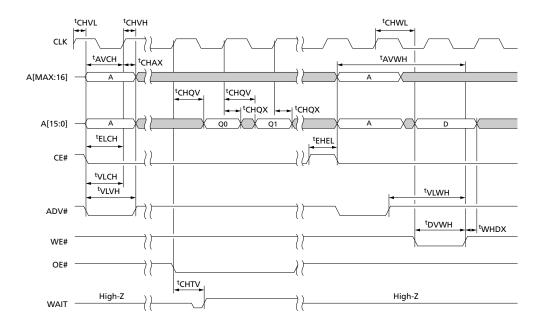

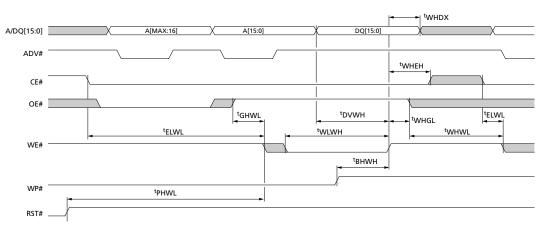

| Figure 55: | AADM Synchronous Burst READ Cycle (ADV# De-asserted Between Address Cycles)     |     |

| Figure 56: | AADM Synchronous Burst READ Cycle (ADV# Not De-asserted Between Address Cycles) |     |

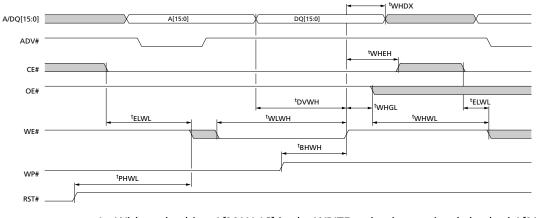

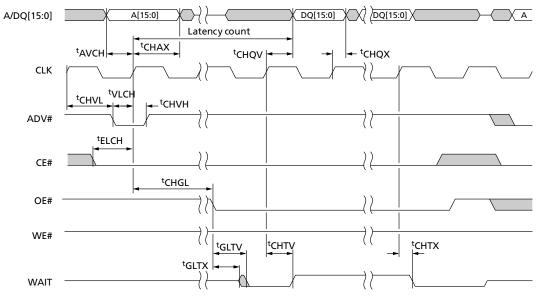

| Figure 57: | AADM Synchronous Burst READ Cycle (Latching A[15:0] only)                       |     |

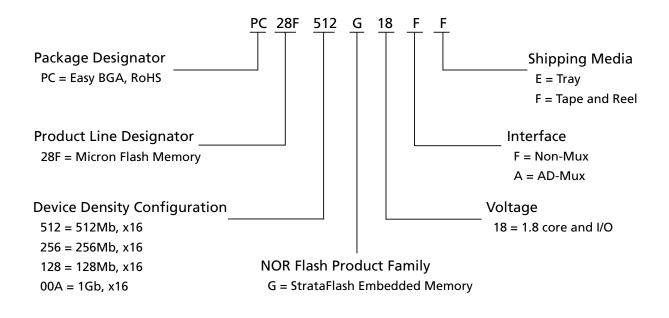

| Figure 58: | Part Number Chart for G18 Components                                            |     |

### **List of Tables**

| Table 1: Main Array Memory Map – 128Mb, 256Mb                                             |    |

|-------------------------------------------------------------------------------------------|----|

| Table 2: Main Array Memory Map – 512Mb, 1Gb                                               |    |

| Table 3: Device ID Codes                                                                  |    |

| Table 4:    Signal Descriptions                                                           |    |

| Table 5: Address Mapping for Address/Data Mux Mode                                        | 16 |

| Table 6: Bus Control Signals                                                              |    |

| Table 7: Command Set                                                                      |    |

| Table 8: Status Register Bit Definitions (Default Value = 0080h)                          | 24 |

| Table 9: CLEAR STATUS REGISTER Command Bus Cycles                                         | 25 |

| Table 10: Read Configuration Register Bit Definitions                                     | 26 |

| Table 11: Supported Clock Frequencies                                                     | 26 |

| Table 12: PROGRAM READ CONFIGURATION REGISTER Bus Cycles                                  | 27 |

| Table 13: Extended Configuration Register Bit Definitions (Default Value = 0004h)         | 28 |

| Table 14:    Output Driver Control Characteristics                                        | 28 |

| Table 15: Program Extended Configuration Register Command Bus Cycles                      | 29 |

| Table 16:    READ MODE Command Bus Cycles                                                 |    |

| Table 17: Device Information                                                              | 31 |

| Table 18: WAIT Behavior Summary – Non-MUX                                                 | 32 |

| Table 19: WAIT Behavior Summary – AD MUX                                                  | 32 |

| Table 20:    Programming Region Next State                                                | 37 |

| Table 21: PROGRAM Command Bus Cycles                                                      | 38 |

| Table 22: BEFP Requirements and Considerations                                            | 40 |

| Table 23:    ERASE Command Bus Cycle                                                      | 42 |

| Table 24: Valid Commands During Suspend                                                   | 43 |

| Table 25: SUSPEND and RESUME Command Bus Cycles                                           | 44 |

| Table 26: BLANK CHECK Command Bus Cycles                                                  |    |

| Table 27: BLOCK LOCK Command Bus Cycles                                                   | 46 |

| Table 28: Block Lock Configuration                                                        | 47 |

| Table 29: Program OTP Area Command Bus Cycles                                             | 48 |

| Table 30: Dual Operation Restrictions                                                     | 52 |

| Table 31: Power Sequencing                                                                |    |

| Table 32: Reset Specifications                                                            |    |

| Table 33: Absolute Maximum Ratings                                                        |    |

| Table 34: Operating Conditions                                                            |    |

| Table 35: DC Current Characteristics and Operating Conditions                             |    |

| Table 36:    DC Voltage Characteristics and Operating Conditions                          |    |

| Table 37: AC Input Requirements                                                           | 61 |

| Table 38: Test Configuration Load Capacitor Values for Worst Case Speed Conditions        | 61 |

| Table 39:   Capacitance                                                                   |    |

| Table 40: AC Read Specifications (CLK-Latching, 133 MHz), V <sub>CCQ</sub> = 1.7V to 2.0V |    |

| Table 41: AC Write Specifications                                                         |    |

| Table 42: Program/Erase Characteristics                                                   |    |

| Table 43: Example of CFI Output (x16 Device) as a Function of Device and Mode             |    |

| Table 44: CFI Database: Addresses and Sections                                            |    |

| Table 45:   CFI ID String                                                                 | 82 |

| Table 46:    System Interface Information                                                 | 82 |

| Table 47: Device Geometry                                                                 | 83 |

| Table 48: Block Region Map Information                                                    | 84 |

| Table 49: Primary Micron-Specific Extended Query                                          |    |

| Table 50:    One Time Programmable (OTP) Space Information                                | 87 |

#### 128Mb, 256Mb, 512Mb, 1Gb StrataFlash Memory Features

| Table 51: | Burst Read Informaton                                         | 88  |

|-----------|---------------------------------------------------------------|-----|

| Table 52: | Partition and Block Erase Region Information                  | 89  |

| Table 53: | Partition Region 1 Information: Top and Bottom Offset/Address | 89  |

| Table 54: | Partition and Erase Block Map Information                     | 91  |

| Table 55: | AADM Asynchronous and Latching Timings                        | 110 |

| Table 56: | AADM Asynchronous Write Timings                               | 112 |

| Table 57: | AADM Synchronous Timings                                      | 113 |

| Table 58: | Valid Line Items                                              | 117 |

### **General Description**

Micron's 65nm device is the latest generation of StrataFlash<sup>®</sup> wireless memory featuring flexible, multiple-partition, dual-operation architecture. The device provides highperformance, asynchronous read mode and synchronous-burst read mode using 1.8V low-voltage, multilevel cell (MLC) technology.

The multiple-partition architecture enables background programming or erasing to occur in one partition while code execution or data reads take place in another partition. This dual-operation architecture also allows two processors to interleave code operations while PROGRAM and ERASE operations take place in the background. The multiple partitions allow flexibility for system designers to choose the size of the code and data segments.

The device is manufactured using 65nm process technologies and is available in industry-standard chip scale packaging.

### **Functional Overview**

This device provides high read and write performance at low voltage on a 16-bit data bus. The multi-partition architecture provides read-while-write and read-while-erase capability, with individually erasable memory blocks sized for optimum code and data storage.

This device is offered in densities from 128Mb to 1Gb. The device supports synchronous burst reads up to 133 MHz using enhanced CLK latching for all densities on 45nm.

Upon initial power-up or return from reset, the device defaults to asynchronous read mode. Configuring the read configuration register enables synchronous burst mode reads. In synchronous burst mode, output data is synchronized with a user-supplied clock signal. In continuous-burst mode, a data read can traverse partition boundaries. A WAIT signal simplifies synchronizing the CPU to the memory.

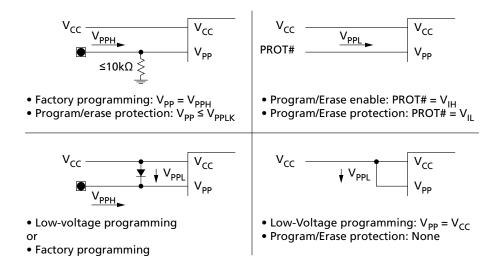

Designed for low-voltage applications, the device supports READ operations with  $V_{CC}$  at 1.8V, and ERASE and PROGRAM operations with  $V_{PP}$  at 1.8V or 9.0V.  $V_{CC}$  and  $V_{PP}$  can be tied together for a simple, ultra low-power design. In addition to voltage flexibility, a dedicated  $V_{PP}$  connection provides complete data protection when  $V_{PP}$  is less than  $V_{PPLK}$ .

A status register provides status and error conditions of ERASE and PROGRAM operations.

One-time programmable (OTP) area enables unique identification that can be used to increase security. Additionally, the individual block lock feature provides zero-latency block locking and unlocking to protect against unwanted program or erase of the array.

The device offers power-savings features, including automatic power savings mode, standby mode, and deep power-down mode. For power savings, the device automatically enters APS following a READ cycle. Standby is initiated when the system deselects the device by de-asserting CE#. Deep power-down provides the lowest power consumption and is enabled by programming in the extended configuration register. DPD is initiated by asserting the DPD pin.

### **Configuration and Memory Map**

The device features a symmetrical block architecture. The main array of the 128Mb device is divided into eight 16Mb partitions. Each partition is divided into eight 256KB blocks (8 x 8 = 64 blocks).

The main array of the 256Mb device is divided into eight 32Mb partitions. Each partition is divided into sixteen 256KB blocks ( $8 \times 16 = 128$  blocks).

The main array of the 512Mb device is divided into eight 64Mb partitions. Each partition is divided into thirty-two 256KB blocks (8 x 32 = 256 blocks).

The main array of the 1Gb device is divided into eight 128Mb partitions. Each partition is divided into sixty-four 256KB blocks ( $8 \times 64 = 512$  blocks).

Each block is divided into as many as 256 1KB programming regions. Each region is divided into as many as thirty-two 32-byte segments

#### Table 1: Main Array Memory Map - 128Mb, 256Mb

|           |              | 128Mb   |                 | 256Mb        |         |                 |  |

|-----------|--------------|---------|-----------------|--------------|---------|-----------------|--|

| Partition | Size<br>(Mb) | Block # | Address Range   | Size<br>(Mb) | Block # | Address Range   |  |

| 7         | 16           | 63      | 07E0000-07FFFFF | 32           | 127     | FF0000-FFFFFF   |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         | •               |              |         |                 |  |

|           |              | 56      | 0700000-071FFFF |              | 112     | FD0000-FDFFFF   |  |

| 6         | 16           | 55      | 06E0000-06FFFFF | 32           | 111     | 0DE0000-0DFFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              | 48      | 060000-061FFFF  |              | 96      | 0C00000-0C1FFFF |  |

| 5         | 16           | 47      | 05E0000-05FFFFF | 32           | 95      | 0BE0000-0BFFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              | 40      | 050000-051FFFF  |              | 80      | 0A00000-0A1FFFF |  |

| 4         | 16           | 39      | 04E0000-04FFFFF | 32           | 79      | 09E0000-09FFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              | 32      | 0400000-041FFFF |              | 64      | 080000-081FFFF  |  |

| 3         | 16           | 31      | 03E0000-03FFFFF | 32           | 63      | 07E0000-07FFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         | .               |              |         |                 |  |

|           |              |         | · .             |              | · .     | ·               |  |

|           |              | 24      | 030000-031FFFF  |              | 48      | 060000-061FFFF  |  |

|           |              | 128Mb   | 256Mb           |              |         |                 |

|-----------|--------------|---------|-----------------|--------------|---------|-----------------|

| Partition | Size<br>(Mb) | Block # | Address Range   | Size<br>(Mb) | Block # | Address Range   |

| 2         | 16           | 23      | 02E0000-02FFFFF | 32           | 47      | 05E0000-05FFFFF |

|           |              |         |                 |              |         |                 |

|           |              |         |                 |              |         |                 |

|           |              |         |                 |              | •       |                 |

|           |              | 16      | 0200000-021FFFF |              | 32      | 0400000-041FFFF |

| 1         | 16           | 15      | 01E0000-01FFFFF | 32           | 31      | 03E0000-03FFFFF |

|           |              |         |                 | •            |         |                 |

|           |              |         |                 |              |         |                 |

|           |              |         |                 |              | •       |                 |

|           |              | 8       | 0100000-011FFFF |              | 16      | 020000-021FFFF  |

| 0         | 16           | 7       | 00E0000-00FFFFF | 32           | 15      | 01E0000-01FFFFF |

|           |              |         |                 |              |         |                 |

|           |              |         |                 |              |         |                 |

|           |              | •       | •               |              | •       | •               |

|           |              | 0       | 000000-001FFFF  |              | 0       | 0000000-001FFFF |

#### Table 1: Main Array Memory Map – 128Mb, 256Mb (Continued)

#### Table 2: Main Array Memory Map – 512Mb, 1Gb

|           |              | 512Mb   |                 |              | 1Gb     |                 |

|-----------|--------------|---------|-----------------|--------------|---------|-----------------|

| Partition | Size<br>(Mb) | Block # | Address Range   | Size<br>(Mb) | Block # | Address Range   |

| 7         | 64           | 255     | 1FE0000-1FFFFFF | 128          | 511     | 3FE0000-3FFFFFF |

|           |              |         |                 | •            | •       |                 |

|           |              |         |                 |              |         |                 |

|           |              | •       | •               |              | •       | •               |

|           |              | 224     | 1C00000-1C1FFFF |              | 448     | 3800000-381FFFF |

| 6         | 64           | 223     | 1BE0000-1BFFFFF | 128          | 447     | 37E0000-37FFFFF |

|           |              |         |                 | •            |         |                 |

|           |              |         |                 |              | •       |                 |

|           |              | •       | •               |              | •       | •               |

|           |              | 192     | 1800000-181FFFF |              | 384     | 300000-301FFFF  |

| 5         | 64           | 191     | 17E0000-17FFFFF | 128          | 383     | 2FE0000-2FFFFFF |

|           |              |         |                 |              |         |                 |

|           |              | •       |                 |              |         |                 |

|           |              | •       |                 |              |         |                 |

|           |              | 160     | 1400000-141FFFF |              | 320     | 2800000-281FFFF |

#### Table 2: Main Array Memory Map – 512Mb, 1Gb (Continued)

|           |              | 512Mb   |                 | 1Gb          |         |                 |  |

|-----------|--------------|---------|-----------------|--------------|---------|-----------------|--|

| Partition | Size<br>(Mb) | Block # | Address Range   | Size<br>(Mb) | Block # | Address Range   |  |

| 4         | 64           | 159     | 13E0000-13FFFFF | 128          | 319     | 27E0000-27FFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              | •       | •               | -            | •       |                 |  |

|           |              | 128     | 1000000-101FFFF |              | 256     | 200000-201FFFF  |  |

| 3         | 64           | 127     | OFE0000-OFFFFFF | 128          | 255     | 1FE0000-1FFFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              | •       | •               |              | •       | •               |  |

|           |              | 96      | 030000-031FFFF  |              | 192     | 1800000-181FFFF |  |

| 2         | 64           | 95      | OBE0000-0BFFFFF | 128          | 191     | 17E0000-17FFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         |                 |  |

|           |              | 64      | 080000-081FFFF  |              | 128     | 1000000-101FFFF |  |

| 1         | 64           | 63      | 07E0000-07FFFFF | 128          | 127     | OFE0000-OFFFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         | •               |  |

|           |              | •       |                 | _            |         |                 |  |

|           |              | 32      | 0400000-041FFFF |              | 64      | 0800000-081FFFF |  |

| 0         | 64           | 31      | 03E0000-03FFFFF | 128          | 63      | 07E0000-07FFFFF |  |

|           |              |         |                 |              |         |                 |  |

|           |              |         |                 |              |         | · ·             |  |

|           |              | · ·     | · ·             |              |         |                 |  |

|           |              | 0       | 000000-001FFFF  |              | 0       | 0000000-001FFFF |  |

### **Device ID**

To order parts or to obtain a data sheet, contact the factory.

#### **Table 3: Device ID Codes**

| Density | Product | Device Identifier Code (Hex) |

|---------|---------|------------------------------|

| 128Mb   | Non-MUX | 8900                         |

|         | A/D MUX | 8903                         |

| 256Mb   | Non-MUX | 8901                         |

|         | A/D MUX | 8904                         |

| 512Mb   | Non-MUX | 887E                         |

|         | A/D MUX | 8881                         |

| 1024Mb  | Non-MUX | 88B0                         |

|         | A/D MUX | 88B1                         |

### **Package Dimensions**

#### Figure 1: 64-Ball Easy BGA (8mm x 10mm x 1.2mm)

Note: 1. All dimensions are in millimeters.

### **Signal Assignments**

Figure 2: 64-Ball Easy BGA (Top View, Balls Down)

|   | • 1        | 2                                              | 3                                              | 4                                           | 5                                           | 6                                              | 7                                              | 8                                              |

|---|------------|------------------------------------------------|------------------------------------------------|---------------------------------------------|---------------------------------------------|------------------------------------------------|------------------------------------------------|------------------------------------------------|

| А |            | $\left(\begin{array}{c} \\ \end{array}\right)$ | $\left(\begin{array}{c} \\ \end{array}\right)$ | $\left(\begin{array}{c} \end{array}\right)$ | ( )                                         | $\left(\begin{array}{c} \\ \end{array}\right)$ | $\left(\begin{array}{c} \\ \end{array}\right)$ | $\left(\begin{array}{c} \\ \end{array}\right)$ |

| В | A1         | A6                                             | A8                                             |                                             | A13                                         | V <sub>CC</sub>                                | A18<br>()<br>A19                               |                                                |

| с | A2         | V <sub>SS</sub>                                | A9                                             | CĒ#                                         | A14                                         | A25                                            | A19                                            | A26                                            |

| D | A3         | A7                                             | À10                                            | À12                                         | À15                                         | WP#                                            | A20                                            | A21                                            |

|   | A4         | A5                                             | A11                                            | RST#                                        | V <sub>CCQ</sub>                            | Vcco                                           | A16                                            | A17                                            |

| E | ( )<br>DQ8 | DQ1                                            | DQ9                                            | DQ3                                         | DQ4                                         | CLK                                            | DQ15                                           | RFU                                            |

| F | RFU        | ()<br>DQ0                                      | ()<br>DQ10                                     | ())<br>DQ11                                 | ()<br>DQ12                                  | ()<br>ADV#                                     | ( )<br>WAIT                                    | ()<br>OE#                                      |

| G |            | $\left(\begin{array}{c} \end{array}\right)$    | $(\overline{})$                                | $\left(\begin{array}{c} \end{array}\right)$ | $\left(\begin{array}{c} \end{array}\right)$ | $\left(\begin{array}{c} \\ \end{array}\right)$ | $(\overline{)}$                                |                                                |

| Н | A23        | <b>RFU</b>                                     | DQ2                                            | V CCQ                                       | DQ5                                         |                                                | DQ14                                           |                                                |

|   | RFU        | V <sub>SSQ</sub>                               | $V_{CC}$                                       | V <sub>SS</sub>                             | DQ13                                        | V <sub>SSQ</sub>                               | DQ7                                            | A24                                            |

Notes:

1. A1 is the least significant address bit.

- 2. B6 is A25 for 512Mb densities and above; otherwise, it is a no connect (NC).

- 3. B8 is A26 for 1Gb density; otherwise, it is a no connect (NC).

- 4. G1 is A23 for 128Mb density and above; otherwise, it is a no connect (NC).

- 5. H8 is A24 for 256Mb density and above; otherwise, it is a no connect (NC).

## **Signal Descriptions**

#### **Table 4: Signal Descriptions**

| Symbol                | Туре         | Description                                                                                                                                                                                                  |

|-----------------------|--------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Non-MUX               |              |                                                                                                                                                                                                              |

| A[MAX:1]              | Input        | Address inputs: Address inputs for all READ/WRITE cycles.                                                                                                                                                    |

| DQ[15:0]              | Input/Output | <b>Data:</b> Data or command inputs during WRITE cycles; data, status, or device information outputs during READ cycles.                                                                                     |

| A/D MUX               |              |                                                                                                                                                                                                              |

| A[MAX:17]             | Input        | Address inputs: Upper address inputs for all READ/WRITE cycles.                                                                                                                                              |

| ADQ[15:0]             | Input/Output | <b>Address or data:</b> Lower address inputs during the address phase for all READ/WRITE cycles; data or command inputs during WRITE cycles; data, status, or device information outputs during READ cycles. |

| <b>Control Signal</b> | S            |                                                                                                                                                                                                              |

| CE#                   | Input        | <b>Chip enable:</b> LOW true input. When LOW, CE# selects the die; when HIGH, CE# deselects the die and places it in standby.                                                                                |

| OE#                   | Input        | Output enable: LOW true input. Must be LOW for READs and HIGH for WRITEs.                                                                                                                                    |

| WE#                   | Input        | Write enable: LOW true input. Must be LOW for WRITEs and HIGH for READs.                                                                                                                                     |

| CLK                   | Input        | Clock: Synchronizes burst READ operations with the host controller.                                                                                                                                          |

| ADV#                  | Input        | <b>Address valid:</b> LOW true input. When LOW, ADV# enables address inputs. For syn-<br>chronous burst READs, address inputs are latched on the rising edge.                                                |

| WP#                   | Input        | Write protect: LOW true input. When LOW, WP# enables block lock down; when HIGH, WP# disables block lock down.                                                                                               |

| RST#                  | Input        | <b>Reset:</b> LOW true input. When LOW, RST# inhibits all operations; must be HIGH for normal operations.                                                                                                    |

| V <sub>PP</sub>       | Input        | <b>Erase/program voltage:</b> Enables voltage for PROGRAM and ERASE operations. Array contents cannot be altered when V <sub>PP</sub> is at or below V <sub>PPLK</sub> .                                     |

| WAIT                  | Output       | <b>WAIT:</b> Configurable HIGH or LOW true output. When asserted, WAIT indicates DQ[15:0] is invalid; when de-asserted, WAIT indicates DQ[15:0] is valid.                                                    |

| V <sub>cc</sub>       | Power        | <b>Core power:</b> Supply voltage for core circuits. All operations are inhibited when $V_{CC}$ is at or below $V_{LKO}$ .                                                                                   |

| V <sub>CCQ</sub>      | Power        | <b>I/O power:</b> Supply voltage for all I/O drivers. All operations are inhibited when $V_{CCQ}$ is at or below $V_{LKOQ}$ .                                                                                |

| V <sub>SS</sub>       | Power        | <b>Logic ground:</b> Core logic ground return. Connect all $V_{SS}$ balls to system ground; do not float any $V_{SS}$ balls.                                                                                 |

| V <sub>SSQ</sub>      | Power        | <b>I/O ground:</b> I/O driver ground return. Connect all $V_{SSQ}$ balls to system ground; do not float any $V_{SSQ}$ balls.                                                                                 |

| Address | A/D Mux<br>Configuration | AADM Mode<br>(RCR Bit 4 = 1) and OE# = 1 | AADM Mode<br>(RCR Bit 4 = 1) and OE# = 0 |

|---------|--------------------------|------------------------------------------|------------------------------------------|

| A1      | DQ0                      | A1                                       | A17                                      |

| A2      | DQ1                      | A2                                       | A18                                      |

| A3      | DQ2                      | A3                                       | A19                                      |

| A4      | DQ3                      | A4                                       | A20                                      |

| A5      | DQ4                      | A5                                       | A21                                      |

| A6      | DQ5                      | A6                                       | A22                                      |

| A7      | DQ6                      | A7                                       | A23                                      |

| A8      | DQ7                      | A8                                       | A24                                      |

| A9      | DQ8                      | A9                                       | A25                                      |

| A10     | DQ9                      | A10                                      | A26                                      |

| A11     | DQ10                     | A11                                      | _                                        |

| A12     | DQ11                     | A12                                      | _                                        |

| A13     | DQ12                     | A13                                      | _                                        |

| A14     | DQ13                     | A14                                      | _                                        |

| A15     | DQ14                     | A15                                      | _                                        |

| A16     | DQ15                     | A16                                      | _                                        |

| A17     | A17                      | GND                                      | GND                                      |

| A18     | A18                      | GND                                      | GND                                      |

| A19     | A19                      | GND                                      | GND                                      |

| A20     | A20                      | GND                                      | GND                                      |

| A21     | A21                      | GND                                      | GND                                      |

| A22     | A22                      | GND                                      | GND                                      |

| A23     | A23                      | GND                                      | GND                                      |

| A24     | A24                      | GND                                      | GND                                      |

| A25     | A25                      | GND                                      | GND                                      |

| A26     | A26                      | GND                                      | GND                                      |

#### Table 5: Address Mapping for Address/Data Mux Mode

### **Bus Interface**

The bus interface uses CMOS-compatible address, data, and bus control signals for all bus WRITE and bus READ operations. The address signals are input only, the data signals are input/output (I/O), and the bus control signals are input only. The address inputs are used to specify the internal device location during bus READ and bus WRITE operations. The data I/Os carry commands, data, or status to and from the device. The control signals are used to select and deselect the device, indicate a bus READ or bus WRITE operation, synchronize operations, and reset the device.

Do not float any inputs. All inputs must be driven or terminated for proper device operation. Some features may use additional signals. See Signal Descriptions for descriptions of these signals.

The following table shows the logic levels that must be applied to the bus control signal inputs for the bus operations listed.

| X = Don't Care; High = V <sub>IH</sub> ; Low = V <sub>IL</sub> |      |      |         |        |      |      |         |          |

|----------------------------------------------------------------|------|------|---------|--------|------|------|---------|----------|

| Bus Operations                                                 | RST# | CE#  | CLK     | ADV#   | OE#  | WE#  | Address | Data I/O |

| Reset                                                          | Low  | Х    | Х       | Х      | Х    | Х    | Х       | High-Z   |

| Standby                                                        | High | High | Х       | Х      | Х    | Х    | Х       | High-Z   |

| Output Disable                                                 | High | Х    | Х       | Х      | High | Х    | Х       | High-Z   |

| Asynchronous Read                                              | High | Low  | Х       | Low    | Low  | High | Valid   | Output   |

| Synchronous Read                                               | High | Low  | Running | Toggle | Low  | High | Valid   | Output   |

| Write                                                          | High | Low  | Х       | Х      | High | Low  | Valid   | Input    |

#### **Table 6: Bus Control Signals**

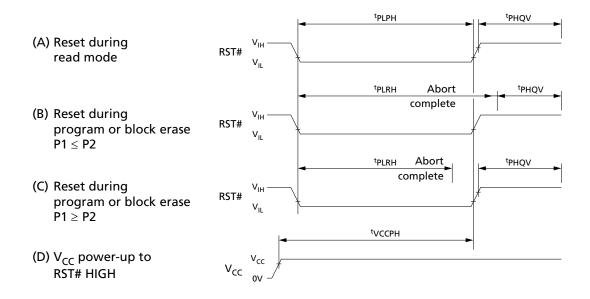

#### Reset

RST# LOW places the device in reset, where device operations are disabled; inputs are ignored, and outputs are placed in High-Z.

Any ongoing ERASE or PROGRAM operation will be aborted and data at that location will be indeterminate.

RST# HIGH enables normal device operations. A minimum delay is required before the device is able to perform a bus READ or bus WRITE operation. See AC specifications.

#### Standby

RST# HIGH and CE# HIGH place the device in standby, where all other inputs are ignored, outputs are placed in High-Z (independent of the level placed on OE#), and power consumption is substantially reduced.

Any ongoing ERASE or PROGRAM operation continues in the background and the device draws active current until the operation has finished.

#### **Output Disable**

When OE# is deasserted with CE# asserted, the device outputs are disabled. Output pins are placed in a high-impedance state. WAIT is deasserted in AD-muxed devices and driven to High-Z in non-multiplexed devices.

#### **Asynchronous Read**

For RCR15 = 1 (default), CE# LOW and OE# LOW place the device in asynchronous bus read mode:

- RST# and WE# must be held HIGH; CLK must be tied either HIGH or LOW.

- Address inputs must be held stable throughout the access, or latched with ADV#.

- ADV# must be held LOW or can be toggled to latch the address.

- Valid data is output on the data I/Os after <sup>t</sup>AVQV, <sup>t</sup>ELQV, <sup>t</sup>VLQV, or <sup>t</sup>GLQV, whichever is satisfied last.

Asynchronous READ operations are independent of the voltage level on V<sub>PP</sub>.

For asynchronous page reads, subsequent data words are output <sup>t</sup>APA after the least significant address bit(s) are toggled: 16-word page buffer, A[3:0].

#### Synchronous Read

For RCR15 = 0, CE# LOW, OE# LOW, and ADV# LOW place the device in synchronous bus read mode:

- RST# and WE# must be held HIGH.

- CLK must be running.

- The first data word is output <sup>t</sup>CHQV after the latency count has been satisfied.

- For array reads, the next address data is output <sup>t</sup>CHQV after valid CLK edges until the burst length is satisfied.

- For nonarray reads, the same address data is output <sup>t</sup>CHQV after valid CLK edges until the burst length is satisfied.

The address for synchronous read operations is latched on the ADV# rising edge or the first rising CLK edge after ADV# low, whichever occurs first for devices that support up to 108 MHz. For devices that support up to 133 MHz, the address is latched on the last CLK edge when ADV# is low.

#### **Burst Wrapping**

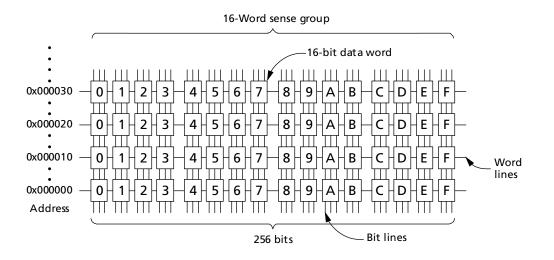

Data stored within the memory array is arranged in rows or word lines. During synchronous burst reads, data words are sensed in groups from the array. The starting address of a synchronous burst read determines which word within the wordgroup is output first, and subsequent words are output in sequence until the burst length is satisfied.

The setting of the burst wrap bit (RCR3) determines whether synchronous burst reads will wrap within the wordgroup or continue on to the next wordgroup.

#### Figure 3: Main Array Word Lines

#### Figure 4: Wrap/No-Wrap Example

#### **End-of-Wordline Delay**

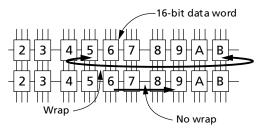

Output delays may occur when the burst sequence crosses the first end-of-wordline boundary onto the start of the next wordline.

No delays occur if the starting address is sense-group aligned or if the burst sequence never crosses a wordline boundary. However, if the starting address is not sense-group aligned, the worst-case end-of-wordline delay is one clock cycle less than the initial access latency count used. This delay occurs only once during the burst access. WAIT informs the system of this delay when it occurs.

#### 3 5 6 7 8 9 В С Е 0x000020 2 4 D Δ F Т 0x000010 2 3 8 С 0 1 4 5 6 7 9 В D Е Ш Ш EOWL delay

#### Figure 5: End-of-Wordline Delay

#### Write

CE# LOW and WE# LOW place the device in bus write mode, where RST# and OE# must be HIGH, CLK and ADV# are ignored, input data and address are sampled on the rising edge of WE# or CE#, whichever occurs first.

During a write operation in muxed devices, address is latched during the rising edge of ADV# OR CE# whichever occurs first and Data is latched during the rising edge of WE# OR CE# whichever occurs first.

Bus WRITE cycles are asynchronous only.

The following conditions apply when a bus WRITE cycle occurs immediately before, or immediately after, a bus READ cycle:

- When transitioning from a bus READ cycle to a bus WRITE cycle, CE# or ADV# must toggle after OE# goes HIGH.

- When in synchronous read mode (RCR15 = 0; burst clock running), bus WRITE cycle timings <sup>t</sup>VHWL (ADV# HIGH to WE# LOW), <sup>t</sup>CHWL (CLK HIGH to WE# LOW), and <sup>t</sup>WHCH (WE# HIGH to CLK HIGH) must be met.

- When transitioning from a bus WRITE cycle to a bus READ cycle, CE# or ADV# must toggle after WE# goes HIGH.

### **Command Definitions**

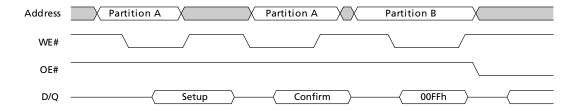

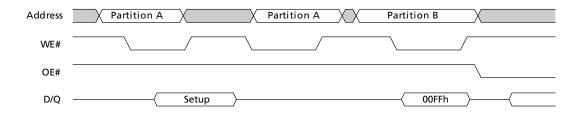

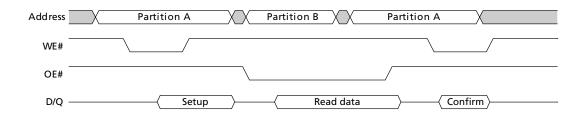

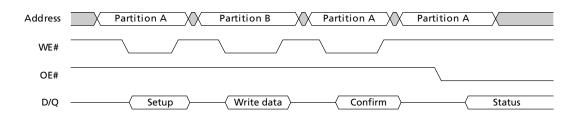

Commands are written to the device to control all operations. Some commands are two-cycle commands that use a SETUP and a CONFIRM command; other commands are single-cycle commands that use only a SETUP command followed by a data READ cycle or data WRITE cycle. Valid commands and their associated command codes are shown in the table below.

The device supports READ-While-WRITE and READ-While-ERASE operations with bus cycle granularity, not command granularity. That is, both bus WRITE cycles of a two-cycle command do not need to occur as back-to-back bus WRITE cycles to the device; READ cycles may occur between the two write WRITE cycles of a two-cycle command.

However, a WRITE operation must not occur between the two bus WRITE cycles of a two-cycle command; this will cause a command sequence error (SR[7,5,4] = 1).

Due to the large buffer size of devices, the system interrupt latency may be impacted during the buffer fill phase of a buffered programming operation. Please refer to the relevant Application Note to implement a software solution for your system

#### Figure 6: Two-Cycle Command Sequence

#### Figure 7: Single-Cycle Command Sequence

#### Figure 8: READ Cycle Between WRITE Cycles

#### **Figure 9: Illegal Command Sequence**

#### Table 7: Command Set

| Command                                      | Code<br>(Setup/Confirm) | Description                                                                                                                                                                                                                                                          |

|----------------------------------------------|-------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Register Operations                          |                         |                                                                                                                                                                                                                                                                      |

| PROGRAM READ CONFIGURA-<br>TION REGISTER     | 0060h/0003h             | Programs the read configuration register. The desired read con-<br>figuration register value is placed on the address bus, and writ-<br>ten to the read configuration register when the CONFIRM com-<br>mand is issued.                                              |

| PROGRAM EXTENDED CONFIGU-<br>RATION REGISTER | 0060h/0004h             | Programs the extended configuration register. The desired ex-<br>tended configuration register value is placed on the address bus,<br>and written to the read configuration register when the CON-<br>FIRM command is issued.                                        |

| PROGRAM OTP AREA                             | 00C0h                   | Programs OTP area and OTP lock registers. The desired register data is written to the addressed register on the next WRITE cycle.                                                                                                                                    |

| CLEAR STATUS REGISTER                        | 0050h                   | Clears all error bits in the status register.                                                                                                                                                                                                                        |

| Read Mode Operations                         |                         |                                                                                                                                                                                                                                                                      |

| READ ARRAY                                   | 00FFh                   | Places the addressed partition in read array mode. Subsequent reads outputs array data.                                                                                                                                                                              |

| READ STATUS REGISTER                         | 0070h                   | Places the addressed partition in read status mode. Subsequent reads outputs status register data.                                                                                                                                                                   |

| READ ID                                      | 0090h                   | Places the addressed partition in read ID mode. Subsequent reads from specified address offsets output unique device information.                                                                                                                                    |

| READ CFI                                     | 0098h                   | Places the addressed partition in read CFI mode. Subsequent reads from specified address offsets output CFI data.                                                                                                                                                    |

| Array Programming Operations                 | 5                       |                                                                                                                                                                                                                                                                      |

| SINGLE-WORD PROGRAM                          | 0041h                   | Programs a single word into the array. Data is written to the ar-<br>ray on the next WRITE cycle. The addressed partition automati-<br>cally switches to read status register mode.                                                                                  |

| BUFFERED PROGRAM                             | 00E9h/00D0h             | Initiates and executes a BUFFERED PROGRAM operation. Addi-<br>tional bus READ/WRITE cycles are required between the and<br>confirm commands to properly perform this operation. The ad-<br>dressed partition automatically switches to read status register<br>mode. |

#### **Table 7: Command Set (Continued)**

| Command                              | Code<br>(Setup/Confirm) | Description                                                                                                                                                                                                                                                                    |

|--------------------------------------|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| BUFFERED ENHANCED FACTORY<br>PROGRAM | 0080h/00D0h             | Initiates and executes a BUFFERED ENHANCED FACTORY PRO-<br>GRAM operation. Additional bus READ/WRITE cycles are re-<br>quired after the CONFIRM command to properly perform this<br>operation. The addressed partition automatically switches to<br>read status register mode. |

| Block Erase Operations               |                         |                                                                                                                                                                                                                                                                                |

| BLOCK ERASE                          | 0020h/00D0h             | Erases a single, addressed block. The ERASE operation commen-<br>ces when the CONFIRM command is issued. The addressed parti-<br>tion automatically switches to read status register mode.                                                                                     |

| Security Operations                  |                         |                                                                                                                                                                                                                                                                                |

| Lock Block                           | 0060h/0001h             | Sets the lock bit of the addressed block.                                                                                                                                                                                                                                      |

| Unlock Block                         | 0060h/00D0h             | Clears the lock bit of the addressed block.                                                                                                                                                                                                                                    |

| Lock-Down Block                      | 0060h/002Fh             | Sets the lock-down bit of the addressed block.                                                                                                                                                                                                                                 |

| Other Operations                     |                         |                                                                                                                                                                                                                                                                                |

| SUSPEND                              | 00B0h                   | Initiates a suspend of a PROGRAM or BLOCK ERASE operation<br>already in progress when issued to any device address<br>SR[6] = 1 indicates erase suspend<br>SR[2] = 1 indicates program suspend                                                                                 |

| RESUME                               | 00D0h                   | Resumes a suspended PROGRAM or BLOCK ERASE operation<br>when issued to any device address. A program suspend nested<br>within an erase suspend is resumed first.                                                                                                               |

| BLANK CHECK                          | 00BCh/00D0h             | Performs a blank check of an addressed block. The addressed partition automatically switches to read status register mode.                                                                                                                                                     |

### **Status Register**

The status register is a 16-bit, read-only register that indicates device status, region status, and operating errors. Upon power-up or exit from reset, the status register defaults to 0080h (device ready, no errors).

The status register has status bits and error bits. Status bits are set and cleared by the device; error bits are only set by the device. Error bits are cleared using the CLEAR STA-TUS REGISTER command or by resetting the device.

To read from the status register, first issue the READ STATUS REGISTER command and then read from the device. Note that some commands automatically switch from read mode to read status register mode.

#### Table 8: Status Register Bit Definitions (Default Value = 0080h)

| Bit   | Name                                                                             | Description                                                                                                                                                                                                                                                                                                                                                                                            |

|-------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15:10 | Reserved                                                                         | Reserved for future use; these bits will always be set to zero                                                                                                                                                                                                                                                                                                                                         |

| 9:8   | Partition program er-<br>ror                                                     | <ul> <li>SR[9]/SR[8]</li> <li>0 0 = Region program successful</li> <li>1 0 = Region program error: Attempted write with object data to control mode region</li> <li>0 1= Region-program error: Attempted rewrite to object mode region</li> <li>1 1 = Region-program error: Attempted write using illegal command (SR[4] will also be set along with SR[8,9] for the above error conditions</li> </ul> |

| 7     | Device status                                                                    | 0 = Device is busy; SR[9,8,6:1] are invalid, SR[0] is valid<br>1 = Device is ready; SR[9:8], SR[6:1] are valid                                                                                                                                                                                                                                                                                         |

| 6     | Erase suspend                                                                    | 0 = Erase suspend not in effect<br>1 = Erase suspend in effect                                                                                                                                                                                                                                                                                                                                         |

| 5:4   | Erase error/blank check<br>error<br>program error<br>(command sequence<br>error) | <ul> <li>SR[5]/SR[4]</li> <li>0 0 = PROGRAM or ERASE operation successful</li> <li>0 1 = Program error: operation aborted</li> <li>1 0 = Erase error: Operation aborted; Blank check error: Operation failed</li> <li>1 1 = Command sequence error: Command aborted</li> </ul>                                                                                                                         |

| 3     | V <sub>PP</sub> error                                                            | $0 = V_{PP}$ within acceptable limits during program or erase<br>$1 = V_{PP} < V_{PPLK}$ during program or erase; operation aborted                                                                                                                                                                                                                                                                    |

| 2     | Program suspend                                                                  | 0 = Program suspend not in effect<br>1 = Program suspend in effect                                                                                                                                                                                                                                                                                                                                     |

| 1     | Block lock error                                                                 | 0 = Block not locked during program or erase; operation successful<br>1 = Block locked during program or erase; operation aborted                                                                                                                                                                                                                                                                      |

| 0     | Partition status                                                                 | SR[7]/SR[0]<br>0 0 = Active PROGRAM or ERASE operation in addressed partition<br>BEFP: Program or verify complete, or ready for data<br>0 1 = Active PROGRAM or ERASE operation in other partition<br>BEFP: Program or Verify in progress<br>1 0 = No active PROGRAM or ERASE operation in any partition<br>BEFP: Operation complete<br>1 1 = Reserved                                                 |

#### **Clear Status Register**

The status register has status bits and error bits. Status bits are set and cleared by the device; error bits are only set by the device. Error bits are cleared using the CLEAR STA-TUS REGISTER command or by resetting the device.

**Note:** Care should be taken to avoid status register ambiguity. If a command sequence error occurs while in erase suspend, SR[5:4] will be set, indicating a command sequence error. When the ERASE operation is resumed (and finishes), any errors that may have occurred during the ERASE operation will be masked by the command sequence error. To avoid this situation, clear the status register prior to resuming any suspended ERASE operation.

The CLEAR STATUS REGISTER command functions independent of the voltage level on  $V_{PP}$ . Issuing the CLEAR STATUS REGISTER command places the addressed partition in read status register mode. Other partitions are not affected.

#### Table 9: CLEAR STATUS REGISTER Command Bus Cycles

| Command                  | Setup WRITE Cycle | Setup WRITE Cycle | Confirm WRITE Cycle | Confirm WRITE Cycle |

|--------------------------|-------------------|-------------------|---------------------|---------------------|

|                          | Address Bus       | Data Bus          | Address Bus         | Data Bus            |

| CLEAR STATUS<br>REGISTER | Device address    | 0050h             | _                   | -                   |

### **Read Configuration Register**

The read configuration register is a volatile, 16-bit read/write register used to select bus read modes and to configure synchronous burst read behavior of the device.

The read configuration register is programmed using the PROGRAM READ CONFIGU-RATION REGISTER command. To read the read configuration register, issue the READ ID command and then read from offset 0005h.

Upon power-up or exit from reset, the read configuration register defaults to asynchronous mode (RCR15 = 1; all other bits are ignored).

#### **Table 10: Read Configuration Register Bit Definitions**

| Bit   | Name          | Description                                                        |

|-------|---------------|--------------------------------------------------------------------|

| 15    | Read mode     | 0 = Synchronous burst mode                                         |

|       |               | 1 = Asynchronous mode (default)                                    |