# Demonstration board mounting the L6226Q dual full-bridge driver

**Data brief**

### **Features**

- Operating supply voltage from 8 to 52 V

- 2.8 A output peak current (1.4 A DC)

- $R_{DS(on)}$  0.73  $\Omega$  typ. value @  $T_J$  = 25 °C

- Operating frequency up to 100 kHz

- Programmable high-side overcurrent detection and protection

- Diagnostic output

- Paralleled operation

- Cross conduction protection

- Thermal shutdown

- Undervoltage lockout

- Integrated fast free wheeling diodes

The L6226Q is a DMOS dual full-bridge designed for motor control applications, realized in BCD multipower technology. The L6226Q features thermal shutdown and a non-dissipative overcurrent detection on the high-side power MOSFETs plus a diagnostic output that can be easily used to implement the overcurrent protection.

Board description EVAL6226QR

## 1 Board description

Table 1. EVAL6226QR electrical specifications (recommended values)

| Parameter                                     | Value                         |  |

|-----------------------------------------------|-------------------------------|--|

| Supply voltage range (VS)                     | 8 to 52 Vdc                   |  |

| Output current rating (OUTx)                  | up to 1.4 A <sub>r.m.s.</sub> |  |

| Switching frequency                           | up to 100 kHz                 |  |

| Input and enable voltage range                | 0 to + 5 V                    |  |

| OCD pin voltage range                         | -0.3 to 10 V                  |  |

| L6226Q thermal resistance junction-to-ambient | 42°C/W                        |  |

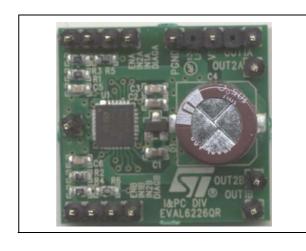

Figure 1. EVAL6226QR demonstration board description

EVAL6226QR Board description

Table 2. EVAL6226QR pin connections

| Name  | Name Type Function |                                                                                                                                                                                               |

|-------|--------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VS    | Power supply       | Bridge A and bridge B power supply                                                                                                                                                            |

| PGND  | Ground             | Power ground terminal                                                                                                                                                                         |

| IN1A  | Logic input        | Bridge A logic input 1                                                                                                                                                                        |

| IN2A  | Logic Input        | Bridge A logic input 2                                                                                                                                                                        |

| ENA   | Logic input        | Bridge A enable (active high). When low, the power DMOSs of bridge A are switched OFF.                                                                                                        |

| IN1B  | Logic input        | Bridge B logic input 1                                                                                                                                                                        |

| IN2B  | Logic input        | Bridge B logic input 2                                                                                                                                                                        |

| ENB   | Logic input        | Bridge B enable (active high). When low, the power DMOSs of bridge B are switched OFF.                                                                                                        |

| DIAGA | Open drain output  | Bridge A overcurrent detection and thermal protection pin.<br>An internal open drain transistor pulls to GND when<br>overcurrent on bridge A is detected or in case of thermal<br>protection. |

| DIAGB | Open drain output  | Bridge B overcurrent detection and thermal protection pin.<br>An internal open drain transistor pulls to GND when<br>overcurrent on bridge B is detected or in case of thermal<br>protection. |

| SGND  | Ground             | Signal ground terminal                                                                                                                                                                        |

| OUT1A | Power output       | Bridge A output 1                                                                                                                                                                             |

| OUT2A | Power output       | Bridge A output 2                                                                                                                                                                             |

| OUT1B | Power output       | Bridge B output 1                                                                                                                                                                             |

| OUT2B | Power output       | Bridge B output 2                                                                                                                                                                             |

Board description EVAL6226QR

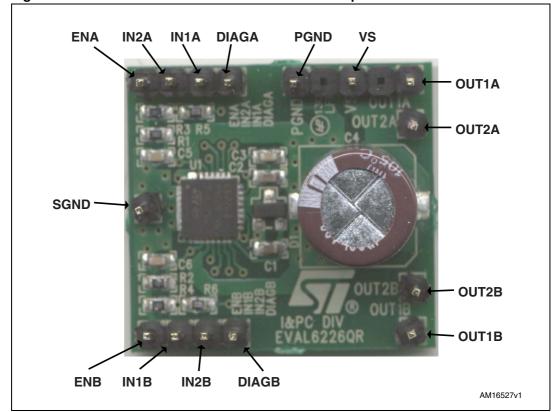

Figure 2. EVAL6226QR schematic

EVAL6226QR Board description

Table 3. EVAL6226QR part list

| Part reference | Part value       | Part description              |

|----------------|------------------|-------------------------------|

| C1             | 220 nF/25 V      | Capacitor                     |

| C2             | 220 nF/63 V      | Capacitor                     |

| C3             | 10 nF/25 V       | Capacitor                     |

| C4             | 100 μF/63 V      | Capacitor                     |

| C5, C6         | 5.6 nF           | Capacitor                     |

| D1             | BAT46SW          | Diodes                        |

| R1, R2, R3, R4 | 100 kΩ 5% 0.25 W | Resistor                      |

| R5, R6         | 10 kΩ 1% 0.25 W  | Resistor                      |

| R9, R10        | 0.4 kΩ1 W        | Resistor                      |

| U1             | L6226Q           | Dual full-bridge in VFQFPN5x5 |

Figure 3. Component placement

Board description EVAL6226QR

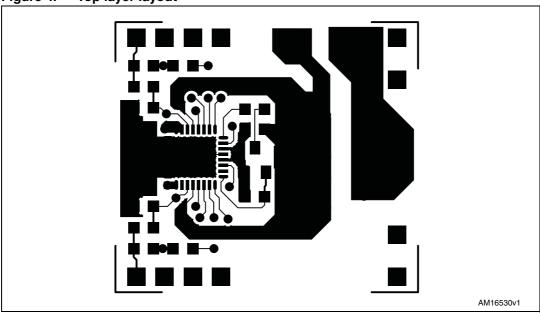

Figure 4. Top layer layout

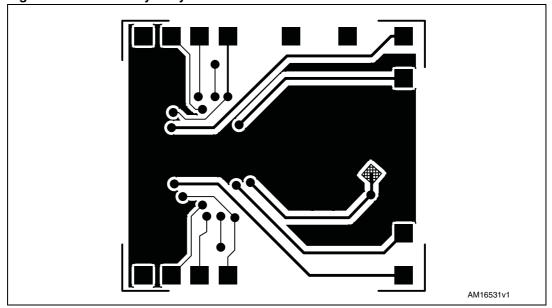

Figure 5. Bottom layer layout

EVAL6226QR Revision history

# 2 Revision history

Table 4. Document revision history

| Date        | Revision | Changes          |

|-------------|----------|------------------|

| 11-Jan-2013 | 1        | Initial release. |

#### **Please Read Carefully:**

Information in this document is provided solely in connection with ST products. STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, modifications or improvements, to this document, and the products and services described herein at any time, without notice.

All ST products are sold pursuant to ST's terms and conditions of sale.

Purchasers are solely responsible for the choice, selection and use of the ST products and services described herein, and ST assumes no liability whatsoever relating to the choice, selection or use of the ST products and services described herein.

No license, express or implied, by estoppel or otherwise, to any intellectual property rights is granted under this document. If any part of this document refers to any third party products or services it shall not be deemed a license grant by ST for the use of such third party products or services, or any intellectual property contained therein or considered as a warranty covering the use in any manner whatsoever of such third party products or services or any intellectual property contained therein.

UNLESS OTHERWISE SET FORTH IN ST'S TERMS AND CONDITIONS OF SALE ST DISCLAIMS ANY EXPRESS OR IMPLIED WARRANTY WITH RESPECT TO THE USE AND/OR SALE OF ST PRODUCTS INCLUDING WITHOUT LIMITATION IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE (AND THEIR EQUIVALENTS UNDER THE LAWS OF ANY JURISDICTION), OR INFRINGEMENT OF ANY PATENT, COPYRIGHT OR OTHER INTELLECTUAL PROPERTY RIGHT.

UNLESS EXPRESSLY APPROVED IN WRITING BY TWO AUTHORIZED ST REPRESENTATIVES, ST PRODUCTS ARE NOT RECOMMENDED, AUTHORIZED OR WARRANTED FOR USE IN MILITARY, AIR CRAFT, SPACE, LIFE SAVING, OR LIFE SUSTAINING APPLICATIONS, NOR IN PRODUCTS OR SYSTEMS WHERE FAILURE OR MALFUNCTION MAY RESULT IN PERSONAL INJURY, DEATH, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE. ST PRODUCTS WHICH ARE NOT SPECIFIED AS "AUTOMOTIVE GRADE" MAY ONLY BE USED IN AUTOMOTIVE APPLICATIONS AT USER'S OWN RISK.

Resale of ST products with provisions different from the statements and/or technical features set forth in this document shall immediately void any warranty granted by ST for the ST product or service described herein and shall not create or extend in any manner whatsoever, any liability of ST.

ST and the ST logo are trademarks or registered trademarks of ST in various countries.

Information in this document supersedes and replaces all information previously supplied.

The ST logo is a registered trademark of STMicroelectronics. All other names are the property of their respective owners.

© 2013 STMicroelectronics - All rights reserved

STMicroelectronics group of companies

Australia - Belgium - Brazil - Canada - China - Czech Republic - Finland - France - Germany - Hong Kong - India - Israel - Italy - Japan - Malaysia - Malta - Morocco - Philippines - Singapore - Spain - Sweden - Switzerland - United Kingdom - United States of America

www.st.com

4