## DEMO MANUAL DC1717A

## LTC4417

## Prioritized PowerPath™ Controller

#### DESCRIPTION

Demonstration circuit DC1717A uses the LTC®4417 to arbitrate between three input supply rails, selecting the highest priority, valid supply to power the load. The rail's priority is defined by the input connection (V1-V3). Each rail has overvoltage and undervoltage thresholds set by external resistors. If the highest priority rail voltage falls out of the defined window (overvoltage or undervoltage), the rail with the next highest priority, which is valid, is

enabled and powers the load. Two or more LTC4417s can be cascaded to provide switchover between more than three rails.

# Design files for this circuit board are available at http://www.linear.com/demo

## **PERFORMANCE SUMMARY** Specifications are at T<sub>A</sub> = 25°C

| SYMBOL                     | PARAMETER                                         | CONDITIONS                                                               | MIN   | TYP  | MAX   | UNITS |

|----------------------------|---------------------------------------------------|--------------------------------------------------------------------------|-------|------|-------|-------|

| V1-V3, V <sub>OUT</sub>    | V1 to V3, V <sub>OUT</sub> Operating Supply Range |                                                                          | 2.5   |      | 36    | V     |

| $\Delta V_{G}$             | Open (VS-VG) Clamp Voltage                        | V <sub>OUT</sub> = 11V, G1 to G3 = Open                                  | 5.4   | 6.2  | 6.7   | V     |

| $\Delta V_{G(SOURCE)}$     | Sourcing (VS-VG) Clamp Voltage                    | $V_{OUT} = 11V, I = -10\mu A$                                            | 5.8   | 6.6  | 7     | V     |

| $\Delta V_{G(SINK)}$       | Sinking (VS-VG) Clamp Voltage                     | V <sub>OUT</sub> = 11V, I = 10μA                                         | 4.5   | 5.2  | 6     | V     |

| $\Delta V_{G(OFF)}$        | G1 to G3 Off (VS-VG) Threshold                    | V1 = V2 = V3 = 2.8V, V <sub>OUT</sub> = 2.6V, G1 to G3 Rising Edge       | 0.12  | 0.35 | 0.6   | V     |

| $\Delta V_{G(SLEW,ON)}$    | G1 to G3 Pull-Down Slew Rate                      | V <sub>OUT</sub> = 11V, C <sub>GATE</sub> = 10nF                         | 4     | 9    | 20    | V/µs  |

| $\Delta V_{G(SLEW,OFF)}$   | G1 to G3 Pull-Up Slew Rate                        | V <sub>OUT</sub> = 11V, C <sub>GATE</sub> = 10nF                         | 7.5   | 13   | 22    | V/µs  |

| I <sub>GATE(LOW)</sub>     | G1 to G3 Low Pull-Down Current                    | $V_{OUT} = 2.6V$ , V1 to V3 = 2.8V, (G1 to G3) = $\Delta V_{G} + 300$ mV | 0.8   | 2    | 7     | μА    |

| V <sub>REV</sub>           | Reverse Voltage Threshold                         | Measure (V1 to V3) – V <sub>OUT</sub> , V <sub>OUT</sub> Falling         | 30    | 120  | 200   | mV    |

| t <sub>G(SWITCHOVER)</sub> | Break-Before-Make Time                            | V <sub>OUT</sub> = 11V, C <sub>GATE</sub> = 10nF                         | 0.7   | 2    | 3     | μs    |

| V <sub>VALID(OL)</sub>     | VALID1 to VALID3 Output Low Voltage               | I = 1mA, (V1 to V3) = 2.5V, V <sub>OUT</sub> = 0V                        |       | 0.2  | 0.55  | V     |

| t <sub>PVALID(OFF)</sub>   | VALID1 to VALID3 Delay OFF from OV/UV Fault       |                                                                          | 5     | 8    | 13    | μs    |

| V <sub>SHDN</sub> (THR)    | SHDN Threshold Voltage                            | SHDN Rising                                                              | 0.4   | 0.8  | 1.2   | V     |

| V <sub>SHDN_EN(HYS)</sub>  | SHDN, EN Threshold Hysteresis                     |                                                                          |       | 100  |       | mV    |

| I <sub>SHDN_EN</sub>       | SHDN, EN Pull-Up Current                          | SHDN = EN = 0V                                                           | -0.5  | -2   | -5    | μА    |

| V <sub>OV_UV(THR)</sub>    | OV1 to O3, UV1 to UV3 Comparator<br>Threshold     | V <sub>OUT</sub> = 11V, OV1 to OV3 Rising, UV1 to UV3 Falling            | 0.985 | 1    | 1.015 | V     |

| V <sub>OV_UV(HYS)</sub>    | OV1 to 03, UV1 to UV3 Comparator<br>Hysteresis    | V <sub>OUT</sub> = 11V                                                   | 15    | 30   | 45    | mV    |

| t <sub>VALID</sub>         | V1 to V3 Validation Time                          |                                                                          | 100   | 256  | 412   | ms    |

| V1                         | Operating Voltage of Channel V1                   |                                                                          | 9.6   | 12   | 14.4  | V     |

| V2                         | Operating Voltage of Channel V2                   |                                                                          | 4     | 5    | 6     | V     |

| V3                         | Operating voltage of Channel V3                   |                                                                          | 6.4   | 8    | 9.6   | V     |

| I <sub>LOAD</sub>          | Load Current                                      |                                                                          |       | 2    |       | А     |

| AVI                        | Auxiliary Voltage Input                           |                                                                          | 6     |      | 24    | V     |

#### **OVERVIEW**

The LTC4417 controls three sets of external back-to-back P-channel MOSFETs to connect the proper rail to the load. Precision comparators are used to monitor each of the three input rails for both UV and OV conditions. The highest priority input supply whose voltage is within its respective OV/UV window for at least 256ms is considered valid and connected to the load. Low signals on the VALID1, VALID2, and VALID3 pins indicate validation of the V1, V2, and V3 voltages.

DC1717A is designed to operate from inputs of 12V, 5V, and 8V, applied to V1, V2 and V3 respectively. The valid range of each supply is  $\pm 20\%$ , as set by OV and UV comparators and their associated resistive dividers. V1

has the highest priority, V3 has the lowest. The highest priority input that is also within its valid range is selected to power the output. V1, V2 and V3 inputs are protected against input glitches of up to ±42V. Maximum load current is 2A, limited by MOSFET capability.

Logic and LEDs are included to provide visual information about the operating status. These circuits are powered from a 6V to 24V auxiliary voltage input (AVI) which is regulated by an LT3060 (U4) to 5V. This auxiliary 5V rail also powers 100k $\Omega$  pull-ups for  $\overline{\text{VALID}}$  pins. AVI must be present in order for the board to operate. See the Modification section for a means of eliminating AVI.

#### **OPERATING PRINCIPLES**

To eliminate back-and-forth switching during rail switchover, the LTC4417 provides a 30mV hysteresis in the OV and UV comparators, and an externally adjustable current mode hysteresis using the OV/UV resistive dividers. DC1717A's input reference hysteresis is 6%, and can be changed to 3% by moving the JP1 jumper to the 30mV position.

The controller's "break-before-make" switching method prevents cross conduction between input channels and reverse current from the output capacitor into the selected input supply.

Each channel's control circuit of the LTC4417 has a REV comparator, which monitors the connecting input supply and output load voltage. The REV comparator delays the connection until the output voltage droops 120mV below the input voltage. This prevents reverse current.

The LTC4417 has two common control pins: EN and SHDN.

Pulling the EN pin below 1V turns off all external back-to-back P-channel MOSFETs. When this pin is driven above 1V, the highest priority valid channel is connected to the load. All these actions are provided without resetting the 256ms OV/UV timers.

Pulling the SHDN pin below 0.8V turns off all external back-to-back P-channel MOSFETs, placing the controller

in a low current state and resetting the 256ms timers used to validate input rail voltages. It requires at least 256ms to validate each rail voltage after the SHDN pin signal goes high.

The LTC4417 features two different driving modes for the P-channel MOSFET gates.

One mode is provided by the internal soft-start circuitry, which limits output voltage slew rate to no more than 5V/ms. As the highest output voltage slew rate, usually, can impose the highest requirements for circuit components, 5V/ms should be taken into account as a worst case for component selection.

The soft-start circuitry is enabled each time under the following conditions:

- If the LTC4417 is first powered on, or

- If SHDN is forced low, or

- If V<sub>OUT</sub> falls below ~0.7V

Soft-start is disabled when:

- any channel turns off, including the channel that is soft starting.

- 32ms validation delay time has elapsed during the softstart interval.

LINEAD

dc1717a1

#### **OPERATING PRINCIPLES**

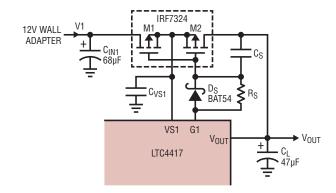

The other driving mode of the P-channel MOSFETs is used in the voltage switching operation, when the higher priority rail replaces the rail losing validity. The gate driver operates with a fixed current, which is defined by the external component parameters  $R_S$  and  $C_S$  shown in Figure 1.

The LTC4417 circuit designer should select the value of  $R_S$  and  $C_S$  based on the MOSFET parameters, power rail source characteristics, acceptable output voltage droop during transient, and the value of load capacitance.

Figure 1

#### DESIGN PROCEDURE FOR MODIFICATION OF DC1717A

The valid input range for any supply is controlled by the OV and UV comparators with resistive dividers (R4-R13). See the LTC4417 data sheet for design equations to select resistors to match a particular requirement.

Dual MOSFETs, Q1-Q3, may be replaced with single devices Q4-Q9 by simply removing Q1-Q3. Pads for Q4-Q9 are located on the bottom side of the board.

The requirement for AVI may be eliminated by removing jumpers JP2 and JP3, and removing resistor R19. This modification leaves the <u>LEDs</u> unpowered and the inputs of U2 and U3 clamp the <u>VALID</u> pins at 0.7V, but otherwise leaves the LTC4417 operating autonomously.

The following design considerations and equations demonstrate the interrelation of the main component values and transient parameters in the rail transitions, when the output voltage exceeds 0.7V. The variables  $C_S$  and  $R_S$  used in the design equations correspond to the following board components:

- C20, R23 for V1 (+12V channel)

- C21, R26 for V2 (+5.0V channel)

- C22, R28 for V3 (+8.0V channel)

To have dominant influence on the transient time  $C_S$  should be at least ten times larger than the P-channel MOSFET's reverse transfer capacitance (Miller). In this design, for all rails,  $C_S$  (C20, C21,and C22) equals 47nF.

The slew rate of the output voltage can be expressed as a function of  $C_S$ :

$$\frac{dV_{OUT}}{dt} = \frac{dV_{CS}}{dt} = \frac{V_{SINK} - |V_{THRES}|}{R_S \cdot C_S}$$

(1)

where:

- $V_{SINK}$  is the LTC4417 parameter rated in the data sheet as  $\Delta V_{G(SINK)} = 4.5V-6V$ .

- V<sub>THRES</sub> is the P-channel gate threshold voltage, which is between –1.5V and –3.5V for the Si7905DN installed on the board.

- $R_S = 249\Omega$  and  $C_S = 47nF$ .

Given that  $dV_{OUT}/dt$  is based on the transient time requirement, it is possible to define  $R_S$  from equation 1.

The output voltage slew rate,  $dV_{OUT}/dt$ , range for the circuit with the listed parameters is between 85V/ms and 385V/ms.

During the transition of rails, the load can be disconnected from any rail for a time:

$T_{DISCON} = t_{G(SWITCHOVER)} + t_{pVALID(OFF)} + t_{GATE\_THRES}$ Two first summands of the  $T_{DISCON}$  are rated in the LTC4417 data sheet as:

$$t_{G(SWITCHOVER)} = (0.3 \text{ to } 3)\mu s$$

$t_{pVALID(OFF)} = (5 \text{ to } 13)\mu s$

#### DESIGN PROCEDURE FOR MODIFICATION OF DC1717A

The second summand,  $t_{pVALID(OFF)}$ , should be taken into account if the associated LTC4417 input does not have any bypass capacitor and the rail can be disconnected from the input instantly.

The third one must be calculated as:

$$t_{GATE\_THRES} = R_S \cdot C_S \left[ -In \left( 1 - \frac{V_{THRES}}{V_{SINK}} \right) \right]$$

(2)

It is possible to determine the minimum capacitive load required to hold the output up during switchover as a:

$$C_{LOAD(MIN)} \ge \frac{I_{LOAD(MAX)} \cdot T_{DISCON}}{V_{OUT(DROOPMAX)}}$$

(3)

where:

- I<sub>LOAD(MAX)</sub> is the maximum load current, A

- V<sub>OUT(DROOPMAX)</sub> is the maximum acceptable voltage droop, V

As shown in the equation (3), the use of external slew rate control will add additional delay to the total switchover time. Unfortunately, the actual components cannot be chosen until the load capacitance is known. This circular issue can only be resolved through an iterative process.

The process starts by calculating the  $C_{LOAD(MIN)}$ , assuming that  $t_{GATE\_THRES}$  = 10µs. For clarity this value will be labeled  $C_{LOAD(INIT)}$ . Using the calculated  $C_{LOAD(INIT)}$ , calculate  $R_S$  from the expression of the  $T_{DISCON}$ . To ensure the newly calculated  $R_S$  based on  $C_{LOAD(INIT)}$  is sufficient, calculate  $C_{LOAD}$  with the calculated  $R_S$ .

If  $C_{LOAD(INIT)}$  (the initial calculated  $C_{LOAD}$ ) is higher than the newly calculated  $C_{LOAD}$  then the process is completed. If the  $C_{LOAD(INIT)}$  is lower than the newly calculated  $C_{LOAD}$ , calculate  $R_S$  using the higher value and repeat this process.

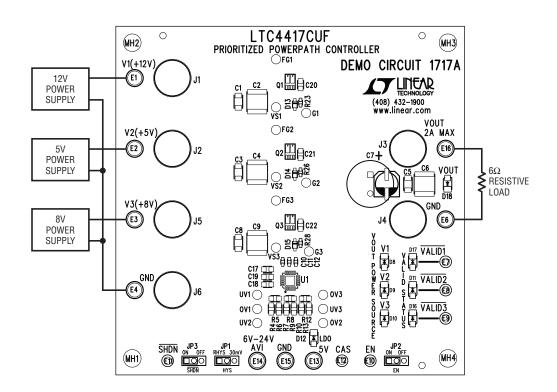

Figure 2

#### **TURRETS**

V1: 12V supply input; do not exceed ±42V.

V2: 5V supply input; do not exceed ±42V.

V3: 8V supply input; do not exceed ±42V.

GND: Adjacent ground connection for input supplies.

VOUT: Output for up to 2A load.

GND: Adjacent ground connection for load.

AVI: Auxiliary Voltage Input. 6V to 24V input regulated by U4 to 5V for LEDs, logic and pull ups on various pins.

GND: Adjacent ground connection for auxiliary supply.

5V: 5V regulated output provided by U4, for powering logic, LEDs and pull ups. Use this turret to verify that 5V is present.

Each of the following turrets is a direct connection to the like-name LTC4417 pin:

VALID1: pulled up with 100kOhm to auxiliary 5V supply.

$\overline{\text{VALID2}}$ : pulled up with 100kOhm to auxiliary 5V supply.

VALID3: pulled up with 100kOhm to auxiliary 5V supply.

EN: pulled up by  $2\mu A$  internal to the LTC4417. Optional R33 may be added as a pull-up to the auxiliary 5V power supply.

$\overline{SHDN}$ : pulled up by  $2\mu A$  internal to the LTC4417. Optional R36 may be added as a pull-up to the auxiliary 5V power supply.

CAS: used to cascade a second DC1717A.Connect the CAS turret of the high priority DC1717A to the EN turret of the lower priority DC1717A.

Grounds must be connected in common.

#### **JUMPERS**

JP1, HYS: Add 30mV fixed hysteresis to the OV and UV comparators, or 3% referred to actual supply input. In the RHYS position input-referred hysteresis is set to 6.4%, as controlled by R11. Default stuffing position is for 30mV.

JP2, EN: Directly controls EN pin. Default stuffing position is ON. pulled up by internal 2uA current source.

## LEDS

No more than one of D8, D9 and D10 will be illuminated at any given moment:

D8: indicates power is being taken from V1.

D9: indicates power is being taken from V2.

D10: indicates power is being taken from V3.

D11, D16 and D17 indicate the presence of a valid input on any of the three supplies:

D17: V1 is 12V±20%.

D11: V2 is 5V+20%.

D16: V3 is 8V±20%.

### **QUICK START PROCEDURE**

Refer to the Figure 3 for proper measurement equipment setup and follow the procedure below:

Initially, the LTC4417 should be disabled by:

- placing the jumper JP2 (EN) header in the OFF position, and

- placing the jumper JP3 (SHDN) header in the OFF position

Connecting the auxiliary power source (6V to 24V) to the DC1717A (AVI and GND turrets) lights the green LED (LDO-D12) indicating the presence of auxiliary +5V supply for powering logic.

With power off, connect three power supplies with output voltages of 12V, 5V, and 8V to corresponding DC1717A turrets or banana jacks V1(+12V), V2(+5V), V3(+8V), and GND.

Connect  $6\Omega$  load resistor (30W) to the DC1717A output turret or banana jack (VOUT). Do not use an electronic load in constant current mode.

Turn on three power supplies. No additional LEDs should light.

Change the jumper **JP3** (SHDN) header position from OFF to ON. Three LEDs (VALID1, VALID2, and VALID3) validating the input rail voltages should light.

Placing the jumper **JP2** (EN) in the ON position turns on the LTC4417 powering the load with 12V (2.0A). In an initial power up the LTC4417 uses a fixed slew rate for the output voltage, which should be not larger than 5V/ms.

The prioritizing function is demonstrated by simply turning off one or two of the V1, V2 and V3 supplies. The output will be powered from the remaining supply of the highest priority. V1, V2 and V3 may be adjusted up and down beyond  $\pm 20\%$  to invalidate a given input.

Figure 3

## **PARTS LIST**

| ITEM | QTY | REFERENCE                  | PART DESCRIPTION                         | MANUFACTURER/PART NUMBER           |

|------|-----|----------------------------|------------------------------------------|------------------------------------|

| 1    | 0   | C1, C3, C5, C8             | Cap., 1206                               | Opt                                |

| 2    | 0   | C2, C4, C6, C9             | Cap., 2220                               | Opt                                |

| 3    | 1   | C7                         | CAP., ALUM., 47µF 50V 20% SMT            | Sun Elect., 50CE47BS               |

| 4    | 5   | C10, C11, C12, C13, C15    | Cap., X5R, 1µF 50V, 10%, 0603            | Murata, GRM188R61H105KAALD         |

| 5    | 1   | C14                        | Cap., X5R 10µF 10V 20% 0805              | Taiyo Yuden LMK212BJ106MG -T       |

| 6    | 1   | C16                        | Cap., X7R 10nF 10V 20% 0805              | Taiyo Yuden EMK105BJ103MG-T        |

| 7    | 3   | C17, C18, C19              | Cap., X7R 0.1µF 50V 10% 0805             | Taiyo Yuden UMK212BJ104KG-T        |

| 8    | 3   | C20, C21, C22              | Cap., X7R 0.047µF 50V, 10%, 0805         | Murata, GRM21BR71H473KA01L         |

| 9    | 3   | D1, D2, D3                 | Diode, TVS Bi-Directional, 26V, 600W     | Diodes/Zetex SMBJ26CA-13-F         |

| 10   | 0   | D7                         | Zener Diode, 5.1V SOD-123                | OPT                                |

| 11   | 8   | D8-D12, D16, D17, D18      | LED, Green                               | Panasonic LN1351CTR                |

| 12   | 3   | D13, D14, D15              | Diode, Schottky,SOD323                   | Vishay Semi., BAT42WS-V-GS08       |

| 13   | 9   | E1-E4, E6, E13-E16         | TURRET, 0.094"                           | Mill-Max 2501-2-00-80-00-00-07-0   |

| 14   | 6   | E7, E8, E9, E10, E11, E12  | TURRET, 0.063"                           | Mill-Max 2308-2-00-80-00-00-07-0   |

| 15   | 3   | JP1, JP2, JP3              | Headers, Sgl. Row 3 Pins 2mm Ctrs.       | Samtec TMM-103-02-L-S              |

| 16   | 3   | SHUNTS ON JP1-JP3 (1and 2) | Shunt, 2mm Ctrs.                         | Samtec 2SN-BK-G                    |

| 17   | 6   | J1, J2, J3, J4, J5, J6     | Jack, Banana                             | Keystone 575-4                     |

| 18   | 3   | Q1, Q2, Q3                 | Dual P-Chan., 40V POWERPAK1212-8-DUAL    | Vishay Si7905DN-T1-GE3             |

| 19   | 0   | Q4, Q5, Q6, Q7, Q8, Q9     | MOSFET P-Chan., 40V, FDD4685, DPAK       | Opt                                |

| 20   | 1   | Q10                        | XTOR N-Chan., SOT23                      | Diode Inc., MMBTA42-7-F            |

| 21   | 1   | Q11                        | XTOR N-Chan., SOT23                      | Diode Inc., MMBT3904-7-F           |

| 22   | 1   | R4                         | RES., Chip 1.69M 0.125W 1% 0805          | Vishay, CRCW08051M69FKEA           |

| 23   | 3   | R5, R8, R12                | RES., Chip 69.8k 0.125W 1% 0805          | Vishay, CRCW080569K8FKEA           |

| 24   | 3   | R6, R9, R13                | RES., Chip 130k 0.125W 1% 0805           | NIC, NRC10F1303TRF                 |

| 25   | 1   | R7                         | RES., Chip 590k 0.125W 1% 0805           | Vishay, CRCW0805590KFKEA           |

| 26   | 1   | R10                        | RES., Chip 1.05M 0.125W 1% 0805          | Vishay, CRCW08051M05FKEA           |

| 27   | 1   | R11                        | RES., Chip 127k 0.1W 1% 0603             | Vishay, CRCW0603127KFKED           |

| 28   | 7   | R14-R16, R20-R22, R29      | RES., Chip 1k 0.1W 5% 0603               | Vishay, CRCW06031K00JNEA           |

| 29   | 0   | R17                        | RES., Chip 845k 0.1W 1% 0603             | Opt                                |

| 30   | 0   | R18                        | RES., Chip 115k 0.06W 1% 0603            | Opt                                |

| 31   | 1   | R19                        | RES., Chip 30.9k 0.1W 1% 0603            | Vishay, CRCW060330K9FKEA           |

| 32   | 3   | R23, R26, R28              | RES., Chip 249Ω 0.1W 1% 0603             | Vishay, CRCW060249RFKEA            |

| 33   | 5   | R30, R31, R32, R33, R36    | RES., Chip 100k 0.1W 5% 0603             | NIC, NRC06J104TRF                  |

| 34   | 1   | R34                        | RES., Chip 68k 0.25W 5% 1206             | NIC, NRC12J683TRF                  |

| 35   | 1   | R35                        | RES., Chip 240Ω 0.25W 1% 1206            | Vishay, CRCW1206240RFKEA           |

| 36   | 1   | U1                         | I.C., PowerPath™ Controller, QFN24UF-4X4 | Linear Technology Corp. LTC4417CUF |

| 37   | 3   | U2,U3,U5                   | I.C., Triple 3-Input NOR Gate TSSOP14    | NXP/Philips Semi. 74HC27PW         |

| 38   | 1   | U4                         | I.C., Low Dropout Reg. TSOT23-8          | Linear Tech. Corp. LT3060ETS8-5    |

| 39   | 4   | MH1-MH4                    | Standoff, Nylon, 0.50, 1/2"              | Keystone, 8833 (SNAP ON)           |

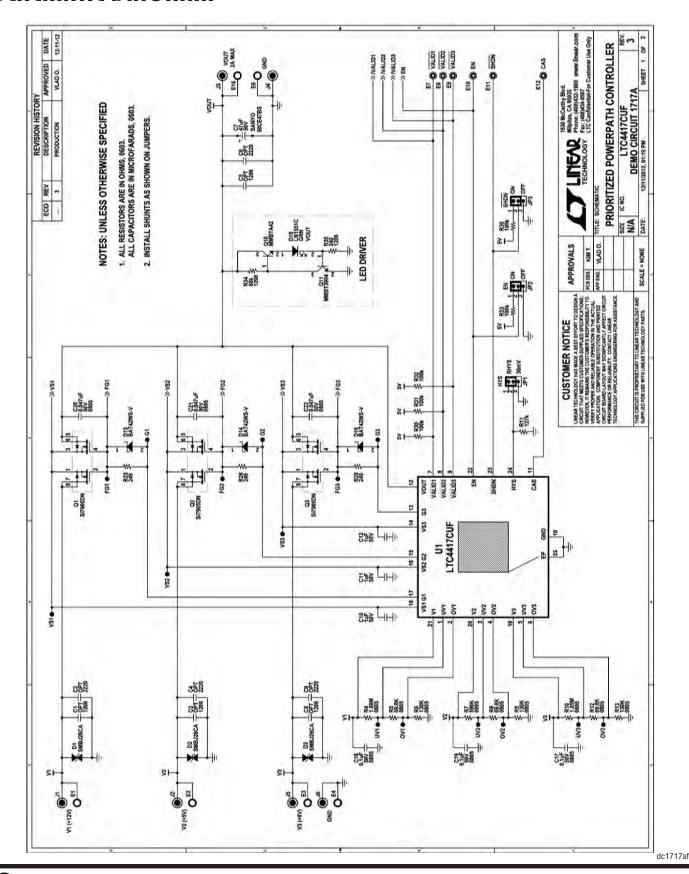

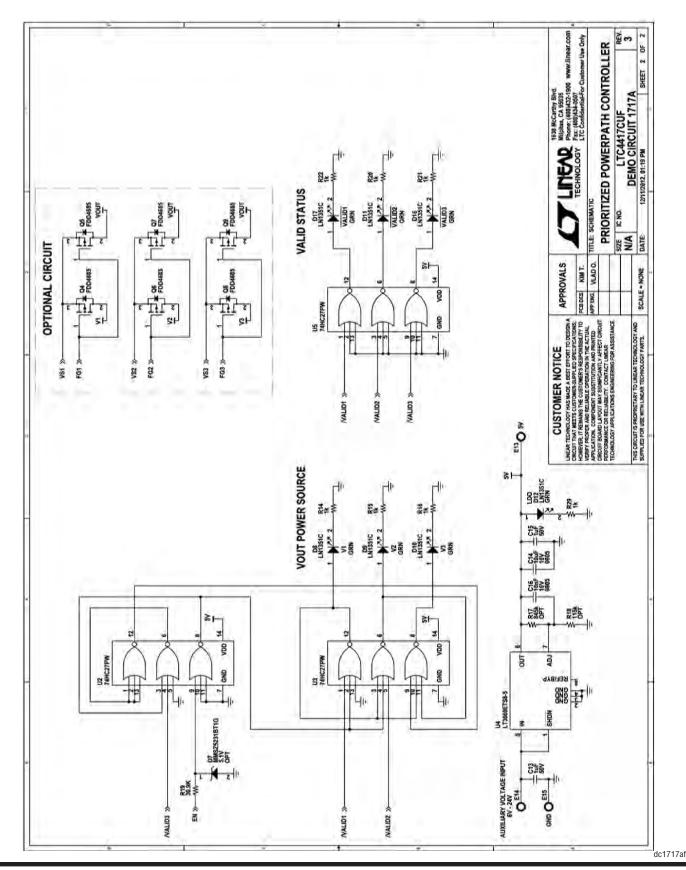

#### **SCHEMATIC DIAGRAM**

#### SCHEMATIC DIAGRAM

#### DEMO MANUAL DC1717A

#### DEMONSTRATION BOARD IMPORTANT NOTICE

Linear Technology Corporation (LTC) provides the enclosed product(s) under the following AS IS conditions:

This demonstration board (DEMO BOARD) kit being sold or provided by Linear Technology is intended for use for **ENGINEERING DEVELOPMENT OR EVALUATION PURPOSES ONLY** and is not provided by LTC for commercial use. As such, the DEMO BOARD herein may not be complete in terms of required design-, marketing-, and/or manufacturing-related protective considerations, including but not limited to product safety measures typically found in finished commercial goods. As a prototype, this product does not fall within the scope of the European Union directive on electromagnetic compatibility and therefore may or may not meet the technical requirements of the directive, or other regulations.

If this evaluation kit does not meet the specifications recited in the DEMO BOARD manual the kit may be returned within 30 days from the date of delivery for a full refund. THE FOREGOING WARRANTY IS THE EXCLUSIVE WARRANTY MADE BY THE SELLER TO BUYER AND IS IN LIEU OF ALL OTHER WARRANTIES, EXPRESSED, IMPLIED, OR STATUTORY, INCLUDING ANY WARRANTY OF MERCHANTABILITY OR FITNESS FOR ANY PARTICULAR PURPOSE. EXCEPT TO THE EXTENT OF THIS INDEMNITY, NEITHER PARTY SHALL BE LIABLE TO THE OTHER FOR ANY INDIRECT, SPECIAL, INCIDENTAL, OR CONSEQUENTIAL DAMAGES.

The user assumes all responsibility and liability for proper and safe handling of the goods. Further, the user releases LTC from all claims arising from the handling or use of the goods. Due to the open construction of the product, it is the user's responsibility to take any and all appropriate precautions with regard to electrostatic discharge. Also be aware that the products herein may not be regulatory compliant or agency certified (FCC, UL, CE, etc.).

No License is granted under any patent right or other intellectual property whatsoever. LTC assumes no liability for applications assistance, customer product design, software performance, or infringement of patents or any other intellectual property rights of any kind.

LTC currently services a variety of customers for products around the world, and therefore this transaction is not exclusive.

**Please read the DEMO BOARD manual prior to handling the product**. Persons handling this product must have electronics training and observe good laboratory practice standards. **Common sense is encouraged**.

This notice contains important safety information about temperatures and voltages. For further safety concerns, please contact a LTC application engineer.

Mailing Address:

Linear Technology 1630 McCarthy Blvd. Milpitas, CA 95035

Copyright © 2004, Linear Technology Corporation