# 20V, 350mA, Rail-to-Rail Operational Amplifier

### **General Description**

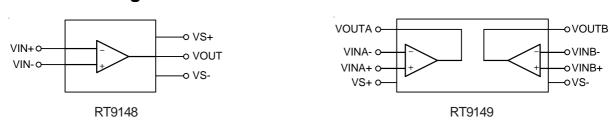

The RT9148/9 consists of a low power, high slew rate, single supply rail-to-rail input and output operational amplifier.

The RT9148 contains a single amplifier and RT9149 contains two amplifiers in one package.

The RT9148/9 has a high slew rate (35V/µs), 350mA peak output current and offset voltage below 15mV. The RT9148/ 9is ideal for Thin Film Transistor Liquid Crystal Displays (TFT LCD).

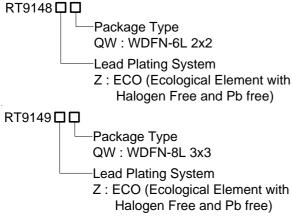

The RT9148 is available in a WDFN-6L 2x2 package. The RT9149 is available in a WDFN-8L 3x3 package. The RT9148/9 are specified for operation over the full -40°C to 85°C temperature range.

## **Applications**

- TFT LCD Panels

- Notebook Computers

- Monitors

- LCDTVs

## **Ordering Information**

#### Note:

Richtek products are:

- > RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- ➤ Suitable for use in SnPb or Pb-free soldering processes.

#### **Features**

- Rail-to-Rail Output Swing

- Supply Voltage: 6V to 20V

- Peak Output Current: 350mA

- High Slew Rate: 35V/μs

- Unity Gain Stable

- RoHS Compliant and Halogen Free

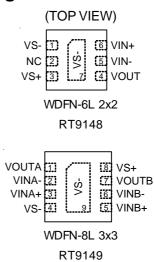

### **Pin Configurations**

## **Marking Information**

RT9148ZQW

0E: Product Code W: Date Code

RT9149ZQW

86: Product Code YMDNN: Date Code

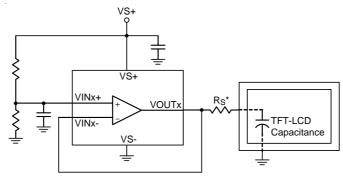

# **Typical Application Circuit**

<sup>\*:</sup> R<sub>S</sub> may be needed for some applications.

# **Function Block Diagram**

# **Functional Pin Description**

RT9148

| Pin No. Pin Name      |      | Pin Function            |  |

|-----------------------|------|-------------------------|--|

| 1,<br>7 (Exposed Pad) | VS-  | Negative Supply Input.  |  |

| 2                     | NC   | No Internal Connection. |  |

| 3                     | VS+  | Positive Supply Input.  |  |

| 4                     | VOUT | Output.                 |  |

| 5                     | VIN- | Negative Input.         |  |

| 6                     | VIN+ | Positive Input.         |  |

#### RT9149

| 1113143               |          |                                |  |

|-----------------------|----------|--------------------------------|--|

| Pin No                | Pin Name | Pin Function                   |  |

| 1                     | VOUTA    | Output of Amplifier A.         |  |

| 2                     | VINA-    | Negative Input of Amplifier A. |  |

| 3                     | VINA+    | Positive Input of Amplifier A. |  |

| 4,<br>9 (Exposed Pad) | VS-      | Negative Supply Input.         |  |

| 5                     | VINB+    | Positive Input of Amplifier B. |  |

| 6                     | VINB-    | Negative Input of Amplifier B. |  |

| 7                     | VOUTB    | Output of Amplifier B.         |  |

| 8                     | VS+      | Positive Supply Input.         |  |

|                       |          |                                |  |

# Absolute Maximum Ratings (Note 1)

| • Supply Voltage, (VS+ to VS-)                                              | 24V            |

|-----------------------------------------------------------------------------|----------------|

| • VINx+, VINx- to VS                                                        | -0.3V to 24V   |

| • VINx+ to VINx                                                             | ±5V            |

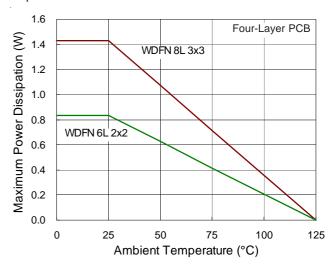

| <ul> <li>Power Dissipation, P<sub>D</sub> @ T<sub>A</sub> = 25°C</li> </ul> |                |

| WDFN-6L 2x2                                                                 | 0.833W         |

| WDFN-8L 3x3                                                                 | 1.429W         |

| Package Thermal Resistance (Note 2)                                         |                |

| WDFN-6L 2x2, $\theta_{JA}$                                                  | 120°C/W        |

| WDFN-8L 3x3, $\theta_{JA}$                                                  | 70°C/W         |

| WDFN-8L 3x3, $\theta_{JC}$                                                  | 8.2°C/W        |

| • Lead Temperature (Soldering, 10 sec.)                                     | 260°C          |

| • Junction Temperature                                                      | 150°C          |

| Storage Temperature Range                                                   | –65°C to 150°C |

| • ESD Susceptibility (Note 3)                                               |                |

| HBM (Human Body Mode)                                                       | 2kV            |

| MM (Machine Mode)                                                           | 200V           |

|                                                                             |                |

# Recommended Operating Conditions (Note 4)

| • Supply Voltage, VS- = 0V, VS+ 6 <sup>v</sup> | / to 20 | V |

|------------------------------------------------|---------|---|

|------------------------------------------------|---------|---|

### **Electrical Characteristics**

$(V_{S+} = 16V, V_{S-} = 0V, V_{INX+} = V_{OUTX} = V_{S+} / 2, R_L = 10k\Omega$  and  $C_L = 10pF, T_A = 25^{\circ}C$ , unless otherwise specified)

| Parameter                        | Symbol            | Test Conditions                         | Min                     | Тур                     | Max                     | Unit  |

|----------------------------------|-------------------|-----------------------------------------|-------------------------|-------------------------|-------------------------|-------|

| Input Characteristics            | •                 |                                         | •                       |                         | •                       |       |

| Input Offset Voltage             | Vos               | V <sub>CM</sub> = V <sub>S+</sub> / 2   |                         | 2                       | 15                      | mV    |

| Input Bias Current               | I <sub>B</sub>    | $V_{CM} = V_{S+} / 2$                   |                         | 2                       | 50                      | nA    |

| 1 15 14                          | 4)/               | I <sub>L</sub> = 0 to -80mA             |                         | 0.1                     |                         | mV/mA |

| Load Regulation                  | $\Delta V_{LOAD}$ | I <sub>L</sub> = 0 to 80mA              |                         | -0.1                    |                         |       |

| Common Mode Input<br>Range       | CMIR              |                                         | 0.5                     |                         | V <sub>S+</sub><br>-0.5 | V     |

| Common Mode Rejection Ratio      | CMRR              | $0.5V \leq V_{OUTx} \leq V_{S+} - 0.5V$ |                         | 95                      |                         | dB    |

| Open Loop Gain                   | A <sub>VOL</sub>  | $0.5V \le V_{OUTx} \le V_{S+} - 0.5V$   |                         | 118                     |                         | dB    |

| Output Characteristics           |                   |                                         |                         |                         |                         |       |

| Output Swing Low                 | VoL               | I <sub>L</sub> = -50mA                  |                         | 0.6                     | 1.5                     | V     |

| Output Swing High                | Voн               | I <sub>L</sub> = 50mA                   | V <sub>S+</sub><br>-1.5 | V <sub>S+</sub><br>-0.3 |                         | V     |

| Transient Peak Output<br>Current | I <sub>PK</sub>   |                                         | 300                     | 350                     | 400                     | mA    |

Copyright ©2012 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

DS9148/9-02 March 2012 www.richtek.com

| Parameter                       | Symbol         | Symbol Test Conditions                                               |   | Тур | Max | Unit |

|---------------------------------|----------------|----------------------------------------------------------------------|---|-----|-----|------|

| Power Supply                    |                |                                                                      |   | •   | •   | •    |

| Power Supply Rejection Ratio    | PSRR           | $V_{S+} = 6V \text{ to } 20V, V_{CM} = V_{OUTx} = V_{S+} / 2$        |   | 96  |     | dB   |

| Quiescent Current               | $I_{DD}$       | No Load                                                              |   | 4   |     | mA   |

| Dynamic Performance             |                |                                                                      |   |     |     |      |

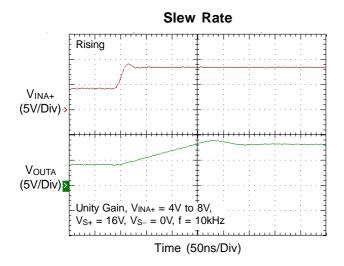

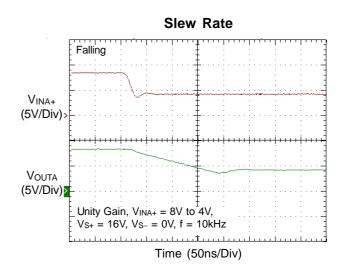

| Slew Rate                       | SR             | 4V step, 20% to 80%, A <sub>V</sub> = 1                              |   | 35  |     | V/µs |

| Setting to $\pm 0.1\%$ (AV = 1) | t <sub>S</sub> | $A_V = 1$ , $V_{OUTx} = 2V$ step<br>$R_L = 10k\Omega$ , $C_L = 10pF$ | - | 270 |     | ns   |

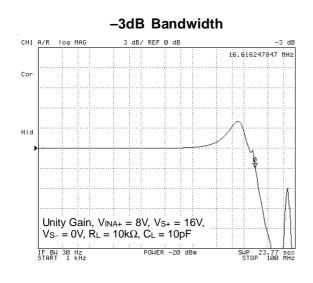

| -3dB Bandwidth                  | BW             | $R_L = 10k\Omega$ , $C_L = 10pF$                                     |   | 16  |     | MHz  |

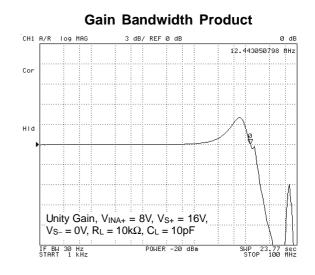

| Gain-Bandwidth Product          | GBWP           | $R_L = 10k\Omega$ , $C_L = 10pF$                                     |   | 12  |     | MHz  |

| Phase Margin                    | PM             | $R_L = 10k\Omega$ , $C_L = 10pF$                                     |   | 50° |     |      |

- Note 1. Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

- Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a high effective thermal conductivity four-layer test board per JEDEC 51-7.  $\theta_{JC}$  is measured at the exposed pad of the package.

- Note 3. Devices are ESD sensitive. Handling precaution is recommended.

- Note 4. The device is not guaranteed to function outside its operating conditions.

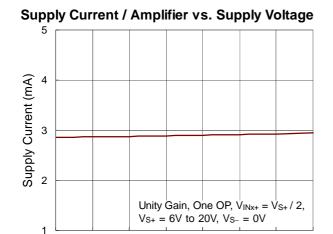

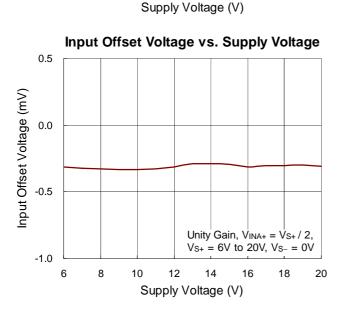

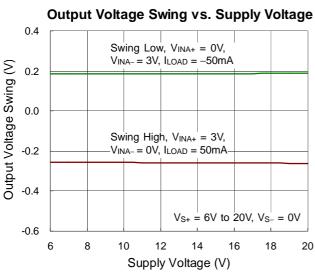

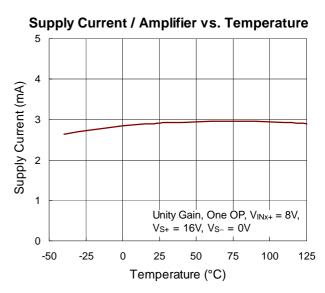

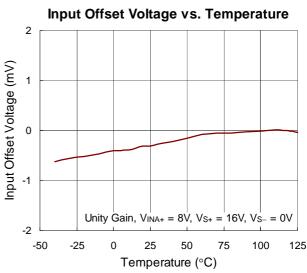

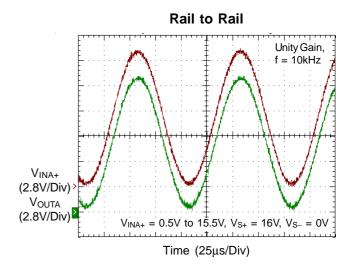

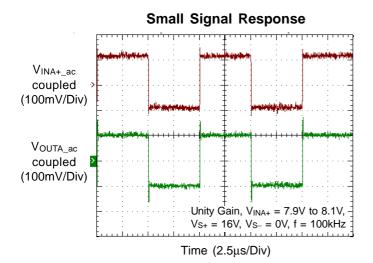

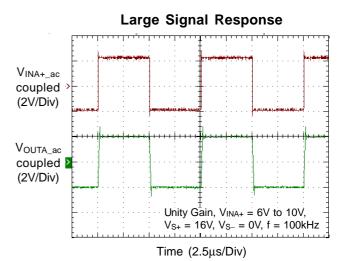

# **Typical Operating Characteristics**

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

DS9148/9-02 March 2012 www.richtek.com

DS9148/9-02 March 2012

### **Applications Information**

The RT9148/9 is a high performance operational amplifier capable of driving large loads for different applications. A high slew rates, rail-to-rail input and output capability, and low power consumption are the features which make the RT9148/9 ideal for LCD applications. The RT9148/9 also has wide bandwidth and phase margin to drive a load with  $10k\Omega$  resistance and 10pF capacitance.

#### **Operating Voltage**

The RT9148/9 total supply voltage range is guaranteed from 6V to 20V. The specifications are stable over both the full supply range and operating temperatures from -40°C to 85°C. The output swing of the RT9148/9 typically extends to within 1.5V of positive/negative supply rails with 50mA load current source/sink. Decreasing the load current will obtain an output swing even closer to the supply rails.

#### **Short Circuit Condition**

An internal short circuit protection is implemented to protect the device from output short circuit. The RT9148/ 9 limits the short circuit current to ±350mA if the output is directly shorted to positive/negative supply rails.

#### **LCD Panel Applications**

The RT9148/9 is mainly designed for LCD V-com buffer. The operational amplifier has 350mA instantaneous source/ sink peak current.

#### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula:

$$P_{D(MAX)} = (T_{J(MAX)} - T_A) / \theta_{JA}$$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications of the RT9148/9, the maximum junction temperature is 125°C and T<sub>A</sub> is the ambient temperature. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For WDFN-8L 3x3 packages, the thermal resistance, θ<sub>JA</sub>, is 70°C/W on a standard JEDEC 51-7 four-layer thermal test board. For WDFN-6L 2x2 packages, the thermal resistance,  $\theta_{JA}$ , is 120°C/W on a standard JEDEC 51-7 four-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$ can be calculated by the following formula:

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (70^{\circ}C/W) = 1.429W$$

for WDFN-8L 3x3 package

$$P_{D(MAX)} = (125^{\circ}C - 25^{\circ}C) / (120^{\circ}C/W) = 0.833W$$

for WDFN-6L 2X2 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . For the RT9148/9 packages, the derating curve in Figure 1 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 1. Derating Curve for the RT9148/9 Packages

Copyright ©2012 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

RT9148/9

#### **Layout Consideration**

PCB layout is very important for designing power converter circuits. The following layout guidelines should be strictly followed for best performance of the RT9148/9.

- Place the power components as close to the IC as possible. The traces should be wide and short, especially for the high current loop.

- A series resistance may be needed at the output for some applications.

- ▶ Connect a 0.1µF capacitor from VINx+ to ground and place it as close to the IC as possible for better performance.

- > The exposed pad of the chip should be connected to a large PCB plane for maximum thermal consideration.

www.richtek.com

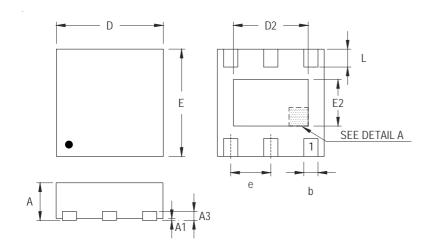

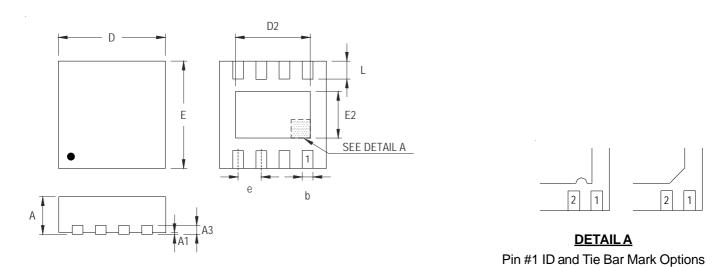

## **Outline Dimension**

**DETAIL A**

Pin #1 ID and Tie Bar Mark Options

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| Cumhal | Dimensions l | n Millimeters | Dimensions In Inches |       |  |

|--------|--------------|---------------|----------------------|-------|--|

| Symbol | Min          | Max           | Min                  | Max   |  |

| А      | 0.700        | 0.800         | 0.028                | 0.031 |  |

| A1     | 0.000        | 0.050         | 0.000                | 0.002 |  |

| A3     | 0.175        | 0.250         | 0.007                | 0.010 |  |

| b      | 0.200        | 0.350         | 0.008                | 0.014 |  |

| D      | 1.950        | 2.050         | 0.077                | 0.081 |  |

| D2     | 1.000        | 1.450         | 0.039                | 0.057 |  |

| Е      | 1.950        | 2.050         | 0.077                | 0.081 |  |

| E2     | 0.500        | 0.850         | 0.020                | 0.033 |  |

| е      | 0.650        |               | 0.0                  | )26   |  |

| L      | 0.300        | 0.400         | 0.012                | 0.016 |  |

W-Type 6L DFN 2x2 Package

Note: The configuration of the Pin #1 identifier is optional, but must be located within the zone indicated.

| O. male el | Dimensions I | n Millimeters | Dimensions In Inches |       |  |

|------------|--------------|---------------|----------------------|-------|--|

| Symbol     | Min          | Max           | Min                  | Max   |  |

| А          | 0.700        | 0.800         | 0.028                | 0.031 |  |

| A1         | 0.000        | 0.050         | 0.000                | 0.002 |  |

| A3         | 0.175        | 0.250         | 0.007                | 0.010 |  |

| b          | 0.200        | 0.300         | 0.008                | 0.012 |  |

| D          | 2.950        | 3.050         | 0.116                | 0.120 |  |

| D2         | 2.100        | 2.350         | 0.083                | 0.093 |  |

| Е          | 2.950        | 3.050         | 0.116                | 0.120 |  |

| E2         | 1.350        | 1.600         | 0.053                | 0.063 |  |

| е          | 0.650        |               | 0.0                  | 26    |  |

| L          | 0.425        | 0.525         | 0.017                | 0.021 |  |

W-Type 8L DFN 3x3 Package

### **Richtek Technology Corporation**

5F, No. 20, Taiyuen Street, Chupei City Hsinchu, Taiwan, R.O.C.

Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.

DS9148/9-02 March 2012