Address: Telephone: Fax: Email: Website:

+44 (0)1493 665111 sales@midascomponents.co.uk www.midascomponents.co.uk

# Specification MCT057HA6W320240LSL

# **Contents**

|     |                            | Page       |

|-----|----------------------------|------------|

| 1.  | Revision History           | 3          |

| 2.  | General Specification      | 4          |

| 3.  | Module Coding System       | 5          |

| 4.  | Block Diagram              | 6          |

| 5.  | Electrical Characteristics | 7          |

| 6.  | Absolute Maximum Ratings   | 7          |

| 7.  | Interface Pin Function     | 8          |

| 8.  | Timing Characteristics     | 10         |

| 9.  | Waveform                   | 13         |

| 10. | Optical Characteristics    | 21         |

| 11  | Contour Drawing            | 24         |

| 12. | LED driving conditions     | 25         |

| 13. | Reliability Test           | <b>2</b> 6 |

|     |                            |            |

# 1. Revision History

| DATE       | VERSION | REVISED PAGE NO. | Note        |

|------------|---------|------------------|-------------|

| 2012/06/20 | 1       |                  | First issue |

|            |         |                  |             |

|            |         |                  |             |

|            |         |                  |             |

# 2. General Specification

This product is composed of a TFT LCD panel, driver ICs, FPC, Control Board and a backlight unit. The following table described the features of MCT057H06W320240LSL

■ Dot Matrix: 320 x RGB x240

■ Module dimension: FI F.FGx 101.55 x 6.3 (max.) mm

■ View area: 117.9 x 89.1 mm

■ Active area: 115.2 x 86.4 mm

■ Dot pitch: 0.12 x 0.36 mm

■ LCD type: TFT, Negative, Transmissive

■ View direction: 6 o'clock

■ Backlight Type: LED, Normally White

Controller IC: HX8218-A+HZ8615A(or compatible)

Address: Telephone: Fax: Email: Website:

+44 (0)1493 665111 sales@midascomponents.co.uk www.midascomponents.co.uk

# Midas Active Matrix Display Part Number System

MC 320240 057 2 3 5 1 4 7 8 9 10 11 12 13 14

```

1 = MC: Midas Components

```

2 = T: TFT A: Active Matrix OLED

3 = Size

4 = Series

5 = Viewing Angle: 6: 6 O'clock 12: 12 O'clock

6 = Blank: No Touch T: Touchscreen

7 = Operating Temp Range: S: 0 to 50Deg C B: -20+60Deg C

W: -20+70Deg C E: -30+85Deg C

8 = No of Pixels

9 = **Orientation: P:** Portrait **L:** Landscape

10 = **Mode:** R: Reflective M: Transmissive T: Transflective

S: Sunlight Readable (transmissive)

11 = **Backlight: Blank:** None **L:** LED **C:** CCFL

12 = **Blank:** No Module/board **C:** Controller board module

13 = **Blank:** None V: Video

14 = **Blank:** None **B**: Bracket

15 = **Blank:** None H: Host Cable

16 = Blank: None K: Keyboard

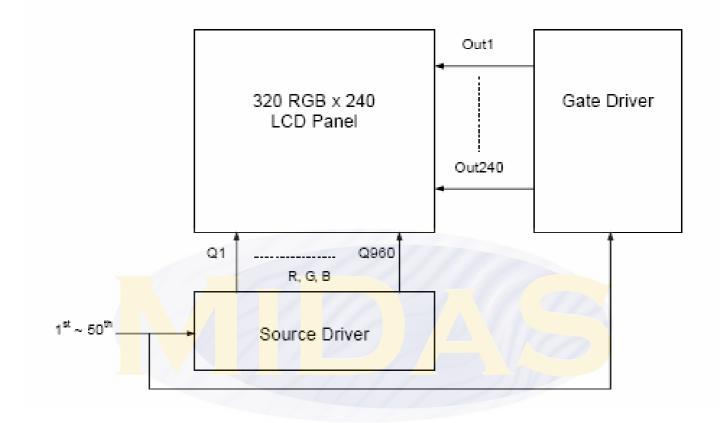

# 4.Block Diagram

# **5.Electrical Characteristics**

| Item                     | Symbol           | Condition             | Min          | Тур | Max          | Unit |

|--------------------------|------------------|-----------------------|--------------|-----|--------------|------|

| Supply Voltage For Logic | $V_{DD}$         | _                     | 3.0          | 3.3 | 3.6          | V    |

| Input High Volt.         | V <sub>IH</sub>  | =                     | $0.7 V_{DD}$ | _   | $V_{DD}$     | V    |

| Input Low Volt.          | V <sub>IL</sub>  | _                     | 0            | _   | $0.3 V_{DD}$ | V    |

| Power Supply Voltage     | $V_{GH}$         | Ta=25℃                | 10           |     | 30           | V    |

| l construction           | $V_{GL}$         | Ta=25℃                | -17          |     | -5           | V    |

| Supply Current           | I <sub>VDD</sub> | V <sub>DD</sub> =3.3V | _            | 5   | 8            | mA   |

# 6.Absolute Maximum Ratings

| Item                  | Symbol              | Min  | Тур | Max  | Unit       |

|-----------------------|---------------------|------|-----|------|------------|

| Operating Temperature | T <sub>OP</sub>     | -20  | _   | +70  | $^{\circ}$ |

| Storage Temperature   | T <sub>ST</sub>     | -30  | _   | +80  | $^{\circ}$ |

|                       | $V_{GH}$            | -0.3 | _   | 32.0 | V          |

| Power Supply Voltage  | $V_{GL}$            | -22  | _   | 0.3  | V          |

|                       | $V_{GH}$ - $V_{GL}$ | -0.3 | _   | +45  | V          |

# 7. Interface Pin Function

#### 7-1 LCM PIN Definition

| Pin No. | Symbol           | I/O | Description                                      | Remark |

|---------|------------------|-----|--------------------------------------------------|--------|

| 1       | IF1              | I   | Input data format control (Note1)                | Note1  |

| 2       | IF2              |     | Input data format control (Note1)                | Note1  |

| 3       | POL              | 0   | Polarity Signal connect to VCOM driving circuit. | Note3  |

| 4       | RESET            |     | Hardware reset.                                  |        |

| 5       | SPENA            |     | Chip select                                      | Note2  |

| 6       | SPCL             |     | Serial Clock                                     | Note2  |

| 7       | SPDA             | I/O | Serial Data                                      |        |

| 8       | B0               | I   | Blue Data bit (LSB)                              |        |

| 9       | B1               |     | Blue Data bit                                    |        |

| 10      | B2               |     | Blue Data bit                                    |        |

| 11      | B3               | I   | Blue Data bit                                    |        |

| 12      | B4               |     | Blue Data bit                                    |        |

| 13      | B5               |     | Blue Data bit                                    |        |

| 14      | B6               |     | Blue Data bit                                    |        |

| 15      | B7               |     | Blue Data bit(MSB)                               |        |

| 16      | G0               |     | Green Data bit(LSB)                              |        |

| 17      | G1 /             |     | Green Data bit                                   |        |

| 18      | G2               |     | Green Data bit                                   |        |

| 19      | G <mark>3</mark> |     | Green Data bit                                   |        |

| 20      | G4               |     | Green Data bit                                   |        |

| 21      | G5               |     | Green Data bit                                   |        |

| 22      | G6               |     | Green Data bit                                   |        |

| 23      | G7               |     | Green Data bit(MSB)                              |        |

| 24      | R0               | l   | Red Data bit(LSB)                                |        |

| 25      | R1               |     | Red Data bit                                     |        |

| 26      | R2               |     | Red Data bit                                     |        |

| 27      | R3               |     | Red Data bit                                     |        |

| 28      | R4               | I   | Red Data bit                                     |        |

| 29      | R5               |     | Red Data bit                                     |        |

| 30      | R6               | I   | Red Data bit                                     |        |

| 31      | R7               |     | Red Data bit(MSB)                                |        |

| 32      | Hsync            |     | Horizontal synchronous signal                    |        |

| 33      | Vsync            | I   | Vertical synchronous signal                      |        |

| 34      | Data CLK         |     | Dot data clock                                   |        |

| 35      | AVDD(analog)     | I   | Analog power: 4.5V~5.5V                          |        |

| 36      | AVDD(analog)     |     | Analog power: 4.5V~5.5V                          |        |

| 37      | VDD(Digital)     | Ī   | Digital power: 3V~3.6V                           |        |

| 38      | VDD(Digital)     |     | Digital power: 3V~3.6V                           |        |

| 39      | NPC              | 0   | NTSC/PAL mode Auto detection result              |        |

|         |                  |     | H:NTSC/L:PAL                                     |        |

| 40      | VGL              | 1   | Gate off power                                   |        |

| 41      | VGL              | I   | Gate off power                                   |        |

| 42 | UD   | [ | Up/Down scan setting. H: Reverse scan / L:        |       |

|----|------|---|---------------------------------------------------|-------|

|    |      |   | Nomal scan                                        |       |

| 43 | VGH  | I | Gate on power                                     |       |

| 44 | LRC  |   | Shift direction of device internal shift register |       |

|    |      |   | control.                                          |       |

| 45 | GND  | I | GROUND                                            |       |

| 46 | VCOM | I | VCOM driving input                                | Note3 |

| 47 | VCOM | I | VCOM driving input                                |       |

| 48 | ENB  |   | Data enable input. Normally pull low.             | Note4 |

| 49 | GND  | I | GROUND                                            |       |

| 50 | GND  |   | GROUND                                            |       |

**Note:** 1. Control the input data format.

| IF2,IF1      | Input data format |

|--------------|-------------------|

| L,L(default) | Serial RGB        |

| L,H          | Parallel RGB      |

| H,L          | CCIR601           |

| H,H          | CCIR656           |

- 2. Pin 5、Pin 6 usually pull high.

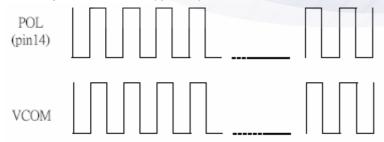

- 3. The polarity of VCOM (Pin 46,47) should be generated from POL (Pin 3).

- 4. For digital RGB input data format, both SYNC mode and DE+SYNC mode are supported. If ENB signal is fixed low, SYNC mode is used. Otherwise, DE+SYNC mode is used.

- 5. The phase of POL (pin 3):

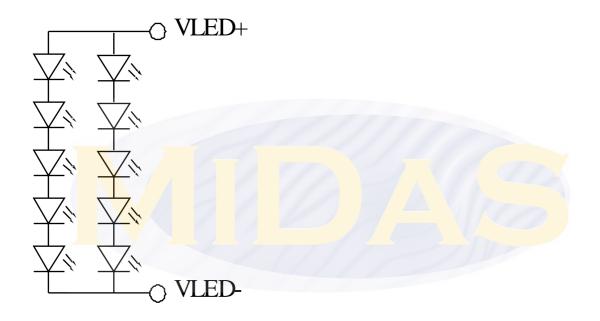

#### 7.2 Backlight PIN Definition

| Pin No. | Symbol | 1/0 | Description         |

|---------|--------|-----|---------------------|

| 1       | VLED+  | I   | Red, LED_ Anode     |

| 2       | VLED-  | I   | Black, LED_ Cathode |

Note: The backlight interface connector is a model PHR-2 manufactured by JST or equivalent.

The matching connector part number is S 2B-PH-K-S manufactured by JST or equivalent.

# 8. AC Characteristics

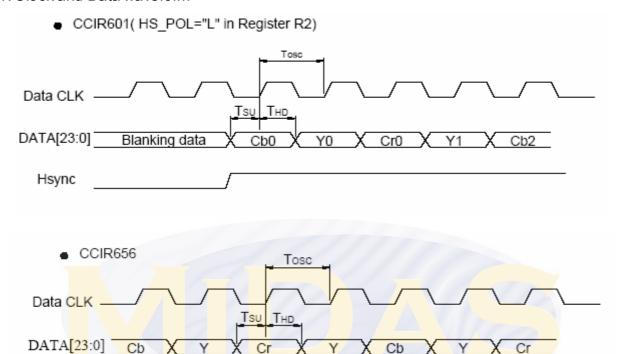

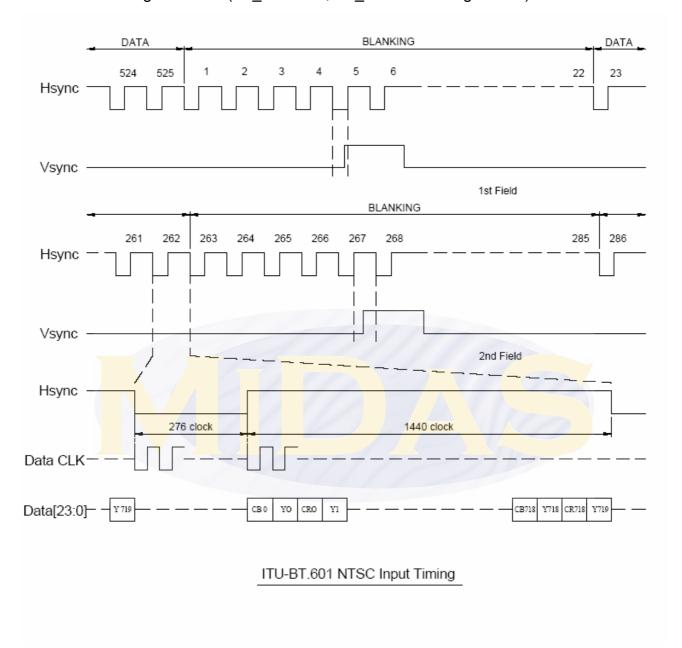

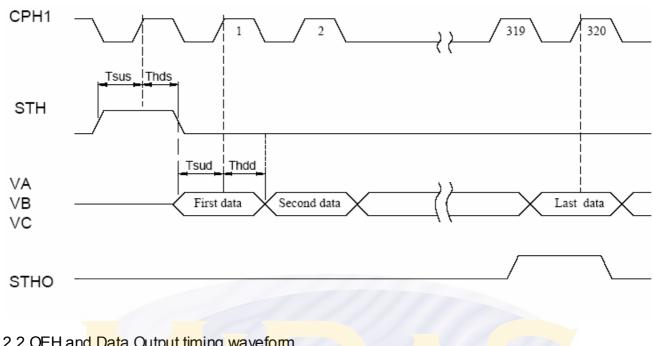

#### 8.1. CCIR601/656 Interface

#### 8.1.1. Input signal characteristics

| PARAMETER       | Symbol          | Min. | Тур. | Max. | Unit |

|-----------------|-----------------|------|------|------|------|

| CLK period      | Tosc            | -    | 37   | -    | ns   |

| Data setup time | Tsu             | 12   | -    | -    | ns   |

| Data hold time  | T <sub>HD</sub> | 12   | -    | -    | ns   |

#### 8.1.2 Hardware reset timing

| PARAMETER             | Symbol           | Min. | Тур. | Max. | Unit |

|-----------------------|------------------|------|------|------|------|

| RESET low pulse width | T <sub>RSB</sub> | 10   | -    | -    | μS   |

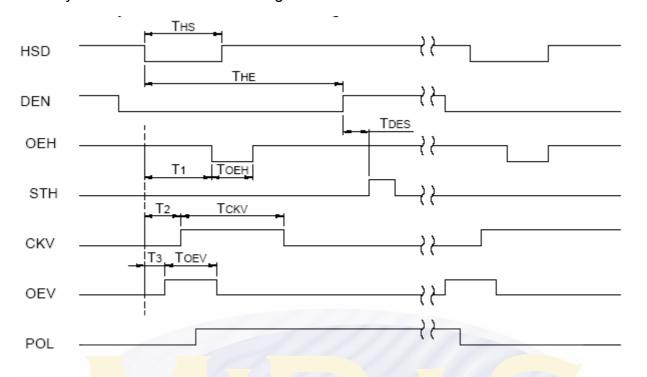

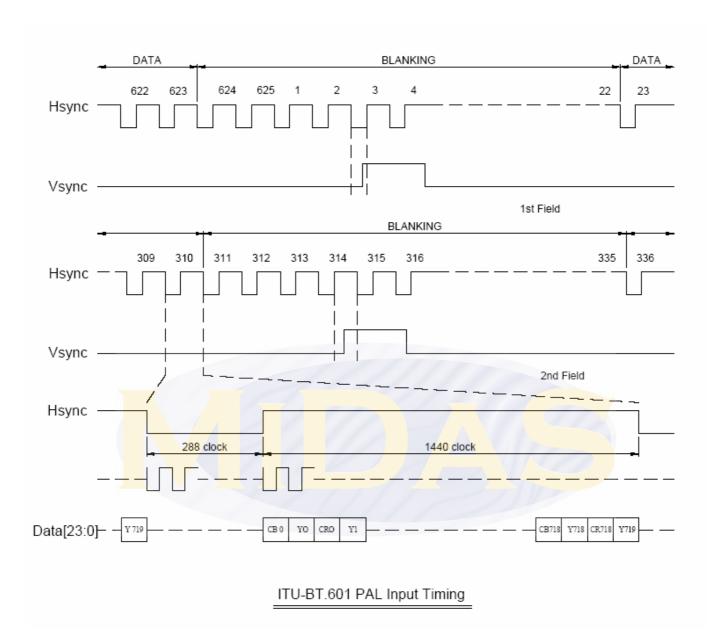

## 8.1.3. Output signal characteristics

| PARAMETER                | Symbol          | Min.             | Тур. | Max. | Unit           |                |

|--------------------------|-----------------|------------------|------|------|----------------|----------------|

| Rising time              | T <sub>r</sub>  | -                | -    | 10   | ns             |                |

| Falling time             |                 | $T_{f}$          | -    | -    | 10             | ns             |

| Internal STH setup time  |                 | T <sub>sus</sub> | 12   |      | -              | ns             |

| Internal STH hold time   |                 | T <sub>HDS</sub> | 12   | -    |                | ns             |

| Internal data setup time |                 | T <sub>SUD</sub> | 60   | -    | -              | ns             |

| Internal data hold time  |                 | T <sub>HDD</sub> | 40   | _    | <u> </u>       | ns             |

| OEH pulse width          |                 | T <sub>OEH</sub> | -)   | 1248 | -              | ns             |

| OEV pulse width          |                 | Toev             |      | 4992 | -              | ns             |

| CKV pulse width          |                 | Тску             | -    | 3744 | -              | ns             |

| Hsync – DEH time         |                 | T <sub>1</sub>   | -    | 4368 | -              | ns             |

| Hsync – CKV time         |                 | T <sub>2</sub>   | -    | 2496 | -              | ns             |

| Hsync – OEV time         |                 | T <sub>3</sub>   | -    | 624  | -              | ns             |

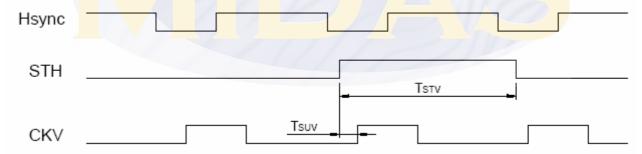

| Vsync – setup time       |                 | $T_{suv}$        |      | 1872 | -              | ns             |

| Vsync – pulse time       |                 | $T_{STV}$        |      | 1    | -              | T <sub>H</sub> |

| Vsync – STV time         | NTSC            | T <sub>VS1</sub> | -    | 19   | -              | T <sub>H</sub> |

| vsync – 31 v time        | PAL             | T <sub>vs1</sub> | -    | 27   | -              | T <sub>H</sub> |

| OEH – STV time           | T <sub>HE</sub> | -                | 2    | -    | T <sub>H</sub> |                |

| Output settling time     |                 | Toes             | -    | 12   | 20             | μS             |

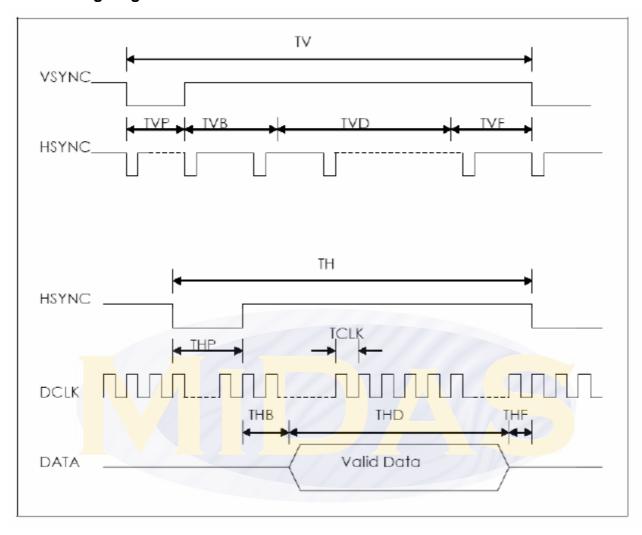

## 8.2. 24-bits parallel RGB Interface

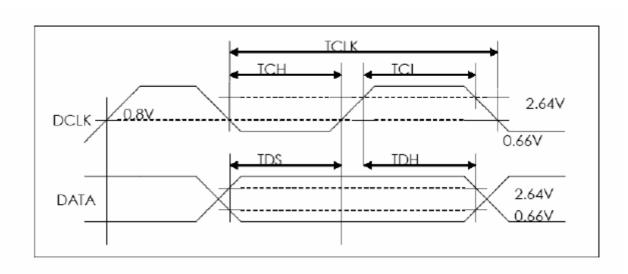

# 8.2.1 AC Timing Characteristics

| Signal | ltem          |                | Symbol | Min  | Тур   | Max | Unit |

|--------|---------------|----------------|--------|------|-------|-----|------|

|        | Frequency     |                | Dclk   | -    | 6.4   | -   | MHZ  |

| Dclk   | High Tir      | ne             | Tch    | -    | 78    | -   | ns   |

|        | Low Tin       | ne             | Tcl    | -    | 78    | -   | ns   |

| Data   | Setup Ti      | me             | Tds    | 12   | -     | -   | ns   |

| Data   | Hold Tir      | ne             | Tdh    | 12   | -     | -   | ns   |

|        | Period        | t              | TH     | -    | 408   | -   | DCLK |

|        | Pulse Width   |                | Thp    | -    | 30    | -   | DCLK |

| Hsync  | Back-Porch    |                | Thb    | -    | 38    | -   | DCLK |

|        | Display Pe    | eriod          | Thd    | -    | 320   | -   | DCLK |

|        | Front-Po      | rch            | Thf    | //-/ | 20    | -   | DCLK |

|        | Period        | NTSC           | Tv     |      | 262.5 |     | ТН   |

|        | Pellod        | PAL            |        |      | 312.5 |     | III  |

|        | Pulse Width   |                | Tvp    | 1    | 3     | 5   | ТН   |

| Vsync  | Back-Porch    | NTSC           | Tvb    |      | 15    |     | TH   |

| VSylic | Dack-Polcii   | PAL            | TVD    | /    | 23    |     | 111  |

|        | Display Pe    | Display Period |        | -    | 240   | -   | TH   |

|        | Front-Porch   | NTSC           | Tvf    |      | 4.5   |     | TH   |

|        | 1 TOTIL-FOIGH | PAL            | IVI    | -    | 46.5  | -   | 111  |

## 8.2.2 AC Timing Diagrams

## 9. Waveform

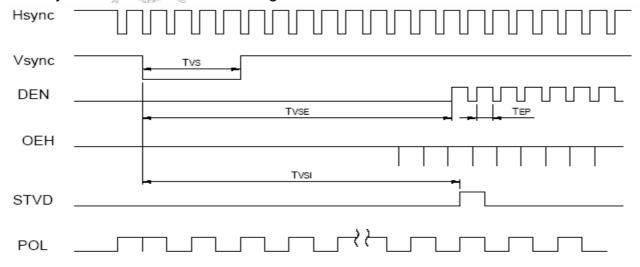

## 9.1. Timing Controller Timing Chart

#### 9.1.1. Clock and Data waveform

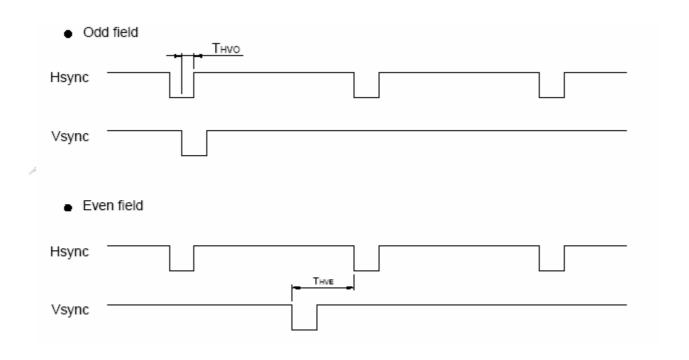

#### 9.1.2 Digital / Analog RGB timing waveform

#### 9.1.2.1 Hsync and Vsync timing

#### 9.1.22 Hs ync and horizontal control timing waveform

## 9.1.2.3 Hs ync and vertical shift clock timing waveform

# 9.1.2.4 Hsync and vertical shift clock timing waveform

## 9.1.3 CCIR601 timing waveform (VS\_POL="H", HS\_POL="L" in Register R2)

#### 9.2 Source Driver Timing Chart

#### 9.2.1 Clock and Start Pulse timing waveform

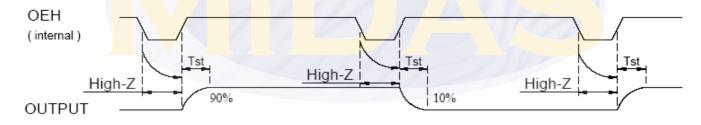

## 9.2.2 OEH and Data Output timing waveform

## 9.3 Analog video signal characteristics

| PARAMETER                                      | Symbol           | Min. | Тур.  | Max. | Unit |

|------------------------------------------------|------------------|------|-------|------|------|

| Video signal amplitude (VA, VB, VC)            | VIAC             | ı    | 3.81  | -    | V    |

| video signal amplitude (VA, VB, VC)            | V <sub>IDC</sub> | -    | 2.385 | -    | V    |

| POL                                            |                  |      |       |      |      |

| VA VIDC VIAC VIAC VIAC VIAC VIAC VIAC VIAC VIA |                  | -    |       |      |      |

Fig. 4-(a) Horizontal timing

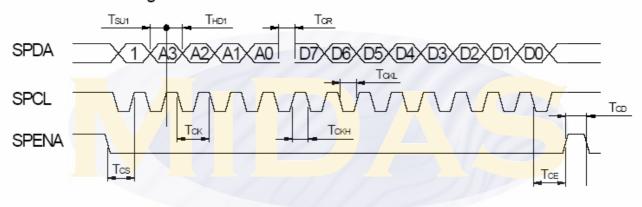

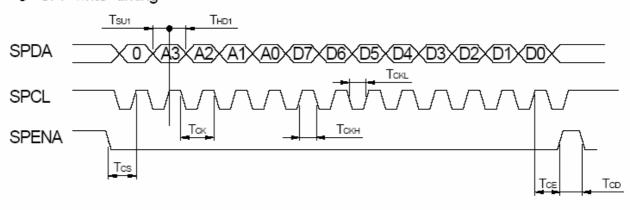

## 9.4 SPI timing characteristics

| PARAMETER                | Symbol           | Min. | Тур. | Max. | Unit |

|--------------------------|------------------|------|------|------|------|

| SPCL period              | T <sub>CK</sub>  | 60   | -    | -    | ns   |

| SPCL high width          | Тскн             | 30   | -    | -    | ns   |

| SPCL low width           | T <sub>CKL</sub> | 30   | -    | -    | ns   |

| Data setup time          | T <sub>SU1</sub> | 12   | -    | -    | ns   |

| Data hold time           | T <sub>HD1</sub> | 12   | -    | -    | ns   |

| SPENA to SPCK setup time | T <sub>CS</sub>  | 20   | -    | -    | ns   |

| SPENA to SPDA hold time  | T <sub>CE</sub>  | 20   | -    | -    | ns   |

| SPENA high pulse width   | T <sub>CD</sub>  | 50   | -    | -    | ns   |

| SPDA output latency      | T <sub>CR</sub>  |      | 1/2  | -    | Тск  |

## SPI "read" timing

## • SPI "write" timing

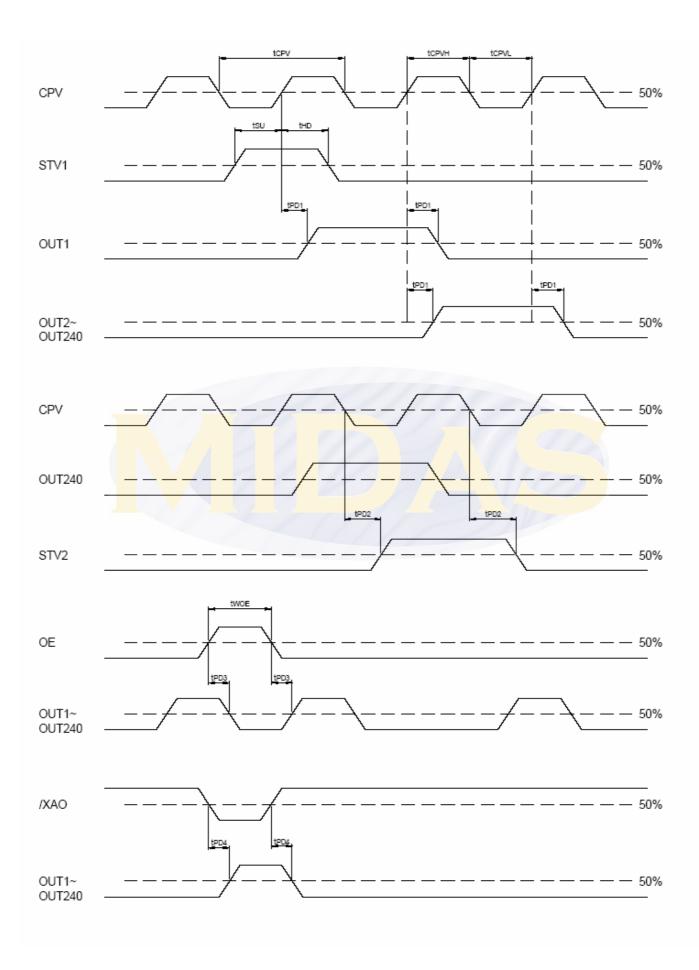

# 9.5 Gate Driver Timing Chart

| Parameter           | Symbol      | Condition     | Sp   | Spec |         |

|---------------------|-------------|---------------|------|------|---------|

| Faranietei          | Symbol      | Condition     | Min. | Max. | Unit    |

| Operation frequency | tCPV        |               | 5    | -    |         |

| CPV pulse width     | tCPVH,tCPVL | 50%duty cycle | 2.5  | -    | $\mu$ s |

| OE pulse width      | twOE        |               | 1    | -    |         |

| Data setup time     | tsu         |               | 0.4  | -    |         |

| Data hold time      | thd         |               | 0.7  | -    |         |

| Output delay time   | tpd1        | CL=300pF      | -    | 1    |         |

| Output delay time   | tpd2        | CL=300pF      | -    | 0.8  | us      |

| Output delay time   | tpd3        | CL=300pF      | -    | 0.8  |         |

| Output delay time   | tpd4        | CL=300pF      | -    | 10   | ]       |

# 10. Optical Characteristics

| ltem          |                     | Symbol | Condition                  | Min.   | Тур.   | Max.       | Unit              | Remark                    |

|---------------|---------------------|--------|----------------------------|--------|--------|------------|-------------------|---------------------------|

| Response time |                     | Tr     | θ=0°                       | _      | 15     | 30         | ms                | Note 3,5                  |

| 1 Copolise (  | uiiic               | Tf     | 0-0                        | _      | 35     | 50         | ms                | 14010 0,0                 |

| Contrast ra   | atio                | CR     | At optimized viewing angle | 350    |        |            |                   | Note 4,5                  |

| Color         | White               | Wx     | Wx θ=0°                    |        | (0.30) | (0.35)     |                   | Note                      |

| chromaticity  | hromaticity   Wille | Wy     | 0-0                        | (0.27) | (0.32) | (0.37)     |                   | 2,6,7                     |

|               | Hor.                | θR     | CR≧10                      | 50     | 65     | _          | Deg.              |                           |

| Viewing       | HOI.                | θL     |                            | 50     | 65     | _          |                   | Note 1                    |

| angle         | Ver.                | θТ     |                            | 30     | 50     | _          |                   | Note 1                    |

|               | ver.                | θВ     |                            | 50     | 55     |            |                   |                           |

| Uniformi      | ty                  | U      | <b>7</b> -                 | (70)   | (75)   | _          | %                 | Note 8                    |

| Brightnes     | SS                  | 4-5    | 2 <mark>5°</mark> C        | 800    |        | <u>-</u> \ | Cd/m <sup>2</sup> | Center of display. Note 9 |

PS. The inaccuracy of average brightness is around 10% to 15% due to material differences.

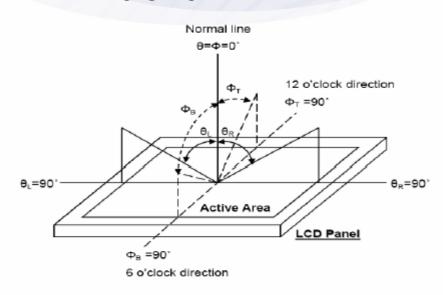

Note 1: Definition of viewing angle range

Fig. 8-1 Definition of viewing angle

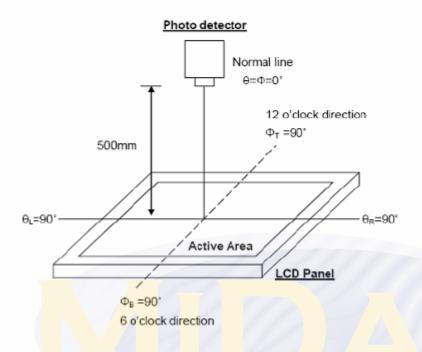

#### Note 2: Test equipment setup:

After stabilizing and leaving the panel alone at a driven temperature for 5 minutes, the measurement should be executed. Measurement should be executed in a stable, windless, and dark room. Optical specifications are measured by Topcon BM-7 luminance meter 1.0° field of view at a distance of 50cm and normal direction.

Fig. 8-2 Optical measurement system setup

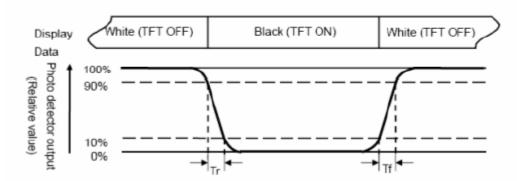

#### Note 3: Definition of Response time:

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time, Tr, is the time between photo detector output intensity changed from 90% to 10%. And fall time, Tf, is the time between photo detector output intensity changed from 10% to 90%.

Fig. 3-3 Definition of response time

#### Note 4: Definition of contrast ratio:

The contrast ratio is defined as the following expression.

Note 5: White Vi =

$$V_{i50} \pm 1.5V$$

Black Vi =  $V_{i50} \pm 2.0V$

"±" means that the analog input signal swings in phase with VCOM signal.

"±" means that the analog input signal swings out of phase with VCOM signal. The 100% transmission is defined as the transmission of LCD panel when all the input terminals of module are electrically opened.

Note 6: Definition of color chromaticity (CIE 1931)

Color coordinates measured at the center point of LCD

Note 7: Measured at the center area of the panel when all the input terminals of LCD panel are electrically opened.

Note 9: The brightness of center will decrease 10% to 15% due to rising temperatures in work environment.

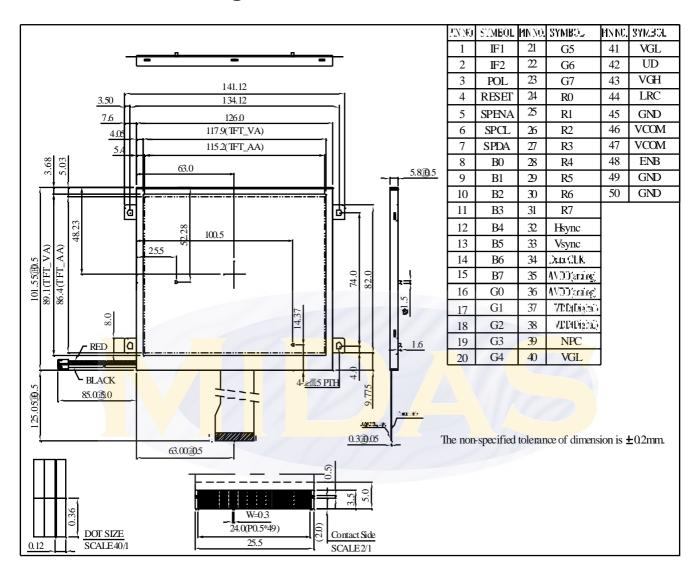

# 11. Contour Drawing

# 12. LED driving conditions

| Parameter     | Symbol           | Min. | Тур. | Max. | Unit | Remark     |

|---------------|------------------|------|------|------|------|------------|

| LED Current   | I <sub>LED</sub> | 120  |      | 130  | mA   | Note1      |

| LED voltage   | $V_{LED}$        | 13.5 |      | 16.0 | V    |            |

| LED life Time | -                |      | 50K  |      | -    | Note 2,3.4 |

Note1 : There are 2Groups LED shown as below,  $V_{\text{LED}}$ =13.5 (min.)

Note2 : Ta=25°C

Note3 : Brightness to be decreased to 50% of the initial value

Note4:50K hours is only an estimate for reference.

# 13. Reliability Test

## WIDE TEMPERATURE RELIABILITY TEST

| N<br>O | ITEM                               | CONDITION                     | I       | STANDARD                  | NOTE         |

|--------|------------------------------------|-------------------------------|---------|---------------------------|--------------|

| 1      | High Temp. Storage                 | 80℃                           | 240 Hrs | Appearance without defect |              |

| 2      | Low Temp. Storage                  | -30℃                          | 240 Hrs | Appearance without defect |              |

| 3      | High Temp. & High<br>Humi. Storage | 60 ℃<br>90%RH                 | 240 Hrs | Appearance without defect |              |

| 4      | High Temp. Operating Display       | <b>70</b> ℃                   | 240 Hrs | Appearance without defect |              |

| 5      | Low Temp. Operating Display        | -20℃                          | 240 Hrs | Appearance without defect |              |

| 6      | Thermal Shock                      | -20 °C, 30min. → 70°C, 30min. |         | Appearance without defect | 10<br>cycles |

# Inspection Provision

#### 1.Purpose

The Midas inspection provision provides outgoing inspection provision and its expected quality level based on our outgoing inspection of Midas LCD produces.

#### 2. Applicable Scope

The Midas inspection provision is applicable to the arrangement in regard to outgoing inspection and quality assurance after outgoing.

- 3.Technical Terms

- 3-1 Midas Technical Tems

- 4. Outgoing Inspection

- 4-1 Inspection Method

MIL-STD-105E Level

Regular inspection

4-2 Inspection Standard

|                 |                      | ltem                             | AQL(%) | Remarks                                                         |

|-----------------|----------------------|----------------------------------|--------|-----------------------------------------------------------------|

| Major<br>Defect | Dots                 | Opens Shorts Erroneous operation | 0.4    | Faults which substantially lower the                            |

|                 | Solder<br>appearance | Shorts<br>Loose                  |        | practicality and<br>the initial purpose<br>difficult to achieve |

|                 | Cracks               | Display surface cracks           |        |                                                                 |

|                 | Dimensions           | External from<br>Dimensions                               | 0.4  |                                               |

|-----------------|----------------------|-----------------------------------------------------------|------|-----------------------------------------------|

| Minor<br>Defect | Inside the glass     | Black spots                                               | 0.65 | Faults which appear to pose                   |

|                 | Polarizing plate     | Scratches, foreign<br>Matter, air bubbles, and<br>peeling |      | almost no<br>obstacle to the<br>practicality, |

|                 | Dots                 | Pinhole, deformation                                      |      | effective use, and operation                  |

|                 | Color tone           | Color unevenness                                          |      |                                               |

|                 | Solder<br>appearance | Cold solder<br>Solder projections                         |      |                                               |

#### 4-3 Inspection Provisions

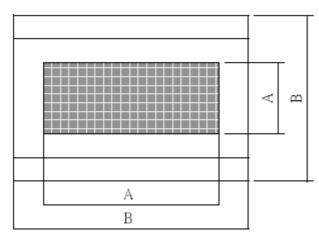

#### \*Viewing Area Definition

Fig. 1

A: Zone Viewing Area

B: Zone Glass Plate Outline

\*Inspection place to be 500 to 1000 lux illuminance uniformly without glaring.

The distance between luminous source(daylight fluorescent lamp and cool white fluorescent lamp)

and sample to be 30 cm to 50 cm.

\*Test and measurement are performed under the following conditions, unless otherwise specified.

Temperature  $20 \pm 15^{\circ}$ C Humidity  $65 \pm 20^{\circ}$ R.H.

Pressure 860~1060hPa(mmbar)

In case of doubtful judgment, it is performed under the following conditions.

Temperature  $20 \pm 2^{\circ}$ C Humidity  $65 \pm 5\%$ R.H.

Pressure 860~1060hPa(mmbar)

#### 5. Specification for quality check

#### 5-1-1 Electrical characteristics:

| NO. | Item               | Criterion              |

|-----|--------------------|------------------------|

| 1   | Non operational    | Fail                   |

| 2   | Miss operating     | Fail                   |

| 3   | Contrast irregular | Fail                   |

| 4   | Response time      | Within Specified value |

#### 5-1-2 Components soldering:

Should be no defective soldering such as shorting, loose terminal cold solder, peeling of printed circuit board pattern, improper mounting position, etc.

#### 5-2 Inspection Standard for TFT panel

#### 5-2-1 The environmental condition of inspection:

The environmental condition and visual inspection shall be conducted as below.

(1) Ambient temperature : 25±5°C

(2) Humidity: 25~75% RH

- (3) External appearance inspection shall be conducted by using a single 20W fluorescent lamp or equivalent illumination.

- (4) Visual inspection on the operation condition for cosmetic shall be conducted at the distance 30cm or more between the LCD panels and eyes of inspector. The viewing angle shall be 90 degree to the front surface of display panel.

- (5) Ambient Illumination: 300~500 Lux for external appearance inspection.

- (6) Ambient Illumination: 100~200 Lux for light on inspection.

#### 5-2-2 Inspection Criteria

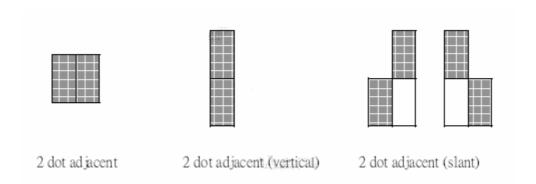

- (1) Definition of dot defect induced from the panel inside

- a) The definition of dot: The size of a defective dot over 1/2 of whole dot is regarded as one defective dot

- b) Bright dot: Dots appear bright and unchanged in size in which LCD panel is displaying under black pattern.

- c) Dark dot: Dots appear dark and unchanged in size in which LCD panel is displaying under pure red, green, blue pattern.

- d) 2 dot adjacent = 1 pair = 2 dots

Picture:

# (2) Display Inspection

| NO. |                                                                   | Item                                                                                                |                         | Acceptable Count |

|-----|-------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|-------------------------|------------------|

|     |                                                                   | Bright Dot                                                                                          | Random                  | N ≦ 2            |

|     |                                                                   |                                                                                                     | 2 dots adjacent         | N ≤ 0            |

|     | Dot defect                                                        | Dark Dot                                                                                            | Random                  | N ≤ 3            |

| 1   |                                                                   |                                                                                                     | 2 dots adjacent         | N ≦ 1            |

| '   |                                                                   | Total bright a                                                                                      |                         | N ≤ 4            |

|     | Functio <mark>nal 1</mark>                                        | <mark>ai</mark> lure <mark>(V-line</mark> / I                                                       | H-line/Cross line etc.) | Not allowable    |

|     | Mura                                                              | It's OK if mura is slight visible through 6% ND filter. (Judged by limit sample if it is necessary) |                         |                  |

|     | Newton                                                            | Orbicular of interference fringes is not allowed in the                                             |                         |                  |

| 2   | ring (touch optimum contrast within the active area under viewing |                                                                                                     |                         |                  |

|     | panel) angle.                                                     |                                                                                                     |                         |                  |

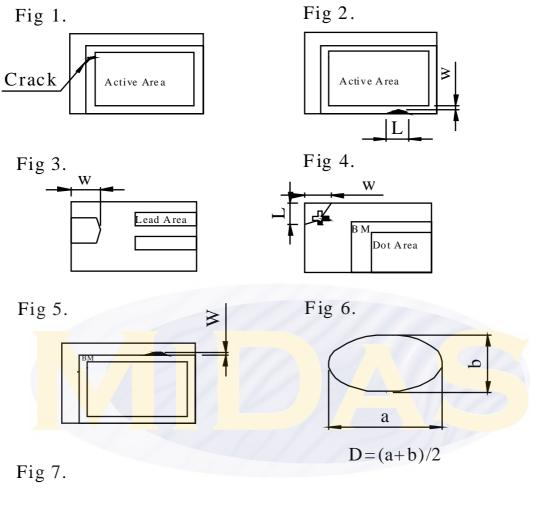

# (3) Appearance inspection

| NO. | ltem                                 | Standards                                                                                   |

|-----|--------------------------------------|---------------------------------------------------------------------------------------------|

| 1   | Panel Crack                          | Not allow. It is shown in Fig.1.                                                            |

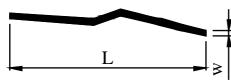

| 2   | Broken CF Non -lead<br>Side of TFT   | The broken in the area of W > 2mm is ignored, L is ignored. It is shown in Fig.2.           |

| 3   | Broken Lead Side of TFT              | FPC lead, electrical line or alignment mark can't be damaged. It is shown in Fig.3.         |

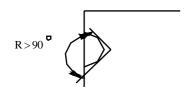

| 4   | Broken Comer of TFT at Lead Side     | FPC lead. electrical line or alignment mark can't be damaged. It is shown in Fig.4.         |

| 5   | Burr of TFT / CF Edge                | The distance of burr from the edge of TFT / CF, W $\leq$ 0.3mm. It is shown in Fig.5.       |

| 6   | Foreign Black /<br>White/Bright Spot | (1) 0.15 < D $\leq$ 0.5 mm, N $\leq$ 4 ; (2) D $\leq$ 0.15mm, Ignore. It is shown in Fig.6. |

| 7   | Foreign Black /<br>White/Bright Line | $ \begin{array}{l} \hbox{(1) 0.05$                                                          |

| 8   | Color irregular                      | Not remarkable color irregular.                                                             |

Fig8.

Notes

- 1.W:Widh

- 2.Lengh

- 3.D:Average Diameter 4.N:Count

- 5.All the anhle of the broken must be larger than 90~.It is shown in Fig.8.(R>90 $\sim$ )

#### NOTICE:

- SAFETY

- 1. If the LCD panel breaks, be careful not to get the liquid crystal to touch your skin.

- 2. If the liquid crystal touches your skin or clothes, please wash it off immediately by using soap and water.

- HANDLING

- 1. Avoid static electricity which can damage the CMOS LSI.

- 2. Do not remove the panel or frame from the module.

- 3. The polarizing plate of the display is very fragile. So, please handle it very carefully.

- 4. Do not wipe the polarizing plate with a dry cloth, as it may easily scratch the surface of plate.

- 5. Do not use ketonics solvent & Aromatic solvent. Use a soft cloth soaked with a cleaning naphtha solvent.

- STORAGE

- 1. Store the panel or module in a dark place where the temperature is 25±5°C and the humidity is below 65% RH.

- 2. Do not place the module near organics solvents or corrosive gases.

- 3. Do not crush, shake, or jolt the module.

- TERMS OF WARRANT

- 1. Acceptance inspection period

The period is within one month after the arrival of contracted commodity at the buyer's factory site.

2. Applicable warrant period

The period is within twelve months since the date of shipping out under normal using and storage conditions.