# W DESIGN SC1452 Dual 150mA LDO Regulator with Programmable Reset

# POWER MANAGEMENT

#### Description

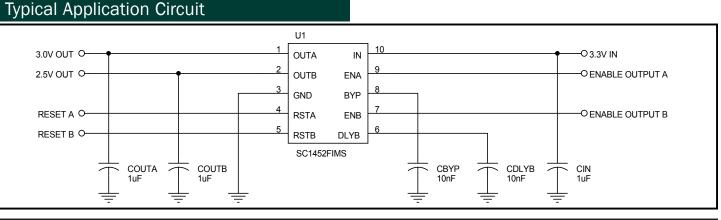

The SC1452 is a state of the art device intended to provide maximum performance and flexibility in battery operated systems. It has been designed specifically to fully support a single Li-lon battery and its external charger voltages.

The SC1452 contains two independently enabled, ultra low dropout voltage regulators (ULDOs). It operates from an input voltage range of 2.25V to 6.5V, and a wide variety of output voltage options are available which are designed to provide an initial tolerance of  $\pm 1\%$  and  $\pm 2\%$  over temperature.

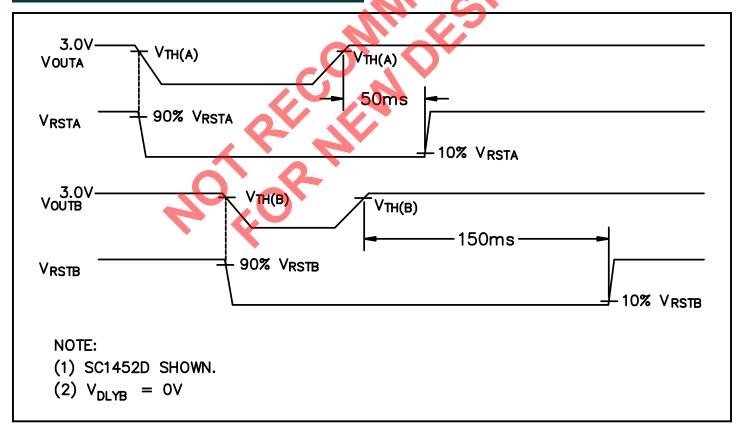

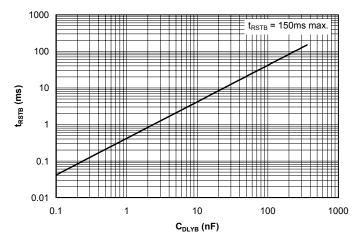

Each regulator has an associated active-low reset signal which is asserted when the voltage output declines below the preset threshold. Once the output recovers, the reset continues to be asserted (delayed) for a predetermined time, 50ms for reset A and 150ms for reset B. In the case of regulator B, the delay time may be reduced by the addition of an external capacitor.

The SC1452 has a bypass pin to enable the user to capacitively decouple the bandgap reference for very low output noise (down to  $50\mu$ Vrms).

The devices utilize CMOS technology to achieve very low operating currents (typically 130uA with both outputs supplying 150mA). The dropout voltage is typically 155mV at 150mA, helping to prolong battery life. In addition, the devices are guaranteed to provide 400mA of peak current for applications which require high initial inrush current. They have been designed to be used with low ESR ceramic capacitors to save cost and PCB area.

The SC1452 comes in the low profile 10-lead MSOP package.

#### Features

- Up to 150mA per regulator output

- Low quiescent current (130µA typical with both outputs at 150mA)

- Low dropout voltage

- Wide selection of output voltages

- Stable operation with ceramic caps

- Tight load and line regulation

- Current and thermal limiting

- Reverse input polarity protection

- <1µA off-mode current</p>

- ◆ Logic controlled enable

- Active low resets valid for V<sub>IN</sub> down to OV

- Programmable reset

- Full industrial temperature range

- 10-Pin MSOP package. Also available in Lead-free, fully WEEE and RoHS compliant

#### Applications

- Cellular telephones

- Palmtop/Laptop computers

- Battery-powered equipment

- Bar code scanners

- SMPS post regulator/dc to dc modules

- High efficiency linear power supplies

- DSP supplies

#### Absolute Maximum Ratings

Exceeding the specifications below may result in permanent damage to the device, or device malfunction. Operation outside of the parameters specified in the Electrical Characteristics section is not implied. Exposure to Absolute Maximum rated conditions for extended periods of time may affect device reliability.

| Parameter                             | Symbol           | Maximum                | Units |

|---------------------------------------|------------------|------------------------|-------|

| Input Supply Voltage                  | V <sub>IN</sub>  | -5 to +7               | V     |

| Enable Input Voltage                  | V <sub>EN</sub>  | -5 to +V <sub>IN</sub> | V     |

| Operating Ambient Temperature Range   | T <sub>A</sub>   | -40 to +85             | С°    |

| Operating Junction Temperature Range  | TJ               | -40 to +125            | °C    |

| Storage Temperature                   | T <sub>stg</sub> | -60 to +150            | °C    |

| Thermal Impedance Junction to Ambient | $\theta_{JA}$    | 113                    | °C/W  |

| Thermal Impedance Junction to Case    | θ <sub>JC</sub>  | 42                     | °C/W  |

| ESD Rating (Human Body Model)         | ESD              | 2                      | kV    |

#### **Electrical Characteristics**

Unless specified:  $T_A = 25^{\circ}C$ ,  $V_{IN} = V_{OUT} + 1V$ ,  $I_{OUTA} = I_{OUTB} = 1$ mA,  $C_{IN} = C_{OUT} = 1.0 \mu$ F,  $V_{ENA} = V_{ENB}$ Values in **bold** apply over full operating temperature range.

| Parameter                     | Symbol                | Conditions                                                                                              | Min  | Тур              | Max | Units |

|-------------------------------|-----------------------|---------------------------------------------------------------------------------------------------------|------|------------------|-----|-------|

| IN                            |                       | C.N                                                                                                     | -    |                  | 1   |       |

| Input Supply Voltage          | V <sub>IN</sub>       |                                                                                                         | 2.25 |                  | 6.5 | V     |

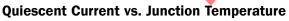

| Quiescent Current             | Ι <sub>α</sub>        | $V_{eNA} = 0V, V_{eNB} = V_{N}, I_{OUTB} = 150 \text{mA or}$                                            |      | 110              | 150 | μA    |

|                               |                       | V <sub>ENE</sub> = 0V, V <sub>ENA</sub> = V <sub>IN</sub> , I <sub>OUTA</sub> = 150mA                   |      |                  | 200 |       |

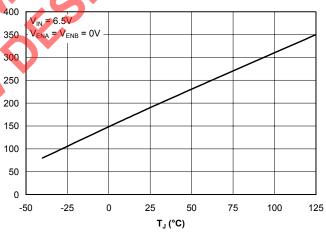

|                               |                       | $V_{\text{ENA}} = V_{\text{ENB}} = V_{\text{IN}}$ , $I_{\text{OUTA}} = I_{\text{OUTB}} = 150 \text{mA}$ |      | 130              | 200 | μA    |

|                               | $\checkmark$          |                                                                                                         |      |                  | 250 |       |

|                               |                       | $V_{IN}$ = 6.5V, $V_{ENA}$ = $V_{ENB}$ = 0V (OFF)                                                       |      | 0.2              | 1.0 | μA    |

|                               |                       |                                                                                                         |      |                  | 1.5 |       |

| OUTA, OUTB                    |                       |                                                                                                         |      |                  |     |       |

| Output Voltage <sup>(1)</sup> | V <sub>OUT</sub>      | I <sub>OUT</sub> = 1mA                                                                                  | -1%  | V <sub>OUT</sub> | +1% | V     |

|                               |                       | $0mA \leq I_{_{OUT}} \leq 150mA,  V_{_{OUT}} + 1V \leq V_{_{I\!N}} \leq 5.5V$                           | -2%  |                  | +2% |       |

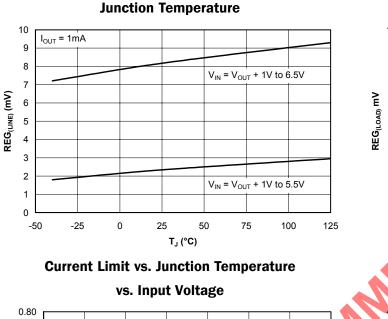

| Line Regulation(1)            |                       | $V_{_{OUT}}$ + 1V $\leq$ $V_{_{IN}} \leq$ 5.5V, I $_{_{OUT}}$ = 1mA                                     |      | 2.5              | 10  | mV    |

|                               |                       |                                                                                                         |      |                  | 12  |       |

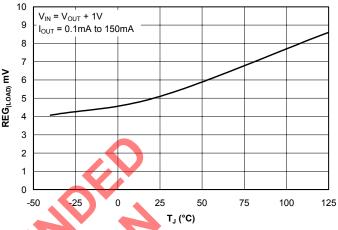

| Load Regulation(1)            | REG <sub>(LOAD)</sub> | $0.1 \text{mA} \leq I_{\text{out}} \leq 150 \text{mA}$                                                  |      | -5               | -20 | mV    |

|                               |                       |                                                                                                         |      |                  | -30 |       |

## POWER MANAGEMENT

## Electrical Characteristics (Cont.)

Unless specified:  $T_A = 25^{\circ}C$ ,  $V_{IN} = V_{OUT} + 1V$ ,  $I_{OUTA} = I_{OUTB} = 1mA$ ,  $C_{IN} = C_{OUT} = 1.0 \mu$ F,  $V_{ENA} = V_{ENB} = V_{IN}$ . Values in **bold** apply over full operating temperature range.

| Parameter                                | Symbol                | Conditions                                                                                                           | Min  | Тур   | Мах  | Units             |

|------------------------------------------|-----------------------|----------------------------------------------------------------------------------------------------------------------|------|-------|------|-------------------|

| Dropout Voltage <sup>(1)(2)</sup>        | V <sub>D</sub>        | I <sub>OUT</sub> = 1mA                                                                                               |      | 1     |      | mV                |

|                                          |                       | I <sub>OUT</sub> = 50mA                                                                                              |      | 52    | 70   | mV                |

|                                          |                       |                                                                                                                      |      |       | 90   |                   |

|                                          |                       | I <sub>out</sub> = 150mA                                                                                             |      | 155   | 210  | mV                |

|                                          |                       |                                                                                                                      |      |       | 270  |                   |

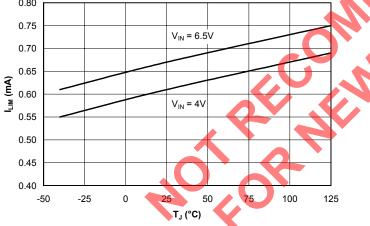

| Current Limit                            | ILIM                  |                                                                                                                      | 400  |       |      | mA                |

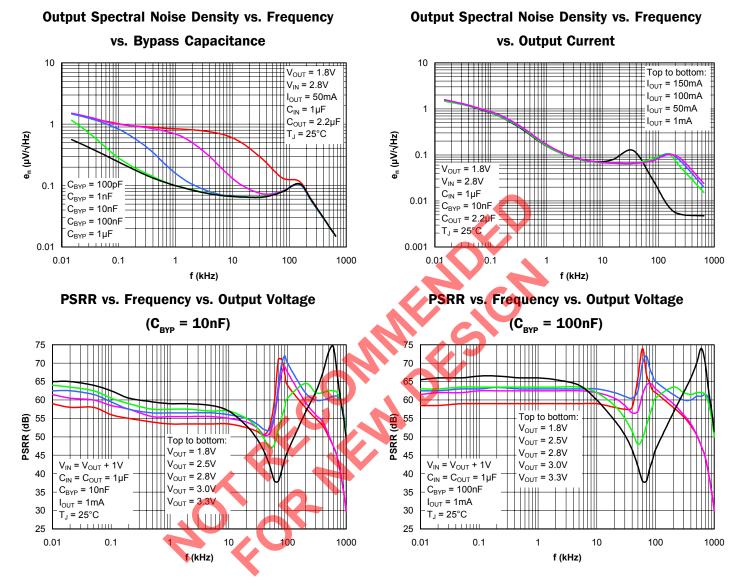

| Ripple Rejection                         | PSRR                  | f = 120Hz, C <sub>BYP</sub> = 10nF                                                                                   |      | 59    |      | dB                |

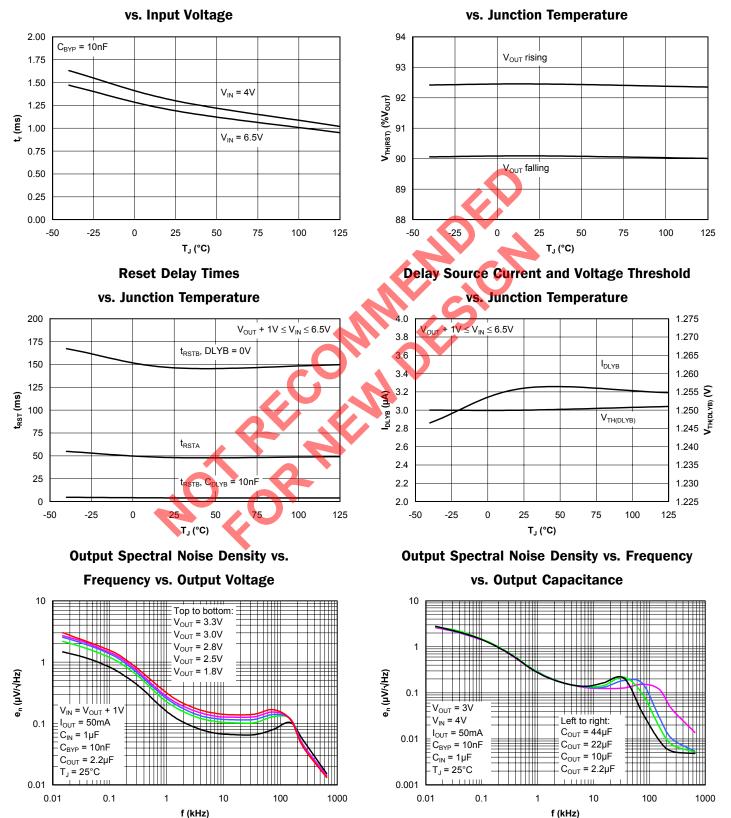

| Output Voltage Noise                     | e <sub>n</sub>        | f = 10Hz to 100kHz, I <sub>out</sub> = 50mA,<br>C <sub>BYP</sub> = 10nF, C <sub>out</sub> = 2,2 $\mu$ F, 1.8V output |      | 27    |      | μV <sub>RMS</sub> |

|                                          |                       | f = 10Hz to 100kHz, $I_{out}$ = 50mA,<br>C <sub>BYP</sub> = 10nF, C <sub>out</sub> = 2.2µF, 3.3V output              |      | 55    |      |                   |

| ВҮР                                      |                       |                                                                                                                      |      |       |      |                   |

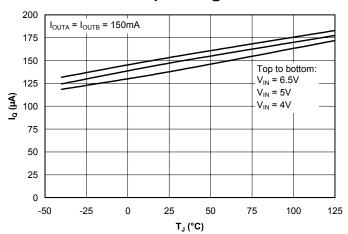

| Start-up Rise Time                       | t,                    | C <sub>BYP</sub> = 10nF                                                                                              |      | 1.25  |      | ms                |

| ENA, ENB                                 |                       |                                                                                                                      |      |       |      |                   |

| Enable Input Threshold                   | V <sub>H</sub>        |                                                                                                                      | 1.6  |       |      | V                 |

|                                          | VL                    |                                                                                                                      |      |       | 0.4  |                   |

| Enable Input Bias Current <sup>(3)</sup> | I <sub>ENA/B</sub>    | $0V \le V_{ENA/B} \le V_{IN}$                                                                                        | -0.5 |       | +0.5 | μA                |

| RSTA, RSTB                               |                       |                                                                                                                      |      |       |      |                   |

| Reset Threshold                          | V <sub>TH(RST)</sub>  | V <sub>out</sub> falling                                                                                             | 88   | 90    | 92   | %V <sub>OUT</sub> |

|                                          |                       | V <sub>out</sub> rising                                                                                              | 90   | 92    | 94   |                   |

| Reset A Delay                            | t <sub>rsta</sub>     |                                                                                                                      | 30   | 50    | 70   | ms                |

| Reset B Delay                            | t <sub>RSTB</sub>     | V <sub>DLYB</sub> = 0V                                                                                               | 90   | 150   | 210  | ms                |

|                                          |                       | C <sub>DLYB</sub> = 10nF                                                                                             |      | 4     |      |                   |

| Reset A, B Output Voltage (4)            | V <sub>OH</sub>       | I <sub>SOURCE</sub> = 0.5mA                                                                                          | 90   | 98    |      | %V <sub>OUT</sub> |

|                                          | V <sub>oL</sub>       | I <sub>SINK</sub> = 1.2mA                                                                                            |      | 0.02  | 0.10 | V                 |

| DLYB                                     |                       |                                                                                                                      |      |       |      |                   |

| Delay Voltage Threshold                  | V <sub>TH(DLYB)</sub> |                                                                                                                      |      | 1.250 |      | V                 |

| Delay Source Current                     | I <sub>DLYB</sub>     | V <sub>outb</sub> < V <sub>th</sub>                                                                                  | 2.1  | 3.0   | 3.9  | μA                |

#### POWER MANAGEMENT

#### Electrical Characteristics (Cont.)

Unless specified:  $T_A = 25^{\circ}C$ ,  $V_{IN} = V_{OUT} + 1V$ ,  $I_{OUTA} = I_{OUTB} = 1mA$ ,  $C_{IN} = C_{OUT} = 1.0 \mu$ F,  $V_{ENA} = V_{ENB} = V_{IN}$ . Values in **bold** apply over full operating temperature range.

| Parameter                   | Symbol            | Conditions | Min | Тур | Max | Units |  |

|-----------------------------|-------------------|------------|-----|-----|-----|-------|--|

| Over Temperature Protection |                   |            |     |     |     |       |  |

| High Trip Level             | T <sub>HI</sub>   |            |     | 150 |     | °C    |  |

| Hysteresis                  | T <sub>HYST</sub> |            |     | 20  |     | °C    |  |

#### NOTES:

(1) Low duty cycle pulse testing with Kelvin connections required.

(2) Defined as the input to output differential at which the output drops 100mV below the value measured at a differential of 1V. Not measurable on 1.5V and 1.8V outputs due to minimum  $V_{\rm M}$  constraints.

- (3) Guaranteed by design.

- (4)  $V_{OHA}$  will be a percentage of  $V_{OUTA}$ , and  $V_{OHB}$  will be a percentage of  $V_{OUTB}$

#### **Timing Diagrams**

option:

**Voltage Options**

Х

А

В

С

D

Е

F

Replace X in the part number (SC1452XIMS) by the

letter shown below for the corresponding voltage

$V_{outa}$  (V)

1.8

2.5

2.8

3.0

3.3

3.0

3.0

3.0

3.3

3.3

$V_{outb}$  (V)

1.8

2.5

2.8

3.0

3.3

2.5

1.8

2.8

2.5

2.8

# POWER MANAGEMENT

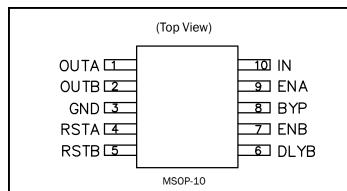

#### Pin Configuration

#### Ordering Information

| Part Numbers            | Package |

|-------------------------|---------|

| SC1452XIMSTR (1)(2)     |         |

| SC1452XIMSTRT (1)(2)(3) | MSOP-10 |

#### Notes:

(1) Where X denotes voltage options - see Voltage Options table.

(2) Only available in tape and reel packaging. A reel contains 2500 devices.

(3) Lead-free product. This product is fully WEEE and RoHS compliant.

#### Pin Descriptions

| Pin #  | Pin Name     | Pin Function                                                                                                                                                                                      |

|--------|--------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1      | OUTA         | Regulator A output                                                                                                                                                                                |

| 2      | OUTB         | Regulator B output.                                                                                                                                                                               |

| 3      | GND          | Ground pin.                                                                                                                                                                                       |

| 4      | RSTA         | Power on reset for output A. Active low when OUTA is below the reset threshold. RSTA goes high 50ms (typical) after OUTA rises above the reset threshold.                                         |

| 5      | RSTB         | Power on reset for output B. Active low when OUTB is below the reset threshold. RSTB goes high 150ms (typical - can be adjusted using $C_{_{DLYB}}$ ) after OUTB rises above the reset threshold. |

| 6      | DLYB         | Programmable delay for RESETB. Delay time can be set by connecting a capacitor, $C_{_{DLYB}}$ , between this pin and ground. Ground this pin if using the default delay time.                     |

| 7      | ENB          | Active high enable pin for output B. CMOS compatible input. Connect to IN if not being used.                                                                                                      |

| 8      | BYP          | Bypass pin for bandgap reference. Connect a 10nF capacitor, $C_{_{BYP}}$ , between this pin and ground for low noise operation.                                                                   |

| 9      | ENA          | Active high enable pin for output A. CMOS compatible input. Connect to IN if not being used.                                                                                                      |

| 10     | IN           | Input pin for both regulators.                                                                                                                                                                    |

| @ 2006 | Somtoch Corp | 5 www.semtech.com                                                                                                                                                                                 |

#### 5

SC1452

# POWER MANAGEMENT

MTECH

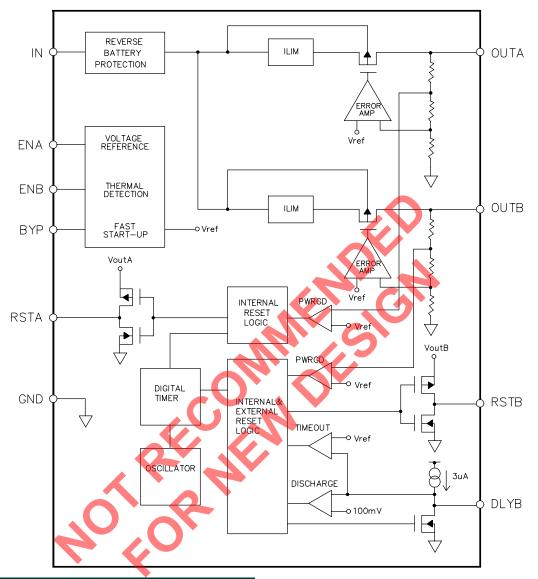

**Block Diagram**

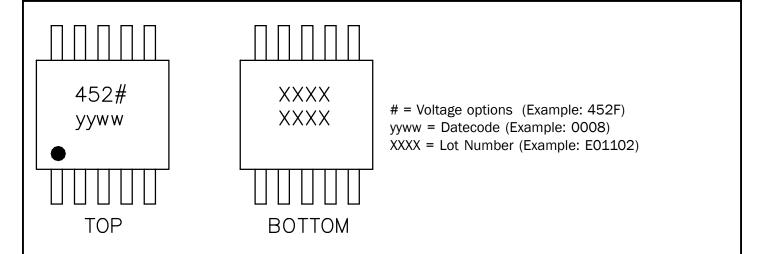

## Marking Information

#### Applications Information

#### **Theory Of Operation**

The SC1452 is intended for applications where very low dropout voltage, low supply current and low output noise are critical. Furthermore, the SC1452, by combining two ultra low dropout (ULDO) regulators, along with enable controls and power-on resets (which function is usually served by external devices), provides a very space efficient solution for multiple supply requirements.

The SC1452 contains two ULDOs, both of which are supplied by one input supply, between IN and GND. Each ULDO has its own active high enable pin (ENA/ENB). Pulling this pin low causes that specific ULDO to enter a very low power shutdown state.

Each ULDO also has its own power on reset pin (RSTA/ RSTB), which asserts low whenever the output voltage is below the reset threshold for that output. Each reset remains asserted low until a specific delay time after the output rises back above the reset threshold. For output A, this delay time is typically 50ms. Output B has a programmable reset delay. If DLYB is grounded, the reset delay will be controlled by an internal timer to 150ms. If a capacitor is connected between DLYB and GND, a constant current,  $I_{DLYB}$ , charges this capacitor until the delay threshold,  $V_{TH(DLYB)}$ , is reached, or the internal timer times out. See "Adjusting RSTB Delay Time". One advantage of on-board resets is that they remain asserted low all the way down to  $V_{IN} = 0V$ , whereas external devices may require pull-down resistors.

A bypass pin (BYP) is provided to decouple the bandgap reference to reduce output noise (on both outputs) and also to improve power supply rejection.

The SC1452 contains an internal bandgap reference which is fed into the inverting input of two error amplifiers, one for each output. The output voltage of each regulator is divided down internally using a resistor divider and compared to the bandgap voltage. The error amplifier drives the gate of a low  $R_{DS(ON)}$  P-channel MOSFET pass device.

Each regulator has its own current limit circuitry to ensure that the output current will not damage the device during output short, overload or start-up. The current limit is guaranteed to be greater than 400mA to allow fast charging of the output capacitor and high initial currents for DSP initialization.

The SC1452 has a fast start-up circuit to speed up the initial charging time of the bypass capacitor to enable the output voltage to come up quicker.

The SC1452 includes thermal shutdown circuitry to turn off the device if  $T_j$  exceeds 150°C (typical), with the device remaining off until  $T_j$  drops by 20°C (typical). Reverse battery protection circuitry ensures that the device cannot be damaged if the input supply is accidentally reversed, limiting the reverse current to less than 1.5mA.

#### Adjusting **RSTB** Delay Time

The power on reset delay for regulator B,  $t_{RSTB}$ , can be reduced externally by connecting a capacitor to the delay time set pin DLYB. If DLYB is connected to ground, the internally controlled delay time of 150ms (typ.) will apply.

Referring to the block diagram, as the output of regulator B ( $V_{outB}$ ) rises and reaches the reset threshold voltage (92%  $V_{outB(NOM)}$ ), two things happen:

1) the internal 150ms timer starts;

2) the 3µA current source turns on, charging  $\rm C_{_{DLYB}}$  (if connected).

If DLYB is connected to ground, RSTB goes high 150ms after  $V_{outb}$  crosses the threshold voltage. If a capacitor is connected between DLYB and ground, the voltage at DLYB can be described by the following equation:

$$V_{\text{DLYB}} = \frac{3 \bullet 10^{-6} \bullet t}{C_{\text{DLYB}}}$$

An internal comparator compares this voltage to a 1.25V reference, and triggers the reset high once this voltage is reached. The delay time can be calculated by rearranging the above equation, solving for t:

$$t_{\text{RSTB}} = \frac{C_{\text{DLYB}} \bullet 1.25}{3 \bullet 10^{-6}} = 416,667 \bullet C_{\text{DLYB}}$$

Note that the *maximum* delay time is 150ms, as RSTB goes high when either the internal timer or externally set timer times out, so if  $t_{\rm RSTB}$  is set externally for 200ms, the reset delay will still be 150ms. Thus for a 150ms delay, DLYB should be grounded, and for a delay time

### Applications Information (Cont.)

less than 150ms,  $\rm C_{_{DLYB}}$  can be calculated using the equation above, or read from the chart below.

#### **Component Selection**

Output capacitor - Semtech recommends a minimum capacitance of  $1\mu$ F at the output with an equivalent series resistance (ESR) of <  $1\Omega$  over temperature. The SC1452 has been designed to be used with ceramic capacitors, but does not have to be used with ceramic capacitors, allowing the designer a choice. Increasing the bulk capacitance will further reduce output noise and improve the overall transient response.

Input capacitor - Semtech recommends the use of a  $1\mu$ F ceramic capacitor at the input. This allows for the device being some distance from any bulk capacitance on the rail. Additionally, input droop due to load transients is reduced, improving overall load transient response.

Bypass capacitor - Semtech recommends the use of a 10nF ceramic capacitor to bypass the bandgap reference. Increasing this capacitor to 100nF will further improve power supply rejection.  $C_{\rm BYP}$  may be omitted if low noise operation is not required.

#### **Thermal Considerations**

The worst-case power dissipation for this part is given by:

$$P_{D(MAX)} = (V_{IN(MAX)} - V_{OUTA(MIN)}) \bullet I_{OUTA(MAX)} + (V_{IN(MAX)} - V_{OUTB(MIN)}) \bullet I_{OUTB(MAX)} + V_{IN(MAX)} \bullet I_{O(MAX)}$$

(1)

For all practical purposes, equation (1) can be reduced to the following expression:

$$P_{D(MAX)} = (V_{IN(MAX)} - V_{OUTA(MIN)}) \bullet I_{OUTA(MAX)} + (V_{IN(MAX)} - V_{OUTB(MIN)}) \bullet I_{OUTB(MAX)}$$

(2)

Looking at a typical application:

$V_{IN(MAX)} = 4.2V$   $V_{OUTA} = 3V - 2\% \text{ (worst case)} = 2.94V$   $V_{OUTB} = 3.3V - 2\% \text{ (worst case)} = 3.234V$   $I_{OUTA} = I_{OUTB} = 150\text{mA}$   $T_A = 85 ^{\circ}\text{C}$ Inserting these values into equation (2) above gives us:

$$P_{D(MAX)} = (4.2 - 2.94) \bullet 0.15 + (4.2 - 3.234) \bullet 0.15$$

= 0.189 + 0.145

= 0.334 W

Using this figure, we can calculate the maximum thermal impedance allowable to maintain  $T_1 \le 125$  °C:

$$\theta_{JA(MAX)} = \frac{(T_{J(MAX)} - T_{A(MAX)})}{P_{D(MAX)}}$$

$$= \frac{(125 - 85)}{0.334}$$

$$= 120^{\circ}C/W$$

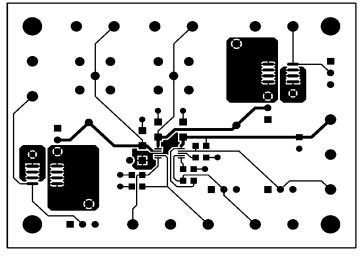

With the standard MSOP-10 Land Pattern shown at the end of this datasheet, and minimum trace widths, the thermal impedance junction to ambient for SC1452 is 113°C/W. Thus no additional heatsinking is required for the above conditions. The junction temperature can be further reduced by using larger trace widths and connecting pcb copper area to the GND pin (pin 3), which connects directly to the device substrate. Lower junction temperatures improve overall output voltage accuracy.

#### **Layout Considerations**

While layout for linear devices is generally not as critical as for a switching application, careful attention to detail will ensure reliable operation.

1) Attaching the part to a larger copper footprint will enable better heat transfer from the device, especially on PCBs where there are internal ground and power planes.

2) Place the input, output and bypass capacitors close to the device for optimal transient response and device behaviour.

SC1452

## POWER MANAGEMENT

## Applications Information (Cont.)

3) Connect all ground connections directly to the ground plane. If there is no ground plane, connect to a common local ground point before connecting to board ground.

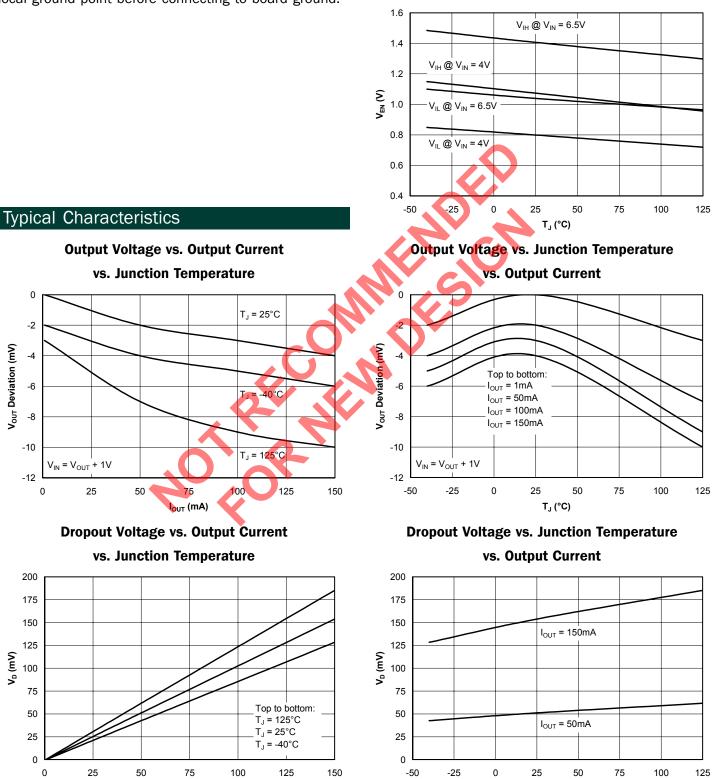

Enable Input Voltage vs. Junction Temperature vs. Input Voltage

IOUT (mA)

T<sub>J</sub> (°C)

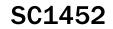

Typical Characteristics (Cont.)

Line Regulation vs.

EMTECH

vs. Output Current

Load Regulation vs. Junction Temperature

Off-State Quiescent Current

**Quiescent Current vs. Junction Temperature**

#### vs. Input Voltage

SC1452

**Reset Threshold Voltage**

# POWER MANAGEMENT

Typical Characteristics (Cont.)

#### Bypass Start-up Rise Time vs. Junction Temperature

EMTECH

© 2006 Semtech Corp.

## Typical Characteristics (Cont.)

EMTECH

## POWER MANAGEMENT

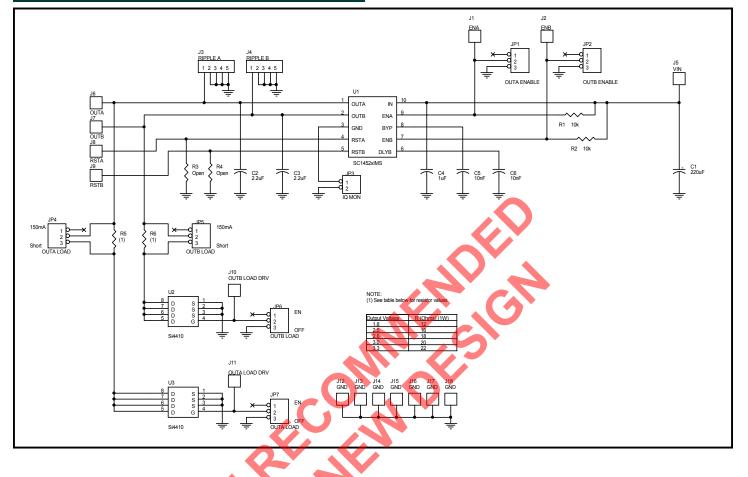

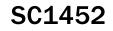

Evaluation Board Schematic

## Evaluation Board Gerber Plots

Top Copper

Bottom Copper

$\bigcirc$

$\bigcirc$

$\circ$   $\circ$

0

0 000

$\bigcirc$

0

Q

000

$^{\circ}$

0

$\bigcirc$

0

00

00 00

Ο

0

$\odot$

$\odot$

$\circ$

$\bigcirc$

000

0

0

00

0

Ο

Q

⊡0

$\bigcirc$

Ο

Ο

$\bigcirc$

Ο

Evaluation Board Gerber Plots (Cont.)

Top Silk Screen

## Evaluation Board Bill of Materials

| Quantity | Reference           | Part/Description | Vendor  | Notes                           |

|----------|---------------------|------------------|---------|---------------------------------|

| 1        | C1                  | 220µF, 10V       | Various |                                 |

| 2        | C2, C3              | 2.2µF ceramic    | Murata  | GRM42-6X7R225K16                |

| 1        | C4                  | 1µF ceramic      | Murata  | GRM42-6X7R105K25                |

| 2        | C5, C6              | 10nF ceramic     | Various |                                 |

| 2        | J1, J2              | Test pin         | Various | White                           |

| 2        | J3, J4              | BNC socket       | Various | V <sub>out</sub> ripple monitor |

| 3        | J5 - J7             | Test pin         | Various | Red                             |

| 2        | J8, J9              | Test pin         | Various | Yellow                          |

| 2        | J10, J11            | Test pin         | Various | Orange                          |

| 7        | J12 - J18           | Test pin         | Various | Black                           |

| 6        | JP1, JP2, JP4 - JP7 | Header, 3 pin    | Various |                                 |

| 1        | JP3                 | Header, 2 pin    | Various |                                 |

| 2        | R1, R2              | 10kΩ, 1/10W      | Various |                                 |

| 2        | R3, R4              | Not placed       |         |                                 |

| 2        | R5, R6              | See schematic    | Various | 1W                              |

| 1        | U1                  | SC1452xIMS       | Semtech |                                 |

| 2        | U2, U3              | Si4410           | Vishay  |                                 |

## POWER MANAGEMENT

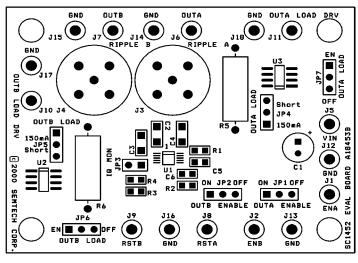

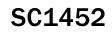

**Outline Drawing - MSOP-10**

ЛТЕСН

Semtech Corporation Power Management Products Division 200 Flynn Road, Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804