## QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 757A-A/-B ADDRESSABLE 2-WIRE BUS BUFFER

### LTC4302-1/LTC4302-2

#### DESCRIPTION

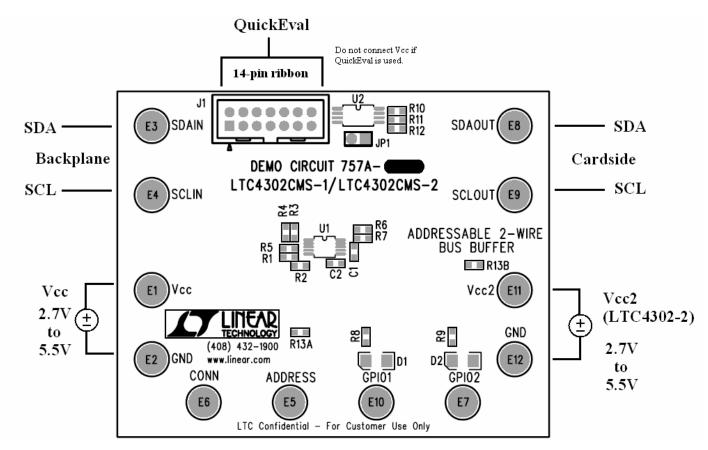

Demonstration circuit 757-A/-B features the LTC4302-1/LTC4302-2, an Addressable 2-Wire I2C bus and SMBus compatible Bus Buffer. The LTC4302-1/LTC4302-2 allows a peripheral board to be inserted and removed from a live backplane without corruption of the bus. The LTC4302-1/LTC4302-2 maintain electrical isolation between the backplane and peripheral board until their Vcc supply is valid and a master device on the backplane side addresses the LTC4302-1/LTC4302-2 and commands them to connect. The LTC4302-1/LTC4302-2 ADDRESS pin provides 32 possible addresses set by an external resistive divider between Vcc and GND. The LTC4302-1/LTC4302-2 work with supply voltages ranging from 2.7V to 5.5V. The SDA and SCL inputs and outputs do not load the bus lines when Vcc is low.

Rise time accelerator circuitry allows for heavier capacitive bus loading while still meeting system timing requirements. During insertion, the SDA and SCL lines are

precharged to 1V to minimize bus disturbances. Two general purpose input/output pins (GPIOs) on the LTC4302-1 can be configured as inputs, open-drain outputs or push-pull outputs. The status of a GPIO is displayed with an LED on the DC757-A/-B. The LTC4302-2 option replaces one GPIO pin with a second supply voltage pin VCC2, providing level shifting between systems with different supply voltages.

The DC757-A/-B is a part of the QuickEval systems which allows for quick and easy evaluation of the LTC4302-1/LTC4302-2 with a software interface.

Design files for this circuit board are available. Call the LTC factory.

#### **OPERATION**

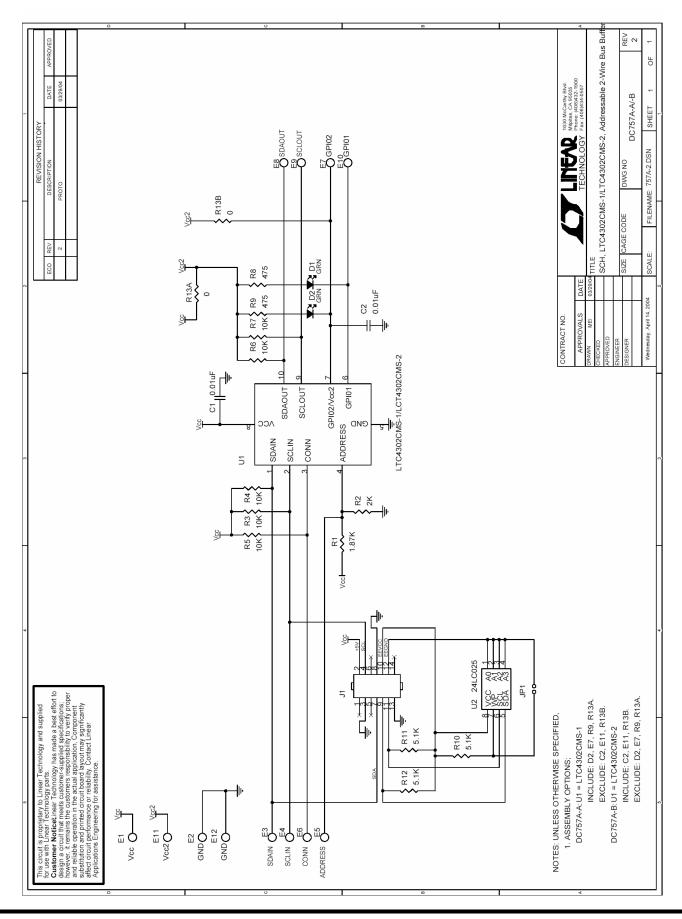

For operation with the DC757-A/-B, connect the backplane side supply of 2.7V to 5.5V to Vcc (as shown in Figure 1). For the DC757-B, with the LTC4302-2, connect the card side supply (2.7V to 5.5V) to Vcc2. The backplane SDA and SCL are connected to SDAIN and SCLIN respectively while the card side bus lines are connected to SDAOUT and SCLOUT. The host controller on the backplane side first addresses and configures the LTC4302-1/LTC4302-2 to connect the backplane to card side. Communication between the backplane and card side components are then established and a host controller on either side can then control the LTC4302-1/LTC4302-2. Additional configurations include enabling and disabling the rise time accelerators on the backplane side and/or the card side, setting the GPIO(s) to opendrain output, push-pull output, or input mode, and setting or resetting the GPIO(s) outputs. A host controller

can also read the internal registers of the LTC4302-1/LTC4302-2.

The CONN pin, when pulled low, resets the LTC4302-1/LTC4302-2 to its registers default state and disables communication to it. Communication can be reestablished when CONN is released high.

On the DC757-A/-B, the board's default values for resistors R1 and R2 are  $1.87 k\Omega$  and  $2 k\Omega$  respectively and set the address of the LTC4302-1/LTC4302-2 to (111 0000)<sub>2</sub>. For different addressing on multiple LTC4302-1/LTC4302-2s daisy chained on the same back plane, the resistors can be changed to values suggested in Table 1 of the data sheet.

The DC757 can be configured for either a -A or -B. For a -A board, U1 is an LTC4302-1, R13A pulls up the output lines and GPIOs to Vcc, and R13B and C2 are re-

moved. To change to a -B board, use an LTC4302-2 for U1, remove R13A, R9 and D2, and add C2 and R13B to

connect the Vcc2 pin to the corresponding test turret.

Figure 1. DC757-A/-B Equipment Setup

#### **QUICKEVAL SETUP**

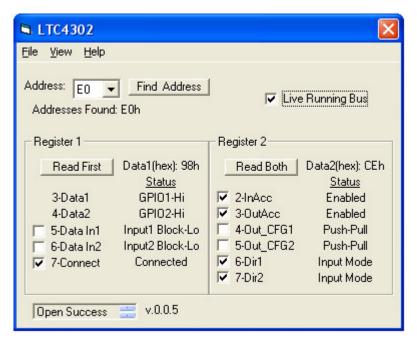

The DC757-A/-B connects to the QuickEval USB Controller DC590A via 14-pin ribbon cable. The DC590A is connected to a USB port on a PC. When the QuickEval software is opened, QuickEval will detect the DC757-A/-B and bring up the LTC4302-1/LTC4302-2 software interface (shown in Figure 2). Vcc is supplied from the DC590A and an external supply is not needed. Vcc2 however will still require power on the DC757-B.

Operation with the software interface starts with the selection of an address. Listed in the drop down menu are the 32 possible addresses for the LTC4302-1/LTC4302-2. By clicking the Find Address button, the software scans through the addresses and lists which addresses

respond with an Acknowledge. Select the address for the LTC4302-1/LTC4302-2 to be communicated with.

The LTC4302-1/LTC4302-2 has two Read/Write internal registers. Checking a bit on the interface sets the corresponding bit to a 1 and unchecking sets it to 0. The first data byte is read when Read First is clicked or a bit in the first register is changed. A two data byte read is carried out when Read Both is clicked or a bit in the second register is changed. The status display for each bit is updated after a read.

The Live Running Bus check box enables a timer that sends a bogus  $(0101\ 0101)_2$  data byte on the backplane bus lines every 100ms. This can be used for evaluation of the LTC4302-1/LTC4302-2 features. Connect a scope

## QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 757A-A/-B ADDRESSABLE 2-WIRE BUS BUFFER

probe on SCLIN and on SCLOUT then check the Live Running Bus. Check and uncheck the Connect bit to view on the scope the connection of the backplane to the card side and then the electrical isolation between the two. Enable and disable the rise time accelerators to view the difference in rise times.

Note: The DC590A board has its own bi-directional buffering that may have an affect with the rise time accelerators of the LTC4302-1/LTC4302-2. Viewing the data lines with the data sent from the DC590A is not a true and accurate observation of the performance of the LTC4302-1/LTC4302-2. It is best to look at the clock lines when using the DC590A.

Figure 2. LTC4302-1/LTC4302-2 QuickEval Interface

# QUICK START GUIDE FOR DEMONSTRATION CIRCUIT 757A-A/-B ADDRESSABLE 2-WIRE BUS BUFFER