# Dual Input Multiservice Line Card Adaptive Clock Translator

Data Sheet AD9557

#### **FEATURES**

Supports GR-1244 Stratum 3 stability in holdover mode Supports smooth reference switchover with virtually no disturbance on output phase

Supports Telcordia GR-253 jitter generation, transfer, and tolerance for SONET/SDH up to OC-192 systems

Supports ITU-T G.8262 synchronous Ethernet slave clocks

Supports ITU-T G.823, G.824, G.825, and G.8261

Auto/manual holdover and reference switchover

2 reference inputs (single-ended or differential)

Input reference frequencies: 2 kHz to 1250 MHz

Reference validation and frequency monitoring (1 ppm)

Programmable input reference switchover priority

20-bit programmable input reference divider

2 pairs of clock output pins, with each pair configurable as a single differential LVDS/HSTL output or as 2 single-ended CMOS outputs

Output frequencies: 360 kHz to 1250 MHz

Programmable 17-bit integer and 24-bit fractional

feedback divider in digital PLL

Programmable digital loop filter covering loop bandwidths from 0.1 Hz to 5 kHz (2 kHz maximum for <0.1 dB of peaking)

Low noise system clock multiplier

Frame sync support

Adaptive clocking

Optional crystal resonator for system clock input

On-chip EEPROM to store multiple power-up profiles

Pin program function for easy frequency translation configuration

Software controlled power-down 40-lead, 6 mm × 6 mm, LFCSP package

#### **APPLICATIONS**

Network synchronization, including synchronous Ethernet and SDH to OTN mapping/demapping

Cleanup of reference clock jitter

SONET/SDH clocks up to OC-192, including FEC

Stratum 3 holdover, jitter cleanup, and phase transient control  $\,$

**Wireless base station controllers**

Cable infrastructure

**Data communications**

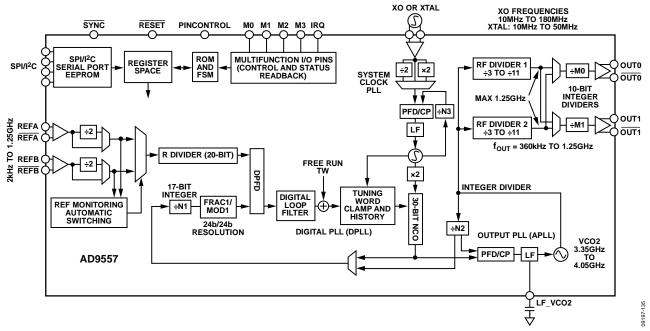

#### **GENERAL DESCRIPTION**

The AD9557 is a low loop bandwidth clock multiplier that provides jitter cleanup and synchronization for many systems, including synchronous optical networks (SONET/SDH). The AD9557 generates an output clock synchronized to up to four external input references. The digital PLL allows for reduction of input time jitter or phase noise associated with the external references. The digitally controlled loop and holdover circuitry of the AD9557 continuously generates a low jitter output clock even when all reference inputs have failed.

The AD9557 operates over an industrial temperature range of -40°C to +85°C. If more inputs/outputs are needed, refer to the AD9558 for the four-input/six-output version of the same part.

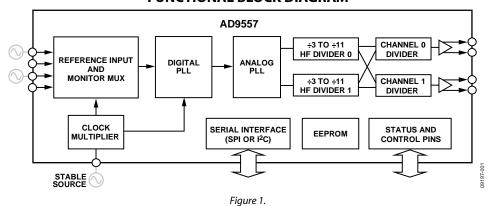

#### **FUNCTIONAL BLOCK DIAGRAM**

# **TABLE OF CONTENTS**

| Features1                                                  | Digital PLL (DPLL) Core                                | 30 |

|------------------------------------------------------------|--------------------------------------------------------|----|

| Applications1                                              | Loop Control State Machine                             | 32 |

| General Description1                                       | System Clock (SYSCLK)                                  | 33 |

| Functional Block Diagram1                                  | System Clock Inputs3                                   | 33 |

| Revision History                                           | SYStem Clock Multiplier3                               | 33 |

| Specifications4                                            | Output PLL (APLL)                                      | 35 |

| Supply Voltage4                                            | Clock Distribution3                                    | 36 |

| Supply Current4                                            | Clock Dividers                                         | 36 |

| Power Dissipation                                          | Output Power-Down3                                     | 36 |

| Logic Inputs (RESET, ASYNC, PINCONTROL, M3 to              | Output Enable3                                         | 36 |

| M0A)5                                                      | Output Mode3                                           | 36 |

| Logic Outputs (M3 to M0, IRQ)6                             | Clock Distribution Synchronization                     | 36 |

| System Clock Inputs (XOA, XOB)6                            | Status and Control                                     | 37 |

| Reference Inputs                                           | Multifunction Pins (M3 to M0)                          | 37 |

| Reference Monitors                                         | IRQ Pin                                                | 37 |

| Reference Switchover Specifications                        | Watchdog Timer3                                        | 38 |

| Distribution Clock Outputs9                                | EEPROM                                                 | 38 |

| Time Duration of Digital Functions                         | Serial Control Port4                                   | 14 |

| Digital PLL11                                              | SPI/I <sup>2</sup> C Port Selection4                   | 14 |

| Digital PLL Lock Detection11                               | SPI Serial Port Operation4                             | 14 |

| Holdover Specifications11                                  | I <sup>2</sup> C Serial Port Operation4                |    |

| Serial Port Specifications—SPI Mode12                      | Programming the I/O Registers                          | 51 |

| Serial Port Specifications—I <sup>2</sup> C Mode13         | Buffered/Active Registers5                             | 51 |

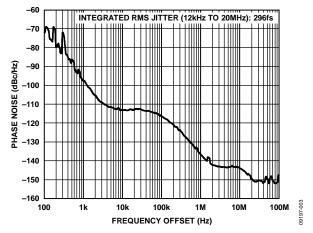

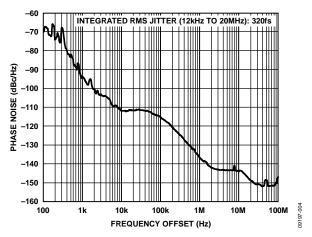

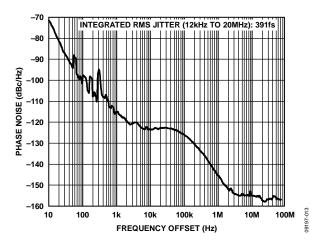

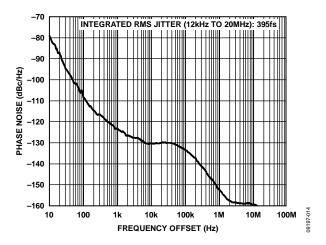

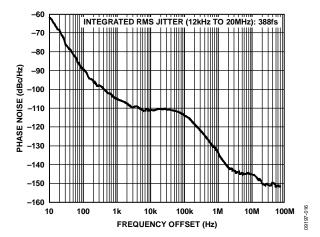

| Jitter Generation                                          | Autoclear Registers5                                   | 51 |

| Absolute Maximum Ratings16                                 | Register Access Restrictions5                          | 51 |

| ESD Caution                                                | Thermal Performance5                                   | 52 |

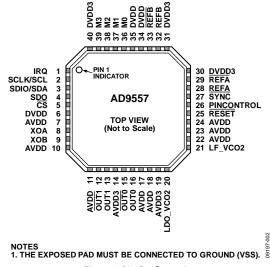

| Pin Configuration and Function Descriptions17              | Power Supply Partitions5                               | 53 |

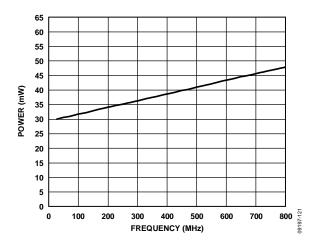

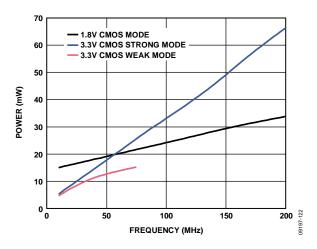

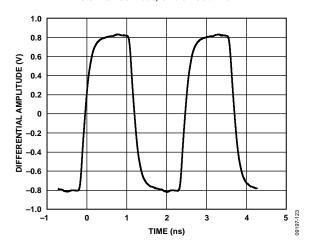

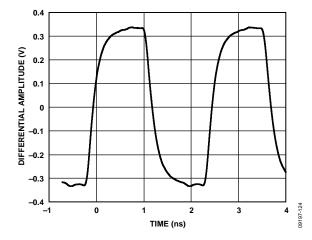

| Typical Performance Characteristics                        | Recommended Configuration for 3.3 V Switching Supply 5 | 53 |

| Input/Output Termination Recommendations24                 | Configuration for 1.8 V Supply                         | 53 |

| Getting Started                                            | Pin Program Function Description                       | 54 |

| Chip Power Monitor and Startup25                           | Overview of On-Chip ROM Features                       | 54 |

| Multifunction Pins at Reset/Power-Up25                     | Hard Pin Programming Mode5                             |    |

| Device Register Programming Using a Register Setup File 25 | Soft Pin Programming Mode Overview5                    |    |

| Register Programming Overview                              | Register Map5                                          | 56 |

| Theory of Operation                                        | Register Map Bit Descriptions6                         | 55 |

| Overview                                                   | Serial Port Configuration (Register 0x0000 to          |    |

| Reference Clock Inputs                                     | Register 0x0005)6                                      | 55 |

| Reference Monitors                                         | Silicon Revision (Register 0x000A)6                    | 55 |

| Reference Profiles                                         | Clock Part Serial ID (Register 0x000C to               |    |

| Reference Switchover                                       | Register 0x000D)6                                      | 55 |

| System Clock (Register 0x0100 to Register 0x0108)66                                                    | Operational Controls (Register 0x0A00 to                            | =0      |

|--------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------|---------|

| General Configuration (Register 0x0200 to                                                              | Register 0x0A0D)                                                    | .79     |

| Register 0x0214)67                                                                                     | Quick In/Out Frequency Soft Pin Configuration                       | 0.7     |

| IRQ Mask (Register 0x020A to Register 0x020F)68                                                        | (Register 0x0C00 to Register 0x0C08)                                |         |

| DPLL Configuration (Register 0x0300 to Register 0x032E) .69                                            | Status Readback (Register 0x0D00 to Register 0x0D14)                |         |

| Output PLL Configuration (Register 0x0400 to                                                           | EEPROM Control (Register 0x0E00 to Register 0x0E3C)                 | .86     |

| Register 0x0408)72                                                                                     | EEPROM Storage Sequence (Register 0x0E10 to                         |         |

| Output Clock Distribution (Register 0x0500 to                                                          | Register 0x0E3C)                                                    |         |

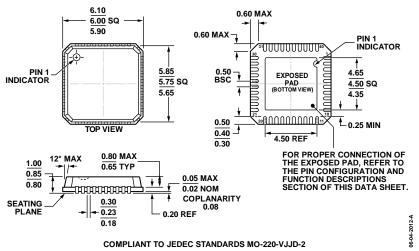

| Register 0x0515)74                                                                                     | Outline Dimensions                                                  | .92     |

| Reference Inputs (Register 0x0600 to Register 0x0602)76                                                | Ordering Guide                                                      | .92     |

| DPLL Profile Registers (Register 0x0700 to Register 0x0766)77                                          |                                                                     |         |

| REVISION HISTORY                                                                                       |                                                                     |         |

| 5/13—Rev. A to Rev. B                                                                                  | Changes to Register 0x000A, Table 35                                | . 56    |

| Change to Register 0x0101, Bit 4; Table 3556                                                           | Changes to Register 0x0304, Table 35                                | . 57    |

| Changes to Bit 4; Table 4366                                                                           | Change to Default Value in Register 0x0400 and Register 0x0403      |         |

| 3/12—Rev. 0 to Rev. A                                                                                  | Changes to Register 0x0405, Table 35                                |         |

| Change to Output Frequency Range Parameter, Table 66                                                   | Change to Bit 0, Register 0x070E, Table 35                          |         |

| Changes to Test Conditions/Comments Column, Table 9 8                                                  | Change to Bit 6, Register 0x0D01, Table 35                          |         |

| Changed Name of Pin 21 in Figure 217                                                                   | Added Address 0x0E3D to Address 0xE45, Table 35                     | . 64    |

| Changes to Table 20                                                                                    | Changes to Description, Register 0x0005, Table 38;                  |         |

| Changes to Chip Power Monitor and Startup, Device Register                                             | Added Table 40, Renumbered Sequentially; Changes to                 |         |

| Programming Using a Register Setup File, and Registers That                                            | Descriptions, Register 0x000C and Register 0x000D, Table 41         | . 65    |

| Differ from the Defaults for Optimal Performance Sections 25                                           | Changes to Summary Text, Register 0x0200 to                         | <u></u> |

| Changes to Initialize and Calibrate the Output PLL (APLL)                                              | Register 0x0209, Table 46 and Table 47                              | .67     |

| Section                                                                                                | Changes to Register 0x0304, Table 54; Change to Bits[7:6], Table 55 | 60      |

| Changes to Program the Reference Profiles Section; Changed                                             | Changes to Table Title, Table 63; Changes to Description,           | .05     |

| Lock the Digital PLL Section Name to Generate the Reference                                            | Register 0x0400 and Register 0x0403, Table 64                       | 73      |

| Acquisition; Changes to Generate the Reference Acquisition                                             | Changes to Register 0x0405, Table 64                                |         |

| Section                                                                                                | Changes to Description Column, Register 0x0500, Table 67;           | .,.     |

| Changes to Figure 35; Changed 225 MHz to 200 MHz and                                                   | Changes to Description Column, Register 0x0501, Bits[6:4]           |         |

| 3.45 GHz to 3.35 GHz in Overview Section                                                               | and Bit 0, Table 68                                                 | .74     |

| Changed 180 MHz to 175 MHz in DPLL Overview Section 30                                                 | Change to Description Column, Register 0x0505, Bits[6:4],           |         |

| Changed DPLL Output Frequency to DCO Frequency Throughout; Changes to Programmable Digital Loop Filter | Table 70                                                            | .75     |

| Section                                                                                                | Change to Register 0x0600, Bits[7:2], Table 72                      | . 76    |

| Changes to System Clock Inputs Section                                                                 | Changes to Register 0x0707; Change to Register 0x070A,              |         |

| Changed VCO2 Lower Frequency to 3.35 GHz in Figure 39;                                                 | Bits[3:0], Table 76                                                 | .77     |

| Changes to Output PLL (APLL) Section35                                                                 | Changes to Register 0x0A01, Table 87                                |         |

| Changed 1024 to 1023 in Clock Dividers Section;                                                        | Changes to Table 96                                                 |         |

| Changes to Divider Synchronization Section36                                                           | Changes to Register 0x0D01, Bit 6 and Bit 1, Table 99               |         |

| Changes to the Multifunction Pins (M0 to M3) Section                                                   | Added Table 123                                                     |         |

| Added the Programming the EEPROM to Configure an M Pin to                                              | Changes to Table 124                                                |         |

| Control Synchronization of the Clock Distribution Section42                                            | Changes to Table 125                                                | .91     |

| Changes to the Power Supply Partitions Section53                                                       | 10/11—Revision 0: Initial Version                                   |         |

| Changed 89.5° to 88.5° in DPLL Phase Margin Section54                                                  |                                                                     |         |

# **SPECIFICATIONS**

Minimum (min) and maximum (max) values apply for the full range of supply voltage and operating temperature variations. Typical (typ) values apply for AVDD3 = DVDD\_I/O = 3.3 V; AVDD = DVDD = 1.8 V;  $T_A = 25 ^{\circ}\text{C}$ , unless otherwise noted.

## **SUPPLY VOLTAGE**

Table 1.

| Parameter      | Min   | Тур  | Max   | Unit | Test Conditions/Comments |

|----------------|-------|------|-------|------|--------------------------|

| SUPPLY VOLTAGE |       |      |       |      |                          |

| DVDD3          | 3.135 | 3.30 | 3.465 | V    |                          |

| DVDD           | 1.71  | 1.80 | 1.89  | V    |                          |

| AVDD3          | 3.135 | 3.30 | 3.465 | V    |                          |

| AVDD           | 1.71  | 1.80 | 1.89  | V    |                          |

#### **SUPPLY CURRENT**

The test conditions for the maximum (max) supply current are the same as the test conditions for the All Blocks Running parameter of Table 3. The test conditions for the typical (typ) supply current are the same as the test conditions for the Typical Configuration parameter of Table 3.

Table 2.

| Parameter                                               | Min | Тур | Max | Unit | Test Conditions/Comments                                            |

|---------------------------------------------------------|-----|-----|-----|------|---------------------------------------------------------------------|

| SUPPLY CURRENT FOR TYPICAL CONFIGURATION                |     |     |     |      | Typical numbers are for the typical configuration listed in Table 3 |

| I <sub>DVDD3</sub>                                      | 12  | 18  | 26  | mA   | Pin 30, Pin 31, Pin 40                                              |

| I <sub>DVDD</sub>                                       | 13  | 20  | 28  | mA   | Pin 6, Pin 34, Pin 35                                               |

| l <sub>AVDD3</sub>                                      | 35  | 49  | 63  | mA   | Pin 14, Pin 19                                                      |

| lavdd                                                   | 112 | 162 | 215 | mA   | Pin 7, Pin 10, Pin 11, Pin 17, Pin 18, Pin 22, Pin 23, Pin 24       |

| SUPPLY CURRENT FOR THE ALL BLOCKS RUNNING CONFIGURATION |     |     |     |      | Maximum numbers are for all blocks running configuration in Table 3 |

| I <sub>DVDD3</sub>                                      | 12  | 18  | 33  | mA   | Pin 30, Pin 31, Pin 40                                              |

| I <sub>DVDD</sub>                                       | 10  | 19  | 30  | mA   | Pin 6, Pin 34, Pin 35                                               |

| l <sub>AVDD3</sub>                                      | 47  | 68  | 89  | mA   | Pin 14, Pin 19                                                      |

| I <sub>AVDD</sub>                                       | 113 | 163 | 215 | mA   | Pin 7, Pin 10, Pin 11, Pin 17, Pin 18, Pin 22, Pin 23, Pin 24       |

# **POWER DISSIPATION**

Table 3.

| Parameter                         | Min  | Тур  | Max  | Unit | Test Conditions/Comments                                                                                                                                                                                                 |

|-----------------------------------|------|------|------|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| POWER DISSIPATION                 |      |      |      |      |                                                                                                                                                                                                                          |

| Typical Configuration             | 0.36 | 0.55 | 0.76 | W    | System clock: 49.152 MHz crystal; DPLL active; both 19.44 MHz input references in differential mode; one HSTL driver at 644.53125 MHz; one 3.3 V CMOS driver at 161.1328125 MHz and 80 pF capacitive load on CMOS output |

| All Blocks Running                | 0.39 | 0.61 | 0.85 | W    | System clock: 49.152 MHz crystal; DPLL active;<br>both input references in differential mode;<br>one HSTL driver at 750 MHz;<br>two 3.3 V CMOS drivers at 250 MHz and 80 pF capacitive<br>load on CMOS outputs           |

| Full Power-Down                   |      | 44   | 125  | mW   | Typical configuration with no external pull-up or pull-down resistors; about 2/3 of this power is on AVDD3                                                                                                               |

| Incremental Power Dissipation     |      |      |      |      | Conditions = typical configuration; table values show the change in power due to the indicated operation                                                                                                                 |

| Input Reference On/Off            |      |      |      |      |                                                                                                                                                                                                                          |

| Differential Without Divide-by-2  | 20   | 25   | 32   | mW   | Additional current draw is in the DVDD3 domain only                                                                                                                                                                      |

| Differential With Divide-by-2     | 26   | 32   | 40   | mW   | Additional current draw is in the DVDD3 domain only                                                                                                                                                                      |

| Single-Ended Without Divide-by-2  | 5    | 7    | 9    | mW   | Additional current draw is in the DVDD3 domain only                                                                                                                                                                      |

| Output Distribution Driver On/Off |      |      |      |      |                                                                                                                                                                                                                          |

| LVDS (at 750 MHz)                 | 12   | 17   | 22   | mW   | Additional current draw is in the AVDD domain only                                                                                                                                                                       |

| HSTL (at 750 MHz)                 | 14   | 21   | 28   | mW   | Additional current draw is in the AVDD domain only                                                                                                                                                                       |

| 1.8 V CMOS (at 250 MHz)           | 14   | 21   | 28   | mW   | A single 1.8 V CMOS output with an 80 pF load                                                                                                                                                                            |

| 3.3 V CMOS (at 250 MHz)           | 18   | 27   | 36   | mW   | A single 3.3 V CMOS output with an 80 pF load                                                                                                                                                                            |

| Other Blocks On/Off               |      |      |      |      |                                                                                                                                                                                                                          |

| Second RF Divider                 | 36   | 51   | 64   | mW   | Additional current draw is in the AVDD domain only                                                                                                                                                                       |

| Channel Divider Bypassed          | 10   | 17   | 23   | mW   | Additional current draw is in the AVDD domain only                                                                                                                                                                       |

# LOGIC INPUTS (RESET, SYNC, PINCONTROL, M3 TO M0)

Table 4.

| Parameter                                            | Min | Тур | Max  | Unit | Test Conditions/Comments |

|------------------------------------------------------|-----|-----|------|------|--------------------------|

| LOGIC INPUTS (RESET, SYNC, PINCONTROL)               |     |     |      |      |                          |

| Input High Voltage (V <sub>H</sub> )                 | 2.1 |     |      | V    |                          |

| Input Low Voltage (V <sub>IL</sub> )                 |     |     | 8.0  | V    |                          |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> ) |     | ±50 | ±100 | μΑ   |                          |

| Input Capacitance (C <sub>IN</sub> )                 |     | 3   |      | pF   |                          |

| LOGIC INPUTS (M3 to M0)                              |     |     |      |      |                          |

| Input High Voltage (V <sub>H</sub> )                 | 2.5 |     |      | V    |                          |

| Input ½ Level Voltage (V <sub>IM</sub> )             | 1.0 |     | 2.2  | V    |                          |

| Input Low Voltage (V⊥)                               |     |     | 0.6  | V    |                          |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> ) |     | ±60 | ±100 | μΑ   |                          |

| Input Capacitance (C <sub>IN</sub> )                 |     | 3   |      | pF   |                          |

# LOGIC OUTPUTS (M3 TO M0, IRQ)

Table 5.

| Min         | Тур | Max  | Unit                       | Test Conditions/Comments    |

|-------------|-----|------|----------------------------|-----------------------------|

|             |     |      |                            |                             |

| DVDD3 - 0.4 |     |      | ٧                          | I <sub>OH</sub> = 1 mA      |

|             |     | 0.4  | V                          | $I_{OL} = 1 \text{ mA}$     |

|             |     |      |                            | Open-drain mode             |

|             |     | -200 | μΑ                         | V <sub>OH</sub> = 3.3 V     |

|             |     | 100  | μΑ                         | $V_{OL} = 0 V$              |

|             |     | 71   | DVDD3 - 0.4<br>0.4<br>-200 | DVDD3 – 0.4 V 0.4 V -200 μA |

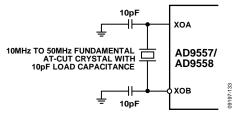

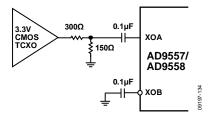

# **SYSTEM CLOCK INPUTS (XOA, XOB)**

# Table 6.

| Parameter                                                                     | Min  | Тур  | Max  | Unit   | Test Conditions/Comments                                                                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------|------|------|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| SYSTEM CLOCK MULTIPLIER                                                       |      |      |      |        |                                                                                                                                                                                                                                                                                                                                    |

| Output Frequency Range                                                        | 750  |      | 805  | MHz    | The VCO range may place limitations on nonstandard system clock input frequencies                                                                                                                                                                                                                                                  |

| Phase Frequency Detector (PFD) Rate                                           |      |      | 150  | MHz    |                                                                                                                                                                                                                                                                                                                                    |

| Frequency Multiplication Range                                                | 2    |      | 255  |        | Assumes valid system clock and PFD rates                                                                                                                                                                                                                                                                                           |

| SYSTEM CLOCK REFERENCE INPUT PATH                                             |      |      |      |        |                                                                                                                                                                                                                                                                                                                                    |

| Input Frequency Range                                                         | 10   |      | 400  | MHz    |                                                                                                                                                                                                                                                                                                                                    |

| Minimum Input Slew Rate                                                       | 20   |      |      | V/µs   | Minimum limit imposed for jitter performance                                                                                                                                                                                                                                                                                       |

| Common-Mode Voltage                                                           | 1.05 | 1.16 | 1.25 | V      | Internally generated                                                                                                                                                                                                                                                                                                               |

| Differential Input Voltage Sensitivity  System Clock Input Doubler Duty Cycle | 250  |      |      | mV p-p | Minimum voltage across pins required to ensure switching between logic states; the instantaneous voltage on either pin must not exceed the supply rails; can accommodate single-ended input by ac grounding of complementary input; 1 V p-p recommended for optimal jitter performance  This is the amount of duty cycle variation |

| -,,                                                                           |      |      |      |        | that can be tolerated on the system clock input to use the doubler                                                                                                                                                                                                                                                                 |

| System Clock Input = 50 MHz                                                   | 45   | 50   | 55   | %      |                                                                                                                                                                                                                                                                                                                                    |

| System Clock Input = 20 MHz                                                   | 46   | 50   | 54   | %      |                                                                                                                                                                                                                                                                                                                                    |

| System Clock Input = $16  \text{MHz}$ to $20  \text{MHz}$                     | 47   | 50   | 53   | %      |                                                                                                                                                                                                                                                                                                                                    |

| Input Capacitance                                                             |      | 3    |      | pF     | Single-ended, each pin                                                                                                                                                                                                                                                                                                             |

| Input Resistance                                                              |      | 4.2  |      | kΩ     |                                                                                                                                                                                                                                                                                                                                    |

| CRYSTAL RESONATOR PATH                                                        |      |      |      |        |                                                                                                                                                                                                                                                                                                                                    |

| Crystal Resonator Frequency Range                                             | 10   |      | 50   | MHz    | Fundamental mode, AT cut crystal                                                                                                                                                                                                                                                                                                   |

| Maximum Crystal Motional Resistance                                           |      |      | 100  | Ω      |                                                                                                                                                                                                                                                                                                                                    |

# **REFERENCE INPUTS**

Table 7.

| Parameter                                    | Min   | Тур | Max  | Unit | Test Conditions/Comments                                                                                                                                            |

|----------------------------------------------|-------|-----|------|------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| DIFFERENTIAL OPERATION                       |       |     |      |      |                                                                                                                                                                     |

| Frequency Range                              |       |     |      |      |                                                                                                                                                                     |

| Sinusoidal Input                             | 10    |     | 750  | MHz  |                                                                                                                                                                     |

| LVPECL Input                                 | 0.002 |     | 1250 | MHz  | The reference input divide-by-2 block must be engaged for $f_{\text{IN}} > 705 \text{ MHz}$                                                                         |

| LVDS Input                                   | 0.002 |     | 750  | MHz  | The reference input divide-by-2 block must be engaged for $f_{\text{IN}} > 705 \text{ MHz}$                                                                         |

| Minimum Input Slew Rate                      | 40    |     |      | V/µs | Minimum limit imposed for jitter performance                                                                                                                        |

| Common-Mode Input Voltage                    |       |     |      |      |                                                                                                                                                                     |

| AC-Coupled                                   | 1.9   | 2   | 2.1  | V    | Internally generated                                                                                                                                                |

| DC-Coupled                                   | 1.0   |     | 2.4  | V    |                                                                                                                                                                     |

| Differential Input Voltage Sensitivity       |       |     |      | mV   | Minimum differential voltage across pins is required to ensure switching between logic levels; instantaneous voltage on either pin must not exceed the supply rails |

| $f_{\text{IN}}$ < 800 MHz                    | 240   |     |      | mV   |                                                                                                                                                                     |

| $f_{IN} = 800 \text{ to } 1050 \text{ MHz}$  | 320   |     |      | mV   |                                                                                                                                                                     |

| $f_{IN} = 1050 \text{ to } 1250 \text{ MHz}$ | 400   |     |      | mV   |                                                                                                                                                                     |

| Differential Input Voltage Hysteresis        |       | 58  | 100  | mV   |                                                                                                                                                                     |

| Input Resistance                             |       | 21  |      | kΩ   |                                                                                                                                                                     |

| Input Capacitance                            |       | 3   |      | pF   |                                                                                                                                                                     |

| Minimum Pulse Width High                     |       |     |      |      |                                                                                                                                                                     |

| LVPECL                                       | 390   |     |      | ps   |                                                                                                                                                                     |

| LVDS                                         | 640   |     |      | ps   |                                                                                                                                                                     |

| Minimum Pulse Width Low                      |       |     |      |      |                                                                                                                                                                     |

| LVPECL                                       | 390   |     |      | ps   |                                                                                                                                                                     |

| LVDS                                         | 640   |     |      | ps   |                                                                                                                                                                     |

| SINGLE-ENDED OPERATION                       |       |     |      |      |                                                                                                                                                                     |

| Frequency Range (CMOS)                       | 0.002 |     | 300  | MHz  |                                                                                                                                                                     |

| Minimum Input Slew Rate                      | 40    |     |      | V/µs | Minimum limit imposed for jitter performance                                                                                                                        |

| Input Voltage High (V <sub>IH</sub> )        |       |     |      |      |                                                                                                                                                                     |

| 1.2 V to 1.5 V Threshold Setting             | 1.0   |     |      | V    |                                                                                                                                                                     |

| 1.8 V to 2.5 V Threshold Setting             | 1.4   |     |      | V    |                                                                                                                                                                     |

| 3.0 V to 3.3 V Threshold Setting             | 2.0   |     |      | V    |                                                                                                                                                                     |

| Input Voltage Low (V <sub>IL</sub> )         |       |     |      |      |                                                                                                                                                                     |

| 1.2 V to 1.5 V Threshold Setting             |       |     | 0.35 | V    |                                                                                                                                                                     |

| 1.8 V to 2.5 V Threshold Setting             |       |     | 0.5  | V    |                                                                                                                                                                     |

| 3.0 V to 3.3 V Threshold Setting             |       |     | 1.0  | V    |                                                                                                                                                                     |

| Input Resistance                             |       | 47  |      | kΩ   |                                                                                                                                                                     |

| Input Capacitance                            |       | 3   |      | pF   |                                                                                                                                                                     |

| Minimum Pulse Width High                     | 1.5   |     |      | ns   |                                                                                                                                                                     |

| Minimum Pulse Width Low                      | 1.5   |     |      | ns   |                                                                                                                                                                     |

## **REFERENCE MONITORS**

Table 8.

| Parameter                        | Min   | Тур | Max             | Unit                         | Test Conditions/Comments                                                                                                           |

|----------------------------------|-------|-----|-----------------|------------------------------|------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE MONITORS               |       |     |                 |                              |                                                                                                                                    |

| Reference Monitor                |       |     |                 |                              |                                                                                                                                    |

| Loss of Reference Detection Time |       |     | 1.1             | DPLL PFD period              | Nominal phase detector period = $R/f_{REF}^{1}$                                                                                    |

| Frequency Out-of Range Limits    | <2    |     | 10 <sup>5</sup> | Δf/f <sub>REF</sub><br>(ppm) | Programmable (lower bound is subject to quality of the system clock (SYSCLK)); SYSCLK accuracy must be better than the lower bound |

| Validation Timer                 | 0.001 |     | 65.535          | sec                          | Programmable in 1 ms increments                                                                                                    |

$<sup>^{1}</sup>$  f<sub>REF</sub> is the frequency of the active reference; R is the frequency division factor determined by the R divider.

# **REFERENCE SWITCHOVER SPECIFICATIONS**

Table 9.

| Parameter                                  | Min | Тур | Max  | Unit               | Test Conditions/Comments                                                                                                                                                                           |

|--------------------------------------------|-----|-----|------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE SWITCHOVER SPECIFICATIONS        |     |     |      |                    | Assumes a jitter-free reference; satisfies                                                                                                                                                         |

| Maximum Output Phase Perturbation          |     |     |      |                    | Telcordia GR-1244-CORE requirements; select                                                                                                                                                        |

| (Phase Build-Out Switchover)               |     |     |      |                    | high PM base loop filter bit (Register 0x070E, Bit 0) is set to 1 for all active references                                                                                                        |

| 50 Hz DPLL Loop Bandwidth                  |     |     |      |                    | Valid for automatic and manual reference switching                                                                                                                                                 |

| Peak                                       |     | 0   | ±100 | ps                 |                                                                                                                                                                                                    |

| Steady State                               |     | 0   | ±100 | ps                 |                                                                                                                                                                                                    |

| 2 kHz DPLL Loop Bandwidth                  |     |     |      |                    | Valid for automatic and manual reference switching                                                                                                                                                 |

| Peak                                       |     | 0   | ±250 | ps                 |                                                                                                                                                                                                    |

| Steady State                               |     | 0   | ±100 | ps                 |                                                                                                                                                                                                    |

| Time Required to Switch to a New Reference |     |     |      |                    |                                                                                                                                                                                                    |

| Phase Build-Out Switchover                 |     |     | 1.1  | DPLL PFD<br>period | Calculated using the nominal phase detector period (NPDP = $R/f_{REF}$ ); the total time required is equal to the time plus the reference validation time and the time required to lock to the new |

|                                            |     |     |      |                    | reference                                                                                                                                                                                          |

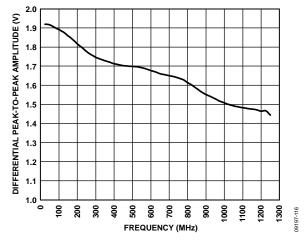

# **DISTRIBUTION CLOCK OUTPUTS**

Table 10.

| Parameter                                                       | Min                                        | Тур          | Max        | Unit                                  | Test Conditions/Comments                               |

|-----------------------------------------------------------------|--------------------------------------------|--------------|------------|---------------------------------------|--------------------------------------------------------|

| HSTL MODE                                                       |                                            | <del>-</del> |            |                                       |                                                        |

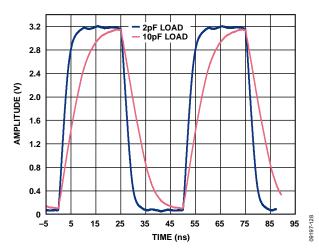

| Output Frequency                                                | 0.36                                       |              | 1250       | MHz                                   |                                                        |

| Rise/Fall Time (20% to 80%) <sup>1</sup>                        |                                            | 140          | 250        | ps                                    | $100 \Omega$ termination across output pins            |

| Duty Cycle                                                      |                                            |              |            | '                                     |                                                        |

| Up to f <sub>оит</sub> = 700 MHz                                | 45                                         | 48           | 52         | %                                     |                                                        |

| Up to $f_{OUT} = 750 \text{ MHz}$                               | 42                                         | 48           | 53         | %                                     |                                                        |

| Up to f <sub>оит</sub> = 1250 MHz                               |                                            | 43           |            | %                                     |                                                        |

| Differential Output Voltage Swing                               | 700                                        | 950          | 1200       | mV                                    | Magnitude of voltage across pins; output driver static |

| Common-Mode Output Voltage                                      | 700                                        | 870          | 960        | mV                                    | Output driver static                                   |

| LVDS MODE                                                       | 1                                          |              |            | 1                                     |                                                        |

| Output Frequency                                                | 0.36                                       |              | 1250       | MHz                                   |                                                        |

| Rise/Fall Time (20% to 80%) <sup>1</sup>                        | 0.50                                       | 185          | 280        | ps                                    | 100 $\Omega$ termination across the output pair        |

| Duty Cycle                                                      |                                            | 103          | 200        | P3                                    | 100 12 terrimiditori deross trie odipat pari           |

| Up to $f_{OUT} = 750 \text{ MHz}$                               | 44                                         | 48           | 53         | %                                     |                                                        |

| Up to four = 800 MHz                                            | 43                                         | 47           | 53         | %                                     |                                                        |

| Up to $f_{OUT} = 1250 \text{ MHz}$                              | 73                                         | 47           | <i>) )</i> | %                                     |                                                        |

| Differential Output Voltage Swing                               |                                            | 73           |            | /0                                    |                                                        |

| Balanced, V <sub>OD</sub>                                       | 247                                        |              | 454        | mV                                    | Voltage swing between output pins; output driver       |

| Balanceu, Vob                                                   | 247                                        |              | 434        | IIIV                                  | static                                                 |

| Unbalanced, ΔV <sub>OD</sub>                                    |                                            |              | 50         | mV                                    | Absolute difference between voltage swing of           |

| oribalaricea, a vop                                             |                                            |              | 30         | •                                     | normal pin and inverted pin; output driver static      |

| Offset Voltage                                                  |                                            |              |            |                                       |                                                        |

| Common Mode, Vos                                                | 1.125                                      | 1.26         | 1.375      | V                                     | Output driver static                                   |

| Common-Mode Difference, ΔVos                                    |                                            |              | 50         | mV                                    | Voltage difference between pins; output driver static  |

| Short-Circuit Output Current                                    |                                            | 13           | 24         | mA                                    | Output driver static                                   |

| CMOS MODE                                                       |                                            |              |            |                                       |                                                        |

| Output Frequency                                                |                                            |              |            |                                       |                                                        |

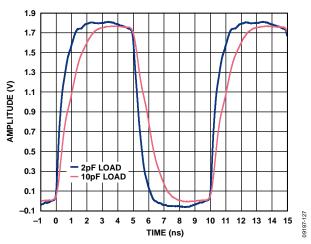

| 1.8 V Supply                                                    | 0.36                                       |              | 150        | MHz                                   | 10 pF load                                             |

| 3.3 V Supply (OUT0)                                             |                                            |              |            |                                       |                                                        |

| Strong Drive Strength Setting                                   | 0.36                                       |              | 250        | MHz                                   | 10 pF load                                             |

| Weak Drive Strength Setting                                     | 0.36                                       |              | 25         | MHz                                   | 10 pF load                                             |

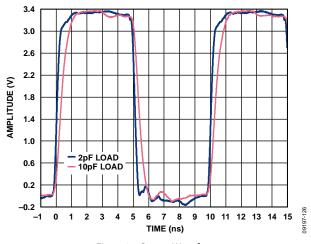

| Rise/Fall Time(20% to 80%) <sup>1</sup>                         | 0.50                                       |              | 23         | 141112                                | To pri loud                                            |

| 1.8 V Supply                                                    |                                            | 1.5          | 3          | ns                                    | 10 pF load                                             |

| 3.3 V Supply                                                    |                                            | 1.5          | 3          | 113                                   | To pri loud                                            |

| Strong Drive Strength Setting                                   |                                            | 0.4          | 0.6        | ns                                    | 10 pF load                                             |

| Weak Drive Strength Setting                                     |                                            | 8            | 0.0        | ns                                    | 10 pF load                                             |

| Duty Cycle                                                      |                                            | U            |            | 113                                   | To priload                                             |

| 1.8 V Mode                                                      |                                            | 50           |            | %                                     | 10 pF load                                             |

| 3.3 V Strong Mode                                               |                                            | 47           |            | %                                     | 10 pF load                                             |

| 3.3 V Weak Mode                                                 |                                            | 51           |            | %                                     | 10 pF load                                             |

| Output Voltage High (V <sub>он</sub> )                          |                                            | <i>3</i> I   |            | 70                                    | Output driver static; strong drive strength            |

| AVDD3 = $3.3 \text{ V, loh} = 10 \text{ mA}$                    | V/\DD3 \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ |              |            | V                                     | Output driver static, strong drive strength            |

| AVDD3 = 3.3  V,  IOH = 10  IIIA<br>AVDD3 = 3.3  V,  IOH = 1  mA | AVDD3 – 0.3<br>AVDD3 – 0.1                 |              |            | V                                     |                                                        |

|                                                                 |                                            |              |            | V                                     |                                                        |

| AVDD3 = $1.8 \text{ V}$ , $I_{OH} = 1 \text{ mA}$               | AVDD – 0.2                                 |              |            | V                                     | Output driver statics strong drive strong th           |

| Output Voltage Low (Vol)                                        |                                            |              | 0.2        | \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ | Output driver static; strong drive strength            |

| $AVDD3 = 3.3 \text{ V, } I_{OL} = 10 \text{ mA}$                |                                            |              | 0.3        | V                                     |                                                        |

| $AVDD3 = 3.3 \text{ V, } I_{OL} = 1 \text{ mA}$                 |                                            |              | 0.1        | V                                     |                                                        |

| $AVDD3 = 1.8 \text{ V, } I_{OL} = 1 \text{ mA}$                 |                                            |              | 0.1        | V                                     |                                                        |

| Parameter                                                    | Min        | Тур  | Max  | Unit | Test Conditions/Comments                                                |

|--------------------------------------------------------------|------------|------|------|------|-------------------------------------------------------------------------|

| OUTPUT TIMING SKEW                                           |            |      |      |      | 10 pF load                                                              |

| Between OUT0 and OUT1                                        |            | 10   | 70   | ps   | HSTL mode on both drivers; rising edge only; any divide value           |

| Additional Delay on One Driver by<br>Changing Its Logic Type |            |      |      |      |                                                                         |

| HSTL to LVDS                                                 | <b>-</b> 5 | +1   | +5   | ps   | Positive value indicates that the LVDS edge is delayed relative to HSTL |

| HSTL to 1.8 V CMOS                                           | -5         | 0    | +5   | ps   | Positive value indicates that the CMOS edge is delayed relative to HSTL |

| OUT1 HSTL to OUT0 3.3 V CMOS,<br>Strong Mode                 |            | 3.53 | 3.59 | ns   | The CMOS edge is delayed relative to HSTL                               |

<sup>&</sup>lt;sup>1</sup> The listed values are for the slower edge (rise or fall).

# TIME DURATION OF DIGITAL FUNCTIONS

Table 11.

| Parameter                          | Min | Тур | Max | Unit | Test Conditions/Comments                                                       |

|------------------------------------|-----|-----|-----|------|--------------------------------------------------------------------------------|

| TIME DURATION OF DIGITAL FUNCTIONS |     |     |     |      |                                                                                |

| EEPROM-to-Register Download Time   |     | 13  | 20  | ms   | Using default EEPROM storage sequence (see Register 0x0E10 to Register 0x0E3F) |

| Register-to-EEPROM Upload Time     |     | 138 | 145 | ms   | Using default EEPROM storage sequence (see Register 0x0E10 to Register 0x0E3F  |

| Minimum Power-Down Exit Time       |     | 1   |     | ms   | Time from power-down exit to system clock lock detect                          |

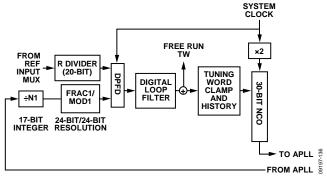

## **DIGITAL PLL**

## Table 12.

| Parameter                                               | Min  | Тур | Max             | Unit    | Test Conditions/Comments                                                                                                      |

|---------------------------------------------------------|------|-----|-----------------|---------|-------------------------------------------------------------------------------------------------------------------------------|

| DIGITAL PLL                                             |      |     |                 |         |                                                                                                                               |

| Phase-Frequency Detector (PFD)<br>Input Frequency Range | 2    |     | 100             | kHz     |                                                                                                                               |

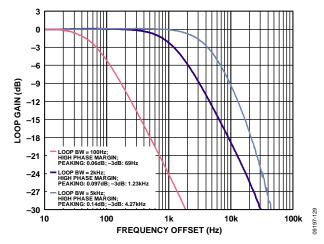

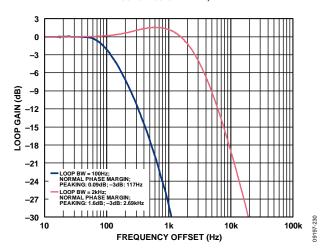

| Loop Bandwidth                                          | 0.1  |     | 2000            | Hz      | Programmable design parameter                                                                                                 |

| Phase Margin                                            | 30   |     | 89              | Degrees | Programmable design parameter                                                                                                 |

| Closed-Loop Peaking                                     | <0.1 |     |                 | dB      | Programmable design parameter; part can be programmed for <0.1 dB peaking in accordance with Telcordia GR-253 jitter transfer |

| Reference Input (R) Division Factor                     | 1    |     | 2 <sup>20</sup> |         | 1, 2,, 1,048,576                                                                                                              |

| Integer Feedback (N1) Division Factor                   | 180  |     | 2 <sup>17</sup> |         | 180, 181,, 131,072                                                                                                            |

| Fractional Feedback Divide Ratio                        | 0    |     | 0.999           |         | Maximum value: 16,777,215/16,777,216                                                                                          |

# **DIGITAL PLL LOCK DETECTION**

# Table 13.

| Parameter                   | Min   | Тур | Max    | Unit | Test Conditions/Comments                |

|-----------------------------|-------|-----|--------|------|-----------------------------------------|

| PHASE LOCK DETECTOR         |       |     |        |      |                                         |

| Threshold Programming Range | 0.001 |     | 65.5   | ns   |                                         |

| Threshold Resolution        |       | 1   |        | ps   |                                         |

| FREQUENCY LOCK DETECTOR     |       |     |        |      |                                         |

| Threshold Programming Range | 0.001 |     | 16,700 | ns   | Reference-to-feedback period difference |

| Threshold Resolution        |       | 1   |        | ps   |                                         |

# **HOLDOVER SPECIFICATIONS**

## Table 14.

| Parameter                  | Min | Тур   | Max | Unit | Test Conditions/Comments                                                                                                                            |  |  |  |

|----------------------------|-----|-------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| HOLDOVER SPECIFICATIONS    |     |       |     |      |                                                                                                                                                     |  |  |  |

| Initial Frequency Accuracy |     | <0.01 |     | ppm  | Excludes frequency drift of SYSCLK source; excludes frequency drift of input reference prior to entering holdover; compliant with GR-1244 Stratum 3 |  |  |  |

# SERIAL PORT SPECIFICATIONS—SPI MODE

Table 15.

| Parameter                                 | Min         | Тур | Max | Unit | Test Conditions/Comments          |

|-------------------------------------------|-------------|-----|-----|------|-----------------------------------|

| <u>cs</u>                                 |             |     |     |      |                                   |

| Input Logic 1 Voltage                     | 2.2         |     |     | V    |                                   |

| Input Logic 0 Voltage                     |             |     | 1.2 | V    |                                   |

| Input Logic 1 Current                     |             | 44  |     | μΑ   |                                   |

| Input Logic 0 Current                     |             | 88  |     | μΑ   |                                   |

| Input Capacitance                         |             | 2   |     | pF   |                                   |

| SCLK                                      |             |     |     |      | Internal 30 kΩ pull-down resistor |

| Input Logic 1 Voltage                     | 2.2         |     |     | V    |                                   |

| Input Logic 0 Voltage                     |             | 8.0 | 1.2 | V    |                                   |

| Input Logic 1 Current                     |             | 200 |     | μΑ   |                                   |

| Input Logic 0 Current                     |             | 1   |     | μΑ   |                                   |

| Input Capacitance                         |             | 2   |     | pF   |                                   |

| SDIO                                      |             |     |     |      |                                   |

| As an Input                               |             |     |     |      |                                   |

| Input Logic 1 Voltage                     | 2.2         |     |     | V    |                                   |

| Input Logic 0 Voltage                     |             |     | 1.2 | V    |                                   |

| Input Logic 1 Current                     |             | 1   |     | μΑ   |                                   |

| Input Logic 0 Current                     |             | 1   |     | μΑ   |                                   |

| Input Capacitance                         |             | 2   |     | pF   |                                   |

| As an Output                              |             |     |     |      |                                   |

| Output Logic 1 Voltage                    | DVDD3 - 0.6 |     |     | V    | 1 mA load current                 |

| Output Logic 0 Voltage                    |             |     | 0.4 | V    | 1 mA load current                 |

| SDO                                       |             |     |     |      |                                   |

| Output Logic 1 Voltage                    | DVDD3 - 0.6 |     |     | V    | 1 mA load current                 |

| Output Logic 0 Voltage                    |             |     | 0.4 | V    | 1 mA load current                 |

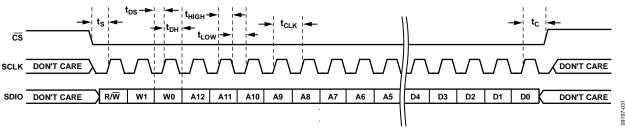

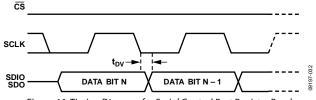

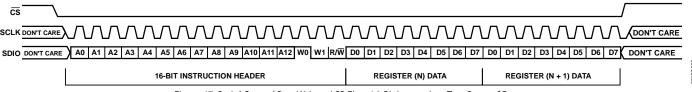

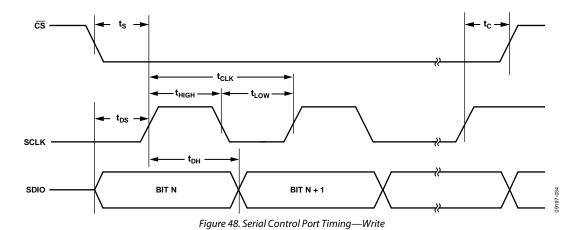

| TIMING                                    |             |     |     |      |                                   |

| SCLK                                      |             |     |     |      |                                   |

| Clock Rate, 1/t <sub>CLK</sub>            |             |     | 40  | MHz  |                                   |

| Pulse Width High, tнын                    | 10          |     |     | ns   |                                   |

| Pulse Width Low, t <sub>LOW</sub>         | 13          |     |     | ns   |                                   |

| SDIO to SCLK Setup, t <sub>DS</sub>       | 3           |     |     | ns   |                                   |

| SCLK to SDIO Hold, t <sub>DH</sub>        | 6           |     |     | ns   |                                   |

| SCLK to Valid SDIO and SDO, $t_{DV}$      |             |     | 10  | ns   |                                   |

| $\overline{CS}$ to SCLK Setup ( $t_{S}$ ) | 10          |     |     | ns   |                                   |

| CS to SCLK Hold (t <sub>c</sub> )         | 0           |     |     | ns   |                                   |

| CS Minimum Pulse Width High               | 6           |     |     | ns   |                                   |

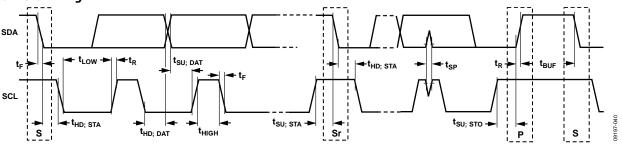

# SERIAL PORT SPECIFICATIONS—I<sup>2</sup>C MODE

Table 16.

| Parameter                                                                      | Min                                  | Тур | Max                | Unit | Test Conditions/Comments                              |

|--------------------------------------------------------------------------------|--------------------------------------|-----|--------------------|------|-------------------------------------------------------|

| SDA, SCL (AS INPUT)                                                            |                                      |     |                    |      |                                                       |

| Input Logic 1 Voltage                                                          | 0.7 ×<br>DVDD3                       |     |                    | V    |                                                       |

| Input Logic 0 Voltage                                                          |                                      |     | $0.3 \times$ DVDD3 | V    |                                                       |

| Input Current                                                                  | -10                                  |     | +10                | μΑ   | For $V_{IN} = 10\%$ to 90% DVDD3                      |

| Hysteresis of Schmitt Trigger Inputs                                           | 0.015 ×<br>DVDD3                     |     |                    |      |                                                       |

| Pulse Width of Spikes That Must Be Suppressed by the Input Filter, tsp         |                                      |     | 50                 | ns   |                                                       |

| SDA (AS OUTPUT)                                                                |                                      |     |                    |      |                                                       |

| Output Logic 0 Voltage                                                         |                                      |     | 0.4                | V    | $I_0 = 3 \text{ mA}$                                  |

| Output Fall Time from $V_{IHmin}$ to $V_{ILmax}$                               | $20 + 0.1  C_b^{ 1}$                 |     | 250                | ns   | $10 \text{ pF} \le C_b \le 400 \text{ pF}^1$          |

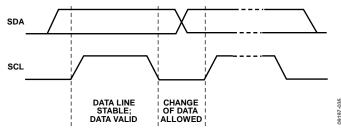

| TIMING                                                                         |                                      |     |                    |      |                                                       |

| SCL Clock Rate                                                                 |                                      |     | 400                | kHz  |                                                       |

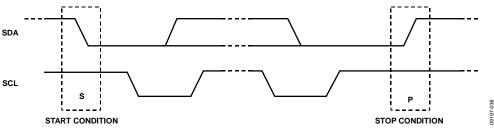

| Bus-Free Time Between a Stop and Start Condition, $t_{\mbox{\scriptsize BUF}}$ | 1.3                                  |     |                    | μs   |                                                       |

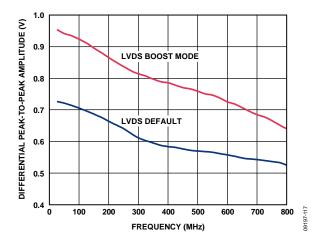

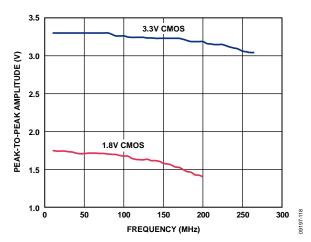

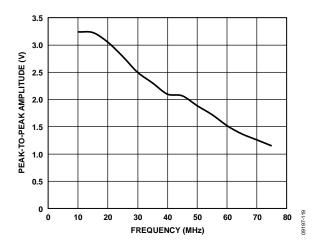

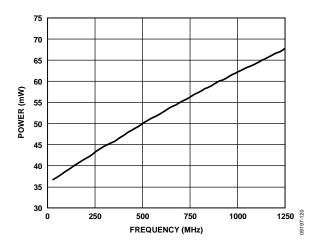

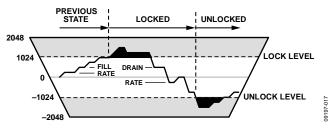

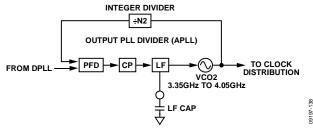

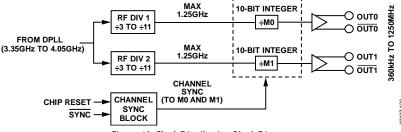

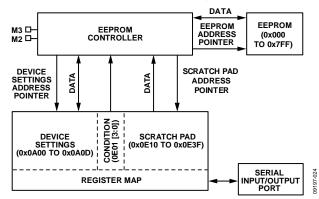

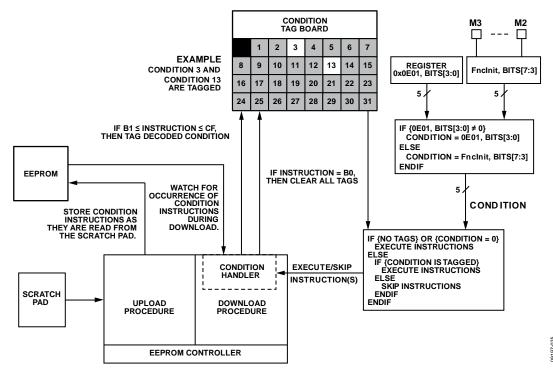

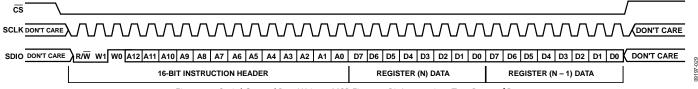

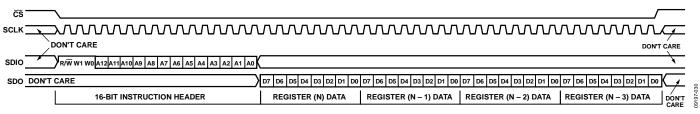

| Repeated Start Condition Setup Time, tsu; STA                                  | 0.6                                  |     |                    | μs   |                                                       |