# Primary-Side-Regulation LED Driver Controller with Active PFC

# **General Description**

The RT7304 is a constant current LED driver with active power factor correction. It supports high power factor across a wide range of line voltages, and it drives the converter in the Quasi-Resonant (QR) mode to achieve higher efficiency. By using Primary Side Regulation (PSR), the RT7304 controls the output current accurately without a shunt regulator and an opto-coupler at the secondary side, reducing the external component count, the cost, and the volume of the driver board.

The RT7304 embeds comprehensive protection functions for robust designs, including LED open-circuit protection, LED short-circuit protection, output diode short-circuit protection, VDD Under-Voltage lockout (UVLO), VDD Over-Voltage Protection (VDD OVP), Over-Temperature Protection (OTP), and cycle-by-cycle current limitation.

# **Marking Information**

0H=DNN

0H= : Product Code DNN : Date Code

# Features

- Tight LED Current Regulation

- No Opto-Coupler and TL431 Required

- Power Factor Correction (PFC)

- Quasi-Resonant

- Maximum/Minimum Switching Frequency Clamping

- Maximum/Minimum On-Time Limitation

- Wide VDD Voltage Range (up to 25V)

- Multiple Protection Features

- LED Open-Circuit Protection

- LED Short-Circuit Protection

- Output Diode Short-Circuit Protection

- VDD Under-Voltage Lockout

- VDD Over-Voltage Protection

- Over-Temperature Protection

- Cycle-by-Cycle Current Limit

- RoHS Compliant and Halogen Free

# Applications

AC/DC LED Lighting driver

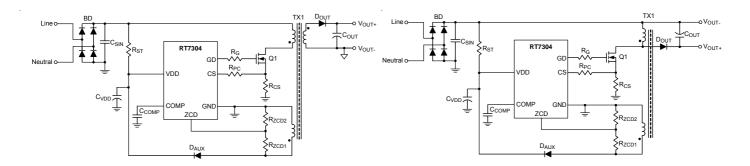

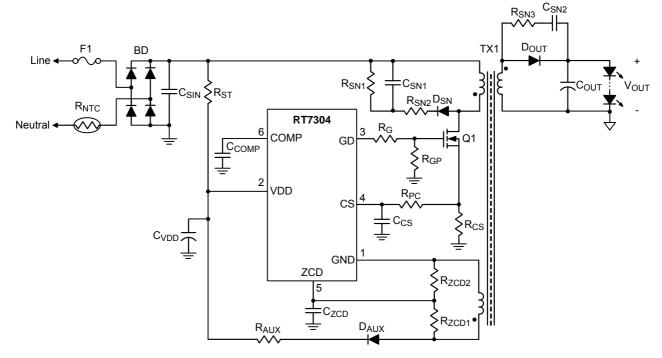

# **Simplified Application Circuit**

Flyback Converter

### **Buck-Boost Converter**

# **Ordering Information**

RT7304

Package Type E : SOT-23-6

-Lead Plating System

G : Green (Halogen Free and Pb Free)

Note :

Richtek products are :

- RoHS compliant and compatible with the current requirements of IPC/JEDEC J-STD-020.

- Suitable for use in SnPb or Pb-free soldering processes.

# **Functional Pin Description**

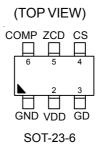

# **Pin Configurations**

| Pin No. | Pin Name | Pin Function                                                                                                                                                                  |

|---------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1       | GND      | Ground of the Controller.                                                                                                                                                     |

| 2       | VDD      | Supply Voltage (V <sub>DD</sub> ) Input. The controller will be enabled when V <sub>DD</sub> exceeds $V_{TH_ON}$ and disabled when $V_{DD}$ is lower than $V_{TH_OFF}$ .      |

| 3       | GD       | Gate Driver Output for External Power MOSFET.                                                                                                                                 |

| 4       | CS       | Current Sense Input. Connect this pin to the current sense resistor.                                                                                                          |

| 5       | ZCD      | Zero Current Detection Input. This pin is used to sense the voltage at auxiliary winding of the transformer for detecting demagnetization time of the magnetizing inductance. |

| 6       | COMP     | Compensation Node. Output of the internal trans-conductance amplifier.                                                                                                        |

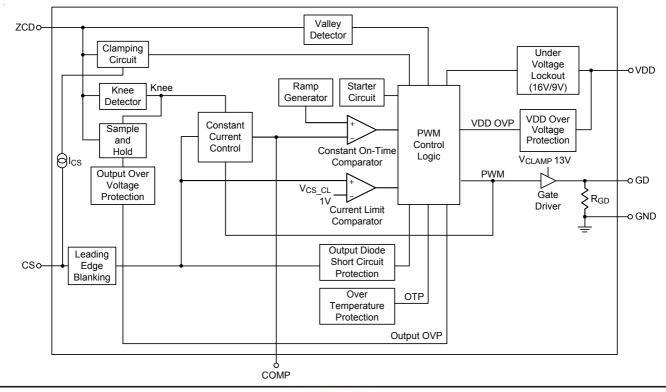

# **Function Block Diagram**

# RICHTEK

# Operation

### **Critical-Conduction Mode (CRM) with Constant On-Time Control.**

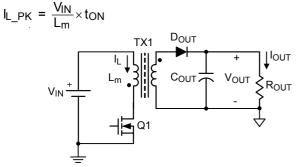

Figure 1 shows a typical flyback converter with input voltage (V<sub>IN</sub>). When main switch Q1 is turned on with a fixed on-time ( $t_{ON}$ ), the peak current ( $I_{L PK}$ ) of the magnetic inductor (L<sub>m</sub>) can be calculated by the following equation :

Figure 1. Typical Flyback Converter

If the input voltage is the output voltage of the full-bridge rectifier with sinusoidal input voltage ( $V_{IN}$  PK x sin( $\theta$ )), the inductor peak current (IL PK) can be expressed as the following equation :

$$I_{L_{PK}} = \frac{V_{IN_{PK}} \times |sin(\theta)| \times t_{ON}}{L_{m}}$$

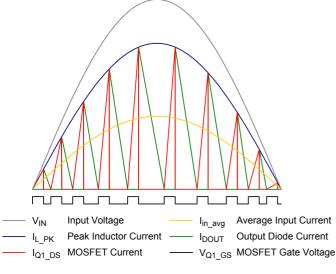

When the converter operates in CRM with constant ontime control, the envelope of the peak inductor current will follow the input voltage waveform with in-phase. Thus, high power factor can be achieved, as shown in Figure 2.

Figure 2. Inductor Current of CRM with Constant **On-Time Control**

### **Primary-Side Constant-Current Regulation**

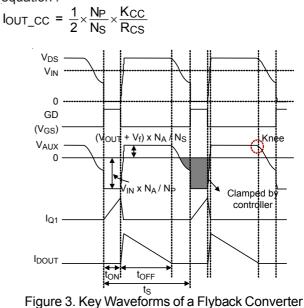

The RT7304 needs no shunt regulator and opto-coupler at the secondary side to achieve the output current regulation. Figure 3 shows several key waveforms of a conventional flyback converter in Quasi-Resonant (QR) mode, in which V<sub>AUX</sub> is the voltage on the auxiliary winding of the transformer, toN is the conducting time of Q1, tOFF is the conducting time of  $D_{OUT}$ ,  $t_S$  is a single switching period, N<sub>P</sub> is the turns number of primary winding and N<sub>S</sub> is the turns number of secondary winding. When the secondary side current IDOUT drops to zero, a knee point on V<sub>AUX</sub> can be detected and t<sub>OFF</sub> can be determined. The average output current (IOUT (t)) can be derived by :

$$I_{OUT} (t) = \frac{1}{2} \times \frac{t_{OFF} (t)}{t_{S} (t)} \times I_{DOUT\_PK} (t)$$

$$= \frac{1}{2} \times \frac{t_{OFF} (t)}{t_{S} (t)} \times \frac{N_{P}}{N_{S}} \times \frac{V_{CS\_PK} (t)}{R_{CS}}$$

In every switching cycle, the RT7304 detects the t<sub>OFF</sub> (t),  $V_{CS PK}(t)$  and  $t_{S}(t)$  for the constant-current regulation loop. For regulating the DC current level of the average output current (I<sub>OUT</sub> (t)) at a programmed level (I<sub>OUT CC</sub>), the RT7304 regulates the t<sub>ON</sub> to make the following equation true :

Average value (K<sub>CC</sub>)

of

$$\left[V_{CS\_PK}(t) \times \frac{t_{OFF}(t)}{t_{S}(t)}\right] = 0.25V (typ.)$$

Therefore, the I<sub>OUT CC</sub> is calculated by the following equation :

### **Voltage Clamping Circuit**

The RT7304 provides a voltage clamping circuit at ZCD pin since the voltage on the auxiliary winding is negative when the main switch is turned on. The lowest voltage on ZCD pin is clamped near zero to prevent the IC from being damaged by the negative voltage. Meanwhile, the sourcing ZCD current (I<sub>ZCD SH</sub>), flowing through the upper resistor (R<sub>ZCD1</sub>), is sampled and held to be a line-voltage-related signal for propagation delay compensation. The RT7304 embeds the programmable propagation delay compensation through CS pin. A sourcing current I<sub>CS</sub> (equal to  $I_{ZCD\_SH} \times K_{PC}$ ) applies a voltage offset ( $I_{CS} \times K_{PC}$ ) R<sub>PC</sub>) which is proportional to line voltage on CS to compensate the propagation delay effect. Thus, the output current can be equal at high and low line voltage.

#### **Quasi-Resonant Operation**

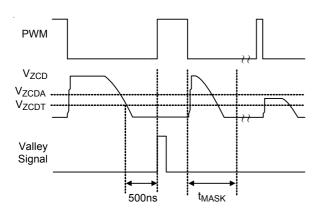

For improving converter's efficiency, the RT7304 detects valleys of the Drain-to-Source voltage (V<sub>DS</sub>) of main switch and turns on it near the selected valley. For the valley detections, a pulse of the "valley signal" is generated after a 500ns(typ.) delay time which starts at which the voltage (V<sub>ZCD</sub>) on ZCD pin goes down and reaches the voltage threshold (V<sub>ZCDT</sub>, 0.4V typ.). During the rising of the  $V_{ZCD}$ , the  $V_{ZCD}$  must reach the voltage threshold (V<sub>ZCDA</sub>, 0.5V typ.). Otherwise, no pulse of the "valley signal" is generated. Moreover, if the timing when the falling V<sub>ZCD</sub> reaches V<sub>ZCDT</sub> is not later than a mask time (t<sub>MASK</sub>, 2µs typ.) then the valley signal will be masked and regards as no valley, as shown in Figure 4.

Figure 4. Valley Signal Generating Method

# RICHTEK

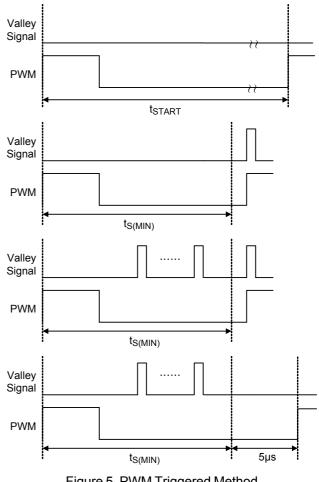

Figure 5 illustrates how valley signal triggers PWM. If no valley signal is detected for a long time, the next PWM is triggered by a starter circuit at the end of the interval (t<sub>START</sub>, 130µs typ.) which starts at the rising edge of the previous PWM signal. A blanking time ( $t_{S(MIN)}$ , 8.5µs typ.), which starts at the rising edge of the previous PWM signal, limits minimum switching period. When the t<sub>S(MIN)</sub> interval is on-going, all of valley signals are not allowed to trigger the next PWM signal. After the end of the  $t_{S(MIN)}$  interval, the coming valley will trigger the next PWM signal. If one or more valley signals are detected during the  $t_{S(MIN)}$ interval and no valley is detected after the end of the  $t_{S(MIN)}$ interval, the next PWM signal will be triggered automatically at the end of the  $t_{S(MIN)}$  + 5µs (typ.).

Figure 5. PWM Triggered Method

# RICHTEK

### Protections

### **LED Open-Circuit Protection**

In an event of output open circuit, the converter will be shut down to prevent being damaged, and it will be autorestarted when the output is recovered. Once the LED is open, the output voltage and  $V_{ZCD}$  will rise. When the sample-and-hold ZCD voltage ( $V_{ZCD_SH}$ ) exceeds its OV threshold ( $V_{ZCD_OVP}$ , 3.1V typ.), output OVP will be activated and the PWM output (GD pin) will be forced low to turn off the main switch. If the output is still open-circuit when the converter restarts, the converter will be shut down again.

### **LED Short-Circuit Protection**

LED short-circuit protection can be achieved by VDD UVLO and cycle-by-cycle current limitation. Once LED short-circuit failure occurs,  $V_{DD}$  drops related to the output voltage. When the  $V_{DD}$  is lower than falling UVLO threshold ( $V_{TH_OFF}$ , 9V typ.), the converter will be shut down and it will be auto-restarted when the output is recovered.

### **Output Diode Short-Circuit Protection**

When the output diode is damaged as short-circuit, the transformer will be led to magnetic saturation and the main switch will suffer from a high current stress. To avoid the above situation, an output diode short-circuit protection is built-in. When CS voltage  $V_{CS}$  exceeds the threshold ( $V_{CS\_SD}$  1.5 typ.) of the output diode short-circuit protection, the RT7304 will shut down the PWM output (GD pin) in few cycles to prevent the converter from damage. It will be auto-restarted when the failure condition is recovered.

### VDD Under-Voltage Lockout (UVLO) and Over-Voltage Protection(VDD OVP)

The RT7304 will be enabled when VDD voltage ( $V_{DD}$ ) exceeds rising UVLO threshold ( $V_{TH_ON}$ , 16V typ.) and disabled when  $V_{DD}$  is lower than falling UVLO threshold ( $V_{TH_OFF}$ , 9V typ.).

When  $V_{DD}$  exceeds its over-voltage threshold ( $V_{OVP}$ , 27V typ.), the PWM output of the RT7304 is shut down. It will be auto-restarted when the  $V_{DD}$  is recovered to a normal level.

### **Over-Temperature Protection (OTP)**

The RT7304 provides an internal OTP function to protect the controller itself from suffering thermal stress and permanent damage. It's not suggested to use the function as precise control of over temperature. Once the junction temperature is higher than the OTP threshold ( $T_{SD}$ , 150°C typ.), the controller will shut down until the temperature cools down by 30°C (typ.). Meanwhile, if V<sub>DD</sub> reaches falling UVLO threshold voltage (V<sub>TH\_OFF</sub>), the controller will hiccup till the over-temperature condition is removed.

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **RT7304**

# Absolute Maximum Ratings (Note 1)

| • VDD to GND                                   | 0.3V to 30V      |

|------------------------------------------------|------------------|

| • GD to GND                                    | 0.3V to 20V      |

| CS, ZCD, COMP to GND                           | 0.3V to 6V       |

| • Power Dissipation, $P_D @ T_A = 25^{\circ}C$ |                  |

| SOT-23-6                                       | - 0.42W          |

| Package Thermal Resistance (Note 2)            |                  |

| SOT-23-6, θ <sub>JA</sub>                      | - 235.6°C/W      |

| Junction Temperature                           | - 150°C          |

| Lead Temperature (Soldering, 10 sec.)          | - 260°C          |

| Storage Temperature Range                      | - –65°C to 150°C |

| ESD Susceptibility (Note 3)                    |                  |

| HBM (Human Body Model)                         | - 2kV            |

| MM (Machine Model)                             | - 200V           |

# Recommended Operating Conditions (Note 4)

| ٠ | Supply Input Voltage, VDD       | 12V to 25V     |

|---|---------------------------------|----------------|

| • | COMP Voltage, V <sub>COMP</sub> | 0.7V to 4.3V   |

| • | Junction Temperature Range      | –40°C to 125°C |

### **Electrical Characteristics**

(V<sub>DD</sub> = 15V,  $T_A$  = 25°C, unless otherwise specification)

| Parameter                                                                                                                | Symbol              | Test Conditions               | Min  | Тур   | Max  | Unit |  |  |  |

|--------------------------------------------------------------------------------------------------------------------------|---------------------|-------------------------------|------|-------|------|------|--|--|--|

| VDD Supply Current and Protections Section                                                                               |                     |                               |      |       |      |      |  |  |  |

| VDD OVP Threshold Voltage                                                                                                | Vovp                |                               | 25.5 | 27    | 28.5 | V    |  |  |  |

| VDD OVP De-bounce Time                                                                                                   |                     | (Note 5)                      |      | 10    |      | μs   |  |  |  |

| Rising UVLO Threshold Voltage                                                                                            | Vth_on              |                               | 15   | 16    | 17   | V    |  |  |  |

| Falling UVLO Threshold Voltage                                                                                           | V <sub>TH_OFF</sub> |                               | 8    | 9     | 10   | V    |  |  |  |

| Operating Supply Current                                                                                                 | I <sub>DD_OP</sub>  | I <sub>ZCD</sub> = 0, GD Open |      |       | 3.5  | mA   |  |  |  |

| Start-up Current                                                                                                         |                     | $V_{DD} = V_{TH_ON} - 1V$     |      |       | 30   | μA   |  |  |  |

| ZCD Section                                                                                                              |                     |                               |      |       |      |      |  |  |  |

| Lower Clamp Voltage                                                                                                      |                     | $I_{ZCD}$ = 0 to -2.5mA       |      | 0     | 0.3  | V    |  |  |  |

| ZCD OVP Threshold Voltage VZCE                                                                                           |                     | At the Knee Point (Note 5)    | 2.8  | 3.1   | 3.4  | V    |  |  |  |

| Constant Current Control Sect                                                                                            | ion                 |                               |      |       |      |      |  |  |  |

| Regulated factor for<br>Constant-Current Control $K_{CC}$ $K_{CC}$ = Average Value of $(V_{CS_PK} \times t_{OFF} / t_S)$ |                     | 0.245                         | 0.25 | 0.255 | V    |      |  |  |  |

| Maximum COMP Voltage                                                                                                     |                     | I <sub>COMP</sub> < 30μA      | 4.5  |       |      | V    |  |  |  |

| Maximum COMP Sourcing<br>Current I <sub>COMP(MAX)</sub> V <sub>COMP</sub> < 3.5V                                         |                     |                               | 62.5 |       | μA   |      |  |  |  |

# RICHTEK

| R | Τ7 | 73 | 04 |

|---|----|----|----|

|   |    | -  | -  |

| Parameter                                                           | Symbol               | Test Conditions                                                                                 | Min  | Тур  | Max  | Unit  |

|---------------------------------------------------------------------|----------------------|-------------------------------------------------------------------------------------------------|------|------|------|-------|

| Timing Control Section                                              |                      | 1                                                                                               |      |      | I    |       |

| Voltage Ramp Slope of the<br>Ramp Generator Output                  | S <sub>ramp</sub>    |                                                                                                 | 238  | 280  | 322  | mV/μs |

| Minimum On-Time                                                     | t <sub>ON(MIN)</sub> | I <sub>ZCD</sub> = -150μA                                                                       | 2.2  | 2.7  | 3.2  | μS    |

| Maximum On-Time                                                     | t <sub>ON(MAX)</sub> |                                                                                                 | 29   | 47   | 65   | μS    |

| Minimum Switching Period                                            | ts(MIN)              |                                                                                                 | 7    | 8.5  | 10   | μS    |

| Duration of Starter                                                 | t <sub>START</sub>   | At No Valley Detected                                                                           | 75   | 130  | 300  | μS    |

| Current Sense Section                                               | •                    |                                                                                                 |      |      |      |       |

| Blanking Time                                                       | t <sub>LEB</sub>     | LEB + Propagation Delay (Note 5)                                                                | 240  | 400  | 570  | ns    |

| Output Diode Short-Circuit<br>Protection Voltage Threshold<br>at CS | Vcs_sd               | Shutdown when V <sub>CS</sub> > V <sub>CS_SD</sub> in 7 cycles.                                 |      | 1.5  |      | V     |

| CS Voltage Threshold for<br>Peak Current Limitation                 | V <sub>CS_CL</sub>   |                                                                                                 | 0.93 | 1.03 | 1.13 | V     |

| Propagation Delay<br>Compensation factor                            | K <sub>PC</sub>      | Sourcing I <sub>CS</sub> = I <sub>ZCD</sub> x K <sub>PC</sub> , I <sub>ZCD</sub> = $-150 \mu A$ |      | 0.02 |      | A/A   |

| Gate Driver Section                                                 | •                    |                                                                                                 |      |      |      |       |

| GD Voltage Rising Time                                              | t <sub>R</sub>       | C <sub>L</sub> = 1nF                                                                            |      | 60   | 80   | ns    |

| GD Voltage Falling Time                                             | t⊢                   | C <sub>L</sub> = 1nF                                                                            |      | 40   | 70   | ns    |

| GD Output Clamping Voltage                                          | V <sub>CLAMP</sub>   | C <sub>L</sub> = 1nF                                                                            |      | 13   |      | V     |

| Internal GD Pull Low Resistor                                       | R <sub>GD</sub>      |                                                                                                 |      | 40   |      | kΩ    |

| Over-Temperature Protection                                         | n Section            |                                                                                                 |      |      |      |       |

| Over-Temperature Threshold                                          | T <sub>SD</sub>      | (Note 5)                                                                                        |      | 150  |      | °C    |

| Over-Temperature Threshold<br>Hysteresis                            | T <sub>SD_HYS</sub>  | (Note 5)                                                                                        |      | 30   |      | °C    |

**Note 1.** Stresses beyond those listed "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions may affect device reliability.

Note 2.  $\theta_{JA}$  is measured at  $T_A = 25^{\circ}C$  on a low effective thermal conductivity two-layer test board per JEDEC 51-3.

Note 3. Devices are ESD sensitive. Handling precaution is recommended.

Note 4. The device is not guaranteed to function outside its operating conditions.

Note 5. Guaranteed by Design.

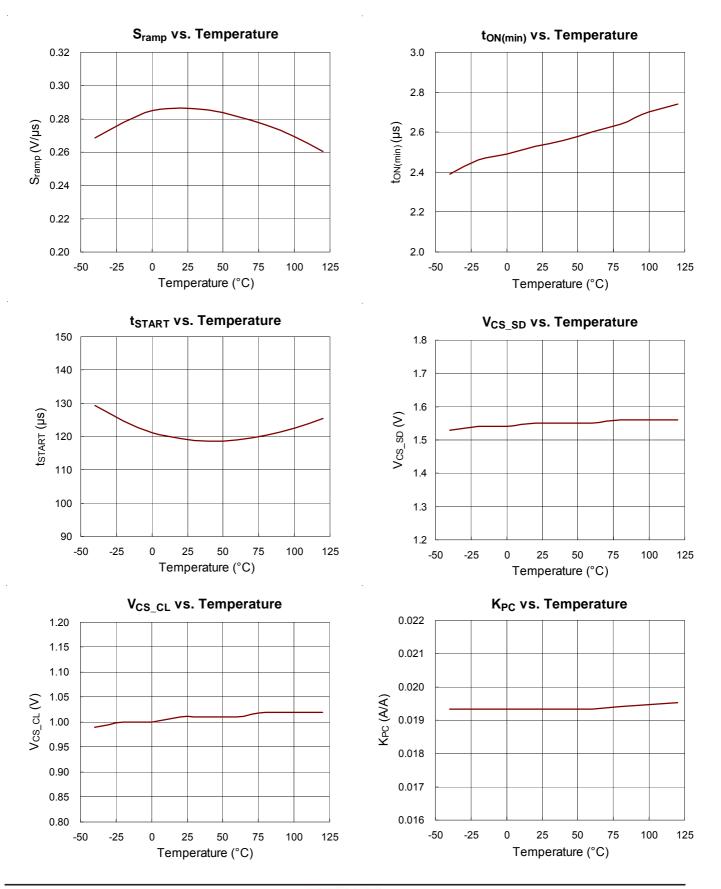

# **Typical Application Circuit**

### **Flyback Application Circuit**

### **Buck-Boost Application Circuit**

Table 1. Suggested Component Values

| CVE | <b>ο (</b> μ <b>F)</b> | <b>Ссомр (</b> µ <b>F)</b> | C <sub>ZCD</sub> (pF) | C <sub>CS</sub> (pF) | <b>R<sub>ST</sub> (Μ</b> Ω) | $R_{GP}(k\Omega)$ | <b>RG</b> (Ω) | <b>R</b> <sub>AUX</sub> (Ω) |

|-----|------------------------|----------------------------|-----------------------|----------------------|-----------------------------|-------------------|---------------|-----------------------------|

|     | 22                     | 1                          | 22                    | 4.7<br>(Optional)    | 1                           | 10                | 47            | 10                          |

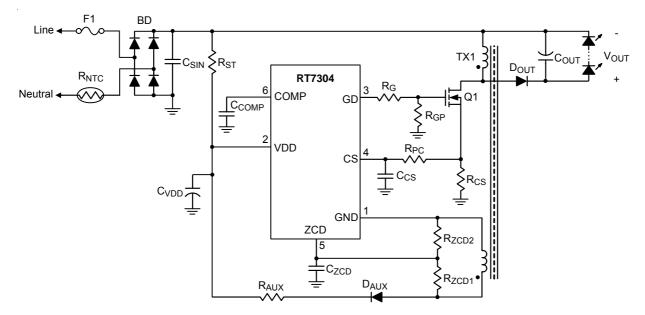

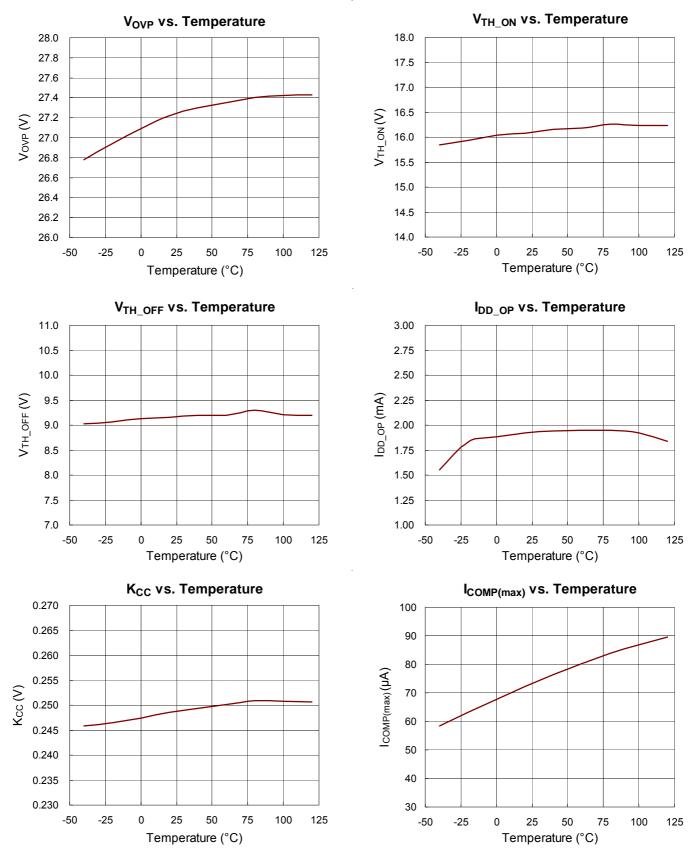

# **Typical Operating Characteristics**

Copyright ©2013 Richtek Technology Corporation. All rights reserved. RICHTEK is a registered trademark of Richtek Technology Corporation.

# **RT7304**

RICHTEK

Copyright ©2013 Richtek Technology Corporation. All rights reserved. **RICHTEK** is a registered trademark of Richtek Technology Corporation.

# **Application Information**

### **Output Current Setting**

Considering the conversion efficiency, the programmed DC level of the average output current ( $I_{OUT}$  (t)) can be rewritten as :

$$l_{OUT\_CC} = \frac{1}{2} \times \frac{N_P}{N_S} \times \frac{K_{CC}}{R_{CS}} \times CTR_{TX1}$$

$$CTR_{TX1} = \frac{I_{SEC\_PK}}{I_{PRI\_PK}} \times \frac{N_S}{N_P}$$

in which CTR<sub>TX1</sub> is the current transfer ratio of the transformer TX1,  $I_{SEC_PK}$  is the peak current of secondary side, and  $I_{PRI_PK}$  is the peak current of the primary side. CTR<sub>TX1</sub> can be estimated to be 0.9.

According to the above parameters, current sense resistor  $R_{CS}$  can be determined as the following equation :

$R_{CS} = \frac{1}{2} \times \frac{N_{P}}{N_{S}} \times \frac{K_{CC}}{I_{OUT\_CC}} \times CTR_{TX1}$

### **Propagation Delay Compensation Design**

The  $V_{CS}$  deviation  $(\Delta V_{CS})$  caused by propagation delay effect can be derived as :

$$\Delta V_{\rm CS} = \frac{V_{\rm IN} \times t_{\rm D} \times R_{\rm CS}}{L_{\rm m}}$$

in which  $t_D$  is the delay period which includes the propagation delay of the RT7304 and the turn-off transition of the main MOSFET. The sourcing current from CS pin of the RT7304 ( $I_{CS}$ ) can be expressed as :

$I_{CS} = K_{PC} \times V_{IN} \times \frac{N_A}{N_P} \times \frac{1}{R_{ZCD1}}$

where  $N_{\text{A}}$  is the turns number of auxiliary winding.

R<sub>PC</sub> can be designed by :

$R_{PC} = \frac{\Delta V_{CS}}{I_{CS}} = \frac{t_D \times R_{CS} \times R_{ZCD1}}{L_m \times K_{PC}} \times \frac{N_P}{N_A}$

### **Minimum On-Time Setting**

The RT7304 limits a minimum on-time ( $t_{ON(MIN)}$ ) for each switching cycle. The  $t_{ON(MIN)}$  is a function of the sampleand-hold ZCD current ( $I_{ZCD SH}$ ) as following :

$t_{ON(MIN)} \times I_{ZCD\_SH} = 375p \times sec \times A (typ.)$

I<sub>ZCD\_SH</sub> can be expressed as :

$$I_{ZCD\_SH} = \frac{V_{IN} \times N_A}{R_{ZCD1} \times N_P}$$

Thus, R<sub>ZCD1</sub> can be determined by :

$$R_{ZCD1} = \frac{t_{ON(MIN)} \times V_{IN}}{375p} \times \frac{N_A}{N_P}$$

(typ.)

In addition, the current flowing out of ZCD pin must be lower than 2.5mA (typ.). Thus, the  $R_{ZCD1}$  is also determined by :

$$R_{ZCD1} > \frac{\sqrt{2} \times V_{AC(MAX)}}{2.5m} \times \frac{N_A}{N_P}$$

where the  $V_{AC(MAX)}$  is maximum input AC voltage.

### **Output Over-Voltage Protection Setting**

Output OVP is achieved by sensing the knee voltage on the auxiliary winging. It is recommended that output OV level ( $V_{OUT_OVP}$ ) is set at 120% of nominal output voltage ( $V_{OUT}$ ). Thus,  $R_{ZCD1}$  and  $R_{ZCD2}$  can be determined by the equation as :

$$V_{OUT} \times \frac{N_A}{N_S} \times \frac{R_{ZCD2}}{R_{ZCD1} + R_{ZCD2}} \times 120\% = 3.1V \text{ (typ.)}$$

#### Table 2. Suggested Component Values Range

| Component         | Range of Typical Value        |  |

|-------------------|-------------------------------|--|

| C <sub>VDD</sub>  | 10μF to 33μF                  |  |

| C <sub>COMP</sub> | 1μF to 4.7μF                  |  |

| C <sub>ZCD</sub>  | 10pF to 22pF                  |  |

| C <sub>CS</sub>   | NC to 22pF                    |  |

| R <sub>ST</sub>   | $0.68 M\Omega$ to $2 M\Omega$ |  |

| R <sub>GP</sub>   | 10k $\Omega$ to 22k $\Omega$  |  |

| R <sub>G</sub>    | 10 $\Omega$ to 47 $\Omega$    |  |

| R <sub>AUX</sub>  | 10 $\Omega$ to 100 $\Omega$   |  |

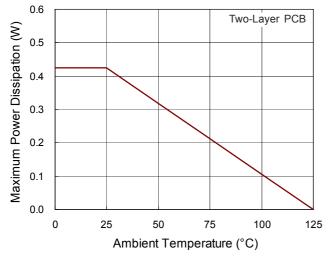

### **Thermal Considerations**

For continuous operation, do not exceed absolute maximum junction temperature. The maximum power dissipation depends on the thermal resistance of the IC package, PCB layout, rate of surrounding airflow, and difference between junction and ambient temperature. The maximum power dissipation can be calculated by the following formula :

### $\mathsf{P}_{\mathsf{D}(\mathsf{MAX})} = (\mathsf{T}_{\mathsf{J}(\mathsf{MAX})} - \mathsf{T}_{\mathsf{A}}) / \theta_{\mathsf{J}\mathsf{A}}$

where  $T_{J(MAX)}$  is the maximum junction temperature,  $T_A$  is the ambient temperature, and  $\theta_{JA}$  is the junction to ambient thermal resistance.

For recommended operating condition specifications, the maximum junction temperature is 125°C. The junction to ambient thermal resistance,  $\theta_{JA}$ , is layout dependent. For SOT-23-6 package, the thermal resistance,  $\theta_{JA}$ , is 235.6°C/W on a standard JEDEC 51-3 two-layer thermal test board. The maximum power dissipation at  $T_A = 25^{\circ}C$  can be calculated by the following formula :

$P_{D(MAX)}$  = (125°C – 25°C) / (235.6°C/W) = 0.42W for SOT-23-6 package

The maximum power dissipation depends on the operating ambient temperature for fixed  $T_{J(MAX)}$  and thermal resistance,  $\theta_{JA}$ . The derating curve in Figure 6 allows the designer to see the effect of rising ambient temperature on the maximum power dissipation.

Figure 6. Derating Curve of Maximum Power Dissipation

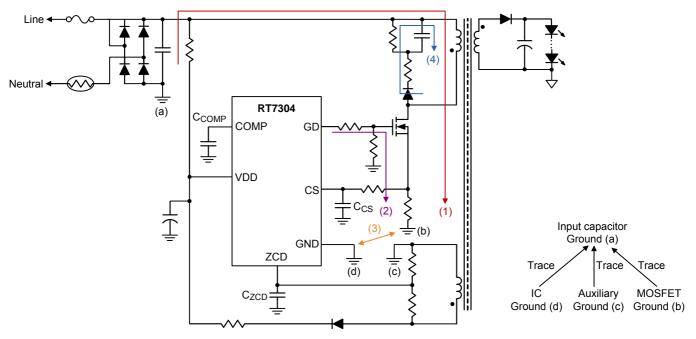

#### Layout Considerations

A proper PCB layout can abate unknown noise interference and EMI issue in the switching power supply. Please refer to the guidelines when designing a PCB layout for switching power supply.

- ➤ The current path(1) from input capacitor, transformer, MOSFET, R<sub>CS</sub> return to input capacitor is a high frequency current loop. The path(2) from GD pin, MOSFET, R<sub>CS</sub> return to input capacitor is also a high frequency current loop. They must be as short as possible to decrease noise coupling and kept a space to other low voltage traces, such as IC control circuit paths, especially. Besides, the path(3) between MOSFET ground(b) and IC ground(d) is recommended to be as short as possible, too.

- The path(4) from RCD snubber circuit to MOSFET is a high switching loop. Keep it as small as possible.

- It is good for reducing noise, output ripple and EMI issue to separate ground traces of input capacitor(a), MOSFET(b), auxiliary winding(c) and IC control circuit(d). Finally, connect them together on input capacitor ground(a). The areas of these ground traces should be kept large.

- Placing bypass capacitor for abating noise on IC is highly recommended. The capacitors C<sub>COMP</sub>,C<sub>ZCD</sub> and C<sub>CS</sub> should be placed as close to controller as possible.

- To minimize parasitic trace inductance and EMI, minimize the area of the loop connecting the secondary winding, the output diode, and the output filter capacitor. In addition, apply sufficient copper area at the anode and cathode terminal of the diode for heat-sinking. It is recommended to apply a larger area at the quiet cathode terminal. A large anode area will induce high-frequency radiated EMI.

Figure 7. PCB Layout Guide

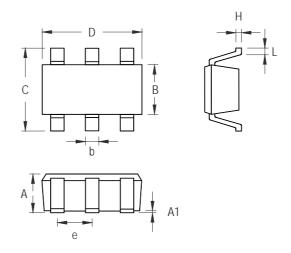

# **Outline Dimension**

| Symbol | Dimensions I | n Millimeters | <b>Dimensions In Inches</b> |       |  |

|--------|--------------|---------------|-----------------------------|-------|--|

| Symbol | Min          | Max           | Min                         | Max   |  |

| А      | 0.889        | 1.295         | 0.031                       | 0.051 |  |

| A1     | 0.000        | 0.152         | 0.000                       | 0.006 |  |

| В      | 1.397        | 1.803         | 0.055                       | 0.071 |  |

| b      | 0.250        | 0.560         | 0.010                       | 0.022 |  |

| С      | 2.591        | 2.997         | 0.102                       | 0.118 |  |

| D      | 2.692        | 3.099         | 0.106                       | 0.122 |  |

| е      | 0.838        | 1.041         | 0.033                       | 0.041 |  |

| Н      | 0.080        | 0.254         | 0.003                       | 0.010 |  |

| L      | 0.300        | 0.610         | 0.012                       | 0.024 |  |

SOT-23-6 Surface Mount Package

### **Richtek Technology Corporation**

14F, No. 8, Tai Yuen 1<sup>st</sup> Street, Chupei City Hsinchu, Taiwan, R.O.C. Tel: (8863)5526789

Richtek products are sold by description only. Richtek reserves the right to change the circuitry and/or specifications without notice at any time. Customers should obtain the latest relevant information and data sheets before placing orders and should verify that such information is current and complete. Richtek cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Richtek product. Information furnished by Richtek is believed to be accurate and reliable. However, no responsibility is assumed by Richtek or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Richtek or its subsidiaries.