**DRV8308** SLVSCF7-FEBRUARY 2014

# **DRV8308 Brushless DC Motor Controller**

Technical

Documents

Sample &

Buy

#### 1 Features

- Three-phase Brushless DC Motor Controller

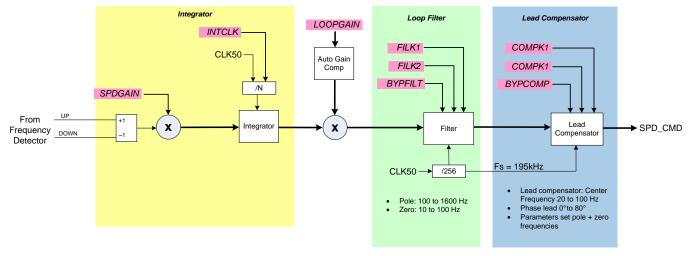

- Fully Digital Speed Loop With Programmable Gain and Loop Filters

- Clock Input or PWM Inputs for Speed Control

- Operating Supply Voltage 8.5 to 32 V

- Drives 10- to 130-mA Gate-Drive Current to 6 N-Channel MOSFETs With Adjustable Slew Rates

- Supports Sensor-based Sinusoidal and Trapezoidal Commutation Control With Tunable Delay

- Flexible Configuration Methods:

- Serial Control

- Internal OTP Memory

- External EEPROM

- 5-V Linear Regulator and Switched Power Output for Hall Sensors

- SPI Control Interface

- Low-power Standby Mode

- Locked Rotor Detection and Restart

- Integrated Overcurrent, Overvoltage, and . Overtemperature Protection

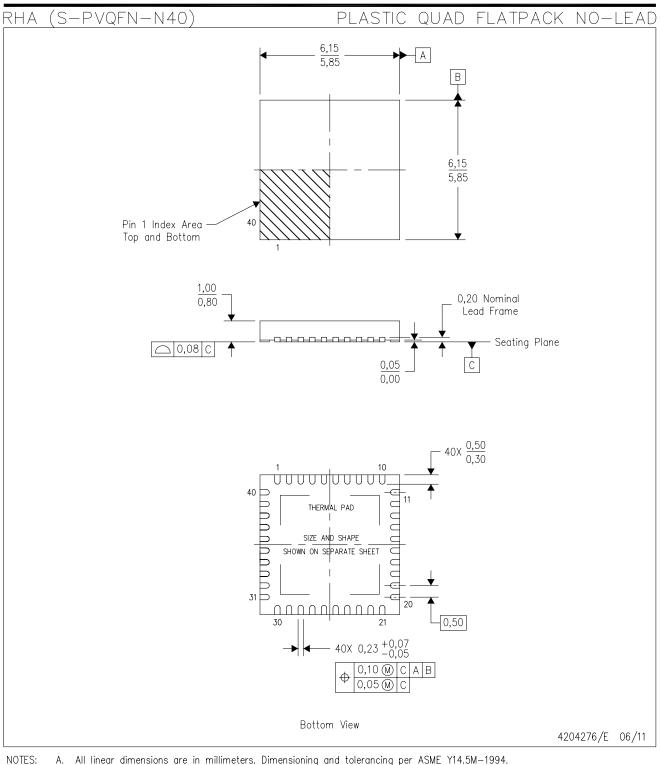

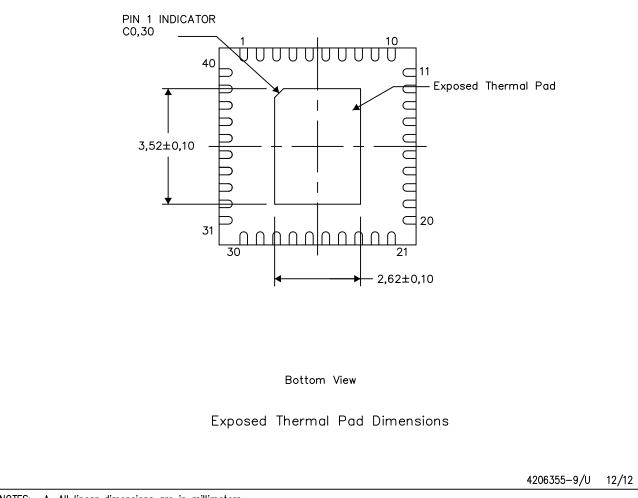

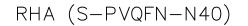

- 6 × 6-mm QFN Package, 0.5-mm Pitch

#### Applications 2

- **Pumps and Industrial Equipment**

- **Currency Counters**

- Printers

# 3 Description

Tools &

Software

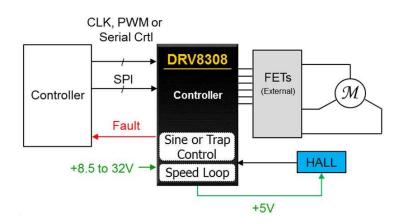

The DRV8308 device is a three half-bridge pre-driver that drives up to 130 mA to six N-type MOSFETs with a single power supply. Aimed at sensored threephase brushless DC motors, this pre-driver includes configurable a digital speed loop, speed controls, and commutation modes to optimize motor performance. When properly tuned, the DRV8308 device can drive motors with less than 0.1% cycle jitter and fast torque compensation.

Support &

Community

20

The integrated digital speed loop allows the motor to maintain speed under variable loads with programmable gain and loop filters. The adjustable slew rates can also lower the switching noise and improve EMC.

The DRV8308 device also supports both the 120° and 180° commutation modes with the ability to adjust the delay to increase power efficiency. For high-performance systems, sinusoidal (180°) commutation mode is used to minimize acoustic noise and torque ripple. Jitter caused by non-ideal Hall placement and matching can be eliminated once constant speed is reached by switching from three Hall sensor phases to just a single Hall sensor.

In addition to advanced programmability features to tune the motor's performance, the SPI interface also provides detailed fault reporting such as locked rotor detection. overcurrent. overtemperature, and overvoltage, as well as charge pump short and failure, to provide robust protection and intelligence to the overall system design.

| Device Information |               |             |  |  |

|--------------------|---------------|-------------|--|--|

| ORDER NUMBER       | PACKAGE (PIN) | BODY SIZE   |  |  |

| DRV8308RHAR        | RHA (40)      | 6-mm × 6-mm |  |  |

| DRV8308RHAT        | RHA (40)      | 6-mm × 6-mm |  |  |

# Simplified Schematic

# **Table of Contents**

| 1 | Feat | tures                              | 1              |

|---|------|------------------------------------|----------------|

| 2 | Арр  | lications                          | 1              |

| 3 | Des  | cription                           | 1              |

| 4 | Sim  | plified Schematic                  | 1              |

| 5 | Rev  | ision History                      | 2              |

| 6 | Terr | minal Configurations and Functions | 3              |

| 7 | Spe  | cifications                        | 6              |

|   | 7.1  | Absolute Maximum Ratings           | 6              |

|   | 7.2  | Handling Ratings                   | 6              |

|   | 7.3  | Recommended Operating Conditions   | <mark>6</mark> |

|   | 7.4  | Thermal Information                | 7              |

|   | 7.5  | Electrical Characteristics         | 8              |

|   | 7.6  | SPI Timing Requirements            | 10             |

| 8 | Deta | ailed Description                  | 11             |

|   | 8.1  | Overview                           | 11             |

|    | 8.2   | Functional Block Diagram          | 12 |

|----|-------|-----------------------------------|----|

|    | 8.3   | Feature Description               | 13 |

|    | 8.4   | Device Functional Modes           | 30 |

|    | 8.5   | Register Map                      | 35 |

| 9  | App   | lications and Implementation      | 39 |

|    | 9.1   | Application Information           | 39 |

| 10 | Pow   | er Supply Recommendations         | 43 |

| 11 | Lay   | out                               | 44 |

|    | 11.1  | Layout Guidelines                 | 44 |

| 12 | Dev   | ice and Documentation Support     | 45 |

|    | 12.1  | Trademarks                        | 45 |

|    | 12.2  | Electrostatic Discharge Caution   | 45 |

|    | 12.3  | Glossary                          | 45 |

| 13 |       | hanical, Packaging, and Orderable |    |

|    | Infor | mation                            | 46 |

|    |       |                                   |    |

# 5 Revision History

| Date          | Revision | Notes           |

|---------------|----------|-----------------|

| February 2014 | *        | Initial Release |

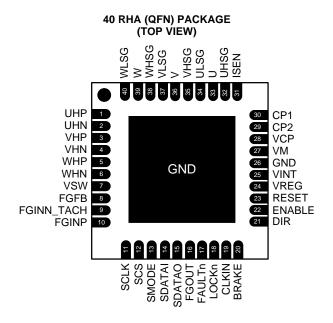

# 6 Terminal Configurations and Functions

#### **Terminal Functions**

| TERMI                                                                                         | NAL      | I/O <sup>(1)</sup> | DECODIDION                                                                                                                                                                                               |                                                                                                  |  |  |  |

|-----------------------------------------------------------------------------------------------|----------|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------|--|--|--|

|                                                                                               |          | 1000               | DESCRIPTION                                                                                                                                                                                              | EXTERNAL COMPONENTS OR CONNECTIONS                                                               |  |  |  |

| POWER AND G                                                                                   | ROUND    |                    |                                                                                                                                                                                                          |                                                                                                  |  |  |  |

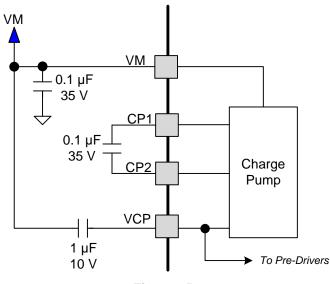

| CP1                                                                                           | 30       | I/O                | Charge pump flying capacitor                                                                                                                                                                             | Connect a 0.1-µF 35-V capacitor between CP1 and CP2                                              |  |  |  |

| CP2                                                                                           | 29       | I/O                |                                                                                                                                                                                                          | Connect a 0.1-pr 35-V capacitor between CFT and CF2                                              |  |  |  |

| GND                                                                                           | 26, PPAD | I                  | Ground reference. Pin 26 and the Power Pad are internally connected.                                                                                                                                     | Connect to board GND                                                                             |  |  |  |

| VCP                                                                                           | 28       | I/O                | Charge pump storage capacitor                                                                                                                                                                            | Connect a 1-µF 35-V ceramic capacitor to VM                                                      |  |  |  |

| VINT                                                                                          | 25       | I/O                | Internal 1.8-V core voltage regulator bypass                                                                                                                                                             | Bypass to GND with a $1-\mu F$ 6.3-V ceramic capacitor                                           |  |  |  |

| VM                                                                                            | 27       | I                  | I Motor supply voltage Connect to motor supply voltage.<br>Bypass to GND with a 0.1-μF ceramic capacitor, plu electrolytic capacitor (47 μF or larger is recommende a voltage rating of 1.5× to 2.5× VM. |                                                                                                  |  |  |  |

| VREG                                                                                          | 24       | I/O                | 5-V regulator output. Active when ENABLE is active.                                                                                                                                                      | Bypass to GND with a 0.1- $\mu$ F 10-V ceramic capacitor. Can provide 5-V power to Hall sensors. |  |  |  |

| VSW                                                                                           | 7        | 0                  | Switched VM power output. When ENABLE is active, VM is applied to this pin.                                                                                                                              | Can be used for powering Hall elements, along with added series resistance.                      |  |  |  |

| CONTROL                                                                                       |          |                    |                                                                                                                                                                                                          |                                                                                                  |  |  |  |

| BRAKE                                                                                         | 20       | I                  | Causes motor to brake. Polarity is programmable. Internal pulldown resistor.                                                                                                                             |                                                                                                  |  |  |  |

| CLKIN                                                                                         | 19       | Ι                  | The clock input, used in Clock<br>Frequency mode and Clock PWM<br>mode. Internal pulldown resistor.                                                                                                      |                                                                                                  |  |  |  |

| DIR 21 I Sets motor rotation direction. Polarity is programmable. Internal pulldown resistor. |          |                    |                                                                                                                                                                                                          |                                                                                                  |  |  |  |

| ENABLE                                                                                        | 22       | I                  | Enables and disables motor. Polarity is programmable. Internal pulldown resistor.                                                                                                                        |                                                                                                  |  |  |  |

(1) I = input, O = output, OD = open-drain output, I/O = input/output

# **Terminal Functions (continued)**

| TERMIN              | IAL        | 110 (1)            |                                                                                                                   |                                                                                                                                                                                     |  |  |  |

|---------------------|------------|--------------------|-------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| NAME                | NUMBER     | I/O <sup>(1)</sup> | DESCRIPTION                                                                                                       | EXTERNAL COMPONENTS OR CONNECTIONS                                                                                                                                                  |  |  |  |

| FAULTn              | 17         | OD                 | Fault indicator – active low when<br>overcurrent, overtemperature, or rotor<br>stall detected. Open-drain output. |                                                                                                                                                                                     |  |  |  |

| FGOUT               | 16         | OD                 | Outputs a TACH signal generated from<br>the FG amplifier or Hall sensors.<br>Open-drain output.                   |                                                                                                                                                                                     |  |  |  |

| LOCKn               | 18         | OD                 | Outputs a signal that indicates the speed loop is locked. Open-drain output.                                      |                                                                                                                                                                                     |  |  |  |

| RESET               | 23         | I                  | Active high to reset all internal logic.<br>Internal pulldown resistor.                                           |                                                                                                                                                                                     |  |  |  |

| SERIAL INTERI       | FACE       |                    |                                                                                                                   | ·                                                                                                                                                                                   |  |  |  |

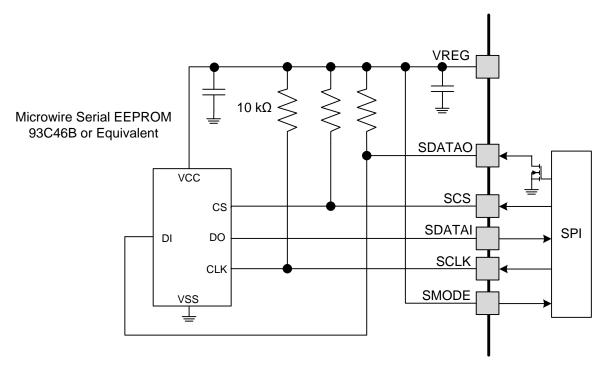

| SCLK <sup>(2)</sup> | 11         | I/OD               | Serial clock                                                                                                      | SPI mode: Serial clock input. Data is clocked on rising edges.<br>Internal pulldown resistor.<br>EEPROM mode: Connect to EEPROM CLK. Open-drain<br>output requires external pullup. |  |  |  |

| SCS <sup>(2)</sup>  | 12         | I/OD               | Serial chip select                                                                                                | SPI mode: Active high enables serial interface operation.<br>Internal pulldown resistor.<br>EEPROM mode: Connect to EEPROM CS. Open-drain output<br>requires external pullup.       |  |  |  |

| SDATAI              | 14         | I                  | Serial data input                                                                                                 | SPI mode: Serial data input. Internal pulldown resistor.<br>EEPROM mode: Serial data input. Connect to EEPROM DO<br>pin.                                                            |  |  |  |

| SDATAO              | 15         | OD                 | Serial data output                                                                                                | SPI mode: Serial data output. Open-drain output.<br>EEPROM mode: Connect to EEPROM DI. Open-drain output<br>requires external pullup.                                               |  |  |  |

| SMODE               | 13         | I                  | Serial mode                                                                                                       | SPI mode: leave open or connect to ground for SPI interface<br>mode.<br>EEPROM mode: Connect to logic high to for EEPROM mode.                                                      |  |  |  |

| POWER STAGE         | E INTERFAC | E                  |                                                                                                                   |                                                                                                                                                                                     |  |  |  |

| ISEN                | 31         | Ι                  | Low-side current sense resistor                                                                                   | Connect to low-side current sense resistor                                                                                                                                          |  |  |  |

| U                   | 33         | Ι                  |                                                                                                                   |                                                                                                                                                                                     |  |  |  |

| V                   | 36         | I                  | Measures motor phase voltages for<br>V <sub>FETOCP</sub>                                                          | Connect to motor windings                                                                                                                                                           |  |  |  |

| W                   | 39         | Ι                  | FEIOCP                                                                                                            |                                                                                                                                                                                     |  |  |  |

| UHSG                | 32         | 0                  |                                                                                                                   |                                                                                                                                                                                     |  |  |  |

| VHSG                | 35         | 0                  | High-side FET gate outputs                                                                                        | Connect to high-side 1/2-H N-channel FET gate                                                                                                                                       |  |  |  |

| WHSG                | 38         | 0                  |                                                                                                                   |                                                                                                                                                                                     |  |  |  |

| ULSG                | 34         | 0                  |                                                                                                                   |                                                                                                                                                                                     |  |  |  |

| VLSG                | 37         | 0                  | Low-side FET gate outputs                                                                                         | Connect to low-side 1/2-H N-channel FET gate                                                                                                                                        |  |  |  |

| WLSG                | 40         | 0                  |                                                                                                                   |                                                                                                                                                                                     |  |  |  |

| HALL AND FG         | INTERFACE  |                    |                                                                                                                   | ·                                                                                                                                                                                   |  |  |  |

| FGFB                | 8          | 0                  | FG amplifier feedback pin                                                                                         | Connect feedback network to FGIN-                                                                                                                                                   |  |  |  |

| FGINN_TACH          | 9          | I <sup>(3)</sup>   | FG amplifier negative input or TACH input                                                                         | Connect to FG trace and filter components. When using a TACH with FGSEL= 3, connect a logic-level TACH signal. If unused, connect FGFB to FG–.                                      |  |  |  |

| FGINP               | 10         | I/O                | FG amplifier positive input                                                                                       | Connect to FG trace and filter components on the PCB (if used).                                                                                                                     |  |  |  |

(2) In SPI mode, these pins are inputs; in EEPROM mode, they are open-drain outputs.

(3) When using FG amp, this pin is an analog input. If in TACH mode, this is a logic-level input.

# **Terminal Functions (continued)**

| TERMI | NAL    | I/O <sup>(1)</sup> | DESCRIPTION                  |                                                                                                                                                          |  |

|-------|--------|--------------------|------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| NAME  | NUMBER | 100                | DESCRIPTION                  | EXTERNAL COMPONENTS OR CONNECTIONS         Connect to Hall sensors. Noise filter capacitors may be desirable, connected between the + and – Hall inputs. |  |

| UHP   | 1      | I                  | Hall sensor U positive input |                                                                                                                                                          |  |

| UHN   | 2      | I                  | Hall sensor U negative input |                                                                                                                                                          |  |

| VHP   | 3      | I                  | Hall sensor V positive input |                                                                                                                                                          |  |

| VHN   | 4      | Т                  | Hall sensor V negative input | desirable, connected between the + and - Hall inputs.                                                                                                    |  |

| WHP   | 5      | Ι                  | Hall sensor W positive input |                                                                                                                                                          |  |

| WHN   | 6      | Ι                  | Hall sensor W negative input |                                                                                                                                                          |  |

#### **Specifications** 7

# 7.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)(2)(3)

|                                                                                                                                                | MIN              | MAX     | UNIT |

|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------|------|

| Power supply voltage range (VM)                                                                                                                | -0.3             | 35      | V    |

| Charge pump and high side gate drivers (VCP, UHSG, VHSG, WHSG)                                                                                 | -0.3             | 50      | V    |

| Output pin, low side gate drivers, charge pump flying cap and switched VM power supply voltage range (U, V, W, ULSG, VLSG, WLSG, CP1, CP2 VSW) | -0.6             | 40      | V    |

| Internal core voltage regulator (VINT)                                                                                                         | -0.3             | 2.0     | V    |

| Linear voltage regulator output (VREG)                                                                                                         | -0.3             | 5.5     | V    |

| Sense current pin (ISEN)                                                                                                                       | -0.3             | 2.0     | V    |

| Digital pin voltage range (SCLK, SCS, SMODE, SDATAI, SDATAO, FGOUT, FAULTn, LOCKn, CLKIN, BRAKE, DIR, ENABLE, RESET)                           | -0.5             | 5.75    | V    |

| Hall sensor input pin voltage (UHP, UHN, VHP, VHN, WHP, WHN, FGFB, FGINN/TACH, FGINP)                                                          | 0                | VREG    | V    |

| Continuous total power dissipation                                                                                                             | See Thermal Info | rmation |      |

| Operating junction temperature range, T <sub>J</sub>                                                                                           | -40              | 150     | °C   |

(1) Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

(2) (3) All voltage values are with respect to network ground terminal.

Power dissipation and thermal limits must be observed

# 7.2 Handling Ratings

over operating free-air temperature range (unless otherwise noted)

| PARAMETER        | DEFINITION                | MIN | MAX | UNIT |

|------------------|---------------------------|-----|-----|------|

| T <sub>STG</sub> | Storage temperature range | -60 | 150 | °C   |

# 7.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                    |                                   |                                                         | MIN | NOM MAX           | UNIT |

|--------------------|-----------------------------------|---------------------------------------------------------|-----|-------------------|------|

| VM                 | Motor power supply vo             | Itage range, ENABLE = 1, motor operating <sup>(1)</sup> | 8.5 | 32                | V    |

| V <sub>MDIS</sub>  | Motor power supply vo             | Itage range, ENABLE = 0, motor not operating            | 4.5 | 35                | v    |

| I <sub>VREG</sub>  | VREG output current <sup>(2</sup> | )                                                       | 0   | 30                | ~ ^  |

| I <sub>VSW</sub>   | VSW output current <sup>(2)</sup> |                                                         | 0   | 30                | mA   |

| f <sub>HALL</sub>  | Hall sensor input frequ           | ency <sup>(3)</sup>                                     | 0   | 30                |      |

| 4                  |                                   | SPDMODE = 00 (Clock frequency mode)                     | 0   | 90                | kHz  |

| † <sub>CLKIN</sub> | Frequency on CLKIN                | SPDMODE = 01 (Clock PWM mode)                           | 16  | 50 <sup>(4)</sup> |      |

Note that at VM < 12 V, gate drive output voltage tracks VM voltage Power dissipation and thermal limits must be observed (1)

(2)

(3) (4)

$f_{\text{HALL}}$  of 50 Hz to 6.7 kHz is best Operational with frequencies above 50 kHz, but resolution is degraded

# 7.4 Thermal Information

|                         | THERMAL METRIC <sup>(1)</sup>                               | DRV8308       |        |

|-------------------------|-------------------------------------------------------------|---------------|--------|

|                         |                                                             | RHA (40 PINS) | UNIT   |

| $\theta_{JA}$           | Junction-to-ambient thermal resistance <sup>(2)</sup>       | 32.0          |        |

| θ <sub>JCtop</sub>      | Junction-to-case (top) thermal resistance <sup>(3)</sup>    | 24.5          |        |

| $\theta_{JB}$           | Junction-to-board thermal resistance <sup>(4)</sup>         | 9.9           | °C 11/ |

| $\Psi_{JT}$             | Junction-to-top characterization parameter <sup>(5)</sup>   | 2.7           | °C/W   |

| $\Psi_{JB}$             | Junction-to-board characterization parameter <sup>(6)</sup> | 10.0          |        |

| $\theta_{\text{JCbot}}$ | Junction-to-case (bottom) thermal resistance <sup>(7)</sup> | 2.7           |        |

For more information about traditional and new thermal metrics, see the IC Package Thermal Metrics application report, SPRA953.

The junction-to-ambient thermal resistance under natural convection is obtained in a simulation on a JEDEC-standard, high-K board, as

specified in JESD51-7, in an environment described in JESD51-2a.

(3) The junction-to-case (top) thermal resistance is obtained by simulating a cold plate test on the package top. No specific JEDEC standard

test exists, but a close description can be found in the ANSI SEMI standard G30-88.

(4) The junction-to-board thermal resistance is obtained by simulating in an environment with a ring cold plate fixture to control the PCB temperature, as described in JESD51-8.

(5) The junction-to-top characterization parameter,  $\psi_{JT}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(6) The junction-to-board characterization parameter,  $\psi_{JB}$ , estimates the junction temperature of a device in a real system and is extracted from the simulation data for obtaining  $\theta_{JA}$ , using a procedure described in JESD51-2a (sections 6 and 7).

(7) The junction-to-case (bottom) thermal resistance is obtained by simulating a cold plate test on the exposed (power) pad. No specific JEDEC standard test exists, but a close description can be found in the ANSI SEMI standard G30-88.

TEXAS INSTRUMENTS

www.ti.com

# 7.5 Electrical Characteristics

over operating free-air temperature range (unless otherwise noted)

|                           | PARAMETER                                    | TEST CONDITIONS                          | MIN  | TYP                                              | MAX     | UNIT            |

|---------------------------|----------------------------------------------|------------------------------------------|------|--------------------------------------------------|---------|-----------------|

| VM SUPF                   | PLY                                          |                                          |      |                                                  |         |                 |

| I <sub>VM</sub>           | VM active current                            | ENABLE = active,<br>VREG and VSW open    |      | 12                                               | 18      | mA              |

| I <sub>STBY</sub>         | VM standby current                           | ENABLE = inactive                        |      |                                                  | 120     | μA              |

| V                         | VM logic reset voltage                       | VM falling                               |      |                                                  | 4.6     | V               |

| V <sub>RESET</sub>        | vivi logic teset voltage                     | VM rising                                | 5.0  |                                                  |         | v               |

| VREG SL                   | JPPLY                                        |                                          |      |                                                  |         |                 |

| V <sub>VREG</sub>         | Output voltage                               | $I_{OUT} = 1$ to 30 mA                   | 4.75 | 5                                                | 5.25    | V               |

| I <sub>VREG</sub>         | Output current                               |                                          |      |                                                  | 30      | mA              |

| VSW SU                    | PPLY                                         |                                          |      |                                                  |         |                 |

| R <sub>DS(ON)</sub>       | VSW switch on-resistance                     | $I_{OUT} = 1$ to 30 mA                   |      | 9                                                | 20      | Ω               |

| I <sub>VSW</sub>          | Output current                               |                                          |      |                                                  | 30      | mA              |

| INTERNA                   | L CLOCK OSCILLATOR                           |                                          |      |                                                  |         |                 |

| f <sub>CLK50</sub>        | Internal CLK50 clock frequency               |                                          |      | 50                                               |         | MHz             |

| LOGIC-L                   | EVEL INPUTS AND OUTPUTS                      |                                          |      |                                                  |         |                 |

| V <sub>IL</sub>           | Low-level input voltage                      |                                          |      |                                                  | 0.8     | V               |

| VIH                       | High-level input voltage                     |                                          | 1.5  |                                                  | 5.5     | V               |

| I <sub>IL</sub>           | Low-level input current                      |                                          | -50  |                                                  | 50      | μA              |

|                           |                                              | V <sub>IN</sub> = 3.3 V, RESET,          |      |                                                  |         | μA              |

|                           | Lligh lovel input surrent                    | DIR, BRAKE, CLKIN,<br>SCS, SCLK, SDATAI, | 20   |                                                  | 100     |                 |

| IIH                       | High-level input current                     | SMODE                                    |      |                                                  |         |                 |

|                           |                                              | V <sub>IN</sub> = 3.3 V, ENABLE          | 6    |                                                  | 9       |                 |

| V <sub>HYS</sub>          | Input hysteresis voltage                     |                                          | 0.1  | 0.3                                              | 0.5     | V               |

|                           |                                              | RESET, DIR, BRAKE,                       |      |                                                  |         | kΩ              |

| R <sub>PD</sub>           | Input pulldown resistance                    | CLKIN, SCS, SCLK,<br>SDATAI, SMODE       | 50   | 100                                              | 150     |                 |

| FD                        |                                              | ENABLE                                   | 350  |                                                  | 550     |                 |

|                           | RAIN OUTPUTS                                 |                                          | 000  |                                                  | 550     |                 |

| V <sub>OL</sub>           | Low-level output voltage                     | I <sub>OUT</sub> = 2.0 mA                |      |                                                  | 0.5     | V               |

| I <sub>OH</sub>           | Output leakage current                       | $V_{OUT} = 3.3 V$                        |      |                                                  | 0.0     | μA              |

| -                         |                                              | V001 - 0.0 V                             |      |                                                  |         | μΛ              |

| V <sub>IO</sub>           | FG amplifier input offset voltage            |                                          | -7   |                                                  | 7       | mV              |

| I <sub>IB</sub>           | FG amplifier input bias current              |                                          |      |                                                  | 1       | μΑ              |

| V <sub>ICM</sub>          | FG amplifier input common mode voltage range |                                          | 1.5  |                                                  | 3.5     | μ <u>μ</u><br>V |

| A <sub>V</sub>            | FG amplifier open loop voltage gain          |                                          | 45   |                                                  | 0.0     | dB              |

| GBW                       | FG amplifier gain bandwidth product          |                                          | 500  |                                                  |         | kHz             |

| V <sub>REF+</sub>         | FG comparator positive reference voltage     |                                          | -20% | V <sub>VREG</sub> / 2                            | 20%     | V               |

| V <sub>IT+</sub>          | FG comparator positive threshold             |                                          | -20% | V <sub>VREG</sub> / 2<br>V <sub>VREG</sub> / 1.8 | 20%     | V               |

| VIT+<br>VIT-              | FG comparator negative threshold             |                                          | -20% | V <sub>VREG</sub> / 1.0<br>V <sub>VREG</sub> / 2 | 20%     | V               |

|                           | NSOR INPUTS                                  |                                          | 2070 | VREG / 2                                         | 2070    | v               |

| V <sub>HYS</sub>          | Hall amplifier hysteresis voltage            |                                          | 15   | 20                                               | 25      | mV              |

| ⊻hys<br>∆V <sub>HYS</sub> | Hall amplifier hysteresis voltage            | Between U, V, W                          | -5   | 20                                               | 25<br>5 | mV              |

|                           | Hall amplifier input differential            |                                          |      |                                                  | 5       | mV              |

| V <sub>ID</sub>           | Hall amplifier input common mode voltage     |                                          |      |                                                  |         | V               |

| V <sub>CM</sub>           | range                                        |                                          | 1.5  |                                                  | 3.5     | v               |

| I <sub>IN</sub>           | Input leakage current                        | H_x+ = H_x-                              | -10  |                                                  | 10      | μA              |

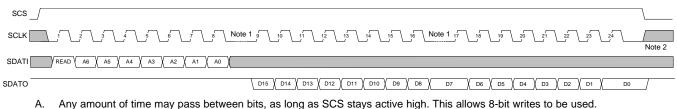

| t <sub>HDEG</sub>         | Hall deglitch time                           |                                          |      | 20                                               |         | μs              |

|                           | DRIVERS                                      | I                                        |      |                                                  |         | ۳۵              |

# **Electrical Characteristics (continued)**

over operating free-air temperature range (unless otherwise noted)

|                       | PARAMETER                                                           | TEST CONDITIONS                   | MIN   | TYP      | MAX   | UNIT |  |  |

|-----------------------|---------------------------------------------------------------------|-----------------------------------|-------|----------|-------|------|--|--|

| V <sub>OUTH</sub>     | High-side gate drive output voltage                                 | $I_0 = 100 \ \mu A, \ VM \ge 12V$ |       | VM + 10  |       | V    |  |  |

| V <sub>OUTL</sub>     | Low-side gate drive output voltage                                  | I <sub>O</sub> = 100 μA           |       | 10       |       | V    |  |  |

|                       |                                                                     | IDRIVE = 000                      |       | 10       |       |      |  |  |

|                       |                                                                     | IDRIVE = 001                      |       | 20       |       |      |  |  |

|                       |                                                                     | IDRIVE = 010                      |       | 30       |       |      |  |  |

|                       |                                                                     | IDRIVE = 011                      |       | 50       |       |      |  |  |

| I <sub>OUT</sub>      | Peak gate drive current                                             | IDRIVE = 100                      |       | 90       |       | mA   |  |  |

|                       |                                                                     | IDRIVE = 101                      |       | 100      |       |      |  |  |

|                       |                                                                     | IDRIVE = 110                      |       | 110      |       |      |  |  |

|                       |                                                                     | IDRIVE = 111                      |       | 130      |       |      |  |  |

| CYCLE-BY              | -CYCLE CURRENT LIMITER                                              |                                   |       |          |       |      |  |  |

| V <sub>LIMITER</sub>  | Voltage limit across R <sub>ISENSE</sub> for the current limiter    |                                   | 0.225 | 0.25     | 0.275 | V    |  |  |

|                       |                                                                     | OCPDEG = 00                       |       | 2.0      |       |      |  |  |

|                       | Time that $V_{\text{LIMITER}}$ is ignored, from the start of        | OCPDEG = 01                       |       | 3.0      |       |      |  |  |

| t <sub>BLANK</sub>    | the PWM cycle                                                       | OCPDEG = 10                       |       | 3.75     |       | μs   |  |  |

|                       |                                                                     | OCPDEG = 11                       |       | 6        |       |      |  |  |

| PROTECTI              | ON CIRCUITS                                                         |                                   |       |          |       |      |  |  |

| V <sub>SENSEOCP</sub> | Voltage limit across R <sub>ISENSE</sub> for overcurrent protection |                                   | 1.7   | 1.8      | 1.9   | V    |  |  |

|                       |                                                                     | OCPDEG = 00                       |       | 1.6      |       |      |  |  |

|                       |                                                                     | OCPDEG = 01                       |       | 2.3      |       |      |  |  |

| t <sub>SENSEOCP</sub> | Deglitch time for V <sub>SENSEOCP</sub> to trigger                  | OCPDEG = 10                       |       | 3        |       | μs   |  |  |

|                       |                                                                     | OCPDEG = 11                       |       | 5        |       |      |  |  |

|                       |                                                                     | OCPTH = 00                        | 200   | 250      | 400   |      |  |  |

|                       | Voltage limit across each external FET's drain                      | OCPTH = 01                        | 400   | 500      | 600   |      |  |  |

| V <sub>FETOCP</sub>   | to source for overcurrent protection                                | OCPTH = 10                        | 600   | 750      | 850   | mV   |  |  |

|                       |                                                                     | OCPTH = 11                        | 850   | 1000     | 1200  |      |  |  |

|                       |                                                                     | OCPDEG = 00                       |       | 1.6      |       |      |  |  |

|                       |                                                                     | OCPDEG = 01                       |       | 2.26     |       |      |  |  |

| <b>t</b> FETOCP       | Deglitch time for V <sub>FETOCP</sub> to trigger                    | OCPDEG = 10                       |       | 3        |       | μs   |  |  |

|                       |                                                                     | OCPDEG = 11                       |       | 5        |       |      |  |  |

|                       |                                                                     | VM rising                         |       | 8        |       |      |  |  |

| V <sub>UVLO</sub>     | VM undervoltage lockout                                             | VM falling                        |       | 7.8      |       | V    |  |  |

|                       |                                                                     | VM rising, OVTH = 0               | 32    | 34       | 36    |      |  |  |

| V <sub>OVLO</sub>     | VM overvoltage lockout                                              | VM rising, OVTH = 1               | 02    | τŪ       | 29    | V    |  |  |

| toctov                | Fault retry time after RLOCK or OTS                                 | RETRY = 1                         |       | 5        | 20    | S    |  |  |

| t <sub>RETRY</sub>    | Thermal shutdown die temperature                                    |                                   | 150   | 160      |       | °C   |  |  |

| T <sub>TSD</sub>      | memai shutuown die temperature                                      | LRTIME = 00                       | 130   | 100      |       | U    |  |  |

|                       |                                                                     |                                   |       |          |       |      |  |  |

| t <sub>LOCK</sub>     | Locked rotor detect time                                            | LRTIME = 01                       |       | 3        |       | s    |  |  |

|                       |                                                                     | LRTIME = 10                       |       | 5        |       |      |  |  |

| . ,                   |                                                                     | LRTIME = 11                       |       | 10       |       |      |  |  |

| V <sub>CPFAIL</sub>   | VCP failure threshold (CPFAIL bit)                                  |                                   |       | VM + 3.0 |       | V    |  |  |

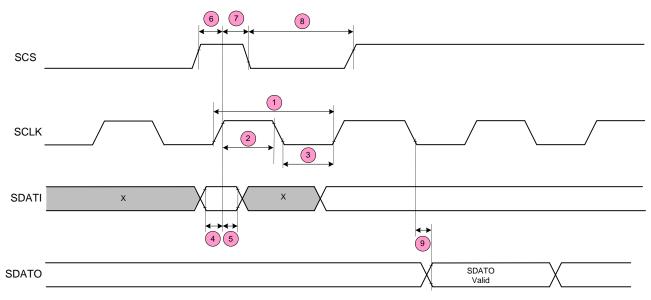

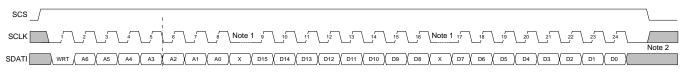

# 7.6 SPI Timing Requirements

| NUMBER <sup>(1)</sup> | PARAMETER              | TEST CONDITIONS <sup>(2)</sup>                                     | MIN | MAX | UNIT |

|-----------------------|------------------------|--------------------------------------------------------------------|-----|-----|------|

| 1                     | t <sub>CYC</sub>       | Clock cycle time                                                   | 62  |     |      |

| 2                     | t <sub>CLKH</sub>      | Clock high time                                                    | 25  |     |      |

| 3                     | t <sub>CLKL</sub>      | Clock low time                                                     | 25  |     |      |

| 4                     | t <sub>SU(SDATI)</sub> | Setup time, SDATI to SCLK                                          | 5   |     |      |

| 5                     | t <sub>H(SDATI)</sub>  | Hold time, SDATI to SCLK                                           | 1   |     | ns   |

| 6                     | t <sub>SU(SCS)</sub>   | Setup time, SCS to SCLK                                            | 5   |     |      |

| 7                     | t <sub>H(SCS)</sub>    | Hold time, SCS to SCLK                                             | 1   |     |      |

| 8                     | t <sub>L(SCS)</sub>    | Inactive time, SCS (between writes)                                | 100 |     |      |

| 9                     | t <sub>D(SDATO)</sub>  | Delay time, SCLK to SDATO (during read)                            |     | 10  |      |

|                       | t <sub>AWAKE</sub>     | Wake time (ENABLE active to high-side gate drive enabled)          |     | 1   | ms   |

|                       | t <sub>SPI</sub>       | Delay from power-up or RESET low until serial interface functional |     | 10  | μs   |

$T_A = 25^{\circ}C$ , over recommended operating conditions unless otherwise noted

(1) These numbers refer to the corresponding number in Figure 1

(2) SMODE = Low

Figure 1. SPI Timing Requirements

# 8 Detailed Description

# 8.1 Overview

The DRV8308 device controls 3-phase brushless DC motors using a speed and direction input interface and Hall signals from the motor. The device drives N-channel MOSFETs with 10-V  $V_{GS}$ , and a configurable gate drive current of 10 to 130 mA.

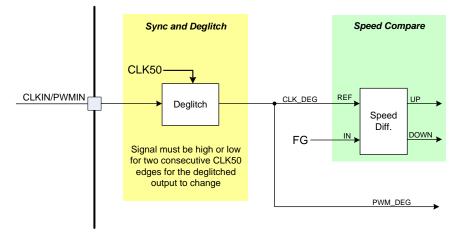

There are three modes of speed input: clock frequency, clock duty cycle (pulse-width modulation), and an internal register that specifies duty cycle. In the clock frequency mode, the device's digital speed control system matches motor speed with the input clock's frequency. Motor speed is either determined from the Halls sensors or signal on the FG input, which can be generated from a board trace underneath the motor that senses magnetic reluctance. The speed control system offers digital tuning of pole and zero frequencies and integrator gain. When properly tuned, the DRV8308 can drive motors with < 0.1% cycle jitter and fast torque compensation for varying loads. The duty cycle speed modes operate in open-loop without speed control.

When the DRV8308 device powers up, the configuration registers are set from either the one-time programmable (OTP) non-volatile memory, or from an external EEPROM (depending on the SMODE pin). After power-up, registers can be set in realtime over SPI, and the OTP memory can be permanently written once.

When the DRV8308 device begins spinning a motor, it initially uses all three Hall sensor phases to commutate. After a constant speed is reached, the LOCKn pin is pulled low and only one Hall sensor becomes used; this feature reduces jitter by eliminating the error caused by non-ideal Hall device placement and matching. Also at this time, commutation transitions to sine wave current drive (if enabled), which minimizes acoustic noise and torque ripple. Commutation timing can be tuned using the ADVANCE register for optimal performance and power efficiency.

Numerous protection circuits prevent system components from being damaged during adverse conditions. Monitored aspects include motor voltage and current, gate drive voltage and current, device temperature, and rotor lockup. When a fault occurs, the DRV8308 device stops driving and pulls FAULTn low, in order to prevent FET damage and motor overheating.

The DRV8308 device is packaged in a compact  $6 \times 6$ -mm, 40-pin QFN with a 0.5-mm pin pitch, and operates through an industrial ambient temperature range of  $-40^{\circ}$ C to  $85^{\circ}$ C.

www.ti.com

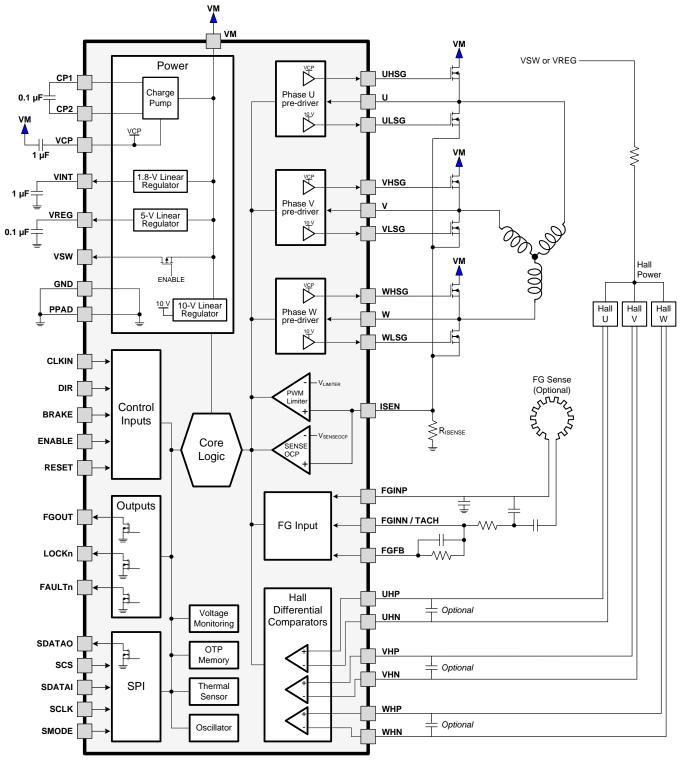

# 8.2 Functional Block Diagram

Figure 2.

## 8.3 Feature Description

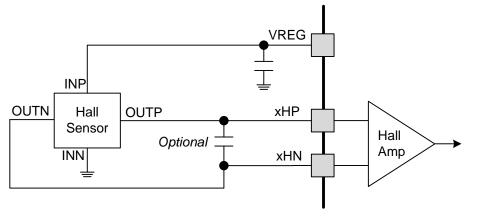

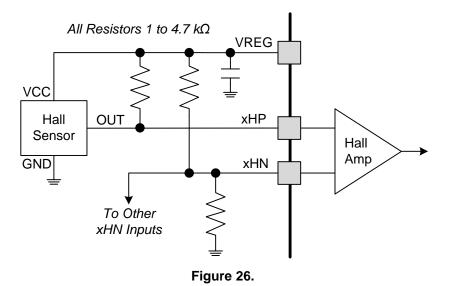

#### 8.3.1 Hall Comparators

Three comparators are provided to process the raw signals from Hall effect transducers to commutate the motor. The Hall amplifiers sense zero crossings of the differential inputs and pass the information to digital logic.

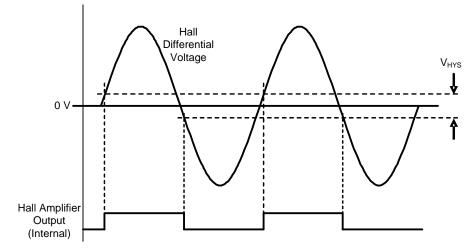

The Hall amplifiers have hysteresis, and their detect threshold is centered at 0. Note, hysteresis is defined as shown in Figure 3:

Figure 3. Hall Amplifier Hysteresis

In addition to the hysteresis, the Hall inputs are deglitched with a circuit that ignores any extra Hall transitions for a period of 20  $\mu$ s after sensing a valid transition. This prevents PWM noise from being coupled into the Hall inputs, which can result in erroneous commutation.

If excessive noise is still coupled into the Hall comparator inputs, it may be necessary to add capacitors between the + and – inputs of the Hall comparators, and (or) between the input or inputs and ground.

The ESD protection circuitry on the Hall inputs implements a diode to VREG. Because of this diode, the voltage on the Hall inputs should not exceed the VREG voltage.

Since VREG is disabled in standby mode (ENABLE inactive), the Hall inputs should not be driven by external voltages in standby mode. If the Hall sensors are powered from VREG or from VSW, this is specified by the DRV8308 device; however, if the Hall sensors are powered externally, they should be disabled if the DRV8308 is put into standby mode. In addition, they should be powered-up before enabling the motor, or an invalid Hall state may cause a delay in motor operation.

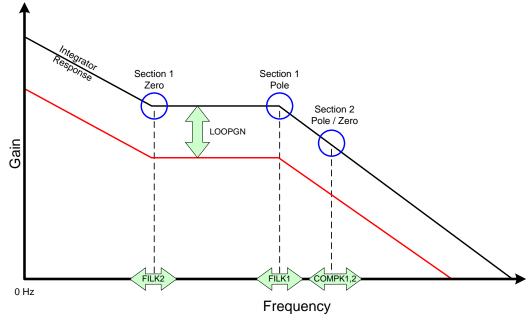

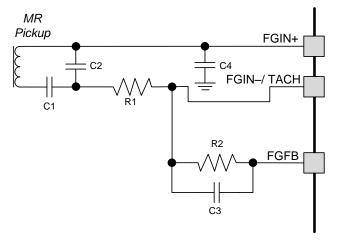

# 8.3.2 FG Amplifier, Comparator, and FG Output

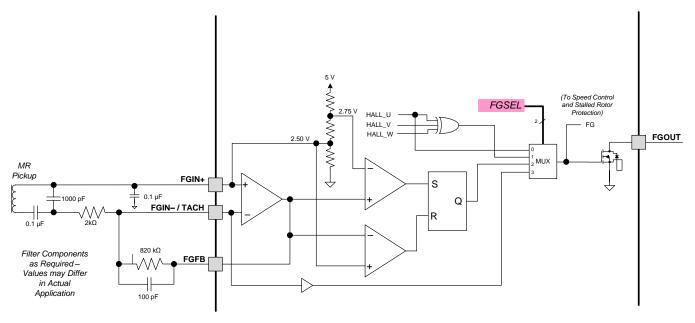

An FG amplifier and comparator provide rotational feedback from an external magnetic reluctance sensor. A diagram of the FG circuit is shown in Figure 4:

TEXAS INSTRUMENTS

www.ti.com

# Feature Description (continued)

Figure 4. FG Circuit Diagram

The output of the FG amplifier is provided on a pin, so the gain of the FG amplifier can be set by the user. Filter circuits can also be implemented.

Note that the FG signal is also fed back internally to the speed control circuits.

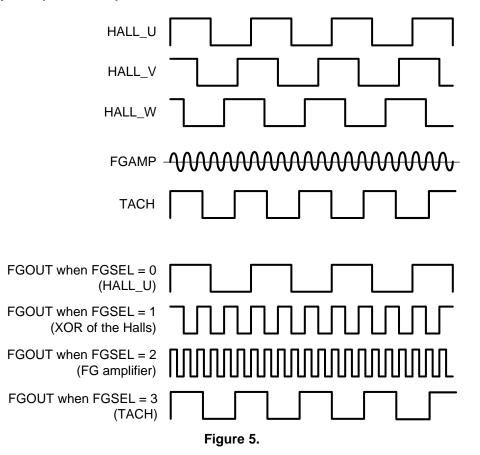

The FG signal that the DRV8308 device uses can be generated from a PCB trace under a motor, or it can be input from a logic-level TACH input, or it can be synthesized from the Hall sensor transitions (selectable by register FGSEL). If generated from Hall transitions, the resulting output can be either an exclusive-or function of the three Hall sensors, or the same as the HALL\_U input, as shown in Figure 5.

Selection of FG operating mode is through the FGSEL register bits.

The FGOUT pin is an open-drain output and requires an external pullup resistor to the logic supply.

# **Feature Description (continued)**

#### 8.3.3 Enable, Reset, and Clock Generation

The ENABLE pin is used to start and stop motor operation. ENABLE can be programmed to be active high or active low, depending on the state of the ENPOL bit; if ENPOL = 0, ENABLE is active high. If ENPOL = 1, the ENABLE pin is active low.

The polarity of ENABLE cannot be modified during operation through register writes; it is controlled only by the contents of the ENPOL bit in OTP memory.

When ENABLE is active, operation of the motor is enabled. When ENABLE is made inactive, the speed control loop is reset, and the motor either brakes or coasts depending on the state of the BRKMOD bit. After motor rotation has stopped (when no transitions occur on the FGOUT pin for a period of 1 s), the DRV8308 device enters a low-power standby state. In the standby state, the motor driver circuitry is disabled (all gate drive outputs are driven low, so the FET outputs are high-impedance), the gate drive regulator and charge pump are disabled, the VREG regulator and VSW power switch are disabled, and all analog circuitry is placed into a low power state. The digital circuitry in the device still operates in standby mode.

All internal logic is reset in three different ways:

- 1. Upon device power-up.

- 2. When VM drops below  $V_{RESET}$ .

- 3. When the RESET pin is high while ENABLE is active.

If RESET is high while ENABLE is inactive, then the registers read as 1. If the RESET pin is not needed, it can be connected to GND. The RESET input is deglitched with a 10-µs timer on assertion and deassertion.

An internal clock generator provides all timing for the DRV8308 device. The master oscillator runs at 100 MHz. This clock is divided to a nominal 50-MHz frequency that clocks the remainder of the digital logic.

Copyright © 2014, Texas Instruments Incorporated

# Feature Description (continued)

# 8.3.4 Commutation

For 3-phase brushless DC motors, rotor position feedback is provided from Hall effect transducers mounted on the motor. These transducers provide three overlapping signals, each 60° apart. The windings are energized in accordance with the signals from the Hall sensors to cause the motor to move.

In addition to the Hall sensor inputs, commutation is affected by a direction control, which alters the direction of motion by reversing the commutation sequence. Control of commutation direction is by the DIRPOL register bit as well as the DIR input pin. The DIRPOL register bit is combined with the pin with an exclusive-OR function as follows:

| DIR Pin | DIRPOL Register Bit | Resulting DIR for Commutation |

|---------|---------------------|-------------------------------|

| 0       | 0                   | 0                             |

| 0       | 1                   | 1                             |

| 1       | 0                   | 1                             |

| 1       | 1                   | 0                             |

Table 1. Direction Behavior

If the commanded direction is changed while the motor is moving, the device either brakes or allows the motor to coast, depending on the state of the BRKMODE bit, until the motor stops. The stopped condition is determined by measuring the period of the HALL\_U signal; when the period exceeds 160 ms, typical operation resumes and the motor starts spinning in the commanded direction. This prevents excessive current flow in the output stage if the motor is reversed while running at speed.

The DRV8308 device supports three commutation modes: standard 120° commutation using three Hall sensors, 120° commutation using a single Hall sensor, and 180° sine-wave-drive commutation.

In standard 120° commutation, mis-positioning of the Hall sensors can cause motor noise, vibration, and torque ripple. 120° commutation using a single Hall sensor (single-Hall commutation) can improve motor torque ripple and vibration because it relies on only one Hall edge for timing.

180° sine-wave-drive commutation is even more advanced, and excites the windings with a waveform that delivers nearly sinusoidal current to each winding.

## 8.3.4.1 120° 3-Hall Commutation

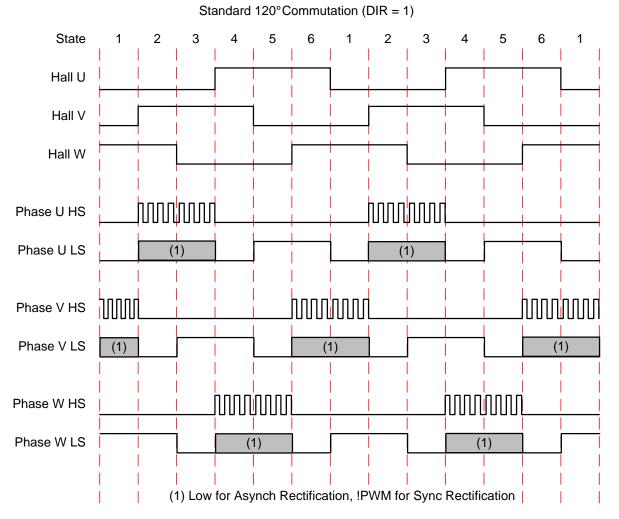

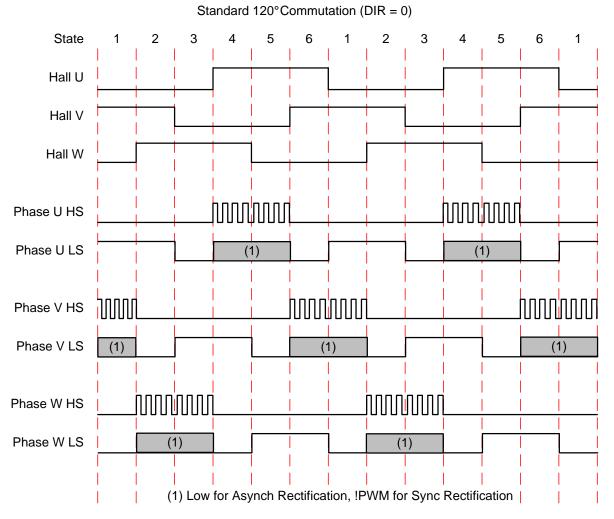

In standard 120° commutation, the motor phases are energized using simple combination logic based on all three Hall sensor inputs.

Standard 120° commutation is in accordance with Table 2, Figure 6, and Figure 7:

|       |     | I               | HALL I | NPUTS | 5   |      |                 |                         | PRE-DRIV | E OUTPUTS               |          |                         |

|-------|-----|-----------------|--------|-------|-----|------|-----------------|-------------------------|----------|-------------------------|----------|-------------------------|

| STATE | I   | DIR = 1 DIR = 0 |        |       | Pha | se U | Phase V Phase W |                         |          | se W                    |          |                         |

|       | U_H | V_H             | W_H    | U_H   | V_H | W_H  | U_HSGATE        | U_HSGATE U_LSGATE       |          | V_LSGATE                | W_HSGATE | W_LSGATE                |

| 1     | L   | L               | Н      | н     | Н   | L    | L               | L                       | PWM      | L / !PWM <sup>(2)</sup> | L        | Н                       |

| 2     | L   | Н               | Н      | Н     | L   | L    | PWM             | L / !PWM <sup>(2)</sup> | L        | L                       | L        | Н                       |

| 3     | L   | Н               | L      | н     | L   | Н    | PWM             | L / !PWM <sup>(2)</sup> | L        | Н                       | L        | L                       |

| 4     | Н   | Н               | L      | L     | L   | Н    | L               | L                       | L        | Н                       | PWM      | L / !PWM <sup>(2)</sup> |

| 5     | Н   | L               | L      | L     | Н   | Н    | L               | Н                       | L        | L                       | PWM      | L / !PWM <sup>(2)</sup> |

| 6     | Н   | L               | Н      | L     | Н   | L    | L               | Н                       | PWM      | L / !PWM <sup>(2)</sup> | L        | L                       |

| 1X    | Н   | Н               | Н      | L     | L   | L    | L               | L                       | L        | L                       | L        | L                       |

| 2X    | L   | L               | L      | н     | Н   | Н    | L               | L                       | L        | L                       | L        | L                       |

Table 2. Standard 120° Commutation<sup>(1)</sup>

(1) Hall sensor is "H" if the positive input pin voltage is higher than the negative input pin voltage. States 1X and 2X are illegal input combinations.

(2) During states where the phase is driven with a PWM signal, using asynchronous rectification, the LS gate is held off (L); using synchronous rectification, the LS gate is driven with the inverse of the HS gate.

Figure 6. Standard 120° Commutation (DIR = 1)

Figure 7. Standard 120° Commutation (DIR = 0)

## 8.3.4.2 120° Single-Hall Commutation

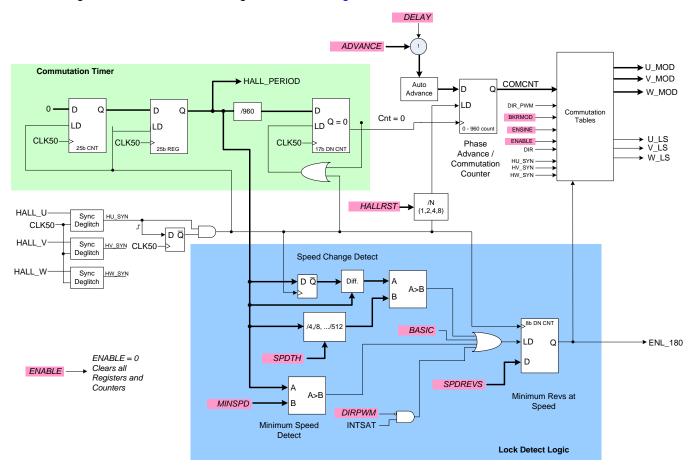

To generate commutation timing for single-Hall commutation, a digital timer is used to create a clock that runs at 960× the Hall sensor frequency. Only one Hall sensor input, HALL\_U, is used for commutation; this eliminates any torque ripple caused by mechanical or electrical offsets of individual Hall sensors.

Single-Hall commutation is only enabled when the register BASIC = 0 and the motor is operating at a nearly constant speed or speed-locked condition. To control this function, logic is used to determine when the speed is constant and the speed control loop is locked. This logic generates the LOCK signal. The LOCK signal is also output on the LOCKn pin.

Except in PWM input modes, LOCK is also prevented from being signaled if the speed control loop integrator is saturated (either at 0 or full-scale), which indicates that the speed control loop is not locked.

Until LOCK goes active (for example, at start-up, stop, or application of a sudden load that causes motor speed to drop very quickly), standard 120° commutation is used. Because of this, three Hall sensors are required regardless of which commutation method is used.

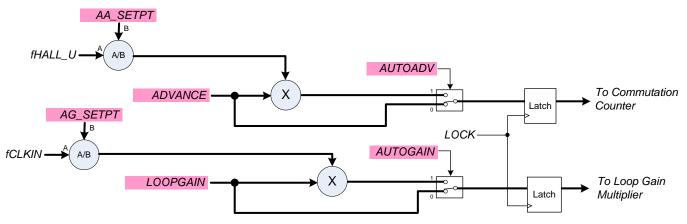

The commutation timer drives a counter that can be offset with a value programmed in the ADVANCE register. This value allows the phase of commutation to be shifted relative to the actual Hall sensor transitions. Note that the phase advance is not functional in standard 120° commutation. The phase advance also has an automatic mode where the advance value is scaled according to motor speed (see Auto Gain and Advance Compensation).

Timing of 120° single-Hall commutation is essentially the same as standard 120° commutation shown previously. However, there are small time differences of when the transitions occur.

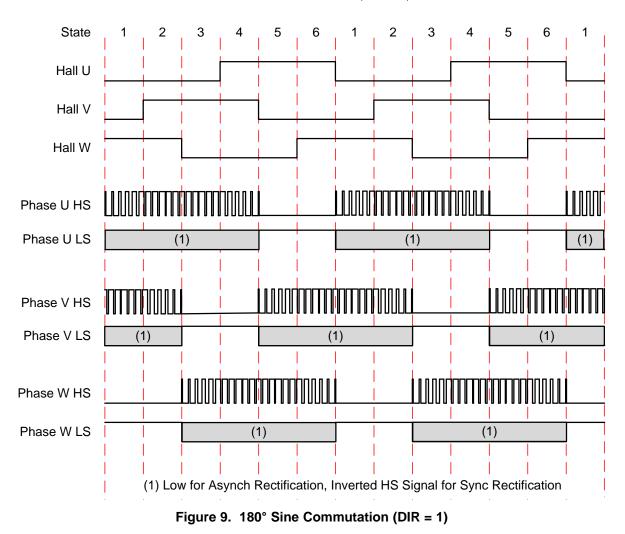

#### 8.3.4.3 180° Sine-Wave-Drive Commutation

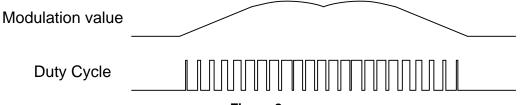

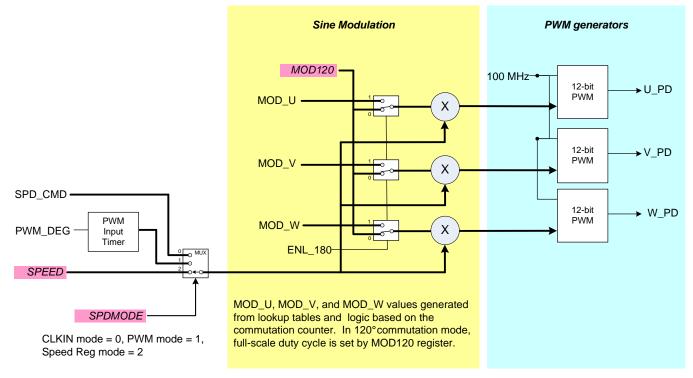

180° sine-wave-drive commutation uses a single Hall sensor to generate commutation timing, as described for 120° single-Hall commutation. In addition, the value of the commutation timer modulates the duty cycle of the outputs in accordance with a fixed pattern that approximates sinusoidal current through the windings.

The output of the commutation block is a 12-bit modulation value for each motor phase (U, V, and W) that represents the duty cycle modulation of the PWM for each output. Note that during 120° commutation, these values are either 0 or set to a constant value derived from the MOD120 register.

To make a smooth transition from 120° operation to 180° operation the MOD120 register should be set to a value of 3970.

During 180° sine-wave-drive commutation, commutation transitions occur midway between Hall transitions. The PWM duty cycle is modulated to provide sinusoidal current waveforms. Commutation (shown for asynchronous rectification) is in accordance with the table and diagrams below. Note that the diagrams show a representation of duty cycle, not level, for the PWM states.

|       |         |     | HALL I | NPUTS | 5       |       | PRE-DRIVE OUTPUTS |                         |          |                         |          |                         |  |

|-------|---------|-----|--------|-------|---------|-------|-------------------|-------------------------|----------|-------------------------|----------|-------------------------|--|

| STATE | DIR = 1 |     |        | -     | DIR = 0 | )     | Pha               | se U                    | Phase V  |                         | Phase W  |                         |  |

|       | U_H     | V_H | W_H    | U_H   | V_H     | $W_H$ | U_HSGATE          | U_LSGATE                | V_HSGATE | V_LSGATE                | W_HSGATE | W_LSGATE                |  |

| 1     | L       | L   | Н      | Н     | Н       | L     | PWM               | L / !PWM <sup>(2)</sup> | PWM      | L / !PWM <sup>(2)</sup> | L        | Н                       |  |

| 2     | L       | Н   | Н      | Н     | L       | L     | PWM               | L / !PWM <sup>(2)</sup> | PWM      | L / !PWM <sup>(2)</sup> | L        | Н                       |  |

| 3     | L       | н   | L      | Н     | L       | Н     | PWM               | L / !PWM <sup>(2)</sup> | L        | Н                       | PWM      | L / !PWM <sup>(2)</sup> |  |

| 4     | Н       | Н   | L      | L     | L       | Н     | PWM               | L / !PWM <sup>(2)</sup> | L        | Н                       | PWM      | L / !PWM <sup>(2)</sup> |  |

| 5     | Н       | L   | L      | L     | Н       | Н     | L                 | Н                       | PWM      | L / !PWM <sup>(2)</sup> | PWM      | L / !PWM <sup>(2)</sup> |  |

| 6     | Н       | L   | Н      | L     | Н       | L     | L                 | Н                       | PWM      | L / !PWM <sup>(2)</sup> | PWM      | L / !PWM <sup>(2)</sup> |  |

| 1X    | Н       | н   | Н      | L     | L       | L     | L                 | L                       | L        | L                       | L        | L                       |  |

| 2X    | L       | L   | L      | Н     | Н       | Н     | L                 | L                       | L        | L                       | L        | L                       |  |

## Table 3. Commutation for Asynchronous Rectification<sup>(1)</sup>

(1) Hall sensor is "H" if the positive input pin voltage is higher than the negative input pin voltage. States 1X and 2X are illegal input combinations.

(2) During states where the phase is driven with a PWM signal, using asynchronous rectification, the LS gate is held off (L); using synchronous rectification, the LS gate is driven with the inverse of the HS gate.

180° Sine Commutation (DIR = 1)

180° Sine Commutation (DIR = 0) 2 2 State 6 5 4 3 1 6 5 4 3 1 6 Hall U Hall V Hall W Phase U HS Phase U LS (1) (1) Phase V HS Phase V LS (1) (1) (1) Phase W HS Phase W LS (1) (1) (1) (1) Low for Asynch Rectification, Inverted HS Signal for Sync Rectification

Figure 10. 180° Sine Commutation (DIR = 0)

# 8.3.5 Commutation Logic Block Diagram

A block diagram of the commutation logic is shown in Figure 11.

Figure 11. Commutation Logic

## 8.3.6 Commutation Parameters

A number of commutation parameters are programmable through registers accessed through the serial interface, including:

- ADVANCE The phase of commutation is advanced (or delayed) relative to the Hall sensor transition by this 8-bit amount. Units are in commutation clocks, which is 1 / 960 of the HALL\_U period. Note that phase advance is only applicable in single-Hall commutation modes. An automatic phase advance compensation mode can also be enabled by the AUTOADV bit (see Auto Gain and Advance Compensation for details).

- DELAY if set, commutation is delayed relative to Hall transitions; if cleared, commutation is advanced relative to Hall transitions.

- BASIC The BASIC bit, when set, prevents single-Hall or 180° commutation from being entered regardless of the above parameters, forces conventional 120° commutation, and disables ADVANCE functionality.

- ENSINE The ENSINE bit, when set, selects 180° sinusoidal commutation. The BASIC bit must also be 0.

- HALLRST HALLRST sets how many HALL\_U cycles pass for each commutation counter reset. In other words, the commutation counter is reset every N HALL\_U edges. Selections available are 1, 2, 4, and 8.

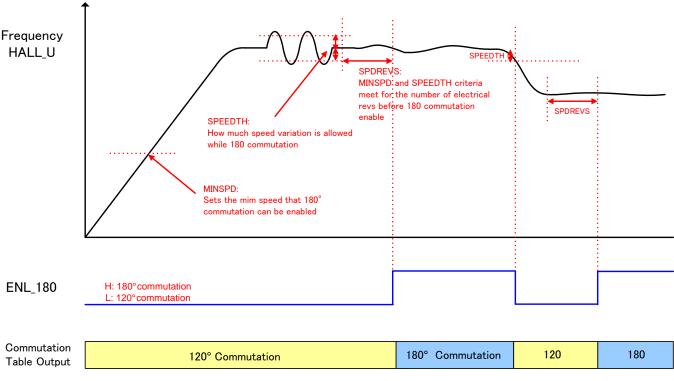

- MINSPD Sets the minimum Hall\_U period that LOCK can be set. The 8-bit field represents 2.56 ms/count, with a max value of 652.8 ms.

- SPDREVS After the MINSPD and SPEEDTH criteria are met, SPDREVS adds a minimum number of Hall\_U periods that must occur for LOCK to be set.

- SPEEDTH Sets how much speed variation is allowed across Hall\_U periods while keeping LOCK set. This 3-bit field sets the percentage variation allowed by changing a programmable divider. Divisions of 1/4, 1/8, 1/16, 1/32, 1/64, 1/128, 1/256, and 1/512 are supported. These divisors correspond to 25%, 12.5%, 6.25%,

www.ti.com

3.13%, 1.56%, 0.78%, 0.39%, and 0.20% variation per revolution.

The diagram below shows how the lock parameters (MINSPD, SPEEDTH, and SPDREV) affect commutation mode.

## 8.3.7 Braking

Motor braking can be initiated by the BRKPOL register bit as well as the BRAKE pin. The BRKPOL register bit can also be used to program the polarity of the BRAKE pin, as it is combined with the pin with an exclusive-OR function as follows:

| BRAKE pin | BRKPOL Register Bit | <b>Resulting Function</b> |

|-----------|---------------------|---------------------------|

| 0         | 0                   | Not brake                 |

| 0         | 1                   | Brake                     |

| 1         | 0                   | Brake                     |

| 1         | 1                   | Not brake                 |

When the motor is braking, all low-side drivers are held in an on state, causing all low-side FETs to turn on, and the integrator is reset to 0.

In addition, braking can be entered when the ENABLE pin is made inactive. BRKMOD controls the behavior of the outputs when ENABLE is inactive. If BRKMOD= 0, the outputs are 3-stated, resulting in the motor coasting; if BRKMOD = 1, all low-side FETs are turned on, causing the motor to brake.

|                   | BRKMOD = 0<br>COAST | BRKMOD = 1<br>BRAKE |  |  |  |  |  |

|-------------------|---------------------|---------------------|--|--|--|--|--|

| RESET = 1         | Coast               | Brake               |  |  |  |  |  |

| BRAKE = active    | Brake               | Brake               |  |  |  |  |  |

| ENABLE = inactive | Coast               | Brake               |  |  |  |  |  |

| Table 5. BRRINDD (continued) |                     |                     |  |  |  |

|------------------------------|---------------------|---------------------|--|--|--|

|                              | BRKMOD = 0<br>COAST | BRKMOD = 1<br>BRAKE |  |  |  |

| DIR                          | Coast               | Brake               |  |  |  |

| Clock off                    | Brake               | Brake               |  |  |  |

| Power down                   | Coast               | Brake               |  |  |  |

## Table 5. BRKMOD (continued)

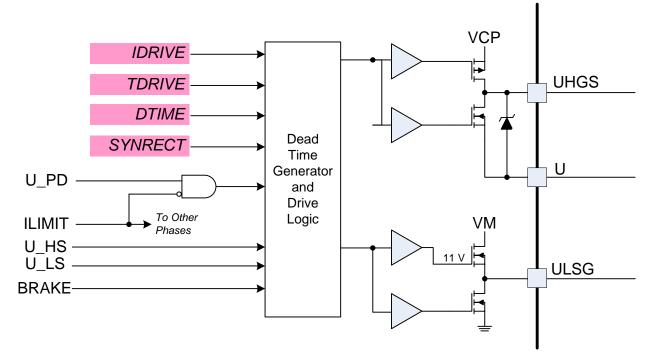

#### 8.3.8 Output Pre-Drivers

The output drivers for each phase consist of N-channel and P-channel MOSFET devices arranged as a CMOS buffer. They are designed to directly drive the gate of external N-channel power MOSFETs.

The outputs can provide synchronous or asynchronous rectification. In asynchronous rectification, only the highside FET is turned on and off with the PWM signal; current is recirculated using external diodes, or the body diodes of the external FETs. In synchronous rectification, the low side FET is turned on when the high side is turned off.

Synchronous rectification is enabled or disabled using the SYNRECT control bit. When set to 1, synchronous rectification is used. In general, synchronous rectification results in better speed control and higher efficiency.

The high-side gate drive output UHSG is driven to VCP whenever the duty cycle output U\_PD from the PWM generator is high, the enable signal U\_HS from the commutation logic is active, and the current limit ( $V_{\text{LIMITER}}$ ) is not active. If the high-side FET is on and a current limit event occurs, the high-side FET is immediately turned off until the next PWM cycle.

The low-side gate drive ULSG is driven to VM whenever the internal signal U\_LS is high, or whenever synchronous rectification is active and UHSG is low.

Phases V and W operate in an identical fashion.

Figure 13.

Figure 14.

The peak drive current of the pre-drivers is adjustable by setting the IDRIVE register bits. Peak drive currents may be set between 10 and 130 mA. Adjusting the peak current changes the output slew rate, which also depends on the FET input capacitance and gate charge.

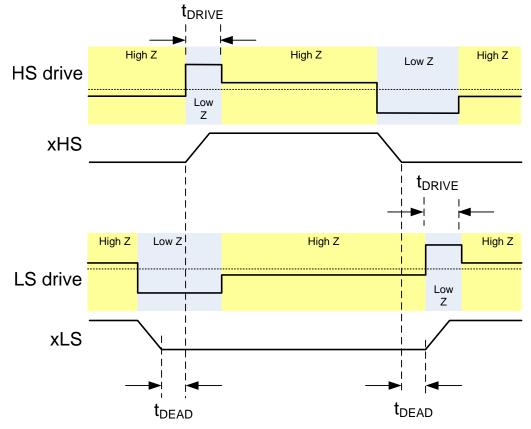

When changing the state of the output, the peak current is applied for a short period of time ( $t_{DRIVE}$ ), to charge the gate capacitance. This time is selected by setting the TDRIVE register bits. Times of 1, 5, 10, or 15 µs may be selected. After this time, a weak current source is used to keep the gate at the desired state. When selecting the gate drive strength for a given external FET, the selected current must be high enough to fully charge and discharge the gate during the time when driven at full current, or excessive power is dissipated in the FET.

During high-side turn-on, the low-side gate is held low with a low impedance. This prevents the gate-source capacitance of the low-side FET from inducing turn-on. Similarly, during low-side turn-on, the high-side gate is held off with a low impedance.