# **Power Management and USB Single Chip**

Check for Samples: TPS65921

## FEATURES

- 3 Step-Down Converters:

- Up to 1.2 A of output current for VDD1

- TPS65921B supports VDD1 up to 1.2 A

- TPS65921B1 supports VDD1 up to 1.4 A (necessary for 1-GHz operation)

- SmartReflex<sup>™</sup> dynamic voltage management

- 3.2 MHz fixed frequency operation

- $V_{IN}$  range from 2.7 to 4.5 V

- Typical 30 µA quiescent per converter

- 4 general-purpose configurable LDOs:

- Dynamic voltage scaling

- 220 mA maximum current for one LDO

- V<sub>IN</sub> range from 2.7 to 4.5 V

- 2 LDOs with low noise and high PSRR

- RTC with alarm wake up mechanism

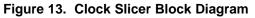

- Clock management

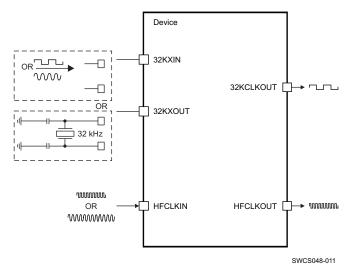

- 32-kHz crystal oscillator

- Clock slicer for 26, 19.2, and 38.4 MHz

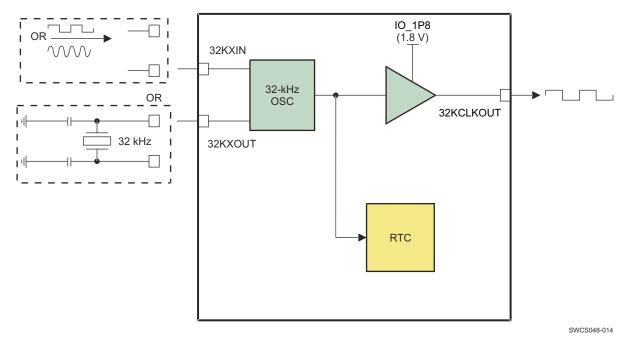

- HF clock output buffer

- USB:

- USB HS 2.0 transceiver

- USB 1.3 OTG-compliant

- 12-bit ULPI 1.1 interface

- USB power supply (5-V CP for VBUS)

- Control

- High-speed I<sup>2</sup>C<sup>™</sup> interface

- All resource configurable by I<sup>2</sup>C

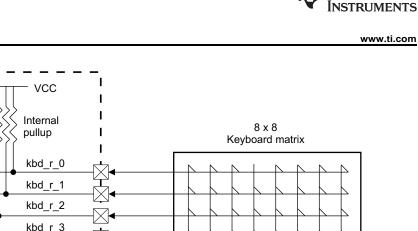

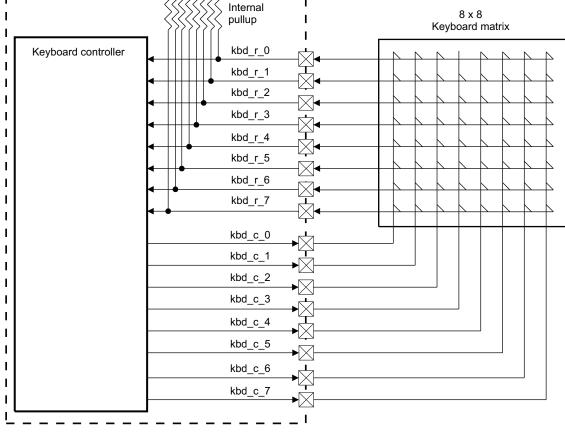

- Keypad interface up to 8 × 8

- 10-bit A/D converter

- Hot-die, thermal shutdown protection

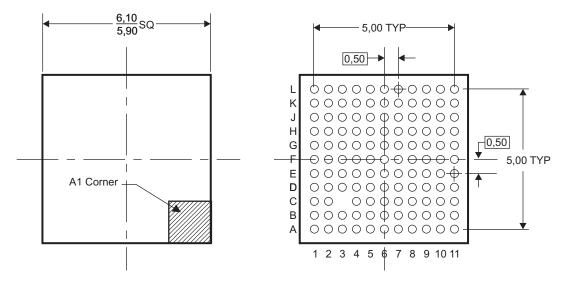

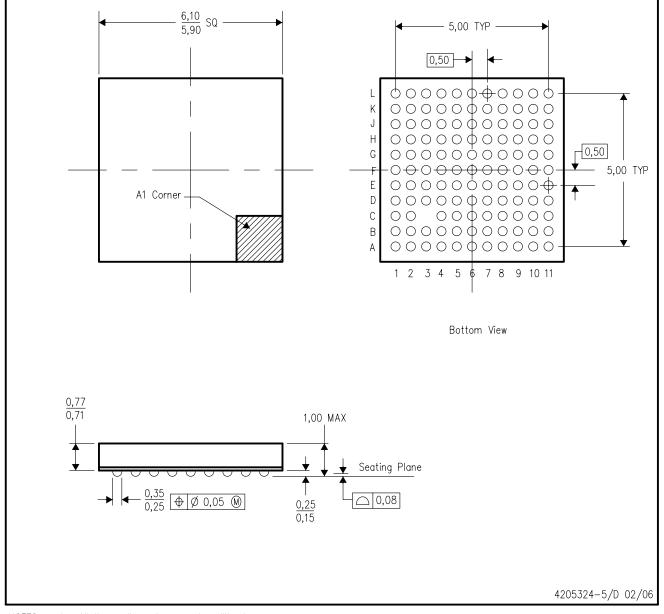

- µ\*BGA 120 balls ZQZ

## APPLICATIONS

- Mobile phones and smart phones

- MP3 players

- Handheld devices

- E-Books

- OMAP<sup>™</sup> and low power DSP supply

## DESCRIPTION

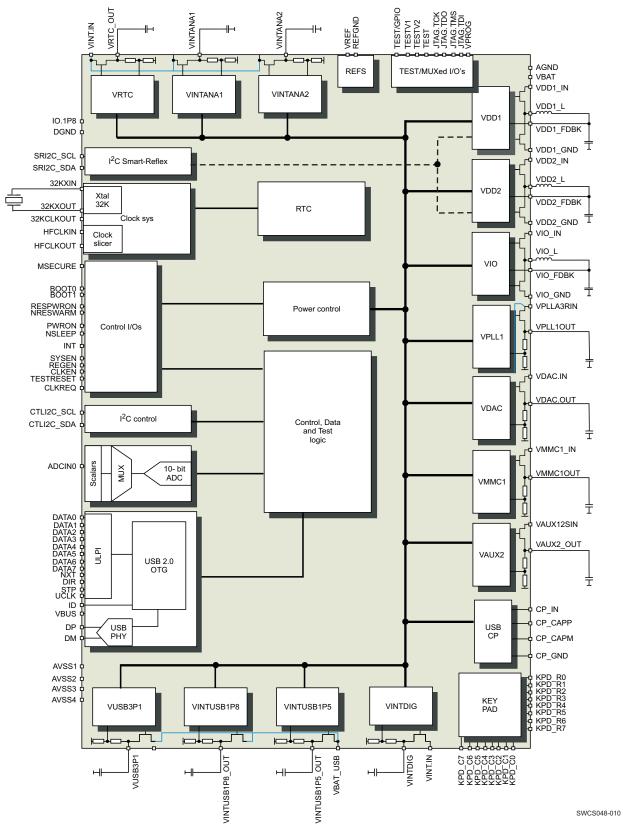

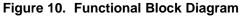

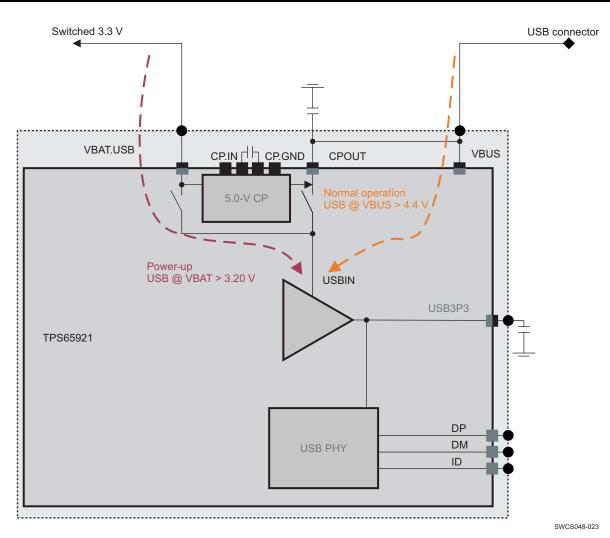

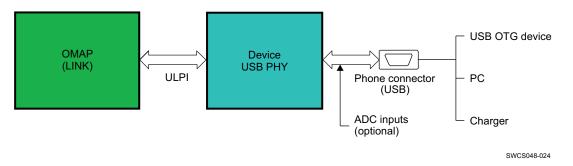

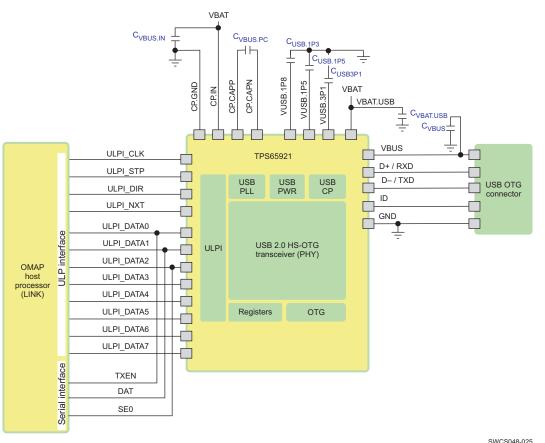

The TPS65921 device is a highly integrated powermanagement circuit (IC) that supports the power and peripheral requirements of the OMAP application processors. The device contains power management, a universal serial bus (USB) high-speed (HS) transceiver, an analog-to-digital converter (ADC), a real-time clock (RTC), a keypad interface, and an embedded power control (EPC). The power portion of the device contains three buck converters, two controllable by a dedicated SmartReflex<sup>™</sup> class-3 interface, multiple low-dropout (LDO) regulators, an EPC to manage the power-sequencing requirements of OMAP, and an RTC module. The USB module provides a HS 2.0 transceiver suitable for direct connection to the OMAP universal transceiver macrocell interface (UTMI) + low pin interface (ULPI) with an integrated charge pump (CP).

The device also provides auxiliary modules: ADC, keypad interface, and general-purpose inputs/outputs (GPIOs) muxed with the JTAG functions. The keypad interface implements a built-in scanning algorithm to decode hardware-based key presses and to reduce software use, with multiple additional GPIOs that can be used as interrupts when they are configured as inputs.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

over operating free-air temperature range (unless otherwise noted)

| PARAMETER                                        | TEST CONDITIONS                                                                                              | MIN  | NOM | MAX                | UNIT |

|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------|------|-----|--------------------|------|

| Main battery supply voltage <sup>(2)</sup>       |                                                                                                              | 0.0  |     | 5.0                | V    |

| Voltage on any input <sup>(3)</sup>              | Where supply represents the voltage applied to the power supply pin associated with the input <sup>(4)</sup> | -0.3 |     | 1.0 × Supply + 0.3 | V    |

| VBUS input                                       |                                                                                                              | -0.3 |     | 7                  | V    |

| Storage temperature range                        |                                                                                                              | -55  |     | 125                | °C   |

| Operating ambient temperature (T <sub>A</sub> )  |                                                                                                              | -40  |     | 85                 | °C   |

| Operating junction temperature $(T_J)$           | Absolute maximum rating                                                                                      | -40  |     | 125                | °C   |

| Operating junction temperature (T <sub>J</sub> ) | For parametric compliance                                                                                    | -40  |     | 150                | °C   |

| Ambient temperature for<br>parametric compliance | With maximum 125°C as junction temperature $(T_J)$                                                           | -40  |     | 85                 | °C   |

(1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device.

(2) The product will have negligible reliability impact if voltage spikes of 5.2 V occur for a total (cumulative over lifetime) duration of 10 milliseconds.

(3) Excepts VBAT input pads and VBUS pad.

(4) Supply equals the reference level of each pin.

## **RECOMMENDED OPERATING CONDITIONS**

over operating free-air temperature range (unless otherwise noted)

|                                                            | PARAMETER                                                      | MIN                          | TYP           | МАХ                               | UNIT |

|------------------------------------------------------------|----------------------------------------------------------------|------------------------------|---------------|-----------------------------------|------|

|                                                            | Power and                                                      | JSB Path                     | ,<br>,        | -                                 |      |

| VBAT/VBAT.USB main                                         | battery supply voltage and                                     | 2.7                          | 3.6           | 4.5                               | V    |

| VBUS                                                       |                                                                | 0                            |               | 7                                 | V    |

|                                                            | HFCLKIN In                                                     | put Clock                    |               |                                   |      |

| Frequency 1/t <sub>C(HFCLKIN)</sub>                        |                                                                | 19.:                         | 2, 26 or 38.4 |                                   | MHz  |

| Pulse duration, HFCLKI                                     | N low or high (BP)                                             | $0.45 \times t_{C(HFCLKIN)}$ |               | 0.55 ×<br>t <sub>C(HFCLKIN)</sub> | ns   |

| HFCLKIN stability                                          |                                                                | -150                         |               | 150                               | ppm  |

| Rise time of HFCLKIN (                                     | BP)                                                            | 0                            |               | 5                                 | ns   |

| Fall time of HFCLKIN (BP)                                  |                                                                | 0                            |               | 5                                 | ns   |

| Input dynamic range                                        | LP/HP (sine wave)                                              | 0.3                          | 0.7           | 1.45                              | Vpp  |

| Input dynamic range                                        | BP/PD (square wave)                                            | 0                            |               | 1.85 <sup>(1)</sup>               | Vpp  |

| Harmonic content of inp component - LP/HP (sin             | ut signal (with 0.7-V <sub>PP</sub> amplitude): Second e wave) |                              |               | -25                               | dBc  |

| V <sub>IH</sub> voltage input<br>high <sup>(1)</sup>       | BP (square mode)                                               | 0.65 × IO.1P8                |               |                                   | V    |

| V <sub>IL</sub> voltage input low <sup>(1)</sup>           | BP (square mode)                                               |                              |               | 0.35 × IO.1P8                     | V    |

|                                                            | Crystal Os                                                     | scillator                    |               |                                   |      |

| Parallel resonance cryst                                   | al frequency 1/t <sub>C(32KHZ)</sub>                           |                              | 32.768        |                                   | kHz  |

| Input voltage, Vin (norm                                   | al mode)                                                       | 1.0                          | 1.3           | 1.55                              | V    |

| Crystal tolerance at roor                                  | m temperature, 25°C                                            | -30                          |               | 30                                | ppm  |

| Crystal tolerance versus temperature range (-40°C to 85°C) |                                                                | -200                         |               | 200                               | ppm  |

| Crystal quality factor                                     |                                                                | 13k                          |               | 54k                               |      |

| Maximum drive power                                        |                                                                |                              |               | 1                                 | μW   |

| Operating drive level                                      |                                                                |                              |               | 0.5                               | μW   |

(1) Bypass input maximum voltage is the same as the maximum voltage provided for the I/O interface (IO.1P8V).

www.ti.com

#### SWCS048F-MARCH 2010-REVISED MARCH 2012

## **RECOMMENDED OPERATING CONDITIONS (continued)**

over operating free-air temperature range (unless otherwise noted)

| 32KXIN 32KXOUT                          | Crystal                                                   | 40%                                                   |          | 60%                       |    |

|-----------------------------------------|-----------------------------------------------------------|-------------------------------------------------------|----------|---------------------------|----|

| duty cycle                              | Square wave                                               | 45%                                                   |          | 55%                       |    |

| 32-kHz clock rise/fall<br>time          | Square wave with capacitive load equivalent to 30 pF      |                                                       |          | $0.1 \times t_{C(32KHZ)}$ | μs |

| V <sub>IH</sub> voltage input high      | Square wave in bypass mode <sup>(1)</sup>                 | 0.65 × VBRTC                                          |          |                           | V  |

| V <sub>IL</sub> voltage input low       | Square wave in bypass mode <sup>(1)</sup>                 |                                                       |          | 0.35 × VBRTC              | V  |

|                                         | DCDC Converters                                           | and LDOs                                              |          |                           |    |

| VDD1.IN, VDD2.IN, VD<br>VDD1, VDD2, VIO | D3.IN input voltage range for step-down converter         | 2.7                                                   | 3.6      | 4.5                       | V  |

| VMMC1.IN input voltage                  | e range for LDO VMMC1                                     | Maximum (2.7,<br>output voltage<br>selected + 250 mV) | 3.6      | 4.5                       | V  |

| VDAC.IN input voltage                   | range for LDO VDAC                                        | 2.7                                                   | 3.6      | 4.5                       | V  |

| VAUX12S.IN input volta                  | ge range for LDO VAUX2                                    | Maximum (2.7,<br>output voltage<br>selected + 250 mV) | 3.6      | 4.5                       | V  |

| VINT.IN input voltage ra<br>and VRTC    | ange for LDO VINTANA1, VINTANA2, VINTDIG                  | Maximum (2.7,<br>output voltage<br>selected + 200 mV) | 3.6      | 4.5                       | V  |

| VPLLA3R.IN input volta                  | ge range for LDO VPLL1                                    | 2.7                                                   | 3.6      | 4.5                       | V  |

| VDD1.OUT ouput voltag                   | ge range for VDD1 step-down converter                     | 0.6                                                   |          | 1.45                      | V  |

| VDD2.OUT ouput voltag                   | ge range for VDD2 step-down converter                     | 0.6                                                   |          | 1.5                       | V  |

| VIO.OUT ouput voltage                   | range for VIO step-down converter                         |                                                       | 1.8/1.85 |                           | V  |

| VMMC1.OUT output vol                    | tage range for LDO VMMC1                                  | 1.85                                                  |          | 3.15                      | V  |

| VDAC.OUT output volta                   | ge range for LDO VDAC                                     | 1.2                                                   |          | 1.8                       | V  |

| VAUX2.OUT output volt                   | age range for LDO VAUX2                                   | 1.3                                                   |          | 2.8                       | V  |

| VPLL1.OUT output volta                  | age range for LDO VPLL1                                   | 1.0                                                   |          | 1.8                       | V  |

| VINTANA1.OUT output                     | voltage for LDO VINTANA1                                  |                                                       | 1.5      |                           | V  |

| VINTANA2.OUT output                     | voltage for LDO VINTANA2                                  |                                                       | 2.5/2.75 |                           | V  |

| VINTUSB1P5V.OUT ou                      | tput voltage for LDO VINTUSB1P5                           | 1.35                                                  | 1.5      | 1.65                      | V  |

| VINTUSB1P8V.OUT ou                      | tput voltage for LDO VINTUSB1P8                           | 1.62                                                  | 1.8      | 1.98                      | V  |

| VUSB3P1V.OUT output                     | t voltage for LDO VUSB3P1                                 |                                                       | 3.1      |                           | V  |

| VINTDIG.OUT output vo                   | bltage range for LDO VINTDIG                              | 1.35                                                  | 1.5      | 1.65                      | V  |

| VRTC.OUT output                         | Normal mode                                               | 1.45                                                  | 1.5      | 1.55                      | V  |

| voltage range                           | Backup mode                                               | 1.0                                                   | 1.3      | 1.55                      | V  |

|                                         | External Comp                                             | onents                                                |          | · · ·                     |    |

| Crystal: Nominal load ca                | ap on each oscillator input CXIN and CXOUT <sup>(2)</sup> | 9                                                     | 10       | 12.5                      | pF |

| Crystal ESR <sup>(3)</sup>              |                                                           |                                                       |          | 90                        | kΩ |

| Crystal shunt capacitan                 | ce, C <sub>O</sub>                                        |                                                       |          | 1                         | pF |

|                                         | Value                                                     | 0.7                                                   | 1        | 1.3                       | μH |

|                                         | DCR                                                       |                                                       |          | 0.1                       | Ω  |

| External coil for VDD1                  | Saturation current for TPS65921B                          | 1.8                                                   |          |                           | А  |

|                                         | Saturation current for TPS65921B1                         | 2.1                                                   |          |                           | А  |

(2) Nominal load capacitor on each oscillator input defined as CXIN = CXOUT = Cosc × 2 - (Cint + Cpin). Cosc is the load capacitor defined in the crystal oscillator specification, Cint is the internal capacitor, and Cpin is the parallel input capacitor.

(3) The crystal motional resistance Rm relates to the equivalent series resistance (ESR) by the following formula:

$$ESR = R_m \left(1 + \frac{C_0}{C_L}\right)^2$$

Measured with the load capacitance specified by the crystal manufacturer. In fact, if CXIN = CXOUT = 10 pF, then CL = 5 pF. Parasitic capacitance from the package and board must also be considered.

www.ti.com

**ISTRUMENTS**

EXAS

## **RECOMMENDED OPERATING CONDITIONS (continued)**

over operating free-air temperature range (unless otherwise noted)

| ver operating nee-air                                                                                                                                                        | temperature range (unless otherwise noted)<br>Value                            | 0.7                                                                                                                     | 1   | 1.3  | μH |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------|-----|------|----|

| External coil for VDD2                                                                                                                                                       | DCR                                                                            | 0.7                                                                                                                     | I   | 0.1  | μΠ |

| and VIO                                                                                                                                                                      | Saturation current                                                             | 900                                                                                                                     |     | 0.1  | mA |

| External capacitor for                                                                                                                                                       | Value <sup>(4)</sup>                                                           | 5                                                                                                                       | 10  | 15   | μF |

| VDD1, VDD2, VIO<br>connected to VDD1.IN,<br>VDD2.IN, VDD3.IN,<br>and VDD1.OUT,<br>VDD2.OUT, VIO.OUT                                                                          | ESR at switching frequency                                                     | 1                                                                                                                       |     | 20   | mΩ |

| Filtering capacitor for                                                                                                                                                      | Value                                                                          | 0.3                                                                                                                     | 1   | 2.7  | μF |

| VMCC1.IN, VDAC.IN,<br>VAUX12S.IN,<br>VPPLA3R.IN, VINT.IN,<br>VBAT.USB,<br>VMMC1.OUT,<br>VDAC.OUT,<br>VDAC.OUT,<br>VAUX2.OUT, VPPL1,<br>VINTDIG, VINTANA1,<br>VINTANA2, VRRTC | ESR                                                                            | 20                                                                                                                      |     | 600  | mΩ |

| Filtering capacitor for                                                                                                                                                      | Value                                                                          | 0.5                                                                                                                     | 2.2 | 6.5  | μF |

| VUSB3V1, VUSB1V8,<br>VUSB1V5                                                                                                                                                 | ESR                                                                            | 20                                                                                                                      |     | 600  | mΩ |

| Filtering capacitor for voltage reference                                                                                                                                    | Connected from V <sub>REF</sub> to REFGND                                      | 0.3                                                                                                                     | 1   | 2.7  | μF |

|                                                                                                                                                                              | Filtering capacitor (Connected between<br>VBUS.CPOUT and GND) and called CVBUS | 1.41 (The minimum<br>can be reduced to<br>1.2 μF, provided the<br>charge-pump is only<br>used to supply<br>VUSB3V1 LDO) | 4.7 | 6.5  | μF |

| External capacitor for<br>charge pump and<br>VBUS                                                                                                                            | Flying capacitor (Connected between CP.CAPP<br>and CP.CAPM) called CVBUS.FC    | 1.32 (The minimum<br>can be reduced to<br>1.2 µF, provided the<br>charge-pump is only<br>used to supply<br>VUSB3V1 LDO) | 2.2 | 3.08 | μF |

|                                                                                                                                                                              | Filtering capacitor ESR for CVUSB.IN and CVBUS.FC                              |                                                                                                                         |     | 20   | mΩ |

|                                                                                                                                                                              | Filtering capacitor CVBUS.IN                                                   | 5                                                                                                                       | 10  | 15   | μF |

| External capacitor for power reference filter                                                                                                                                | Filtering capacitor                                                            | 0.3                                                                                                                     | 1   | 2.7  | μF |

(4) For TPS65921B1, in case of OMAP frequency ≥ 1 GHz, replace 10-μF capacitor on VDD1.OUT by two 22-μF capacitors. One capacitor must be placed near the PMIC and one near the OMAP device.

## **ELECTRICAL CHARACTERISTICS**

## **CRYSTAL OSCILLATOR**

When selecting a crystal, the system designer must consider the temperature and aging characteristics of a crystal versus the user environment and expected lifetime of the system. The following table lists the switching characteristics of the oscillator.

| PARAMETER                                        | MIN | ТҮР    | MAX | UNIT |  |  |  |

|--------------------------------------------------|-----|--------|-----|------|--|--|--|

| Crystal: Internal capacitor on each input (Cint) | 8   | 10     | 12  | pF   |  |  |  |

| Crystal: Parallel input capacitance (Cpin)       |     |        | 1.0 | pF   |  |  |  |

| Parallel resonance crystal frequency             |     | 32.768 |     | kHz  |  |  |  |

| Pin-to-pin capacitance                           |     | 1.6    | 1.8 | pF   |  |  |  |

**Table 1. Base Oscillator Switching Characteristics**

SWCS048F-MARCH 2010-REVISED MARCH 2012

|                                                                 | PARAMETER           |                          |     | TYP | MAX | UNIT |

|-----------------------------------------------------------------|---------------------|--------------------------|-----|-----|-----|------|

| Maximum drive po                                                | ower                |                          |     |     | 1.0 | μW   |

| Operating drive le                                              | vel                 |                          |     |     | 0.5 | μW   |

| Crystal quality fac                                             | tor                 |                          | 13k |     | 54k |      |

| Start-up time, all condition                                    |                     | 3                        |     |     | 500 |      |

| t <sub>SX</sub>                                                 | Start-up time, 25°C |                          |     |     | 360 | ms   |

|                                                                 | Active current      | High jitter mode         |     |     | 1.8 |      |

| I <sub>DDA</sub> consumption (configured through the LOJIT bit) |                     | Low jitter mode          |     |     | 0.8 | μA   |

| I <sub>DDQ</sub> Current consumption                            |                     | Low battery mode (1.2 V) |     |     | 1   |      |

|                                                                 |                     | Startup                  |     |     | 8   | μA   |

## Table 1. Base Oscillator Switching Characteristics (continued)

## **CLOCK SLICER**

| PARAMETER                                                                                                  | MODE <sup>(1)</sup> | MIN  | TYP | MAX  | UNIT |

|------------------------------------------------------------------------------------------------------------|---------------------|------|-----|------|------|

| Internal coupling capacitor                                                                                |                     | 4.2  | 5   | 5.7  | pF   |

|                                                                                                            | LP                  | 15   |     | 60   | kΩ   |

| Parallel input resistance over 10 to 40 MHz range                                                          | HP                  | 30   |     | 75   | kΩ   |

|                                                                                                            | BP/PD               | 1    |     | 100  | MΩ   |

|                                                                                                            | LP                  | 0.3  |     | 0.8  |      |

| Derallel input conscitutes a war 10 to 10 MUz range                                                        | HP                  | 0.3  |     | 0.7  | ~ [  |

| Parallel input capacitance over 10 to 40 MHz range                                                         | BP/PD               | 0.08 |     | 1    | pF   |

|                                                                                                            | BP/PD               | 40   |     | 230  |      |

| Output duty cycle with $V_{IN} = 0.2 V_{PP}$                                                               | LP/HP               | 40%  | 50% | 60%  |      |

|                                                                                                            | LP                  | 4    |     | 18   |      |

| Propagation delay                                                                                          | HP                  | 3    |     | 15   | ns   |

|                                                                                                            | BP/PD               | 0.2  |     | 3    |      |

| Power supply rejection ratio sideband (1% RMS of supply voltage added sine 5 MHz)                          | LP/HP               | 26   |     |      | dBc  |

|                                                                                                            | LP                  |      |     | 175  | μA   |

| Current consumption at maximum input of 40 MHz                                                             | HP                  |      |     | 235  | μA   |

|                                                                                                            | BP/PD               |      |     | 39   | nA   |

| Power-up time                                                                                              | LP/HP               |      |     | 1    | ms   |

| Output peak-to-peak jitter with an input peak-to-peak jitter < 0.1% and for jitter frequency below 300 kHz | LP/HP               |      |     | 0.2% |      |

| Output peak-to-peak jitter with an input peak-to-peak jitter < 0.1% and for jitter frequency above 300 kHz | LP/HP               |      |     | 1.0% |      |

(1) Bypass input maximum voltage is the same as the maximum voltage provided for the I/O interface.

# 32KCLKOUT OUTPUT CLOCK

| NAME             | PARAMETER DESCRIPTION                                            | MIN                     | ТҮР                | MAX              | UNIT |

|------------------|------------------------------------------------------------------|-------------------------|--------------------|------------------|------|

| f                | Frequency                                                        |                         | 32.768             |                  | kHz  |

| CL               | Load capacitance                                                 |                         |                    | 40               | pF   |

| V <sub>OUT</sub> | Output clock voltage, depending on output reference level IO.1P8 |                         | 1.8 <sup>(1)</sup> |                  | V    |

| V <sub>OH</sub>  | Voltage output high                                              | V <sub>OUT</sub> – 0.45 |                    | V <sub>OUT</sub> | V    |

| V <sub>OL</sub>  | Voltage output low                                               | 0                       |                    | 0.45             | V    |

(1) The output voltage depends on output reference level which is IO.1P8.

www.ti.com

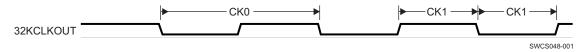

The following table details the output clock timing characteristics. The following figure shows the 32KCLKOUT output clock waveform.

| NAME | PARAMETER                   | DESCRIPTION                              | MIN                                 | ТҮР    | MAX                                 | UNIT   |

|------|-----------------------------|------------------------------------------|-------------------------------------|--------|-------------------------------------|--------|

| CK0  | 1/t <sub>C(32KCLKOUT)</sub> | Frequency                                |                                     | 32.768 |                                     | kHz    |

| CK1  | t <sub>W(32KCLKOUT)</sub>   | Pulse duration,<br>32KCLKOUT low or high | 0.40 ×<br>t <sub>C(32KCLKOUT)</sub> |        | 0.60 ×<br>t <sub>C(32KCLKOUT)</sub> | ns     |

| CK2  | t <sub>R(32KCLKOUT)</sub>   | Rise time, 32KCLKOUT (1)                 |                                     |        | 16                                  | ns     |

| CK3  | t <sub>F(32KCLKOUT)</sub>   | Fall time, 32KCLKOUT (1)                 |                                     |        | 16                                  | ns     |

|      | SSB Phase Noise             | At 1-kHz offset from the carrier         |                                     |        | -110                                | dBc/Hz |

(1) The output capacitive load is equivalent to 30 pF.

Figure 1. 32KCLKOUT Output Clock

## HFCLKOUT OUTPUT CLOCK

The following table summarizes the HFCLKOUT output clock electrical characteristics.

| NAME             | PARAMETER DESCRIPTION                                            | MIN                     | ТҮР                | MAX              | UNIT |

|------------------|------------------------------------------------------------------|-------------------------|--------------------|------------------|------|

| f                | Frequency                                                        |                         | 19.2, 26, or 38.4  |                  | MHz  |

| CL               | Load capacitance                                                 |                         |                    | 30               | pF   |

| V <sub>OUT</sub> | Output clock voltage, depending on output reference level IO.1P8 |                         | 1.8 <sup>(1)</sup> |                  | V    |

| V <sub>OH</sub>  | Voltage output high                                              | V <sub>OUT</sub> – 0.45 |                    | V <sub>OUT</sub> | V    |

| V <sub>OL</sub>  | Voltage output low                                               | 0                       |                    | 0.45             | V    |

#### Table 2. HFCLKOUT Output Clock Electrical Characteristics

(1) The output voltage depends on output reference level which is IO.1P8.

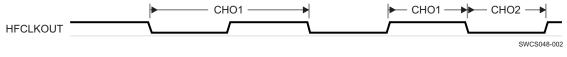

The following table details the HFCLKOUT output clock timing characteristics.

| NAME  | PARAMETER                                     | DESCRIPTION                                    | MIN                               | TYP               | MAX                               | UNIT |

|-------|-----------------------------------------------|------------------------------------------------|-----------------------------------|-------------------|-----------------------------------|------|

| CHO1  | 1/t <sub>C(HFCLKOUT)</sub>                    | Frequency                                      |                                   | 19.2, 26, or 38.4 |                                   | MHz  |

| CHO2  | t <sub>W(HFCLKOUT)</sub>                      | Pulse duration, HFCLKOUT low or high           | 0.4 ×<br>t <sub>C(HFCLKOUT)</sub> |                   | 0.6 ×<br>t <sub>C(HFCLKOUT)</sub> | ns   |

|       | Rise time, HFCLKOUT, low drive <sup>(1)</sup> |                                                |                                   |                   |                                   |      |

|       |                                               | - Load: 5 pF                                   |                                   |                   | 3.8                               |      |

| 01100 |                                               | - Load: 10 pF                                  |                                   |                   | 5.5                               |      |

| CHO3  | <sup>‡</sup> R(HFCLKOUT)                      | Rise time, HFCLKOUT, high drive <sup>(1)</sup> |                                   |                   |                                   | ns   |

|       |                                               | - Load: 10 pF                                  |                                   |                   | 2.9                               |      |

|       |                                               | - Load: 20 pF                                  |                                   |                   | 5.0                               |      |

#### Table 3. HFCLKOUT Output Clock Switching Characteristics

<sup>(1)</sup> Low drive: MISC\_CFG[CLK\_HF\_DRV] = 0 (default) High drive: MISC\_CFG[CLK\_HF\_DRV] = 1

SWCS048F – MARCH 2010 – REVISED MARCH 2012

| NAME | PARAMETER                                     | DESCRIPTION                                    | MIN | ТҮР | MAX | UNIT |

|------|-----------------------------------------------|------------------------------------------------|-----|-----|-----|------|

|      | Fall time, HFCLKOUT, low drive <sup>(1)</sup> |                                                |     |     |     |      |

|      |                                               | - Load: 5 pF                                   |     |     | 3.5 |      |

| CHO4 |                                               | - Load: 10 pF                                  |     |     | 5.1 | ~~~  |

| 0104 | t <sub>F(HFCLKOUT)</sub>                      | Fall time, HFCLKOUT, high drive <sup>(1)</sup> |     |     |     | ns   |

|      |                                               | - Load: 10 pF                                  |     |     | 2.7 |      |

|      |                                               | - Load: 20 pF                                  |     |     | 4.7 |      |

#### Table 3. HFCLKOUT Output Clock Switching Characteristics (continued)

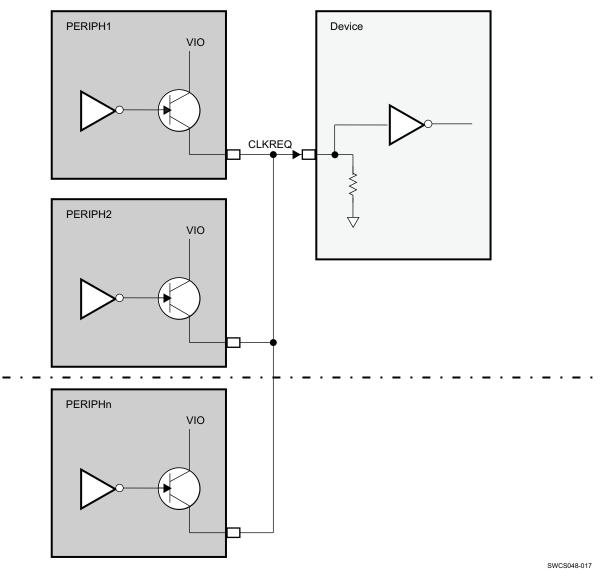

Figure 2 shows the HFCLKOUT output clock waveform.

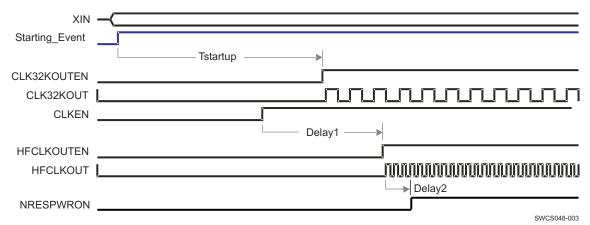

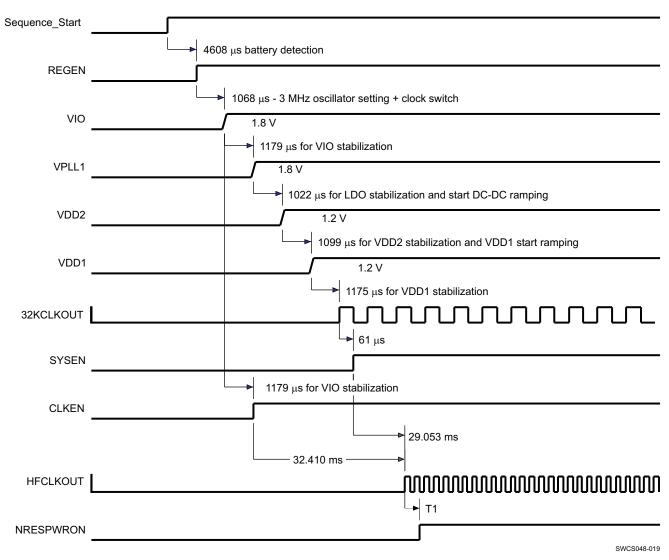

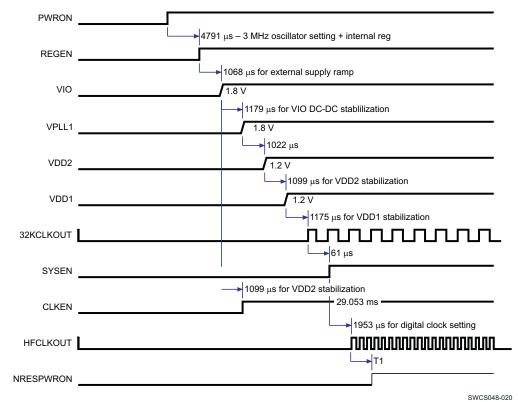

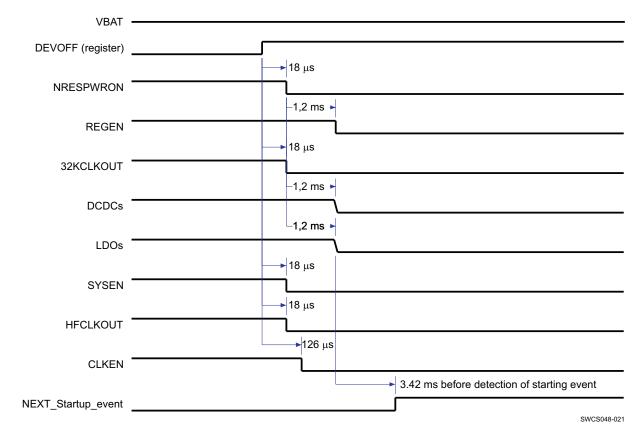

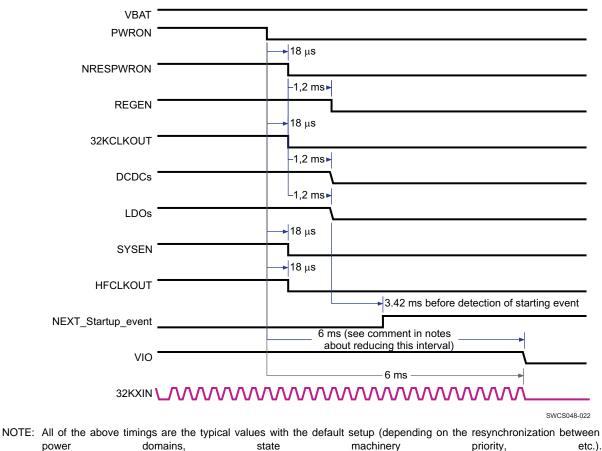

Figure 3 shows the 32KCLKOUT and HFCLKOUT clock stabilization time.

A. Tstartup, Delay1, Delay2, and Delay3 depend on the boot mode (See Power timing chapter).

Figure 3. 32KCLKOUT and HFCLKOUT Clock Stabilization Time

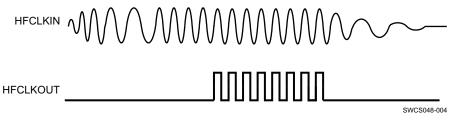

Figure 4. HFCLKOUT Behavior

www.ti.com

## **VDD1 DCDC CONVERTER**

| PARAMETER                                                                                          | COMMENTS                                                                               | MIN | TYP  | MAX  | UNIT  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|------|------|-------|

| Input voltage range                                                                                |                                                                                        | 2.7 | 3.6  | 4.5  | V     |

| Output voltage                                                                                     |                                                                                        | 0.6 |      | 1.45 | V     |

| Output voltage step                                                                                | 0.6 to 1.45 V                                                                          |     | 12.5 |      | mV    |

| Output accuracy <sup>(1)</sup>                                                                     | 0.6 to < 0.8 V                                                                         | -6% |      | 6%   |       |

|                                                                                                    | 0.8 to 1.45 V                                                                          | -5% |      | 5%   |       |

| Switching frequency                                                                                |                                                                                        |     | 3.2  |      | MHz   |

|                                                                                                    | I <sub>O</sub> = 10 mA, sleep                                                          |     | 82%  |      |       |

| Q                                                                                                  | 100 mA < I <sub>O</sub> < 400 mA                                                       |     | 85%  |      |       |

| Conversion efficiency <sup>(2)</sup>                                                               | 400 mA < I <sub>O</sub> < 600 mA                                                       |     | 80%  |      |       |

|                                                                                                    | 600 mA < I <sub>O</sub> < 800 mA                                                       |     | 75%  |      |       |

|                                                                                                    | Active mode<br>Output voltage 0.6 V to 1.45 V<br>for TPS65921B/TPS65921B1              |     |      | 1.2  | A     |

| Output current                                                                                     | Active mode<br>Output Voltage 1.2 V to 1.45 V<br>for TPS65921B1                        |     |      | 1.4  | A     |

|                                                                                                    | Sleep mode                                                                             |     |      | 10   | mA    |

|                                                                                                    | Off at 30°C                                                                            |     |      | 3    |       |

| Ground current (I <sub>Q</sub> )                                                                   | Sleep, unloaded                                                                        |     | 30   | 50   | μA    |

|                                                                                                    | Active, unloaded, not switching                                                        |     |      | 300  |       |

| Short-circuit current                                                                              | V <sub>IN</sub> = V <sub>MAX</sub>                                                     |     | 2.2  |      | А     |

| Load regulation                                                                                    | $0 < I_O < I_{MAX}$                                                                    |     |      | 20   | mV    |

| Transient load regulation at 1.2 $A^{(3)}$                                                         | $I_{O}$ = 10 mA to ( $I_{MAX}/3$ ) + 10 mA,<br>maximum slew rate is $I_{MAX}/3/100$ ns | -65 |      | 50   | mV    |

| Line regulation                                                                                    |                                                                                        |     |      | 10   | mV    |

| Transient line regulation                                                                          | 300 mV_{PP} ac input, 10- $\mu s$ rise and fall time                                   |     |      | 10   | mV    |

| Start-up time                                                                                      |                                                                                        |     | 0.25 | 1    | ms    |

| Recovery time                                                                                      | From sleep to on with constant load                                                    |     | < 10 | 100  | μs    |

| Slew rate (rising or falling) <sup>(4)</sup>                                                       |                                                                                        | 4   | 8    | 16   | mV/µs |

|                                                                                                    | Active (PWM and PSM)                                                                   | -10 |      | 10   | mV    |

| Output ripple                                                                                      | Sleep (PFM)                                                                            | -2% |      | 2%   |       |

| Current limit for PWM/PSM mode<br>switch. PSM is below this limit, and<br>PWM is above this limit. | Active mode                                                                            | 150 |      | 200  | mA    |

| Overshoot                                                                                          | Softstart                                                                              |     |      | 5%   |       |

| Output pulldown resistance                                                                         | In Off mode                                                                            |     | 500  | 700  | Ω     |

(1) Accuracy includes all variations (line and load regulations, line and load transients, temperature, and process). (2) VBAT = 3.6 V, VDD1 = 1.2 V, Fs = 3.2 MHz, L = 1  $\mu$ H, L<sub>DCR</sub> = 100 m $\Omega$ , C = 10  $\mu$ F, ESR = 10 m $\Omega$

For negative transient load, the output voltage must discharge completely and settle to its final value within 100 ms. Transient load is (3) specified at Vout max with a  $\pm$ 50% external capacitor accuracy and includes temperature and procress variation. Load current varies proportional to the output voltage. The slew rate is for increasing and decreasing voltages and the load current is 1.1

(4) Α.

www.ti.com

## **VDD2 DCDC CONVERTER**

| PARAMETER                                                                                          | COMMENTS                                                                               | MIN | ТҮР  | MAX | UNIT  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----|------|-----|-------|

| Input voltage range                                                                                |                                                                                        | 2.7 | 3.6  | 4.5 | V     |

| Output voltage                                                                                     |                                                                                        | 0.6 | 1.0  | 1.5 | V     |

| Output voltage step                                                                                | 0.6 to 1.45 V                                                                          |     | 12.5 |     | mV    |

| Output accuracy <sup>(1)</sup>                                                                     | 0.6 to < 0.8 V                                                                         | -6% |      | 6%  |       |

|                                                                                                    | 0.8 to 1.45 V                                                                          | -5% |      | 5%  |       |

| Switching frequency                                                                                |                                                                                        |     | 3.2  |     | MHz   |

|                                                                                                    | I <sub>O</sub> = 10 mA, sleep                                                          |     | 82%  |     |       |

| Conversion efficiency <sup>(2)</sup>                                                               | 100 mA < I <sub>O</sub> < 300 mA                                                       |     | 85%  |     |       |

|                                                                                                    | 300 mA < I <sub>O</sub> < 500 mA                                                       |     | 80%  |     |       |

|                                                                                                    | Active mode                                                                            |     |      | 600 | mA    |

| Output current                                                                                     | Sleep mode                                                                             |     |      | 10  | mA    |

|                                                                                                    | Off at 30°C                                                                            |     |      | 1   |       |

| Ground current (I <sub>Q</sub> )                                                                   | Sleep, unloaded                                                                        |     | 30   | 50  | μA    |

|                                                                                                    | Active, unloaded, not switching                                                        |     |      | 300 |       |

| Short-circuit current                                                                              | $V_{IN} = V_{MAX}$                                                                     |     | 1.2  |     | А     |

| Load regulation                                                                                    | $0 < I_O < I_{MAX}$                                                                    |     |      | 20  | mV    |

| Transient load regulation <sup>(3)</sup>                                                           | $I_{O}$ = 10 mA to ( $I_{MAX}/3$ ) + 10 mA,<br>maximum slew rate is $I_{MAX}/3/100$ ns | -65 |      | 50  | mV    |

| Line regulation                                                                                    |                                                                                        |     |      | 10  | mV    |

| Transient line regulation                                                                          | 300 mV_{PP} ac input, 10- $\mu s$ rise and fall time                                   |     |      | 10  | mV    |

| Output pulldown resistance                                                                         | In OFF mode                                                                            |     | 500  | 700 | Ω     |

| Start-up time                                                                                      |                                                                                        |     | 0.25 | 1   | ms    |

| Recovery time                                                                                      | From sleep to on with constant load                                                    |     | 25   | 100 | μs    |

| Slew rate (rising or falling) <sup>(4)</sup>                                                       |                                                                                        | 4   | 8    | 16  | mV/µs |

|                                                                                                    | Active (PWM and PSM)                                                                   | -10 |      | 10  | mV    |

| Output ripple                                                                                      | Sleep (PFM)                                                                            | -2% |      | 2%  |       |

| Current limit for PWM/PSM mode<br>switch. PSM is below this limit, and<br>PWM is above this limit. | Active mode                                                                            | 150 |      | 200 | mA    |

| Overshoot                                                                                          | Softstart                                                                              |     |      | 5%  |       |

(1) Accuracy includes all variations (line and load regulations, line and load transients, temperature, and process).

(2)

VBAT = 3.8 V, VDD1 = 1.3 V, Fs = 3.2 MHz, L = 1  $\mu$ H, L<sub>DCR</sub> = 100 mΩ, C = 10  $\mu$ F, ESR = 10 mΩ Output voltage must be able to discharge the load current completely and settle to its final value within 100  $\mu$ s. Load current varies proportional to the output voltage. The slew rate is for increasing and decreasing voltages and the load current is 1.1 (2) (3) (4) Α.

www.ti.com

## **VIO DCDC CONVERTER**

| PARAMETER                                                                                          | COMMENTS                                                                                                 | MIN | ТҮР         | MAX | UNIT  |

|----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|-----|-------------|-----|-------|

| Input voltage range                                                                                |                                                                                                          | 2.7 | 3.6         | 4.5 | V     |

| Output voltage <sup>(1)</sup>                                                                      |                                                                                                          |     | 1.8<br>1.85 |     | V     |

|                                                                                                    | DC accuracy only                                                                                         | -3% |             | 3%  |       |

| Output accuracy                                                                                    | Including all variations (line and load regulations, line and load transients, temperature, and process) | -4% |             | 4%  |       |

| Switching frequency                                                                                |                                                                                                          |     | 3.2         |     | MHz   |

|                                                                                                    | I <sub>O</sub> = 10 mA, sleep                                                                            |     | 85%         |     |       |

| Conversion efficiency <sup>(2)</sup>                                                               | 100 mA < I <sub>O</sub> < 400 mA                                                                         |     | 85%         |     |       |

|                                                                                                    | 400 mA < I <sub>O</sub> < 600 mA                                                                         |     | 80%         |     |       |

| Output ourroat                                                                                     | On mode                                                                                                  |     |             | 700 | mA    |

| Output current                                                                                     | Sleep mode                                                                                               |     |             | 10  | mA    |

|                                                                                                    | Off at 30°C                                                                                              |     |             | 1   |       |

| Ground current (I <sub>Q</sub> )                                                                   | Sleep, unloaded                                                                                          |     | 30          | 50  | μA    |

|                                                                                                    | Active, unloaded, not switching                                                                          |     |             | 300 |       |

| Load regulation                                                                                    | $0 < I_O < I_{MAX}$                                                                                      |     |             | 20  | mV    |

| Line regulation                                                                                    |                                                                                                          |     |             | 10  | mV    |

| Transient load regulation                                                                          | $I_{O}$ = 10 mA to ( $I_{MAX}/3$ ) + 10 mA,<br>maximum slew rate is $I_{MAX}/3/100$ ns                   | -65 |             | 50  | mV    |

| Transient line regulation                                                                          | 300 mV_{PP} ac input, 10- $\mu s$ rise and fall time                                                     |     |             | 10  | mV    |

| Start-up time                                                                                      |                                                                                                          |     | 0.25        | 1   | ms    |

| Recovery time                                                                                      | From sleep to on with constant load                                                                      |     | < 10        | 100 | μs    |

| Slew rate (rising or falling)                                                                      |                                                                                                          | 4   | 8           | 16  | mV/µs |

|                                                                                                    | Active (PWM and PSM)                                                                                     | -10 |             | 10  | mV    |

| Output ripple                                                                                      | Sleep (PFM)                                                                                              | -2% |             | 2%  |       |

| Current limit for PWM/PSM mode<br>switch. PSM is below this limit, and<br>PWM is above this limit. | Active mode                                                                                              | 150 |             | 200 | mA    |

| Overshoot                                                                                          | Softstart                                                                                                |     |             | 5%  |       |

| Output pulldown resistance                                                                         | In Off mode                                                                                              |     | 500         | 700 | Ω     |

(1) This voltage is tuned according to the platform and transient requirements. (2) VBAT = 3.8 V, VIO = 1.8 V, Fs = 3.2 MHz, L = 1  $\mu$ H, LDCR = 100 m $\Omega$ , C = 10  $\mu$ F, ESR = 10 m $\Omega$

SWCS048F-MARCH 2010-REVISED MARCH 2012

## VMMC1 LOW DROPOUT REGULATOR

|                  | PARAMETER                                                                                                                           | TEST CONDITIONS                                                           | MIN                                | TYP                         | MAX                                | UNIT |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|------------------------------------|-----------------------------|------------------------------------|------|

| V <sub>IN</sub>  | Input voltage                                                                                                                       |                                                                           | 2.7                                | 3.6                         | 5.5                                | V    |

| V <sub>OUT</sub> | Output voltage including all<br>variations (line and load<br>regulations, line and load<br>transients, temperature, and<br>process) |                                                                           | 1.7945<br>2.7645<br>2.91<br>3.0555 | 1.85<br>2.85<br>3.0<br>3.15 | 1.9055<br>2.9355<br>3.09<br>3.2445 | V    |

| оит              | Rated output current                                                                                                                | On mode<br>Low-power mode                                                 |                                    |                             | 220<br>5                           | mA   |

|                  | DC load regulation                                                                                                                  | On mode: $0 < I_O < I_{MAX}$                                              |                                    |                             | 20                                 | mV   |

|                  | DC line regulation                                                                                                                  | On mode, $V_{IN} = V_{INmin}$ to $V_{INmax}$<br>at $I_{OUT} = I_{OUTmax}$ |                                    |                             | 3                                  | mV   |

|                  | Turn-on time                                                                                                                        | $I_{OUT}$ = 0, $C_L$ = 1 $\mu F$ (within 10% of $V_{OUT})$                |                                    |                             | 100                                | μs   |

|                  | Wake-up time                                                                                                                        | Full load capability                                                      |                                    |                             | 10                                 | μs   |

|                  |                                                                                                                                     | f < 10 kHz                                                                | 50                                 |                             |                                    |      |

|                  | Pipple rejection                                                                                                                    | 10 kHz < f < 100 kHz                                                      | 40                                 |                             |                                    | dB   |

|                  | Ripple rejection                                                                                                                    | f = 1 MHz                                                                 | 25                                 |                             |                                    | dВ   |

|                  |                                                                                                                                     | $V_{IN} = V_{OUT} + 1 V$ , $I_O = I_{MAX}$                                |                                    |                             |                                    |      |

|                  |                                                                                                                                     | On mode, $I_{OUT} = 0$                                                    |                                    |                             | 70                                 |      |

|                  |                                                                                                                                     | On mode, $I_{OUT} = I_{OUTmax}$                                           |                                    |                             | 290                                |      |

|                  | Ground current                                                                                                                      | Low-power mode, $I_{OUT} = 0$                                             |                                    |                             | 17                                 | μΑ   |

|                  |                                                                                                                                     | Low-power mode, $I_{OUT} = 5 \text{ mA}$                                  |                                    |                             | 20                                 |      |

|                  |                                                                                                                                     | Off mode at 55°C                                                          |                                    |                             | 1                                  |      |

| V <sub>DO</sub>  | Dropout voltage <sup>(1)</sup>                                                                                                      | On mode, $I_{OUT} = I_{OUTmax}$                                           |                                    |                             | 250                                | mV   |

|                  | Transient load regulation <sup>(2)</sup>                                                                                            | I <sub>LOAD</sub> : I <sub>MIN</sub> – I <sub>MAX</sub><br>Slew: 40 mA/µs | -40                                |                             | 40                                 | mV   |

|                  | Transient line regulation                                                                                                           | V <sub>IN</sub> drops 500 mV<br>Slew: 40 mV/µs                            |                                    |                             | 10                                 | mV   |

|                  | Overshoot                                                                                                                           | Softstart                                                                 |                                    |                             | 3%                                 |      |

|                  | Pulldownresistance                                                                                                                  | Default in off mode                                                       | 250                                | 320                         | 450                                | Ω    |

For nominal output voltage

Transient load regulation is always included in the overall accuracy of the selected output voltage option. For voltage levels that have a tighter output voltage specification than the transient load regulation, follow the output voltage specification.

www.ti.com

**ISTRUMENTS**

ÈXAS

## **VDAC LOW DROPOUT REGULATOR**

|                  | PARAMETER                                                                                                                           | TEST CONDITIONS                                                                                                                                    | MIN                     | TYP              | MAX                         | UNIT   |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|------------------|-----------------------------|--------|

| V <sub>IN</sub>  | Input voltage                                                                                                                       |                                                                                                                                                    | 2.7                     | 3.6              | 4.5                         | V      |

| V <sub>OUT</sub> | Output voltage including all<br>variations (line and load<br>regulations, line and load<br>transients, temperature, and<br>process) |                                                                                                                                                    | 1.164<br>1.261<br>1.746 | 12<br>1.3<br>1.8 | 1.236<br>1.339<br>1.854     | V      |

| I <sub>OUT</sub> | Rated output current                                                                                                                | On mode<br>Low-power mode                                                                                                                          |                         |                  | 70<br>5                     | mA     |

|                  | DC load regulation                                                                                                                  | On mode: $0 < I_O < I_{MAX}$                                                                                                                       |                         |                  | 20                          | mV     |

|                  | DC line regulation                                                                                                                  | On mode, $V_{IN} = V_{INmin}$ to $V_{INmax}$<br>at $I_{OUT} = I_{OUTmax}$                                                                          |                         |                  | 3                           | mV     |

|                  | Turn-on time                                                                                                                        | $I_{OUT}$ = 0, $C_L$ = 1 $\mu F$ (within 10% of $V_{OUT})$                                                                                         |                         |                  | 100                         | μs     |

|                  | Wake-up time                                                                                                                        | Full load capability                                                                                                                               |                         |                  | 10                          | μs     |

|                  | Ripple rejection                                                                                                                    | f < 20 kHz<br>20 kHz < f < 100 kHz<br>f = 1 MHz<br>V <sub>IN</sub> = V <sub>OUT</sub> + 1 V, I <sub>O</sub> = I <sub>MAX</sub>                     | 65<br>45<br>40          |                  |                             | dB     |

|                  | Output noise                                                                                                                        | 200 Hz < f < 5 kHz<br>5 kHz < f < 400 kHz<br>400 kHz < f < 10 MHz                                                                                  |                         |                  | 400<br>125<br>50            | nV/√Hz |

|                  | Ground current                                                                                                                      | On mode, $I_{OUT} = 0$<br>On mode, $I_{OUT} = I_{OUTmax}$<br>Low-power mode, $I_{OUT} = 0$<br>Low-power mode, $I_{OUT} = 1$ mA<br>Off mode at 55°C |                         |                  | 150<br>350<br>15<br>25<br>1 | μΑ     |

| V <sub>DO</sub>  | Dropout voltage <sup>(1)</sup>                                                                                                      | On mode, $I_{OUT} = I_{OUTmax}$                                                                                                                    |                         |                  | 250                         | mV     |

| V DO             | Transient load regulation <sup>(2)</sup>                                                                                            | I <sub>LOAD</sub> : Ι <sub>MIN</sub> – Ι <sub>MAX</sub><br>Slew: 60 mA/μs                                                                          | -40                     |                  | 40                          | mV     |

|                  | Transient line regulation                                                                                                           | V <sub>IN</sub> drops 500 mV<br>Slew: 40 mV/µs                                                                                                     |                         |                  | 10                          | mV     |

|                  | Overshoot                                                                                                                           | Softstart                                                                                                                                          |                         |                  | 3%                          |        |

|                  | Pull down resistance                                                                                                                | Default in off mode                                                                                                                                | 250                     | 320              | 450                         | Ω      |

(1) (2)

For nominal output voltage Transient load regulation is always included in the overall accuracy of the selected output voltage option. For voltage levels that have a tighter output voltage specification than the transient load regulation, follow the output voltage specification.

SWCS048F-MARCH 2010-REVISED MARCH 2012

## **VAUX2 LOW DROPOUT REGULATOR**

|                  | PARAMETER                                                                                                                           | TEST CONDITIONS                                                           | MIN | TYP                                                                              | MAX | UNIT |

|------------------|-------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------|-----|------|

| V <sub>IN</sub>  | Input voltage                                                                                                                       |                                                                           | 2.7 | 3.6                                                                              | 4.5 | V    |

| V <sub>OUT</sub> | Output voltage including all<br>variations (line and load<br>regulations, line and load<br>transients, temperature, and<br>process) |                                                                           | -3% | 1.3<br>1.5<br>1.7<br>1.8<br>1.9<br>2.0<br>2.1<br>2.2<br>2.3<br>2.4<br>2.5<br>2.8 | +3% | V    |

| L                | Rated output current                                                                                                                | On mode                                                                   |     |                                                                                  | 100 | mA   |