## LTC5800-IPR

## SmartMesh IP Network Manager 2.4GHz 802.15.4e Wireless Manager

## **NETWORK FEATURES**

- Complete Radio Transceiver, Embedded Processor, and Networking Software for Forming a Self-Healing Mesh Network

- SmartMesh<sup>®</sup> Networks Incorporate:

- Time Synchronized Network-Wide Scheduling

- Per-Transmission Frequency-Hopping

- Redundant Spatially Diverse Topologies

- Network-Wide Reliability and Power Optimization

- NIST Certified Security

- SmartMesh Networks Deliver:

- >99.999% Network Reliability Achieved in the Most Challenging RF Environments

- Sub 50µA Routing Nodes

- Compliant to 6LoWPAN Internet Protocol (IP) and IEEE 802.15.4e Standards

## LTC5800-IPR FEATURES

- Provides Network Management Functions and Security Capabilities

- Manages Networks of Up to 32 Nodes (LTC5800-IPRA) or Up to 100 nodes (LTC5800-IPRB)

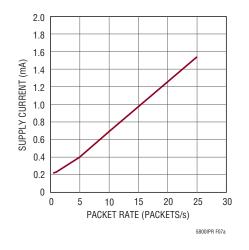

- Sub 1mA Average Current Consumption Enables Battery-Powered Network Management

- PCB Module Versions Available (LTP™5901/2-IPR) with RF Modular Certifications

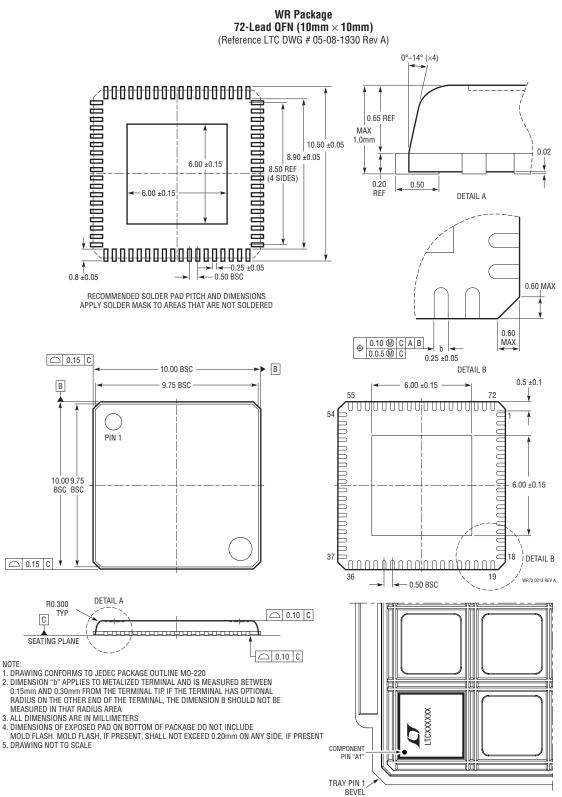

- 72-Lead 10mm × 10mm QFN Package

## DESCRIPTION

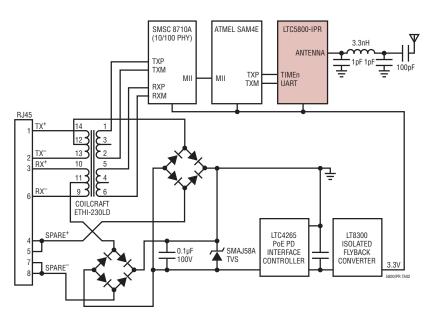

SmartMesh IP<sup>™</sup> wireless sensor networks are self managing, low power internet protocol (IP) networks built from wireless nodes called motes. The LTC®5800-IPR is the IP Manager-on-Chip<sup>™</sup> in the Eterna®\* family of IEEE 802.15.4e system-on-chip (SoC) solutions, featuring a highly integrated, low power radio design by Dust Networks® as well as an ARM Cortex-M3 32-bit microprocessor running Dust's embedded SmartMesh IP networking software.

Based on the IETF 6LoWPAN and IEEE-802.15.4e standards, the LTC5800-IPR SoC runs SmartMesh IP network management software to monitor and manage network performance and provide a data ingress/egress point via a UART interface. The SmartMesh IP software provided with the LTC5800-IPR is fully tested and validated, and is readily configured via a software Application Programming Interface. With Dust's time-synchronized SmartMesh IP networks, all motes in the network may route, source or terminate data, while providing many years of batterypowered operation.

SmartMesh IP motes deliver a highly flexible network with proven reliability and low power performance in an easy-to-integrate platform.

**Δ7**, LT, LTC, LTM, Linear Technology, the Linear logo, Dust, Dust Networks, SmartMesh and Eterna are registered trademarks and LTP, the Dust Networks logo SmartMesh IP and Manageron-Chip are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners. Protected by U.S. Patents, including 7375594, 7420980, 7529217, 7791419, 7881239, 7898322, 8222965.

Eterna is Dust Networks' low power radio SoC architecture.

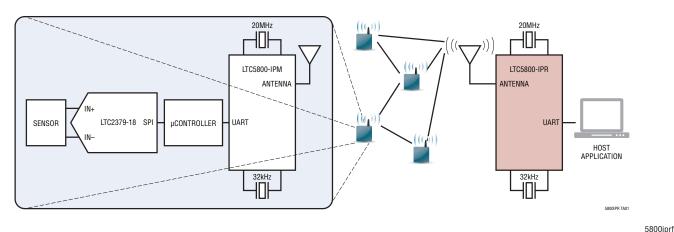

## TYPICAL APPLICATION

## TABLE OF CONTENTS

| Network Features                    | . 1 |

|-------------------------------------|-----|

| LTC5800-IPR Features                | . 1 |

| Typical Application                 | . 1 |

| Description                         | . 1 |

| SmartMesh Network OVerview          |     |

| Absolute Maximum Ratings            | . 4 |

| Order Information                   | . 4 |

| Recommended Operating Conditions    | . 4 |

| Pin Configuration                   | . 4 |

| DC Characteristics                  |     |

| Radio Specifications                | . 5 |

| Radio Receiver Characteristics      | . 6 |

| Radio Transmitter Characteristics   | . 6 |

| Digital I/O Characteristics         | . 7 |

| Temperature Sensor Characteristics  |     |

| System Characteristics              |     |

| UART AC Characteristics             | . 8 |

| TIMEN AC Characteristics            | . 9 |

| RADIO_INHIBIT AC Characteristics    | . 9 |

| Flash AC Characteristics            | 10  |

| Flash SPI Slave AC Characteristics  | 10  |

| External Bus AC Characteristics     | 11  |

| Typical Performance Characteristics |     |

| Pin Functions                       |     |

|                                     |     |

| Operation                           |    |

|-------------------------------------|----|

| Power Supply                        | 23 |

| Supply Monitoring And Reset         |    |

| Precision Timing                    |    |

| Application Time Synchronization    | 24 |

| Time References                     |    |

| Radio                               | 25 |

| UARTS                               | 25 |

| CLI UART                            | 27 |

| Autonomous Mac                      | 27 |

| Security                            |    |

| Temperature Sensor                  |    |

| Radio Inhibit                       |    |

| Flash Programming                   |    |

| Flash Data Retention                |    |

| Networking                          | 29 |

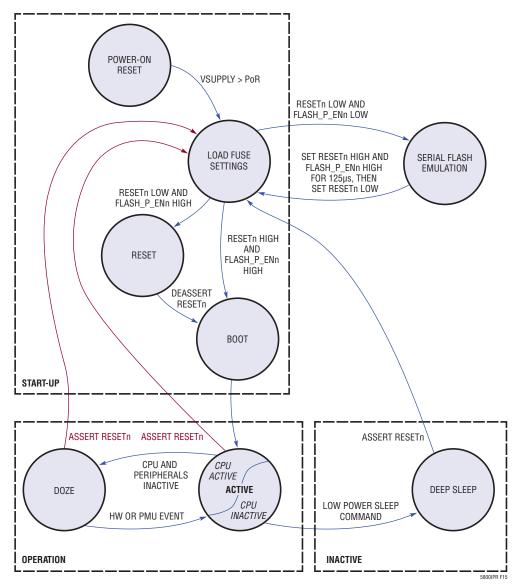

| State Diagram                       |    |

| Applications Information            |    |

| Regulatory And Standards Compliance | 33 |

| Soldering Information               | 33 |

| Related Documentation               |    |

| Package Description                 | 35 |

| Typical Application                 |    |

| Related Parts                       |    |

## SMARTMESH NETWORK OVERVIEW

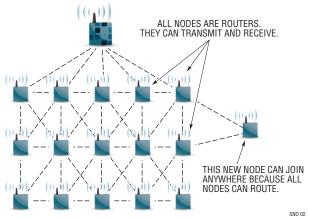

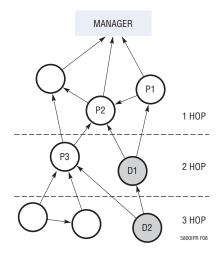

A SmartMesh network consists of a self-forming multi-hop, mesh of nodes, known as motes, which collect and relay data, and a network manager that monitors and manages network performance and security, and exchanges data with a host application.

SmartMesh networks communicate using a time slotted channel hopping (TSCH) link layer, pioneered by Dust Networks. In a TSCH network, all motes in the network are synchronized to within less than a millisecond. Time in the network is organized into time slots, which enable collision-free packet exchange and per-transmission channel-hopping. In a SmartMesh network, every device has one or more parents (e.g., mote 3 has motes 1 and 2 as parents) that provide redundant paths to overcome communications interruption due to interference, physical obstruction or multi-path fading. If a packet transmission fails on one path, the next retransmission may try on a different path and different RF channel.

A network begins to form when the network manager instructs its on-board access point (AP) radio to begin sending advertisements—packets that contain information that enables a device to synchronize to the network and request to join. This message exchange is part of the security handshake that establishes encrypted communications between the manager or application, and mote. Once motes have joined the network, they maintain synchronization through time corrections when a packet is acknowledged.

An ongoing discovery process ensures that the network continually discovers new paths as the RF conditions change. In addition, each mote in the network tracks performance statistics (e.g., quality of used paths, and lists of potential paths) and periodically sends that information to the network manager in packets called health reports. The network manager uses health reports to continually optimize the network to maintain >99.999% data reliability even in the most challenging RF environments.

The use of TSCH allows SmartMesh devices to sleep inbetween scheduled communications and draw very little power in this state. Motes are only active in time slots where they are scheduled to transmit or receive, typically resulting in a duty cycle of <1%. The optimization software in the Network Manager coordinates this schedule automatically. When combined with the Eterna low power radio, every mote in a SmartMesh network—even busy routing ones—can run on batteries for years. By default, all motes in a network are capable of routing traffic from other motes, which simplifies installation by avoiding the complexity of having distinct routers vs non-routing end nodes. Motes may be configured as non-routing to further reduce that particular mote's power consumption and to support a wide variety of network topologies.

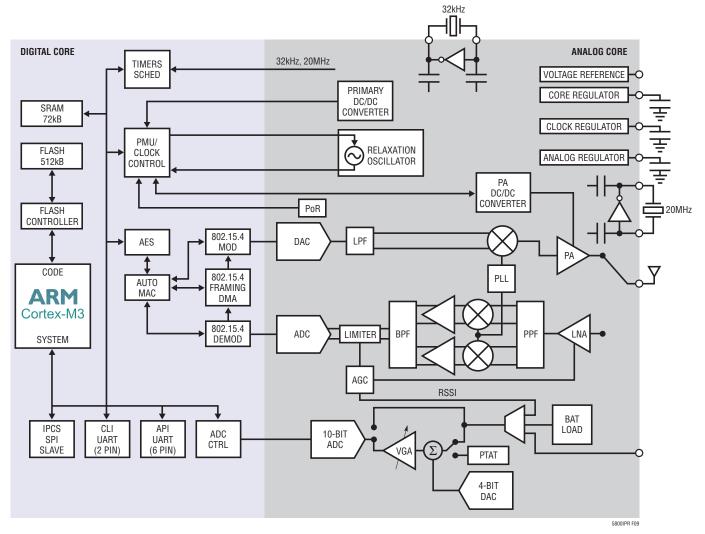

At the heart of SmartMesh motes and network managers is the Eterna IEEE 802.15.4e system-on-chip (SoC), featuring Dust Networks' highly integrated, low power radio design, plus an ARM Cortex-M3 32-bit microprocessor running SmartMesh networking software. The SmartMesh networking software comes fully compiled yet is configurable via a rich set of application programming interfaces (APIs) which allows a host application to interact with the network, e.g., to transfer information to a device, to configure data publishing rates on one or more motes, or to monitor network state or performance metrics. Data publishing can be uniform or different for each device, with motes being able to publish infrequently or faster than once per second as needed.

## ABSOLUTE MAXIMUM RATINGS

(Note 1)

| Supply Voltage on VSUPPLY                    | 3.76V     |

|----------------------------------------------|-----------|

| Input Voltage on AI_0/1/2/3 Inputs           | 1.80V     |

| Voltage on Any Digital I/O pin0.3V to VSUPPL | _Y + 0.3V |

| Input RF Level                               | 10dBm     |

| Storage Temperature Range (Note 3) –55°C     | to 125°C  |

| Junction Temperature (Note 3)                | 125°C     |

| Operating Temperature Range40°C              | C to 85°C |

CAUTION: This part is sensitive to electrostatic discharge (ESD). It is very important that proper ESD precautions be observed when handling the LTC5800-IPR.

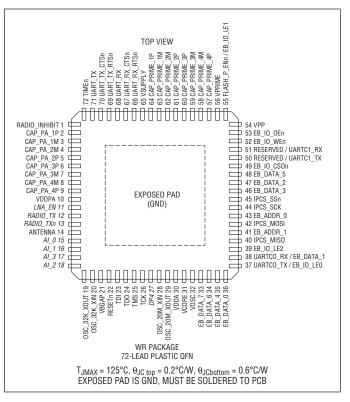

### PIN CONFIGURATION

Pin functions shown in italics are currently not supported in software.

## ORDER INFORMATION

| LEAD FREE FINISH    | PART MARKING   | PACKAGE DESCRIPTION                                      | SPECIFIED TEMPERATURE<br>RANGE |

|---------------------|----------------|----------------------------------------------------------|--------------------------------|

| LTC5800IWR-IPRA#PBF | LTC5800WR-IPRA | 72-Lead (10mm $\times$ 10mm $\times$ 0.85mm) Plastic QFN | –40°C to 85°C                  |

| LTC5800IWR-IPRB#PBF | LTC5800WR-IPRB | 72-Lead (10mm $\times$ 10mm $\times$ 0.85mm) Plastic QFN | –40°C to 85°C                  |

Consult LTC Marketing for parts specified with wider operating temperature ranges. For a description of the dash options see the IP Manager Options section.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

This product is only offered in trays. For more information go to: http://www.linear.com/packaging/

## **RECOMMENDED OPERATING CONDITIONS** The • denotes the specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. VSUPPLY = 3.6V unless otherwise noted.

| SYMBOL  | PARAMETER                                        | CONDITIONS                                    |   | MIN | ТҮР | MAX  | UNITS  |

|---------|--------------------------------------------------|-----------------------------------------------|---|-----|-----|------|--------|

| VSUPPLY | Supply Voltage                                   | Including Noise and Load Regulation           |   | 2.1 |     | 3.76 | V      |

|         | Supply Noise                                     | Requires Recommended RLC Filter, 50Hz to 2MHz |   |     |     | 250  | mV     |

|         | Operating Relative Humidity                      | Non-Condensing                                |   | 10  |     | 90   | % RH   |

|         | Temperature Ramp Rate While Operating in Network |                                               | • | -8  |     | 8    | °C/Min |

# **DC CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted.

| OPERATION/STATE                        | CONDITIONS                                                                                                                                                           | MIN | ТҮР        | MAX | UNITS    |

|----------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|------------|-----|----------|

| Power-On Reset                         | During Power-On Reset, Maximum 750µs + VSUPPLY Rise Time from 1V to 1.9V                                                                                             |     | 12         |     | mA       |

| Doze                                   | RAM On, ARM Cortex-M3, Flash, Radio, and Peripherals Off, All Data and State Retained, 32.768kHz Reference Active                                                    |     | 1.2        |     | μA       |

| Deep Sleep                             | RAM On, ARM Cortex-M3, Flash, Radio, and Peripherals Off, All Data and State Retained, 32.768kHz Reference Inactive                                                  |     | 0.8        |     | μA       |

| In-Circuit Programming                 | RESETn and FLASH_P_ENn Asserted, IPCS_SCK at 8MHz                                                                                                                    |     | 20         |     | mA       |

| Peak Operating Current<br>8dBm<br>0dBm | System Operating at 14.7MHz, Radio Transmitting, During Flash<br>Write. Maximum Duration 4.33ms                                                                      |     | 30<br>26   |     | mA<br>mA |

| Active                                 | ARM Cortex M3, RAM and Flash Operating, Radio and All Other Peripherals Off. Clock Frequency of CPU and Peripherals Set to $7.3728$ MHz, V <sub>CORE</sub> = $1.2$ V |     | 1.3        |     | mA       |

| Flash Write                            | Single Bank Flash Write                                                                                                                                              |     | 3.7        |     | mA       |

| Flash Erase                            | Single Bank Page or Mass Erase                                                                                                                                       |     | 2.5        |     | mA       |

| Radio Tx<br>OdBm<br>8dBm               | Current With Autonomous MAC Managing Radio Operation,<br>CPU Inactive. Clock Frequency of CPU and Peripherals Set to<br>7.3728MHz.                                   |     | 5.4<br>9.7 |     | mA<br>mA |

| Radio Rx                               | Current With Autonomous MAC Managing Radio Operation,<br>CPU Inactive. Clock Frequency of CPU and Peripherals Set to<br>7.3728MHz.                                   |     | 4.5        |     | mA       |

## **RADIO SPECIFICATIONS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted.

| PARAMETER                                         | CONDITIONS                                                              |   | MIN    | ТҮР                | MAX    | UNITS       |

|---------------------------------------------------|-------------------------------------------------------------------------|---|--------|--------------------|--------|-------------|

| Frequency Band                                    |                                                                         | • | 2.4000 |                    | 2.4835 | GHz         |

| Number of Channels                                |                                                                         | • |        | 15                 |        |             |

| Channel Separation                                |                                                                         | • |        | 5                  |        | MHz         |

| Channel Center Frequency                          | Where k = 11 to 25, as Defined by IEEE.802.4.15                         | • | 240    | 5 + 5 •(k ·        | - 11)  | MHz         |

| Modulation                                        | IEEE 802.15.4 Direct Sequence Spread Spectrum (DSSS)                    |   |        |                    |        |             |

| Raw Data Rate                                     |                                                                         | • |        | 250                |        | kbps        |

| Antenna Pin ESD Protection                        | HBM Per JEDEC JESD22-A114F                                              |   |        | ±1000              |        | V           |

| Range (Note 4)<br>Indoor<br>Outdoor<br>Free Space | 25°C, 50% RH, 2dBi Omni-Directional Antenna, Antenna 2m<br>Above Ground |   |        | 100<br>300<br>1200 |        | m<br>m<br>m |

**RADIO RECEIVER CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted.

| PARAMETER                                                | CONDITIONS                                                                                                     | MIN | ТҮР        | MAX | UNITS |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------------------------|-----|------------|-----|-------|

| Receiver Sensitivity                                     | Packet Error Rate (PER) = 1% (Note 5)                                                                          |     | -93        |     | dBm   |

| Receiver Sensitivity                                     | PER = 50%                                                                                                      |     | -95        |     | dBm   |

| Saturation                                               | Maximum Input Level the Receiver Will Properly Receive Packets                                                 |     | 0          |     | dBm   |

| Adjacent Channel Rejection (High Side)                   | Desired Signal at -82dBm, Adjacent Modulated Channel 5MHz<br>Above the Desired Signal, PER = 1% (Note 5)       |     | 22         |     | dBc   |

| Adjacent Channel Rejection (Low Side)                    | Desired Signal at –82dBm, Adjacent Modulated Channel 5MHz<br>Below the Desired Signal, PER = 1% (Note 5)       |     | 19         |     | dBc   |

| Alternate Channel Rejection (High Side)                  | Desired Signal at -82dBm, Alternate Modulated Channel 10MHz<br>Above the Desired Signal, PER = 1% (Note 5)     |     | 40         |     | dBc   |

| Alternate Channel Rejection (Low Side)                   | Desired Signal at –82dBm, Alternate Modulated Channel 10MHz<br>Below the Desired Signal, PER = 1% (Note 5)     |     | 36         |     | dBc   |

| Second Alternate Channel Rejection                       | Desired Signal at –82dBm, Second Alternate Modulated Channel<br>Either 15MHz Above or Below, PER = 1% (Note 5) |     | 42         |     | dBc   |

| Co-Channel Rejection                                     | Desired Signal at -82dBm, Undesired Signal is an 802.15.4<br>Modulated Signal at the Same Frequency, PER = 1%  |     | -6         |     | dBc   |

| LO Feed Through                                          |                                                                                                                |     | -55        |     | dBm   |

| Frequency Error Tolerance (Note 6)                       |                                                                                                                |     | ±50        |     | ppm   |

| Symbol Error Tolerance                                   |                                                                                                                |     | ±50        |     | ppm   |

| Received Signal Strength Indicator (RSSI)<br>Input Range |                                                                                                                |     | -90 to -1( | )   | dBm   |

| RSSI Accuracy                                            |                                                                                                                |     | ±6         |     | dB    |

| RSSI Resolution                                          |                                                                                                                |     | 1          |     | dB    |

## **RADIO TRANSMITTER CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted.

| PARAMETER                                                                                                                                        | CONDITIONS                                                                                                                                                                                                                                      |  | MIN | ТҮР                              | MAX | UNITS                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|-----|----------------------------------|-----|---------------------------------|

| Output Power<br>High Calibrated Setting<br>Low Calibrated Setting                                                                                | Delivered to a 50 $\Omega$ load                                                                                                                                                                                                                 |  |     | 8<br>0                           |     | dBm<br>dBm                      |

| Spurious Emissions                                                                                                                               | $\begin{array}{c} \mbox{Conducted Measurement with a 50} \Omega \mbox{Single-Ended Load,} \\ \mbox{8dBm Output Power. All Measurements Made with Max Hold.} \\ \mbox{RF Implementation Per Eterna Reference Design} \end{array}$                |  |     |                                  |     |                                 |

| 30MHz to 1000 MHz<br>1GHz to 12.75GHz<br>2.4GHz ISM Upper Band Edge (Peak)<br>2.4GHz ISM Upper Band Edge (Average)<br>2.4GHz ISM Lower Band Edge | RBW = 120kHz, VBW = 100Hz<br>RBW = 1MHz, VBW = 3MHz<br>RBW = 1MHz, VBW = 3MHz<br>RBW = 1MHz, VBW = 30Hz<br>RBW = 100kHz, VBW = 10Hz<br>RBW = 100kHz, VBW = 100kHz                                                                               |  |     | <-70<br>-45<br>-37<br>-49<br>-45 |     | dBm<br>dBm<br>dBm<br>dBm<br>dBc |

| Harmonic Emissions<br>2nd Harmonic<br>3rd Harmonic                                                                                               | $\begin{array}{l} \mbox{Conducted Measurement Delivered to a 50} \Omega \mbox{Load}, \\ \mbox{Resolution Bandwidth} = 1 \mbox{MHz}, \mbox{Video Bandwidth} = 1 \mbox{MHz}. \\ \mbox{RF Implementation Per Eterna Reference Design} \end{array}$ |  |     | -50<br>-45                       |     | dBm<br>dBm                      |

**DIGITAL I/O CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted.

| SYMBOL          | PARAMETER                    | CONDITIONS (Note 7)                               |   | MIN           | TYP MAX       | UNITS |

|-----------------|------------------------------|---------------------------------------------------|---|---------------|---------------|-------|

| V <sub>IL</sub> | Low Level Input Voltage      |                                                   | • | -0.3          | 0.6           | V     |

| V <sub>IH</sub> | High Level Input Voltage     | (Note 8)                                          | • | VSUPPLY – 0.3 | VSUPPLY + 0.3 | V     |

| V <sub>OL</sub> | Low Level Output Voltage     | Type 1, I <sub>OL(MAX)</sub> = 1.2mA              | • |               | 0.4           | V     |

| V <sub>OH</sub> | High Level Output Voltage    | Type 1, I <sub>OH(MAX)</sub> = -0.8mA             | • | VSUPPLY – 0.3 | VSUPPLY + 0.3 | V     |

| V <sub>OL</sub> | Low Level Output Voltage     | Type 2, Low Drive, I <sub>OL(MAX)</sub> = 2.2mA   | • |               | 0.4           | V     |

| V <sub>OH</sub> | High Level Output Voltage    | Type 2, Low Drive, I <sub>OH(MAX)</sub> = -1.6mA  | • | VSUPPLY – 0.3 | VSUPPLY + 0.3 | V     |

| V <sub>OL</sub> | Low Level Output Voltage     | Type 2, High Drive, I <sub>OL(MAX)</sub> = 4.5mA  | • |               | 0.4           | V     |

| V <sub>OH</sub> | High Level Output Voltage    | Type 2, High Drive, I <sub>OH(MAX)</sub> = -3.2mA | • | VSUPPLY – 0.3 | VSUPPLY + 0.3 | V     |

|                 | Input Leakage Current        | Input Driven to VSUPPLY or GND                    |   |               | 50            | nA    |

|                 | Pull-Up/Pull-Down Resistance |                                                   |   |               | 50            | kΩ    |

# **TEMPERATURE SENSOR CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted.

| PARAMETER   | CONDITIONS                       | MIN | ТҮР    | MAX | UNITS |

|-------------|----------------------------------|-----|--------|-----|-------|

| Offset      | Temperature Offset Error at 25°C |     | ±0.25  |     | °C    |

| Slope Error |                                  |     | ±0.033 |     | °C/°C |

## **SYSTEM CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted.

| SYMBOL           | PARAMETER                        | CONDITIONS                                                                  |   | MIN | ТҮР | MAX | UNITS |

|------------------|----------------------------------|-----------------------------------------------------------------------------|---|-----|-----|-----|-------|

|                  | Doze to Active State Transition  |                                                                             |   |     | 5   |     | μs    |

|                  | Doze to Radio Tx or Rx           |                                                                             |   |     | 1.2 |     | ms    |

| Q <sub>CCA</sub> | Charge to Sample RF Channel RSSI | Charge Consumed Starting from Doze State and Completing an RSSI Measurement |   |     | 4   |     | μC    |

| Q <sub>MAX</sub> | Largest Atomic Charge Operation  | Flash Erase, 21ms Max Duration                                              | • |     |     | 200 | μC    |

|                  | RESETn Pulse Width               |                                                                             | • | 125 |     |     | μs    |

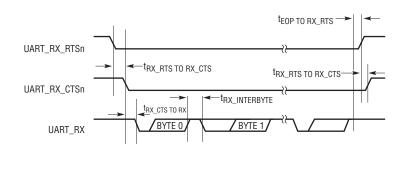

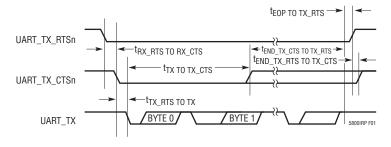

## **UART AC CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted. (Note 13)

| SYMBOL                            | PARAMETER                                                                                                              | CONDITIONS                                                                                |   | MIN | ТҮР | MAX | UNITS      |

|-----------------------------------|------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------|---|-----|-----|-----|------------|

|                                   | Permitted Rx Baud Rate Error                                                                                           | Both Application Programming<br>Interface (API) and Command Line<br>Interface (CLI) UARTs |   | -2  |     | 2   | %          |

|                                   | Generated Tx Baud Rate Error                                                                                           | Both API and CLI UARTs                                                                    |   | -1  |     | 1   | %          |

| t <sub>RX_RTS</sub> to RX_CTS     | Assertion of UART_RX_RTSn to Assertion<br>of UART_RX_CTSn, or Negation of UART_<br>RX_RTSn to Negation of UART_RX_CTSn |                                                                                           | • | 0   |     | 2   | ms         |

| t <sub>CTS_R to RX</sub>          | Assertion of UART_RX_CTSn to Start of Byte                                                                             |                                                                                           | • | 0   |     | 20  | ms         |

| t <sub>EOP to RX_RTS</sub>        | End of Packet (End of the Last Stop Bit) to Negation of UART_RX_RTSn                                                   |                                                                                           | • | 0   |     | 22  | ms         |

| t <sub>BEG_TX_RTS</sub> to TX_CTS | Assertion of UART_TX_RTSn to Assertion of UART_TX_CTSn                                                                 |                                                                                           |   | 0   |     | 22  | ms         |

| tend_tx_rts to tx_cts             | Negation of UART_TX_RTSn to Negation of UART_TX_CTSn                                                                   | Mode 2 Only                                                                               |   |     |     | 22  | ms         |

| tend_tx_cts to tx_rts             | Negation of UART_TX_CTSn to Negation of UART_TX_RTSn                                                                   | Mode 4 Only                                                                               |   | 2   |     |     | Bit Period |

| t <sub>TX_CTS to TX</sub>         | Assertion of UART_TX_CTSn to Start of Byte                                                                             |                                                                                           | • | 0   |     | 2   | Bit Period |

| teop to TX_RTS                    | End of Packet (End of the Last Stop Bit) to Negation of UART_TX_RTSn                                                   |                                                                                           |   | 0   |     | 1   | Bit Period |

| t <sub>RX_INTERBYTE</sub>         | Receive Inter-Byte Delay                                                                                               |                                                                                           |   |     |     | 100 | ms         |

| t <sub>TX to TX_CTS</sub>         | Start of Byte to Negation of<br>UART_TX_CTSn                                                                           |                                                                                           | • | 0   |     |     | ns         |

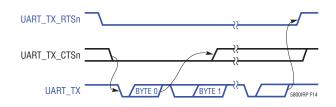

#### Figure 1. API UART Timing

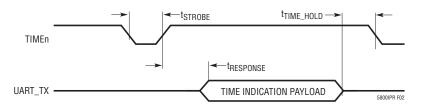

## **TIMEN AC CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted. (Note 13)

| SYMBOL                 | PARAMETER                                                                     | CONDITIONS |   | MIN | ТҮР | MAX | UNITS |

|------------------------|-------------------------------------------------------------------------------|------------|---|-----|-----|-----|-------|

| t <sub>STROBE</sub>    | TIMEn Signal Strobe Width                                                     | •          | • | 125 |     |     | μs    |

| t <sub>response</sub>  | Delay from Rising Edge of TIMEn to the Start of Time Packet on API UART       |            | • | 0   |     | 100 | ms    |

| t <sub>TIME_HOLD</sub> | Delay from End of Time Packet on API UART to Falling Edge of Subsequent TIMEn |            | • | 0   |     |     | ns    |

|                        | Timestamp Resolution (Note 9)                                                 | •          | • |     | 1   |     | μs    |

|                        | Network-Wide Time Accuracy (Note 10)                                          | •          | • |     | ±5  |     | μs    |

Figure 2. Timestamp Timing

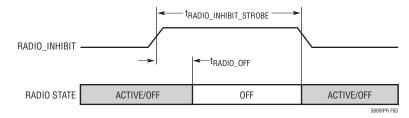

## **RADIO\_INHIBIT AC CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted. (Note 13)

| SYMBOL                            | PARAMETER                                                    | CONDITIONS |   | MIN | ТҮР | MAX | UNITS |

|-----------------------------------|--------------------------------------------------------------|------------|---|-----|-----|-----|-------|

| t <sub>RADIO_OFF</sub>            | Delay from Rising Edge of<br>RADIO_INHIBIT to Radio Disabled | •          | • |     |     | 20  | ms    |

| t <sub>RADIO_INHIBIT_STROBE</sub> | Maximum RADIO_INHIBIT Strobe Width                           |            | • |     |     | 2   | S     |

Figure 3. RADIO\_INHIBIT Timing

# **FLASH AC CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted. (Note 13)

| SYMBOL                  | PARAMETER                                | CONDITIONS            |   | MIN            | ТҮР | MAX | UNITS                   |

|-------------------------|------------------------------------------|-----------------------|---|----------------|-----|-----|-------------------------|

| t <sub>WRITE</sub>      | Time to Write a 32-Bit Word (Note 11)    |                       | • |                |     | 21  | μs                      |

| t <sub>PAGE_ERASE</sub> | Time to Erase a 2kB Page (Note 11)       |                       | • |                |     | 21  | ms                      |

| t <sub>MASS_ERASE</sub> | Time to Erase 256kB Flash Bank (Note 11) |                       | • |                |     | 21  | ms                      |

|                         | Data Retention                           | 25°C<br>85°C<br>105°C |   | 100<br>20<br>8 |     |     | Years<br>Years<br>Years |

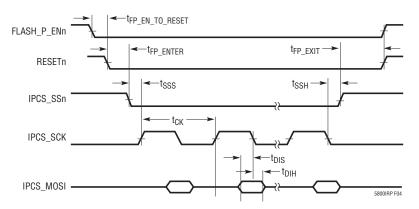

## **FLASH SPI SLAVE AC CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C. VSUPPLY = 3.6V unless otherwise noted. (Note 13)

| SYMBOL                      | PARAMETER                                                                                                                   | CONDITIONS |   | MIN | ТҮР | MAX | UNITS |

|-----------------------------|-----------------------------------------------------------------------------------------------------------------------------|------------|---|-----|-----|-----|-------|

| t <sub>FP_EN_to_RESET</sub> | Setup from Assertion of FLASH_P_ENn to<br>Assertion of RESETn                                                               |            | • | 0   |     |     | ns    |

| t <sub>FP_ENTER</sub>       | Delay from the Assertion RESETn to the First Falling Edge of IPCS_SSn                                                       |            | • | 125 |     |     | μs    |

| t <sub>FP_EXIT</sub>        | Delay from the Completion of the Last Flash SPI<br>Slave Transaction to the Negation of RESETn and<br>FLASH_P_ENn (Note 12) |            | • | 10  |     |     | μs    |

| t <sub>SSS</sub>            | IPCS_SSn Setup to the Leading Edge of IPCS_SCK                                                                              |            |   | 15  |     |     | ns    |

| t <sub>SSH</sub>            | IPCS_SSn Hold from Trailing Edge of IPCS_SCK                                                                                |            |   | 15  |     |     | ns    |

| t <sub>CK</sub>             | IPCS_SCK Period                                                                                                             |            |   | 50  |     |     | ns    |

| t <sub>DIS</sub>            | IPCS_MOSI Data Setup                                                                                                        |            |   | 15  |     |     | ns    |

| t <sub>DIH</sub>            | IPCS_MOSI Data Hold                                                                                                         |            |   | 5   |     |     | ns    |

| t <sub>DOV</sub>            | IPCS_MISO Data Valid                                                                                                        |            | • | 3   |     |     | ns    |

| t <sub>OFF</sub>            | IPCS_MISO Data Tri-state                                                                                                    |            |   | 0   |     | 30  | ns    |

Figure 4. Flash Programming Interface Timing

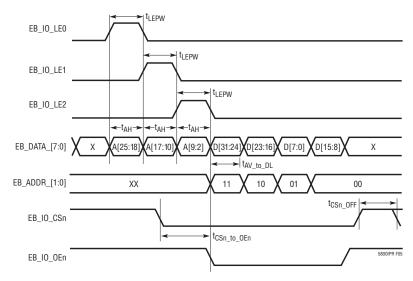

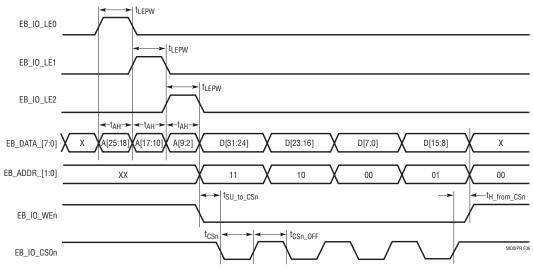

**EXTERNAL BUS AC CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the full operating temperature range, otherwise specifications are at T<sub>A</sub> = 25°C and VSUPPLY = 3.6V unless otherwise noted. (Note 13)

| SYMBOL                  | PARAMETER                                                                                 | CONDITIONS                            |   | MIN | ТҮР | MAX | UNITS |

|-------------------------|-------------------------------------------------------------------------------------------|---------------------------------------|---|-----|-----|-----|-------|

| t <sub>LEPW</sub>       | EB_IO_LE0, EB_IO_LE1, EB_IO_LE2 Pulse Width                                               |                                       |   | 100 |     |     | ns    |

| t <sub>AH</sub>         | EB_DATA_[7:0] Address Hold from the Rising Edge<br>of EB_IO_LEO, EB_IO_LE1, and EB_IO_LE2 | EB_DATA_[7:0] During Address<br>Phase | • | 90  |     |     | ns    |

| t <sub>AV_to_DL</sub>   | EB_ADDR_[1:0] Address Valid Until<br>EB_DATA_[7:0] Data Latched                           |                                       | • | 90  |     |     | ns    |

| t <sub>CSn_to_OEn</sub> | EB_CS0n Asserted Until EB_OEn Asserted                                                    |                                       |   | 150 |     |     | ns    |

| t <sub>CSn_OFF</sub>    | EB_CSOn Negated Between External Bus Transfers                                            |                                       |   | 100 |     |     | ns    |

| t <sub>SU_to_CSn</sub>  | EB_ADDR_[1:0], EB_IO_WEn Setup to<br>EB_CSn Asserted                                      |                                       | • | 50  |     |     | ns    |

| t <sub>H_from_CSn</sub> | EB_ADDR_[1:0], EB_IO_WEn Hold from<br>EB_CSn Negated                                      |                                       | • | 50  |     |     | ns    |

#### Figure 5. External Bus Read Timing

Figure 6. External Bus Write Timing

## **ELECTRICAL CHARACTERISTICS**

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** ESD (electrostatic discharge) sensitive device. ESD protection devices are used extensively internal to Eterna. However, high electrostatic discharge can damage or degrade the device. Use proper ESD handling precautions.

**Note 3:** Extended storage at high temperature is discouraged, as this negatively affects the data retention of Eterna's calibration data. See the FLASH Data Retention section for details.

**Note 4:** Actual RF range is subject to a number of installation-specific variables including, but not restricted to ambient temperature, relative humidity, presence of active interference sources, line-of-sight obstacles, and near-presence of objects (for example, trees, walls, signage, and so on) that may induce multipath fading. As a result, range varies.

**Note 5:** As Specified by IEEE Std. 802.15.4-2006: Wireless Medium Access Control (MAC) and Physical Layer (PHY) Specifications for Low-Rate Wireless Personal Area Networks (LR-WPANs)

http://www.standards.ieee.org/findstds/standard/802.15.4-2011.html

**Note 6:** IEEE Std. 802.15.4-2006 requires transmitters to maintain a frequency tolerance of better than  $\pm 40$  ppm.

**Note 7:** Per pin I/O types are provided in the Pin Functions section. **Note 8:** VIH maximum voltage input must respect the VSUPPLY maximum

voltage specification. **Note 9:** See the SmartMesh IP Manager API Guide for the time Indication notification definition.

**Note 10:** Network time accuracy is a statistical measure and varies over the temperature range, reporting rate and the location of the device relative to the manager in the network. See the Typical Performance Characteristics section for a more detailed description.

**Note 11:** Code execution from flash banks being written or erased is suspended until completion of the flash operation.

**Note 12:** Following erase or write transfers, the IPCS SPI slave status register, 0xD7 must be polled to determine the completion time of the erase or write operation prior to negating either FLASH\_P\_ENn or RESETn. **Note 13:** Guaranteed by design, not production tested.

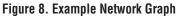

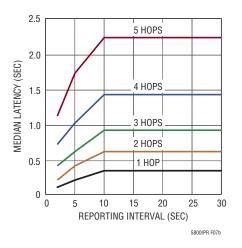

In mesh networks data can propagate from the manager to the nodes, downstream, or from the motes to the manager, upstream, via a sequence of transmissions from one device to the next. As shown in Figure 8, data originating from mote P1 may propagate to the manager directly or through P2. As mote P1 may directly communicate with the manager, mote P1 is referred to as a 1-hop mote. Data originating from mote D1, must propagate through at least one other mote, P2 or P1, and as a result is referred to as a 2-hop mote. The fewest number of hops from a mote to the manager determines the hop depth.

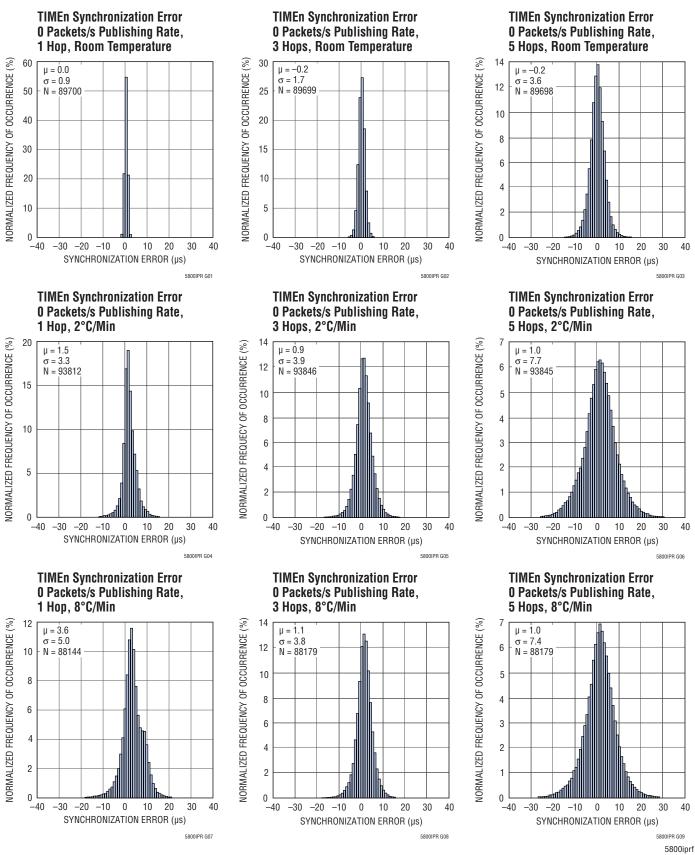

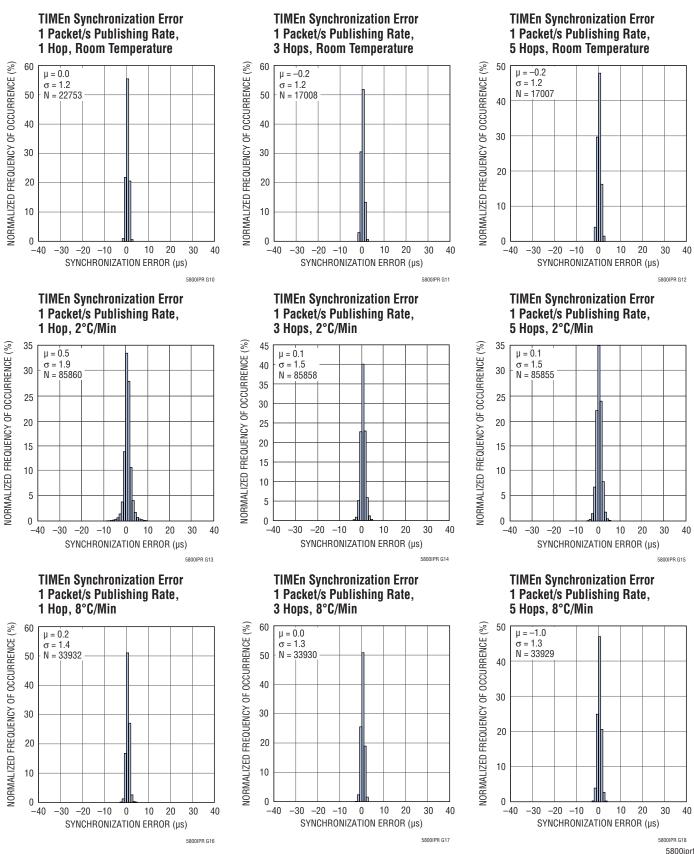

As described in Application Time Synchronization, Eterna provides two mechanisms for applications to maintain a time base across a network. The synchronization performance plots that follow were generated using the more precise TIMEn input. Publishing rate is the rate a mote application sends upstream data. Synchronization improves as the publishing rate increases. Baseline synchronization performance is provided for a network operating with a publishing rate of zero. Actual performance for applications in network will improve as publishing rates increase. All synchronization testing was performed with the 1-hop mote inside a temperature chamber. Timing errors due to temperature changes and temperature differences both between the manager and this mote and between this mote

and its descendents therefore propagated down through the network. The synchronization of the 3-hop and 5-hop motes to the manager was thus affected by the temperature ramps even though they were at room temperature. For 2°C/minute testing the temperature chamber was cycled between -40°C and 85°C at this rate for 24 hours. For 8°C/minute testing, the temperature chamber was rapidly cycled between 85°C and 45°C for 8 hours, followed by rapid cycling between -5°C and 45°C for 8 hours, and lastly, rapid cycling between -40°C and 15°C for 8 hours.

Figure 7

5800inr

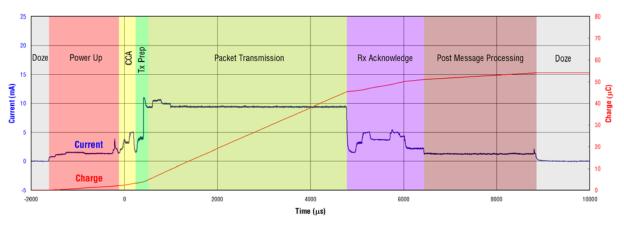

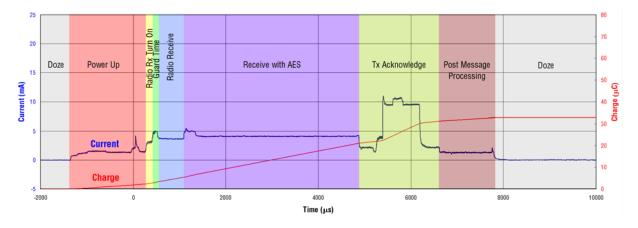

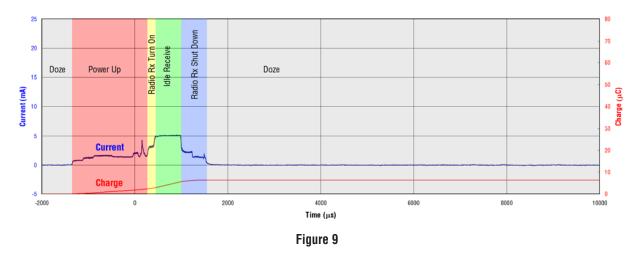

As described in the SmartMesh Network Overview, devices in network spend the vast majority of their time inactive in their lowest power state (doze). On a synchronous schedule a mote will wake to communicate with another mote. Regularly occurring sequences which wake, perform a significant function and return to sleep are considered atomic. These operations are considered atomic as the sequence of events can not be separated into smaller events while performing a useful function. For example, transmission of a packet over the radio is an atomic operation. Atomic operations may be characterized in either charge or energy. In a time slot where a mote successfully sends a packet, an atomic transmit includes setup prior to sending the message, sending the message, receiving the acknowledgment and the post processing needed as a result of the message being sent. Similarly in a time slot when a mote successfully receives a packet, an atomic receive includes setup prior to listening, listening until the

start of the packet transition, receiving the packet, sending the acknowledgement and post processing required due to the arrival of the packet.

To ensure reliability each mote in the network is provided multiple time slots for each packet it nominally will send and forward. The time slots are assigned to communicate upstream, towards the manager, with at least two different motes. When combined with frequency hopping this provides temporal, spatial and spectral redundancy. Given this approach a mote will often listen for a message that it will never receive since the time slot is not being used by the transmitting mote. It has already successfully transmitted the packet. Since typically 3 time slots are scheduled for every 1 packet to be sent or forwarded, motes will perform more of these atomic "Idle Listens" than atomic transmit or atomic receive sequences. Examples of transmit, receive and idle listen atomic operations are shown in Figure 9.

Atomic Operation—Maximum Length Transmit with Acknowledge, 7.5ms Time Slot (54.5µC Total Charge at 3.6V)

Atomic Operation—Maximum Length Receive with Acknowledge, 7.5ms Time Slot (32.6µC Total Charge at 3.6V)

Atomic Operation—Idle Listen, 7.5ms Time Slot (6.4µC Total Charge at 3.6V)

### **PIN FUNCTIONS** Pin functions in italics are currently not supported in software.

The following table organizes the pins by functional groups. For those I/O with multiple functions the alternate functions are shown on the second and third line in their respective row. The **NO** column provides the pin number. The second column lists the function. The **TYPE** column

lists the I/O type. The **I/O** column lists the direction of the signal relative to Eterna. The **PULL** column shows which signals have a fixed passive pull-up or pull-down. The **DESCRIPTION** column provides a brief signal description.

| NO | POWER SUPPLY | ТҮРЕ  | I/0 | PULL | DESCRIPTION                                        |

|----|--------------|-------|-----|------|----------------------------------------------------|

| Р  | GND          | Power | -   | _    | Ground Connection, P = QFN Paddle                  |

| 2  | CAP_PA_1P    | Power | _   | _    | PA DC/DC Converter Capacitor 1 Plus Terminal       |

| 3  | CAP_PA_1M    | Power | -   | _    | PA DC/DC Converter Capacitor 1 Minus Terminal      |

| 4  | CAP_PA_2M    | Power | -   | -    | PA DC/DC Converter Capacitor 2 Minus Terminal      |

| 5  | CAP_PA_2P    | Power | _   | _    | PA DC/DC Converter Capacitor 2 Plus Terminal       |

| 6  | CAP_PA_3P    | Power | -   | _    | PA DC/DC Converter Capacitor 3 Plus Terminal       |

| 7  | CAP_PA_3M    | Power | -   | _    | PA DC/DC Converter Capacitor 3 Minus Terminal      |

| 8  | CAP_PA_4M    | Power | _   | _    | PA DC/DC Converter Capacitor 4 Minus Terminal      |

| 9  | CAP_PA_4P    | Power | -   | _    | PA DC/DC Converter Capacitor 4 Plus Terminal       |

| 10 | VDDPA        | Power | -   | -    | Internal Power Amplifier Power Supply, Bypass      |

| 30 | VDDA         | Power | -   | -    | Regulated Analog Supply, Bypass                    |

| 31 | VCORE        | Power | -   | -    | Regulated Core Supply, Bypass                      |

| 32 | VOSC         | Power | -   | -    | Regulated Oscillator Supply, Bypass                |

| 56 | VPRIME       | Power | -   | -    | Internal Primary Power Supply, Bypass              |

| 57 | CAP_PRIME_4P | Power | -   | _    | Primary DC/DC Converter Capacitor 4 Plus Terminal  |

| 58 | CAP_PRIME_4M | Power | -   | _    | Primary DC/DC Converter Capacitor 4 Minus Terminal |

| 59 | CAP_PRIME_3M | Power | _   | _    | Primary DC/DC Converter Capacitor 3 Minus Terminal |

| 60 | CAP_PRIME_3P | Power | -   | _    | Primary DC/DC Converter Capacitor 3 Plus Terminal  |

| 61 | CAP_PRIME_2P | Power | -   | _    | Primary DC/DC Converter Capacitor 2 Plus Terminal  |

| 62 | CAP_PRIME_2M | Power | -   | _    | Primary DC/DC Converter Capacitor 2 Minus Terminal |

| 63 | CAP_PRIME_1M | Power | _   | _    | Primary DC/DC Converter Capacitor 1 Minus Terminal |

| 64 | CAP_PRIME_1P | Power | -   | _    | Primary DC/DC Converter Capacitor 1 Plus Terminal  |

| 65 | VSUPPLY      | Power | -   | -    | Power Supply Input to Eterna                       |

| NO | RADIO                   | TYPE        | I/0            | PULL | DESCRIPTION                                                                                    |

|----|-------------------------|-------------|----------------|------|------------------------------------------------------------------------------------------------|

| 1  | RADIO_INHIBIT<br>GPI015 | 1 (Note 14) | <br><i> /0</i> | -    | Radio Inhibit<br>General Purpose Digital I/O                                                   |

| 11 | LNA_EN<br>GPI017        | 1           | 0<br>I/0       | -    | External LNA Enable<br>General Purpose Digital I/O                                             |

| 12 | RADIO_TX<br>GPI018      | 1           | 0<br>I/0       | -    | Radio TX Active (External PA Enable/Switch Control)<br>General Purpose Digital I/O             |

| 13 | RADIO_TXn<br>GPI019     | 1           | 0<br>I/0       | -    | Radio TX Active (External PA Enable/Switch Control), Active Low<br>General Purpose Digital I/O |

| 14 | ANTENNA                 | -           | -              | -    | Single-Ended Antenna Port, 50 $\Omega$                                                         |

## **PIN FUNCTIONS** Pin functions in italics are currently not supported in software.

| NO | CRYSTALS     | TYPE    | I/0 | PULL | DESCRIPTION        |

|----|--------------|---------|-----|------|--------------------|

| 19 | OSC_32K_XOUT | Crystal | 0   | _    | 32kHz Crystal Xout |

| 20 | OSC_32K_XIN  | Crystal | I   | _    | 32kHz Crystal Xin  |

| 28 | OSC_20M_XIN  | Crystal | I   | _    | 20MHz Crystal Xin  |

| 29 | OSC_20M_XOUT | Crystal | 0   | _    | 20MHz Crystal Xout |

| NO | RESET  | TYPE | I/0 | PULL | DESCRIPTION             |

|----|--------|------|-----|------|-------------------------|

| 22 | RESETn | 1    | 0   | UP   | Reset Input, Active Low |

| NO | JTAG | TYPE | I/0 | PULL | DESCRIPTION           |

|----|------|------|-----|------|-----------------------|

| 23 | TDI  | 1    | Ι   | UP   | JTAG Test Data In     |

| 24 | TDO  | 1    | 0   | _    | JTAG Test Data Out    |

| 25 | TMS  | 1    | Ι   | UP   | JTAG Test Mode Select |

| 26 | ТСК  | 1    | I   | DOWN | JTAG Test Clock       |

| NO | SPECIAL PURPOSE | TYPE        | I/O | PULL | DESCRIPTION                      |

|----|-----------------|-------------|-----|------|----------------------------------|

| 72 | TIMEn           | 1 (Note 14) | I   | -    | Time Capture Request, Active Low |

| NO | CLI and EXTERNAL MEMORY | TYPE | I/0      | PULL | DESCRIPTION                                                                             |

|----|-------------------------|------|----------|------|-----------------------------------------------------------------------------------------|

| 33 | EB_DATA_7               | 1    | I/0      | _    | External Bus Data Bit 7                                                                 |

| 34 | EB_DATA_6               | 1    | I/0      | _    | External Bus Data Bit 6                                                                 |

| 35 | EB_DATA_4               | 1    | I/0      | _    | External Bus Data Bit 4                                                                 |

| 36 | EB_DATA_0               | 1    | I/0      | -    | External Bus Data Bit 0                                                                 |

| 37 | UARTCO_TX<br>EB_IO_LEO  | 2    | 0<br>0   | -    | CLI UART 0 Transmit<br>External Bus I/O Latch Enable 0 for External Address Bits A[9:2] |

| 38 | UARTCO_RX<br>EB_DATA_1  | 1    | I<br>I/0 | -    | CLI UART 0 Receive<br>External Bus Data Bit 1                                           |

| 39 | EB_IO_LE2               | 1    | 0        | _    | External Bus I/O Latch Enable 2 for External Address Bits A[25:18]                      |

| 41 | EB_ADDR_1               | 2    | 0        | _    | External Bus Address Bit 1                                                              |

| 43 | EB_ADDR_0               | 2    | 0        | -    | External Bus Address Bit 0                                                              |

| 46 | EB_DATA_3               | 1    | I/0      | -    | External Bus Data Bit 3                                                                 |

| 47 | EB_DATA_2               | 1    | I/0      | _    | External Bus Data Bit 2                                                                 |

| 48 | EB_DATA_5               | 1    | I/0      | -    | External Bus Data Bit 5                                                                 |

| 49 | EB_IO_CS0n              | 2    | 0        | _    | External Bus Chip Select 0                                                              |

| 50 | UARTC1_TX               | 2    | 0        | -    | CLI UART 1 Transmit                                                                     |

| 51 | UARTC1_RX               | 1    | I        | _    | CLI UART 1 Receive                                                                      |

| 52 | EB_IO_WEn               | 2    | 0        | _    | External Bus Write Enable Strobe                                                        |

| 53 | EB_I0_0En               | 2    | 0        | _    | External Bus Output Enable Strobe                                                       |

| NO | IPCS SPI/FLASH PROGRAMMING (NOTE 15) | TYPE | I/0 | PULL | DESCRIPTION                                         |

|----|--------------------------------------|------|-----|------|-----------------------------------------------------|

| 40 | IPCS_MISO                            | 2    | 0   | -    | SPI Flash Emulation (MISO) Master In Slave Out Port |

| 42 | IPCS_MOSI                            | 1    | I   | -    | SPI Flash Emulation (MOSI) Master Out Slave In Port |

| 44 | IPCS_SCK                             | 1    | I   | -    | SPI Flash Emulation (SCK) Serial Clock Port         |

| 45 | IPCS_SSn                             | 1    | I   | -    | SPI Flash Emulation Slave Select, Active Low        |

| 55 | FLASH_P_ENn                          | 1    |     | UP   | Flash Program Enable, Active Low                    |

|    | EB_IO_LE1                            |      | 0   | UP   | External Bus I/O Latch Enable 1                     |

### **PIN FUNCTIONS** Pin functions in italics are currently not supported in software.

| NO | API UART     | TYPE        | I/0 | PULL | DESCRIPTION                                     |

|----|--------------|-------------|-----|------|-------------------------------------------------|

| 66 | UART_RX_RTSn | 1 (Note 14) |     | _    | UART Receive (RTS) Request to Send, Active Low  |

| 67 | UART_RX_CTSn | 1           | 0   | -    | UART Receive (CTS) Clear to Send, Active Low    |

| 68 | UART_RX      | 1 (Note 14) |     | -    | UART Receive                                    |

| 69 | UART_TX_RTSn | 1           | 0   | -    | UART Transmit (RTS) Request to Send, Active Low |

| 70 | UART_TX_CTSn | 1 (Note 14) | I   | -    | UART Transmit (CTS) Clear to Send, Active Low   |

| 71 | UART_TX      | 2           | 0   | -    | UART Transmit                                   |

**Note 14:** These inputs are always enabled and must be driven or pulled to a valid state to avoid leakage.

**Note 15:** Embedded programming over the IPCS SPI bus is only available when RESETn is asserted.

**VSUPPLY:** System and I/O Power Supply. Provides power to the chip including the on-chip DC/DC converters. The digital-interface I/O voltages are also set by this voltage. Bypass with  $2.2\mu$ F and  $0.1\mu$ F to ensure the DC/DC converters operate properly.

**VDDPA:** PA-Converter Bypass Pin. A  $0.47\mu$ F capacitor should be connected from VDDPA to ground with as short a trace as feasible. Do not connect anything else to this pin.

**VDDA:** Analog-Regulator Bypass Pin. A  $0.1\mu$ F capacitor should be connected from VDDA to ground with as short a trace as feasible. Do not connect anything else to this pin.

**VCORE:** Core-Regulator Bypass Pin. A 56nF capacitor should be connected from VCORE to ground with as short a trace as feasible. Do not connect anything else to this pin.

**VOSC:** Oscillator-Regulator Bypass Pin. A 56nF capacitor should be connected from VOSC to ground with as short a trace as feasible. Do not connect anything else to this pin.

**VPRIME:** Primary-Converter Bypass Pin. A 0.22µF capacitor should be connected from VPRIME to ground with as short a trace as feasible. Do not connect anything else to this pin.

**VBGAP:** Bandgap reference output. Used for testing and calibration. Do not connect anything to this pin.

**CAP\_PA\_1P, CAP\_PA\_1M Through CAP\_PA\_4P, CAP\_ PA\_4M:** Dedicated Power Amplifier DC/DC Converter Capacitor Pins. These pins are used when the radio is transmitting to efficiently convert VSUPPLY to the proper voltage for the power amplifier. A 56nF capacitor should be connected between each P and M pair. Trace length should be as short as feasible.

**CAP\_PRIME\_1P, CAP\_PRIME\_1M Through CAP\_PRIME\_4P, CAP\_PRIME\_4M:** Primary DC/DC Converter Capacitor Pins. These pins are used when the device is awake to efficiently convert VSUPPLY to the proper voltage for the three on-chip low dropout regulators. A 56nF capacitor should be connected between each P and M pair. Trace length should be as short as feasible.

**ANTENNA:** Multiplexed Receiver Input and Transmitter Output Pin. The impedance presented to the antenna pin should be  $50\Omega$ , single-ended with respect to paddle ground. To ensure regulatory compliance of the final product please see the Eterna Integration Guide for filtering requirements. The antenna pin should not have a DC path to ground; AC blocking must be included if a DC-grounded antenna is used.

## LTC5800-IPR

### PIN FUNCTIONS

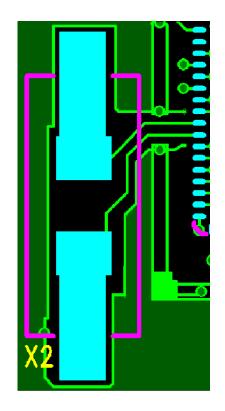

**OSC\_32K\_XOUT:** Output Pin for the 32kHz Oscillator. Connect to 32kHz quartz crystal. The OSC\_32K\_XOUT and OSC\_32K\_XIN traces must be well-shielded from other signals, both on the same PCB layer and lower PCB layers, as shown in Figure 10.

**OSC\_32K\_XIN:** Input for the 32kHz Oscillator. Connect to 32kHz quartz crystal. The OSC\_32K\_XOUT and OSC\_32K\_XIN traces must be well-shielded from other signals, both on the same PCB layer and lower PCB layers, as shown in Figure 10.

**OSC\_20M\_XOUT:** Output for the 20MHz Oscillator. Connect only to a supported 20MHz quartz crystal. The OSC\_20M\_XOUT and OSC\_20M\_XIN traces must be well-shielded from other signals, both on the same PCB layer and lower PCB layers, as shown in Figure 10. See the Eterna Integration Guide for supported crystals.

**OSC\_20M\_XIN:** Input for the 20MHz Oscillator. Connect only to a supported 20MHz quartz crystal. The OSC\_20M\_ XOUT and OSC\_20M\_XIN traces must be well-shielded from other signals, both on the same PCB layer and lower PCB layers, as shown in Figure 10.

**RESETn:** The asynchronous reset signal is internally pulled up. Resetting Eterna will result in the ARM Cortex M3 rebooting and loss of network connectivity. Use of this signal for resetting Eterna is not recommended, except during power-on and in-circuit programming.

**RADIO\_INHIBIT:** RADIO\_INHIBIT provide a mechanism for an external device to temporarily disable radio operation. Failure to observe the timing requirements defined in the RADIO\_INHIBIT AC Characteristics table may result in unreliable network operation. In designs where the RADIO\_INHIBIT function is not needed the input must either be tied, pulled or actively driven low to avoid excess leakage.

**TMS, TCK, TDI, TDO:** JTAG Port Supporting Software Debug and Boundary Scan. An IEEE Std 1149.1b-1994 compliant boundary scan definition language (BDSL) file for the WR QFN72 package can be found here.

Figure 10. PCB Top Metal Layer Shielding of Crystal Signals

**SLEEPn:** The SLEEPn function is not currently supported in software. The SLEEPn input must either be tied, pulled or actively driven high to avoid excess leakage.

**UART\_RX, UART\_RX\_RTSn, UART\_RX\_CTSn, UART\_TX, UART\_TX\_RTSn, UART\_TX\_CTSn:** The API UART interface includes bidirectional wake-up and flow control. Unused input signals must be driven or pulled to their inactive state.

**TIMEn:** Strobing the TIMEn input is the most accurate method to acquire the network time maintained by Eterna. Eterna latches the network timestamp with sub-microsecond resolution on the rising edge of the TIMEn signal and produces a packet on the API serial port containing the timing information.

## **PIN FUNCTIONS**

**UARTCO\_RX, UARTCO\_TX, UARTC1\_RX, UARTC1\_TX:** The CLI UART provides a mechanism for monitoring, configuration and control of Eterna during operation. On the LTC5800-IPR CLI UART 0 is used when Eterna is not configured to support external RAM and CLI UART 1 is used when Eterna is configured to support external RAM. For a complete description of the supported commands see the SmartMesh IP Manager CLI Guide.

**EB\_DATA\_0 through EB\_DATA\_7, EB\_ADDR\_0, EB\_ ADDR\_1, EB\_I0\_LE1 through EB\_I0\_LE2, EB\_I0\_CSOn, EB\_I0\_WEn, EB\_I0\_ENn:** The external bus provides a multiplexed address data bus enabling the Cortex-M3 direct access of external byte wide RAM. The additional RAM is used by network management software enabling the support of a larger network of motes with higher packet throughput. To support the addressing needed, each latch signal, EB\_IO\_LEO, EB\_IO\_LE1, and EB\_IO\_LE2 will strobe to latch 8-bits of address from the EB\_DATA[7:0] bus. EB\_IO\_LEO, EB\_IO\_LE1, and EB\_IO\_LE2 correspond to address bits [9:2], [17:10] and [25:18] respectively. EB\_ADDR\_0 and EB\_ADDR\_1 correspond to the lower two bits of address. For systems with 256kB or less EB\_IO\_LE2 can be ignored. EB\_IO\_CSOn, EB\_IO\_WEn and EB\_IO\_OEn provide chip select, write enable and output enable control of the external RAM.

**FLASH\_P\_ENn, IPCS\_SSn, IPCS\_SCK, IPCS\_MISO, IPCS\_SSn:** The in-circuit programming control system (IPCS) bus enables in-circuit programming of Eterna's flash memory. IPCS\_SCK is a clock and should be terminated appropriately for the driving source to prevent overshoot and ringing.

The LTC5800 is the world's most energy-efficient IEEE 802.15.4 compliant platform, enabling battery and energy harvested applications. With a powerful 32-bit ARM Cortex-M3, best-in-class radio, flash, RAM and purpose-built peripherals, Eterna provides a flexible, scalable and robust networking solution for applications demanding minimal energy consumption and data reliability in even the most challenging RF environments.

Shown in Figure 11, Eterna integrates purpose-built peripherals that excel in both low operating-energy consumption and the ability to rapidly and precisely cycle between operating and low-power states. Items in the gray shaded region labeled Analog Core correspond to the analog/RF components.

#### **POWER SUPPLY**

Eterna is powered from a single pin, VSUPPLY, which powers the I/O cells and is also used to generate internal supplies. Eterna's two on-chip DC/DC converters minimize energy consumption while the device is awake. To conserve power the DC/DC converters are disabled when the device is in low power state. The integrated power supply conditioning architecture, including the two integrated DC/ DC converters and three integrated low dropout regulators, provides excellent rejection of supply noise. Eterna's operating supply voltage range is high enough to support direct connection to lithium-thionyl chloride (Li-SOCl<sub>2</sub>) sources and wide enough to support battery operation over a broad temperature range.

5800ipr

#### SUPPLY MONITORING AND RESET

Eterna integrates a power-on-reset (PoR) circuit. As the RESETn input pin is nominally configured with an internal pull-up resistor, no connection is required. For a graceful shutdown, the software and the networking layers should be cleanly halted via API commands prior to assertion of the RESETn pin. See the SmartMesh IP Manager API Guide for details on the disconnect and reset commands. Eterna includes a soft brown-out monitor that fully protects the flash from corruption in the event that power is removed while writing to flash. The integrated flash supervisory functionality, in conjunction with a fault tolerant file system, yields a robust nonvolatile storage solution.

#### PRECISION TIMING

Eterna's unique low power dedicated timing hardware and timing algorithms provide a significant improvement over competing 802.15.4 product offerings. This functionality provides timing precision two to three orders of magnitude better than any other low power solution available at the time of publication. Improved timing accuracy allows motes to minimize the amount of radio listening time required to ensure packet reception thereby lowering even further the power consumed by SmartMesh networks. Eterna's patented timing hardware and timing algorithms provide superior performance over rapid temperature changes, further differentiating Eterna's reliability when compared with other wireless products. In addition, precise timing enables networks to reduce spectral dead time, increasing total network throughput.

#### **APPLICATION TIME SYNCHRONIZATION**

In addition to coordinating time slots across the network, which is transparent to the user, Eterna's timing management is used to support two mechanisms to share network time. Having an accurate, shared, network-wide time base enables events to be accurately time stamped or tasks to be performed in a synchronized fashion across a network. Eterna will send a time packet through its serial interface when one of the following occurs:

- Eterna receives an API request to read time

- The TIMEn signal is asserted

The use of TIMEn has the advantage of being more accurate. The value of the time stamp is captured in hardware relative to the rising edge of TIMEn. If an API request is used, due to packet processing, the value of the time stamp may be captured several milliseconds after receipt of the packet. See the TIMEn AC Characteristics table for the TIMEn function's definition and specifications.

#### TIME REFERENCES

Eterna includes three clock sources: an internal relaxation oscillator, a low power oscillator designed for a 32.768kHz crystal, and the radio reference oscillator designed for a 20MHz crystal.

#### **Relaxation Oscillator**

The relaxation oscillator is the primary clock source for Eterna, providing the clock for the CPU, memory subsystems, and all peripherals. The internal relaxation oscillator is dynamically calibrated to 7.3728MHz. The internal relaxation oscillator typically starts up in a few  $\mu$ s, providing an expedient, low energy method for duty cycling between active and low power states. Quick start-up from the doze state, defined in the State Diagram section, allows Eterna to wake up and receive data over the UART and SPI interfaces by simply detecting activity on the appropriate signals.

#### 32.768kHz Crystal Oscillator

Once Eterna is powered up and the 32.768kHz crystal source has begun oscillating, the 32.768kHz crystal remains operational while in the Active state, and is used as the timing basis when in Doze state. See the State Diagram section, for a description of Eterna's operational states.

#### 20MHz Crystal Oscillator

The 20 MHz crystal source provides a frequency reference for the radio, and is automatically enabled and disabled by Eterna as needed. Eterna requires specific characterized 20MHz crystal references. See the the Eterna Integration Guide for a complete list of the currently supported 20MHz crystals.

#### RADIO

Eterna includes the lowest power commercially available 2.4GHz IEEE 802.15.4e radio by a substantial margin. (Please refer to Radio Specifications section for power consumption numbers.) Eterna's integrated power amplifier is calibrated and temperature compensated to consistently provide power at a limit suitable for worldwide radio certifications. Additionally, Eterna uniquely includes a hardware-based autonomous MAC that handles precise sequencing of peripherals, including the transmitter, the receiver, and advanced encryption standard (AES) peripherals. The hardware-based autonomous media access controller (MAC) minimizes CPU activity, thereby further decreasing power consumption.

#### UARTS

The principal network interface is through the application programming interface (API) UART. A command-line interface (CLI) UART is also provided for support of test and debug functions. Both UARTs sense activity continuously, consuming virtually no power until data is transferred over the port and then automatically returning to their lowest power state after the conclusion of a transfer. The definition for packet encoding on the API UART interface can be found in the SmartMesh IP Manager API Guide and the CLI command definitions can be found in the SmartMesh IP Manager CLI Guide.

#### **API UART Protocols**

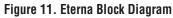

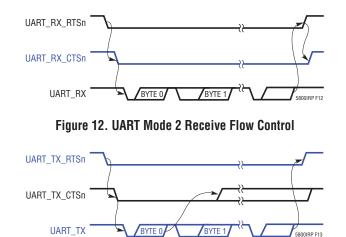

The API UART supports multiple protocols with the goal of supporting a wide range of companion multipoint control units (MCUs) while reducing power consumption of the system. As a general rule, higher serial data rates translate into lower energy consumption for both endpoints. The receive half of the API UART protocol includes two additional signals in addition to UART\_RX: UART\_RX\_ RTSn and UART\_RX\_CTSn. The transmit half of the API UART protocol includes two additional signals in addition to UART\_TX: UART\_TX\_RTSn and UART\_TX\_CTSn. The two supported protocols are referred to as UART Mode 2 and UART Mode 4. Mode setting is controlled via the Fuse Table.

In the Figures accompanying the protocol descriptions, signals driven by the companion processor are drawn in black and signals driven by Eterna are drawn in blue.

### UART Mode 2

UART Mode 2 provides the most energy-efficient method for operating Eterna's API UART. UART Mode 2 requires the use of all six UART signals, but does not require adherence to the minimum inter-packet delay as defined in section UART AC Characteristics. UART Mode 2 incorporates edge-sensitive flow control, at either 9600 or 115200 baud. Packets are HDLC encoded with one stop bit and no parity bit. The flow control signals for Eterna's API receive path are shown in Figure 12, UART Mode 2 Receive Flow Control. Transfers are initiated by the companion processor asserting UART\_RX\_RTSn. Eterna then responds by enabling the UART and asserting UART\_RX\_CTSn. After detecting the assertion of UART\_RX\_CTSn the companion processor sends the entire packet. Following the transmission of the final byte in the packet, the companion processor negates UART\_RX\_RTSn and waits until the negation of UART\_RX\_CTSn before asserting UART\_RX\_RTSn again.

The flow control signals for Eterna's API transmit path are shown in Figure 13, UART Mode 2 Transmit Flow Control. Transfers are initiated by Eterna asserting UART\_TX\_RTSn. The companion processor responds by asserting UART\_ TX\_CTSn when ready to receive data. After detecting the falling edge of UART\_TX\_CTSn Eterna sends the entire packet. Following the transmission of the final byte in the packet Eterna negates UART\_TX\_RTSn and waits until the negation of UART\_TX\_CTSn before asserting UART\_TX\_RTSn again. The companion processor may negate UART\_TX\_CTSn any time after the first byte is transmitted provided the timeout from UART\_TX\_RTSn to UART\_TX\_CTSn is met.

#### UART Mode 4

UART Mode 4 incorporates level-sensitive flow control on the TX channel and requires no flow control on the RX channel, supporting both 9600 and 115200 baud. The use of level-sensitive flow control signals enables higher data rates with the option of using a reduced set of the flow control signals; however, the companion processor must negate UART TX CTSn prior to the end of the packet and wait at least t<sub>RX RTS to RX CTS</sub> between transmit packets See the UART AC Characteristics table for complete timing specifications. Packets are HDLC encoded with one stop bit and no parity bit. The use of the RX flow control signals (UART RX RTSn and UART RX CTSn) for Mode 4 are optional provided the use is limited to the industrial temperature range (-40°C to 85°C); otherwise, the flow control is manditory. The flow control signals for the TX channel are shown in Figure 14, UART Mode 4 Transmit Flow Control. Transfers are initiated by Eterna asserting UART TX RTSn. The UART TX CTSn signal may be actively driven by the companion processor when ready to receive a packet or UART TX CTSn may be tied low if the companion processor is always ready to receive a packet. After detecting a logic '0' on UART TX CTSn Eterna sends the entire packet. Following the transmission of the final byte in the packet Eterna negates UART\_TX\_RTSn and waits for a minimum period defined in the UART AC Characteristics table before asserting UART\_TX\_RTSn again.

For details on the timing of the UART protocol, see section UART AC Characteristics.

Figure 14. UART Mode 4 Transmit Flow Control

#### **CLI UART**

The command line interface (CLI) UART port is a 2-wire protocol (TX and RX) that operates at a fixed 9600 baud rate with one stop bit and no parity. The CLI UART interface is intended to support command line instructions and response activity.

#### AUTONOMOUS MAC

Eterna was designed as a system solution to provide a reliable, ultralow power, and secure network. A reliable network capable of dynamically optimizing operation over changing environments requires solutions that are far too complex to completely support through hardware acceleration alone. As described in the Precision Timing section, proper time management is essential for optimizing a solution that is both low power and reliable. To address these requirements Eterna includes the autonomous MAC, which incorporates a coprocessor for controlling all of the time-critical radio operations. The autonomous MAC provides two benefits: first, preventing variable software latency from affecting network timing and second, greatly reducing system power consumption by allowing the CPU

5800inr

to remain inactive during the majority of the radio activity. The autonomous MAC provides software-independent timing control of the radio and radio-related functions, resulting in superior reliability and exceptionally low power.

### SECURITY

Network security is an often overlooked component of a complete network solution. Proper implementation of security protocols is significant in terms of both engineering effort and market value in an OEM product. Eterna system solutions provide a FIPS-197 validated encryption scheme that includes authentication and encryption at the MAC and network layers with separate keys for each mote. This not only yields end-to-end security, but if a mote is somehow compromised, communication from other motes is still secure. A mechanism for secure key exchange allows kevs to be kept fresh. To prevent physical attacks. Eterna includes hardware support for electronically locking devices, thereby preventing access to Eterna's flash and RAM memory and thus the keys and code stored therein. This lock-out feature also provides a means to securely unlock a device should support of a product require access. For details see the Board Specific Configuration Guide.

### TEMPERATURE SENSOR

Eterna includes a calibrated temperature sensor on chip. The temperature readings are available locally through Eterna's serial API, in addition to being available via the network manager. The performance characteristics of the temperature sensor can be found in the Temperature Sensor Characteristics table.

### **RADIO INHIBIT**

The RADIO\_INHIBIT input enables an external controller to temporarily disable the radio software drivers (for example, to take a sensor reading that is susceptible to radio interference). When RADIO\_INHIBIT is asserted the software radio drivers will disallow radio operations including clear channel assessment, packet transmits, or packet receipts. If the current timeslot is active when RADIO\_INHIBIT is asserted the radio will be disabled after the present operation completes. For details on the timing associated with RADIO\_INHIBIT, see the RADIO\_INHIBIT AC Characteristics table.

### FLASH PROGRAMMING