# TSB12LV32-EP

IEEE 1394-1995 and P1394a Compliant General-Purpose Link-Layer Controller

# Data Manual

# **Contents**

| Se | ction  |          |                                                   | Page |

|----|--------|----------|---------------------------------------------------|------|

| 1  | Overv  | iew      |                                                   | 1    |

|    | 1.1    | TSB12L   | LV32 Description                                  | 1    |

|    | 1.2    | TSB12L   | _V32-EP Features                                  | 1    |

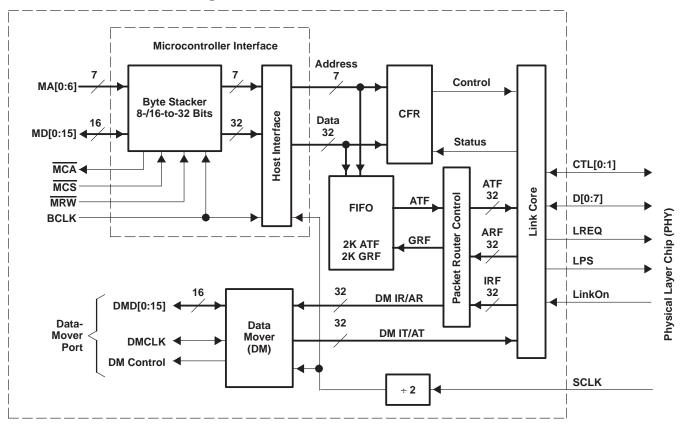

|    | 1.3    | Function | nal Block Diagram                                 | 2    |

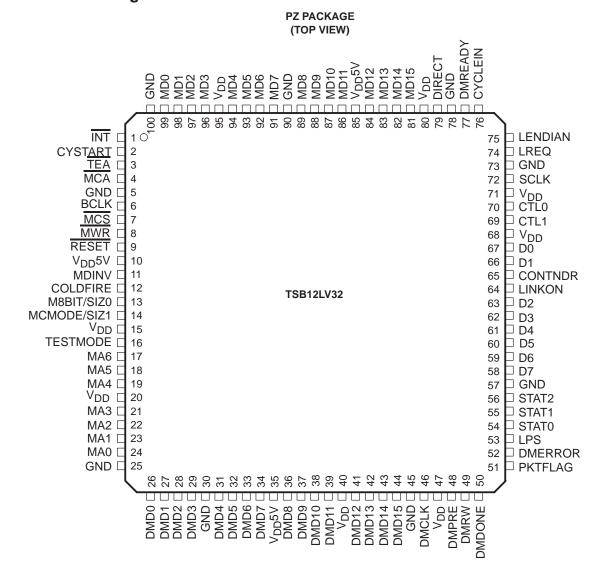

|    | 1.4    |          | al Assignments                                    |      |

|    | 1.5    |          | al Functions                                      |      |

|    |        | 1.5.1    | STAT0, STAT1, and STAT2 Programming               |      |

|    | 1.6    |          | g Information                                     |      |

| 2  |        |          | ers                                               |      |

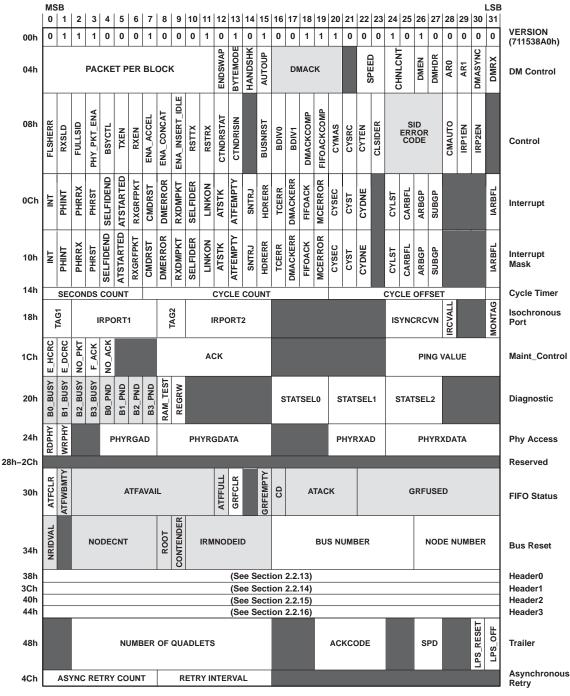

| _  | 2.1    | _        | LV32 Configuration Registers                      |      |

|    | 2.2    |          | ration Register Definitions                       |      |

|    | 2.2    | 2.2.1    | Version Register at 00h                           |      |

|    |        | 2.2.2    | Data-Mover Control Register at 04h                |      |

|    |        | 2.2.3    | Control Register at 08h                           |      |

|    |        | 2.2.4    | Interrupt/Interrupt Mask Registers at 0Ch and 10h |      |

|    |        | 2.2.5    | Cycle Timer Register at 14h                       |      |

|    |        | 2.2.6    | Isochronous Port Register at 18h                  |      |

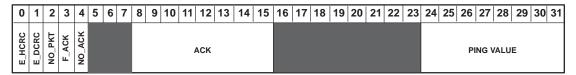

|    |        | 2.2.7    | Maint_Control Register at 1Ch                     |      |

|    |        | 2.2.7    | Diagnostic Register at 20h                        |      |

|    |        | 2.2.9    | Phy Access Register at 24h                        |      |

|    |        | 2.2.9    | Reserved Registers at 28h–2Ch                     |      |

|    |        | 2.2.10   | · · · · · · · · · · · · · · · · · · ·             |      |

|    |        | 2.2.11   | FIFO Status Register at 30h                       |      |

|    |        | 2.2.12   | Bus Reset Register at 34h                         |      |

|    |        |          | Header0 Register at 38h                           |      |

|    |        | 2.2.14   | Header1 Register at 3Ch                           |      |

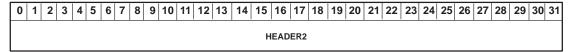

|    |        | 2.2.15   | Header2 Register at 40h                           |      |

|    |        | 2.2.16   | Header3 Register at 44h                           |      |

|    |        | 2.2.17   | Trailer Register at 48h                           |      |

| _  |        | 2.2.18   | Asynchronous Retry Register at 4Ch                |      |

| 3  |        |          | r Interface                                       |      |

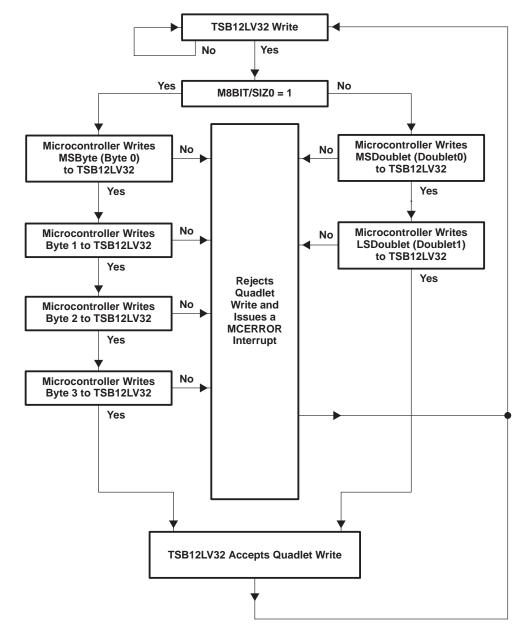

|    | 3.1    |          | ontroller Byte Stack (Write) Operation            |      |

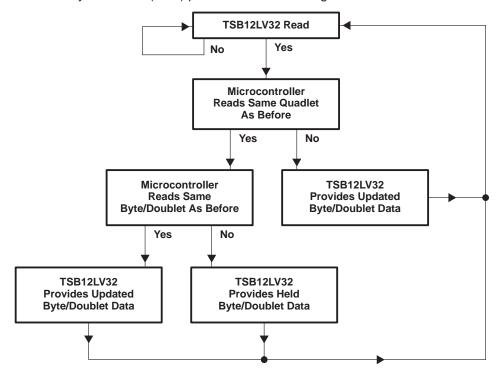

|    | 3.2    |          | ontroller Byte Unstack (Read) Operation           |      |

|    | 3.3    |          | ontroller Interface Read/Write Timing             |      |

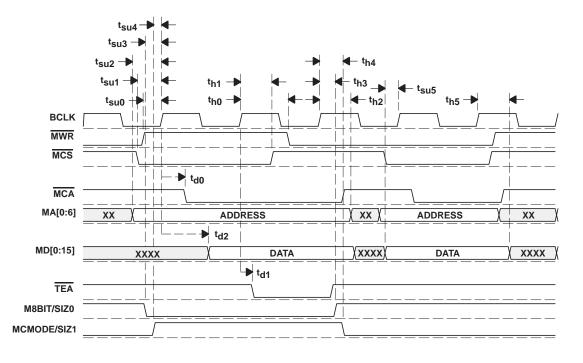

|    |        | 3.3.1    | Microcontroller Handshake Mode                    |      |

|    |        | 3.3.2    | Microcontroller Fixed-Timing Mode                 |      |

|    |        | 3.3.3    | Microcontroller ColdFire Mode                     |      |

|    |        | 3.3.4    | Microcontroller Critical Timing                   |      |

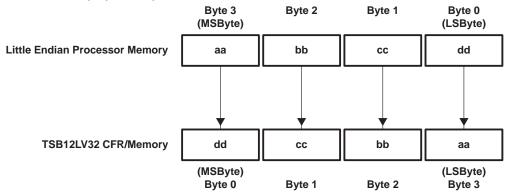

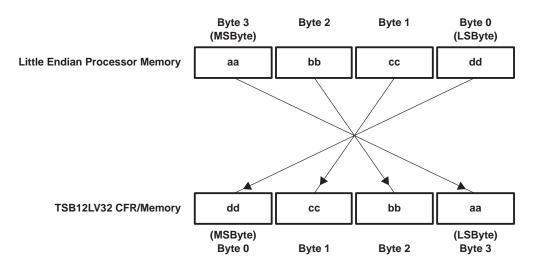

|    |        | 3.3.5    | Endian Swapping                                   |      |

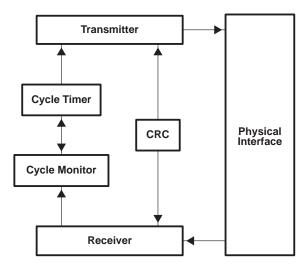

| 4  | Link C |          |                                                   |      |

|    | 4.1    | Physica  | ıl Interface                                      | 41   |

|    | 4.2    | Transmi  | itter                                             | 41   |

|    | 4.3    | Receive  | er                                                | 41   |

|    | 4.4    | •        | imer                                              |      |

|    | 4.5    |          | Monitor                                           |      |

|    | 4.6    | Cyclic R | Redundancy Check (CRC)                            | 42   |

|    | 4.7    | Receive  | ed Packet Routing Control Logic                   | 42   |

|    |        |          |                                                   |      |

| 5  | Data-M | over Port Interface                                                                                     | . 45 |

|----|--------|---------------------------------------------------------------------------------------------------------|------|

|    | 5.1    | Data-Mover Data Flow Diagram                                                                            | 47   |

|    |        | 5.1.1 Isochronous Receive                                                                               | 47   |

|    |        | 5.1.2 Isochronous Transmit                                                                              | . 49 |

|    |        | 5.1.3 Asynchronous Receive                                                                              | 51   |

|    |        | 5.1.4 Asynchronous Transmit                                                                             | 52   |

|    | 5.2    | Data-Mover Modes of Operation                                                                           |      |

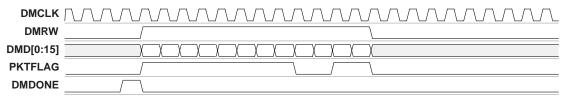

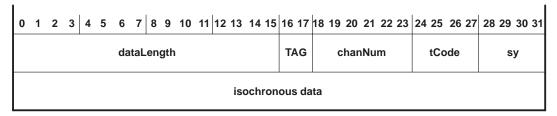

|    |        | 5.2.1 Isochronous Transmit With Automatic Header Insertion                                              | 55   |

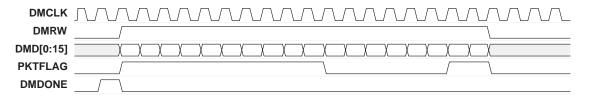

|    |        | 5.2.2 Isochronous Transmit Without Automatic Header Insertion                                           |      |

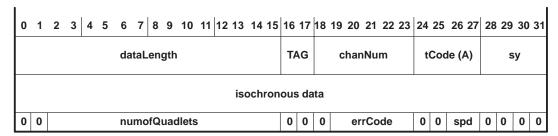

|    |        | 5.2.3 Isochronous Packet Receive Without Header and Trailer Removal                                     | 57   |

|    |        | 5.2.4 Isochronous Packet Receive With Header and Trailer                                                | 58   |

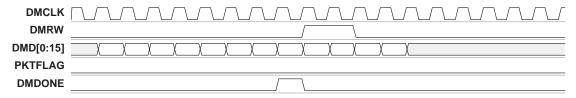

|    |        | 5.2.5 Asynchronous Packet Transmit With Automatic Header Insertion                                      |      |

|    |        | 5.2.6 Asynchronous Packet Transmit Without Automatic Header Insertion                                   |      |

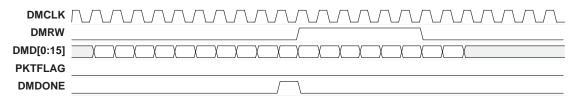

|    |        | 5.2.7 Asynchronous Packet Receive With Headers and Trailer                                              |      |

|    |        | 5.2.8 Asynchronous Packet Receive With Automatic Header and Trailer Removal                             |      |

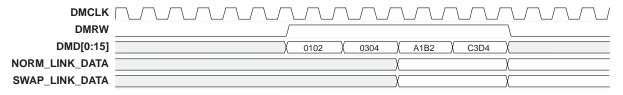

|    | 5.3    | Data-Mover Byte Mode                                                                                    |      |

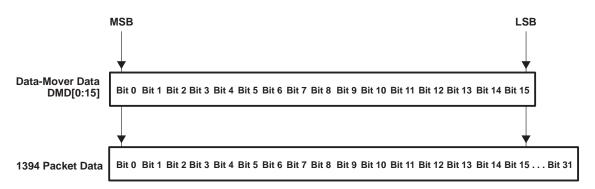

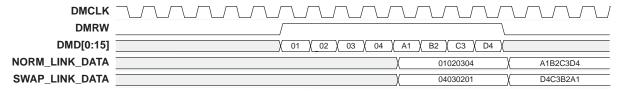

|    | 5.4    | Data-Mover Endian Swapping                                                                              |      |

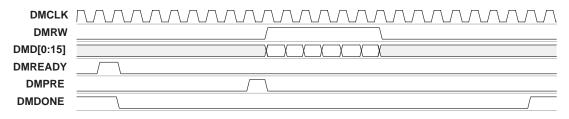

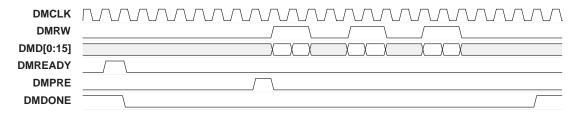

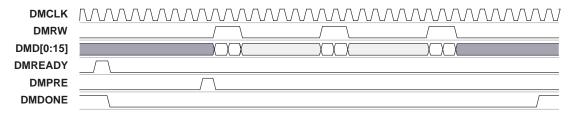

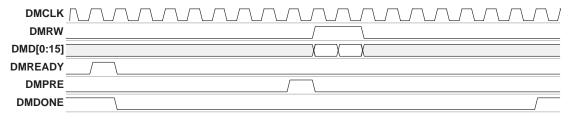

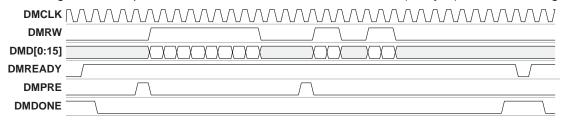

|    | 5.5    | Data-Mover Handshake Mode                                                                               |      |

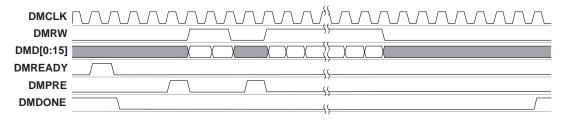

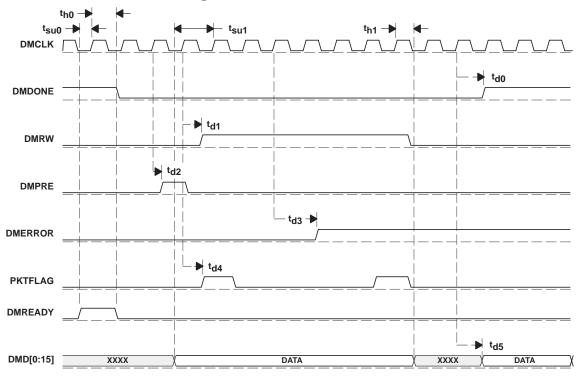

|    | 5.6    | Data-Mover Critical Timing                                                                              |      |

| 6  |        | emory Access                                                                                            |      |

| •  | 6.1    | General                                                                                                 |      |

|    | 6.2    | ATF Access                                                                                              |      |

|    | 6.3    | ATF Burst Access                                                                                        |      |

|    | 6.4    | General-Receive FIFO (GRF)                                                                              |      |

|    | 6.5    | GRF Stored Data Format                                                                                  |      |

| 7  |        | V32 Data Formats                                                                                        |      |

| -  | 7.1    | Asynchronous Transmit/Receive (Microcontroller Interface/Data-Mover Port to/From TSB12LV32)             |      |

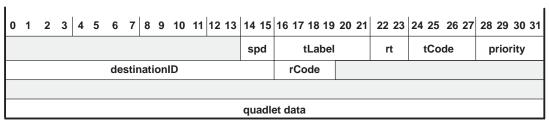

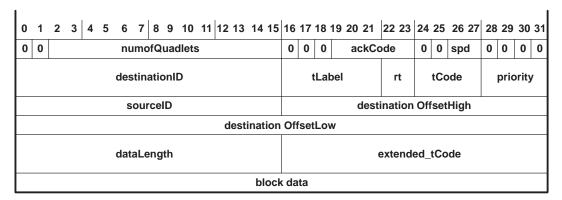

|    |        | 7.1.1 Quadlet Transmit                                                                                  |      |

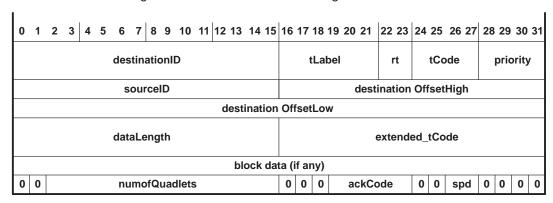

|    |        | 7.1.2 Block Transmit                                                                                    |      |

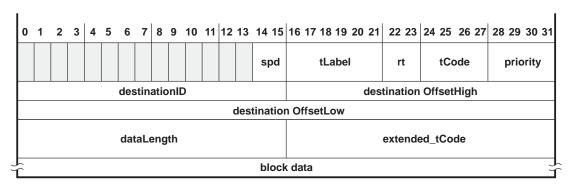

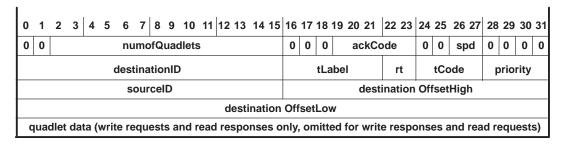

|    |        | 7.1.3 Quadlet Receive                                                                                   |      |

|    |        | 7.1.4 Block Receive                                                                                     |      |

|    | 7.2    | Isochronous Transmit (Data-Mover Port to TSB12LV32)                                                     |      |

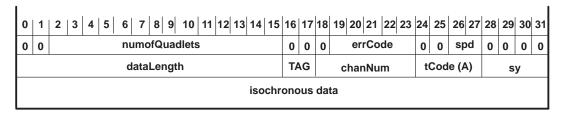

|    | 1.2    | 7.2.1 Isochronous Receive (TSB12LV32 to Microcontroller Interface/Data-Mover Port)                      |      |

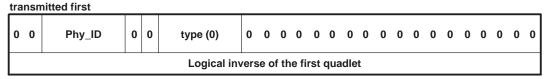

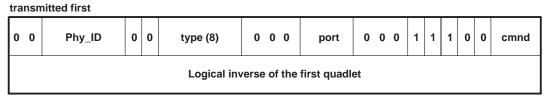

|    | 7.3    | Phy Configuration                                                                                       |      |

|    | 7.0    | 7.3.1 Extended Phy Packets                                                                              |      |

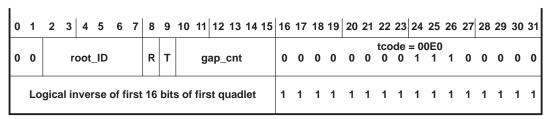

|    | 7.4    | Receive Self-ID Packet                                                                                  |      |

| 8  |        | _V32/Phy Interface                                                                                      |      |

| •  | 8.1    | Principles of Operation                                                                                 |      |

|    | 8.2    | TSB12LV32 Service Request                                                                               |      |

|    | 8.3    | Status Transfer                                                                                         |      |

|    | 8.4    | Receive Operation                                                                                       |      |

|    | 8.5    | Transmit Operation                                                                                      |      |

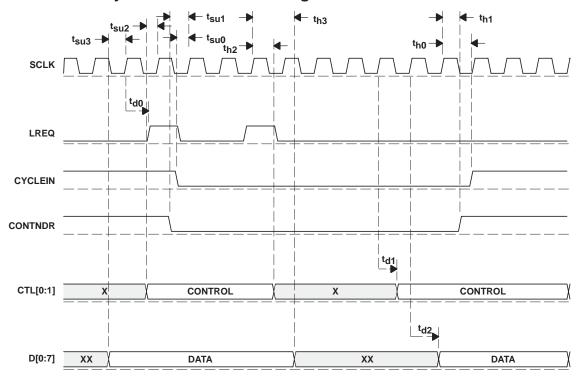

|    | 8.6    | TSB12LV32/Phy Interface Critical Timing                                                                 |      |

| 9  |        | eal Characteristics                                                                                     |      |

| •  | 9.1    | Absolute Maximum Ratings Over Operating Free-Air Temperature Range                                      |      |

|    | 9.2    | Recommended Operating Conditions                                                                        |      |

|    | 9.3    | Electrical Characteristics Over Recommended Ranges of Supply Voltage and Operating Free-Air Temperature | r    |

| 10 | Mecha  | nical Information                                                                                       |      |

|    | Hoona  |                                                                                                         |      |

# **List of Illustrations**

| 1-1 TSB12LV32 Functional Block Diagram       2         3-1 Microcontroller Byte Stack (Write) Operation       26         3-2 Microcontroller Byte Unstack (Read) Operation       27         3-3 Byte Handshake Read       28         3-4 Word Handshake Read       28         3-5 Byte Handshake Write       30         3-6 Word Handshake Write       30         3-7 Byte Fixed-Timing Read       31         3-8 Word Fixed-Timing Read       31         3-9 Byte Fixed-Timing Write       32         3-9 Byte Fixed-Timing Write       32         3-10 Word Fixed-Timing Write       33         3-11 GRF Read Access (Byte Fixed-Timing Mode)       34         3-12 GoldFire Read       36         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-15 Big Endian Format       38         3-17 Little Endian Address-Invariance Illustration Chart       39         4-1 Link Core Components       41         4-1 Link Core Components       41         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header Insertion       48         5-7 Isochronous Transmit With Auto Header In                                                                                                                                                                                                                                                                      | Figure                                                        | Title            | Page |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------|------------------|------|

| 3-2 Microcontroller Byte Unstack (Read) Operation         27           3-3 Byte Handshake Read         28           3-4 Word Handshake Read         28           3-5 Byte Handshake Write         29           3-6 Word Handshake Write         30           3-7 Byte Fixed-Timing Read         31           3-8 Word Fixed-Timing Write         32           3-9 Byte Fixed-Timing Write         32           3-10 Word Fixed-Timing Write         32           3-11 OWord Fixed-Timing Write         33           3-12 GRF Read Access (Byte Fixed-Timing Mode)         34           3-12 GRF Read Access (Word Fixed-Timing Mode)         34           3-13 ColdFire Read         36           3-14 ColdFire Write         37           3-15 Big Endian Format         38           3-16 Big Endian Format         38           3-17 Little Endian Data-Invariance Illustration Chart         39           3-19 Little-Endian Address-Invariance Illustration Chart         40           4-1 Link Core Components         41           5-1 A Typical System Diagram         45           5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)         47           5-5 Isochronous Receive With Header and Trailer Removal         48           5-7 Isochronous                                                                                                                                                                                                                           | 1–1 TSB12LV32 Functional Block Diagram                        |                  | 2    |

| 3-3 Byte Handshake Read       28         3-4 Word Handshake Read       28         3-5 Byte Handshake Write       29         3-6 Word Handshake Write       30         3-7 Byte Fixed-Timing Read       31         3-8 Word Fixed-Timing Read       31         3-9 Byte Fixed-Timing Write       32         3-10 Word Fixed-Timing Write       32         3-11 GRF Read Access (Byte Fixed-Timing Mode)       34         3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-19 Little-Endian Address-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header Insertion       48 <t< td=""><td>3-1 Microcontroller Byte Stack (Write) Operation</td><td></td><td> 26</td></t<>                                                                                                                                                                               | 3-1 Microcontroller Byte Stack (Write) Operation              |                  | 26   |

| 3-4 Word Handshake Read       28         3-5 Byte Handshake Write       29         3-6 Word Handshake Write       30         3-7 Byte Fixed-Timing Read       31         3-8 Word Fixed-Timing Read       31         3-9 Byte Fixed-Timing Write       32         3-10 Word Fixed-Timing Write       32         3-10 Word Fixed-Timing Write       33         3-11 ORF Read Access (Byte Fixed-Timing Mode)       34         3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Address-Invariance Illustration Chart       39         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer Removal       48         5-7 Isochronous Receive With Header and Trailer Removal       59         5-8 Isochronou                                                                                                                                                                                                                                                                      | 3-2 Microcontroller Byte Unstack (Read) Operation .           |                  | 27   |

| 3–5 Byte Handshake Write         29           3–6 Word Handshake Write         30           3–7 Byte Fixed-Timing Read         31           3–8 Word Fixed-Timing Write         32           3–9 Byte Fixed-Timing Write         32           3–10 Word Fixed-Timing Write         33           3–11 QRF Read Access (Byte Fixed-Timing Mode)         34           3–12 QRF Read Access (Word Fixed-Timing Mode)         34           3–13 ColdFire Read         36           3–14 ColdFire Write         37           3–15 Microcontroller Timing         37           3–15 Little Endian Format         38           3–17 Little Endian Data-Invariance Illustration Chart         38           3–18 Little-Endian Data-Invariance Illustration Chart         40           4–1 Link Core Components         41           5–1 A Typical System Diagram         45           5–2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)         46           5–3 Transmit Data Path         46           5–4 Asynchronous Transmit With Auto Header Insertion         49           5–8 Isochronous Receive With Header and Trailer         48           5–7 Isochronous Transmit With Auto Header Insertion         59           5–8 Isochronous Transmit With Auto Header Insertion         50                                                                                                                                                                                                                  | 3–3 Byte Handshake Read                                       |                  | 28   |

| 3-6 Word Handshake Write       30         3-7 Byte Fixed-Timing Read       31         3-8 Word Fixed-Timing Read       31         3-9 Byte Fixed-Timing Write       32         3-10 Word Fixed-Timing Write       32         3-11 GRF Read Access (Byte Fixed-Timing Mode)       34         3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-12 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 I sochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 I sochronous Receive With Auto Header Insertion       48         5-6 I sochronous Receive With Auto Header Insertion       50         5-9 Asynchronous Transmit With Auto Header Insertion       50         5-10 Asynchronous                                                                                                                                                                                                                                    | 3–4 Word Handshake Read                                       |                  | 28   |

| 3-7 Byte Fixed-Timing Read       31         3-8 Word Fixed-Timing Read       31         3-9 Byte Fixed-Timing Write       32         3-10 Word Fixed-Timing Write       33         3-11 GRF Read Access (Byte Fixed-Timing Mode)       34         3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Transmit With Auto Header Insertion       59         5-7 Isochronous Transmit With Auto Header Insertion       50         5-9 Asynchronous Transmit With Auto Header Insertion       52         5-10 Asynchr                                                                                                                                                                                                                                   | 3–5 Byte Handshake Write                                      |                  | 29   |

| 3-8 Word Fixed-Timing Read       31         3-9 Byte Fixed-Timing Write       32         3-10 Word Fixed-Timing Write       33         3-11 GRF Read Access (Byte Fixed-Timing Mode)       34         3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Auto Header Insertion       50         5-8 Isochronous Receive With Header and Trailer Removal       51         5-10 Asynchronous Receive With Header and Trailer Removal       51         5-10 Asynchronous Transmit With Auto Header Insertion<                                                                                                                                                                                                | 3–6 Word Handshake Write                                      |                  | 30   |

| 3-9 Byte Fixed-Timing Write       32         3-10 Word Fixed-Timing Write       33         3-11 GRF Read Access (Byte Fixed-Timing Mode)       34         3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer Removal       48         5-7 Isochronous Transmit With Auto Header Insertion       50         5-8 Isochronous Receive With Headers and Trailer Removal       51         5-9 Asynchronous Receive With Headers and Trailer Removal       51         5-10 Asynchronous Transmit With Auto Header Insertion       50 <t< td=""><td>3–7 Byte Fixed-Timing Read</td><td></td><td> 31</td></t<>                                                                                                                               | 3–7 Byte Fixed-Timing Read                                    |                  | 31   |

| 3-10 Word Fixed-Timing Write       33         3-11 GRF Read Access (Byte Fixed-Timing Mode)       34         3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Transmit With Auto Header Insertion       49         5-8 Isochronous Transmit With Auto Header Insertion       50         5-9 Asynchronous Receive With Headers and Trailer Removal       51         5-10 Asynchronous Receive With Header and Trailer Removal       51         5-10 Asynchronous Receive With Header Insertion       53         5-11 A                                                                                                                                                                                                | 3–8 Word Fixed-Timing Read                                    |                  | 31   |

| 3-11 GRF Read Access (Byte Fixed-Timing Mode)       34         3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer       48         5-7 Isochronous Transmit With Auto Header Insertion       50         5-8 Isochronous Receive With Headers and Trailer       50         5-9 Asynchronous Receive With Headers and Trailer Removal       51         5-10 Asynchronous Receive With Headers and Trailer       52         5-11 Asynchronous Transmit With Auto Header Insertion       52                                                                                                                                                                                                | 3–9 Byte Fixed-Timing Write                                   |                  | 32   |

| 3-12 GRF Read Access (Word Fixed-Timing Mode)       34         3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer       48         5-7 Isochronous Transmit With Auto Header Insertion       50         5-8 Isochronous Receive With Header and Trailer Removal       51         5-9 Asynchronous Receive With Header and Trailer Removal       51         5-9 Asynchronous Receive With Header and Trailer Removal       51         5-10 Asynchronous Transmit With Auto Header Insertion       52         5-11 Asynchronous Transmit With Auto Header Insertion       52                                                                                                                                                                            | 3-10 Word Fixed-Timing Write                                  |                  | 33   |

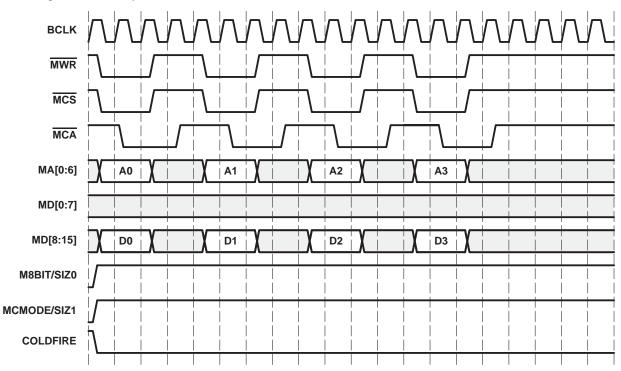

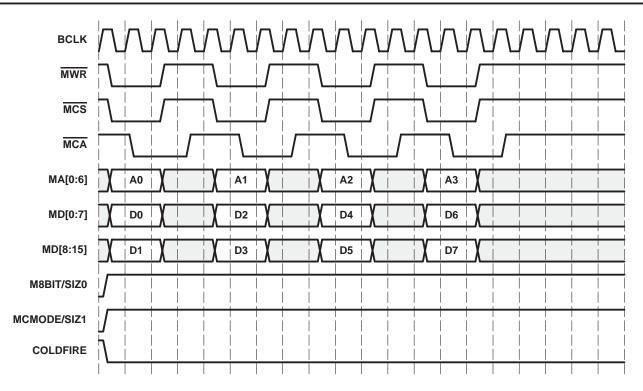

| 3-13 ColdFire Read       36         3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer Removal       48         5-7 Isochronous Transmit With Auto Header Insertion       50         5-9 Asynchronous Receive With Headers and Trailer Removal       51         5-10 Asynchronous Receive With Header and Trailer Removal       51         5-11 Asynchronous Transmit With Auto Header Insertion       53         5-12 Asynchronous Transmit With Auto Header Insertion       53         5-13 Isochronous Transmit With Auto Header Insertion       54         5-14 Isochronous Transmit With Auto Header Insertion at 400 Mb                                                                                                                                                             | 3-11 GRF Read Access (Byte Fixed-Timing Mode)                 |                  | 34   |

| 3-14 ColdFire Write       37         3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer Removal       48         5-7 Isochronous Transmit With Auto Header Insertion       50         5-8 Isochronous Transmit Without Auto Header Insertion       50         5-9 Asynchronous Receive With Headers and Trailer Removal       51         5-10 Asynchronous Transmit With Auto Header Insertion       53         5-12 Asynchronous Transmit With Auto Header Insertion       54         5-13 Isochronous Transmit With Auto Header Insertion       54         5-14 Isochronous Transmit With Auto Header Insertion at 400 Mbps       55         5-15 Isochronous Tr                                                                                                                                                             | 3-12 GRF Read Access (Word Fixed-Timing Mode) .               |                  | 34   |

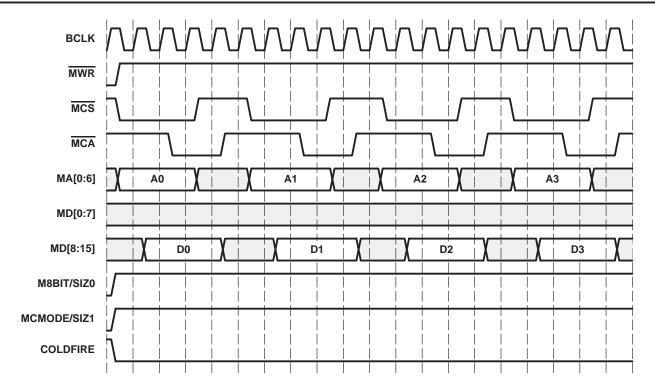

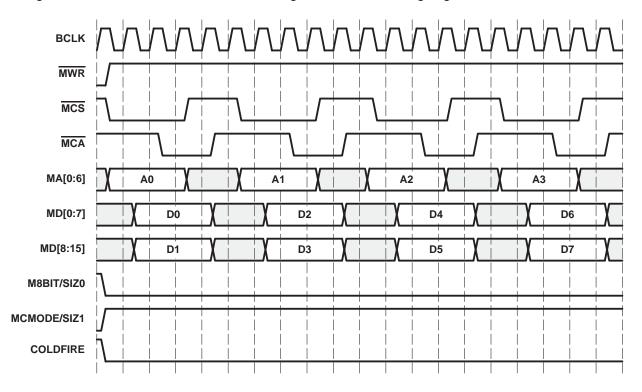

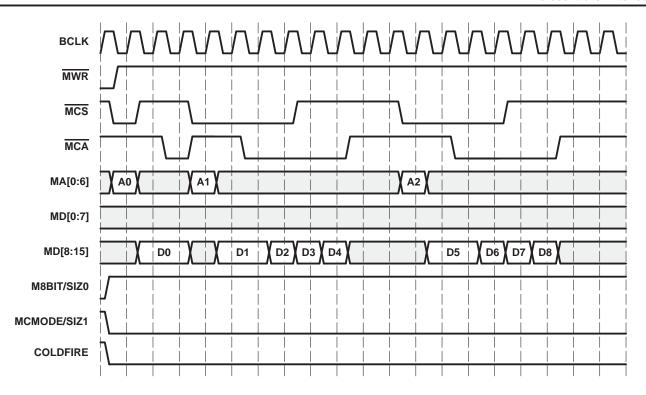

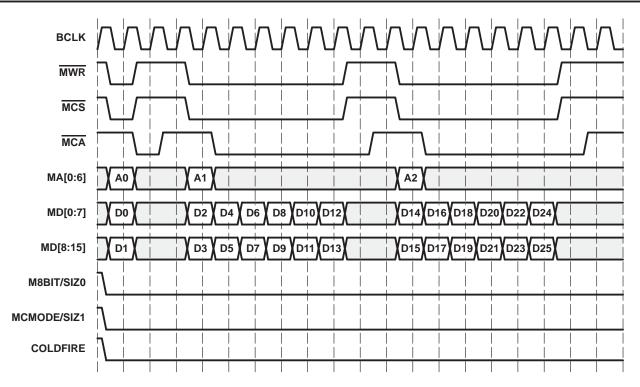

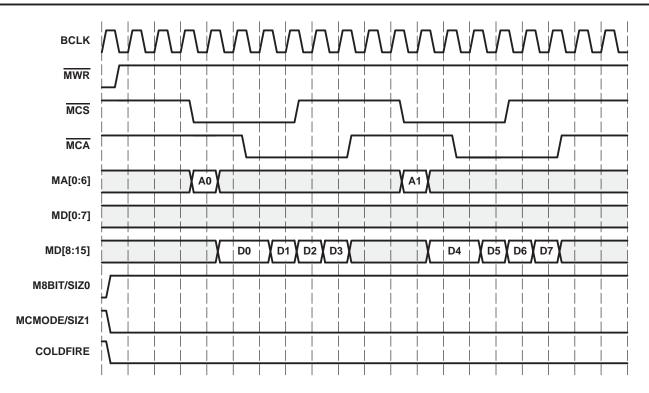

| 3-15 Microcontroller Timing       37         3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer       48         5-7 Isochronous Transmit With Auto Header Insertion       50         5-8 Isochronous Receive Without Header and Trailer Removal       51         5-9 Asynchronous Receive With Headers and Trailer Removal       51         5-10 Asynchronous Transmit With Auto Header Insertion       52         5-11 Asynchronous Transmit With Auto Header Insertion       53         5-12 Asynchronous Transmit With Auto Header Insertion at 400 Mbps       55         5-14 Isochronous Transmit With Auto Header Insertion at 200 Mbps       55         5-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps       56                                                                                                                                   | 3–13 ColdFire Read                                            |                  | 36   |

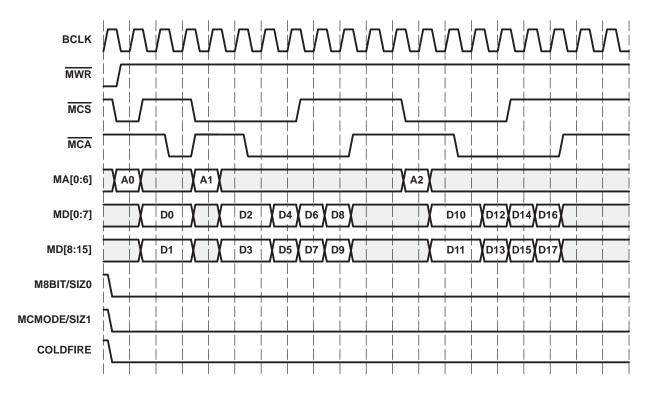

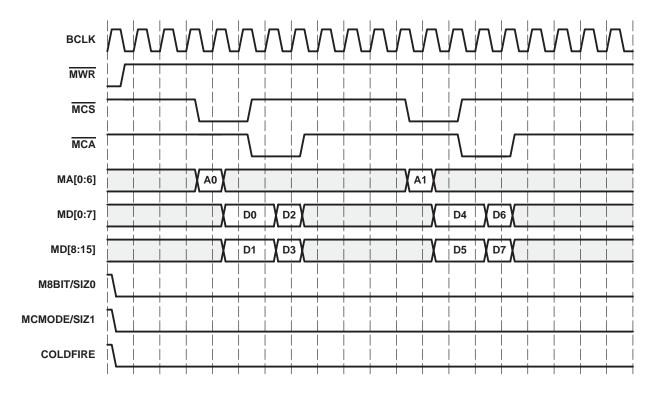

| 3-16 Big Endian Format       38         3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer Removal       48         5-7 Isochronous Transmit With Auto Header Insertion       50         5-9 Asynchronous Receive Without Header and Trailer Removal       51         5-9 Asynchronous Receive Without Header and Trailer Removal       51         5-10 Asynchronous Receive With Headers and Trailer       52         5-11 Asynchronous Transmit With Auto Header Insertion       53         5-12 Asynchronous Transmit With Auto Header Insertion       54         5-13 Isochronous Transmit With Auto Header Insertion at 400 Mbps       55         5-15 Isochronous Transmit With Auto Header Insertion at 200 Mbps       55         5-15 Isochronous Transmit With Auto Header Insert                                                                                                                          | 3–14 ColdFire Write                                           |                  | 37   |

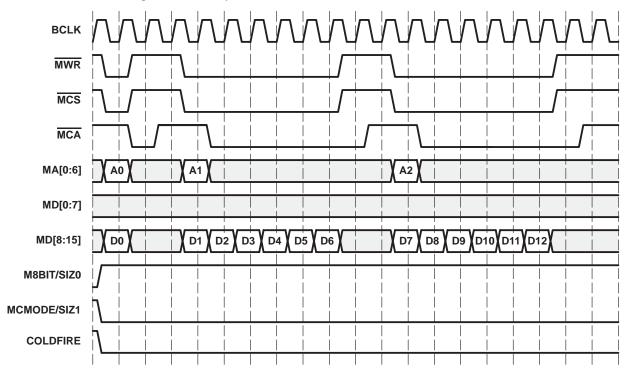

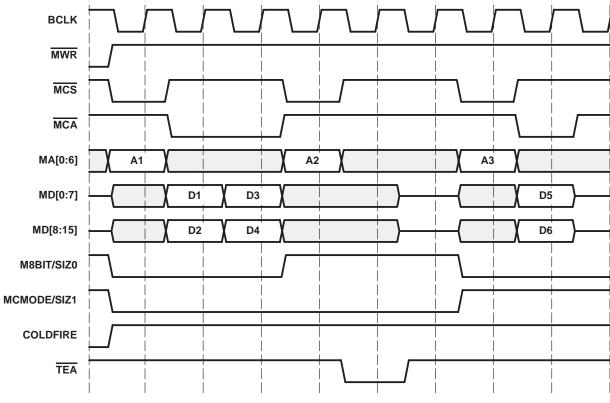

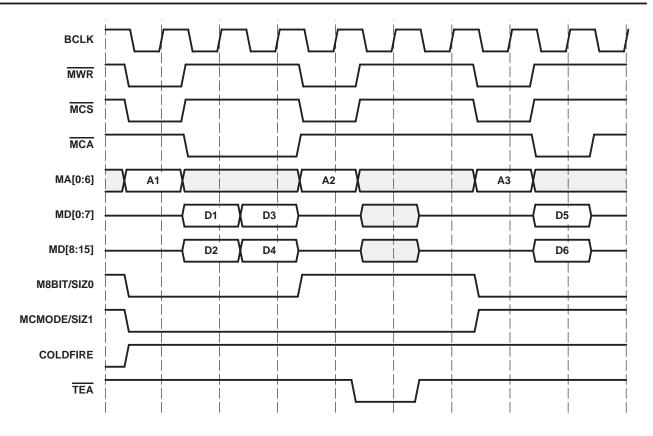

| 3-17 Little Endian Format       38         3-18 Little-Endian Data-Invariance Illustration Chart       39         3-19 Little-Endian Address-Invariance Illustration Chart       40         4-1 Link Core Components       41         5-1 A Typical System Diagram       45         5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)       46         5-3 Transmit Data Path       46         5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)       47         5-5 Isochronous Receive With Auto Header and Trailer Removal       48         5-6 Isochronous Receive With Header and Trailer       48         5-7 Isochronous Transmit With Auto Header Insertion       50         5-8 Isochronous Transmit Without Auto Header Insertion       50         5-9 Asynchronous Receive Without Header and Trailer Removal       51         5-10 Asynchronous Receive With Headers and Trailer       52         5-11 Asynchronous Transmit With Auto Header Insertion       53         5-12 Asynchronous Transmit With Auto Header Insertion       54         5-13 Isochronous Transmit With Auto Header Insertion at 400 Mbps       55         5-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps       56                                                                                                                                                                                                                                         | 3–15 Microcontroller Timing                                   |                  | 37   |

| 3-18 Little-Endian Data-Invariance Illustration Chart                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 3–16 Big Endian Format                                        |                  | 38   |

| 3–19 Little-Endian Address-Invariance Illustration Chart 40 4–1 Link Core Components 41 5–1 A Typical System Diagram 45 5–2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) 46 5–3 Transmit Data Path 46 5–4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1) 47 5–5 Isochronous Receive With Auto Header and Trailer Removal 48 5–6 Isochronous Receive With Header and Trailer 8 5–7 Isochronous Transmit With Auto Header Insertion 49 5–8 Isochronous Transmit Without Auto Header Insertion 50 5–9 Asynchronous Receive Without Header and Trailer 8 5–10 Asynchronous Receive With Headers and Trailer 8 5–11 Asynchronous Transmit With Auto Header Insertion 53 5–12 Asynchronous Transmit With Auto Header Insertion 54 5–13 Isochronous Transmit With Auto Header Insertion 55 5–14 Isochronous Transmit With Auto Header Insertion at 400 Mbps 55 5–15 Isochronous Transmit With Auto Header Insertion at 200 Mbps 55 5–15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 3–17 Little Endian Format                                     |                  | 38   |

| 4–1 Link Core Components415–1 A Typical System Diagram455–2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus)465–3 Transmit Data Path465–4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1)475–5 Isochronous Receive With Auto Header and Trailer Removal485–6 Isochronous Receive With Header and Trailer485–7 Isochronous Transmit With Auto Header Insertion495–8 Isochronous Transmit Without Auto Header Insertion505–9 Asynchronous Receive Without Header and Trailer Removal515–10 Asynchronous Receive With Headers and Trailer525–11 Asynchronous Transmit With Auto Header Insertion535–12 Asynchronous Transmit With Auto Header Insertion545–13 Isochronous Transmit With Auto Header Insertion at 400 Mbps555–14 Isochronous Transmit With Auto Header Insertion at 200 Mbps555–15 Isochronous Transmit With Auto Header Insertion at 100 Mbps56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | $3\!-\!18$ Little-Endian Data-Invariance Illustration Chart . |                  | 39   |

| 5-1 A Typical System Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                               |                  |      |

| 5-2 Isochronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) 5-3 Transmit Data Path 5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1) 5-5 Isochronous Receive With Auto Header and Trailer Removal 5-6 Isochronous Receive With Header and Trailer 5-7 Isochronous Transmit With Auto Header Insertion 5-8 Isochronous Transmit Without Auto Header Insertion 5-9 Asynchronous Receive Without Header and Trailer Removal 5-10 Asynchronous Receive With Headers and Trailer 5-11 Asynchronous Transmit With Auto Header Insertion 5-12 Asynchronous Transmit With Auto Header Insertion 5-13 Isochronous Transmit With Auto Header Insertion 5-14 Isochronous Transmit With Auto Header Insertion at 400 Mbps 5-15 Isochronous Transmit With Auto Header Insertion at 200 Mbps 5-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-16 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-17 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-17 Isochronous Transmit With Auto Header Insertion at 100 Mbps 5-6-18 Isochronous Transmit With Auto Header Insertion at 100 Mbps | ·                                                             |                  |      |

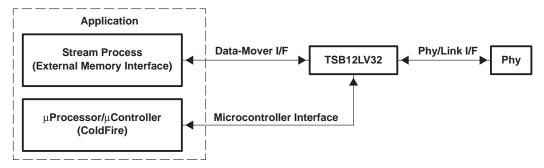

| 5–3 Transmit Data Path                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 5–1 A Typical System Diagram                                  |                  | 45   |

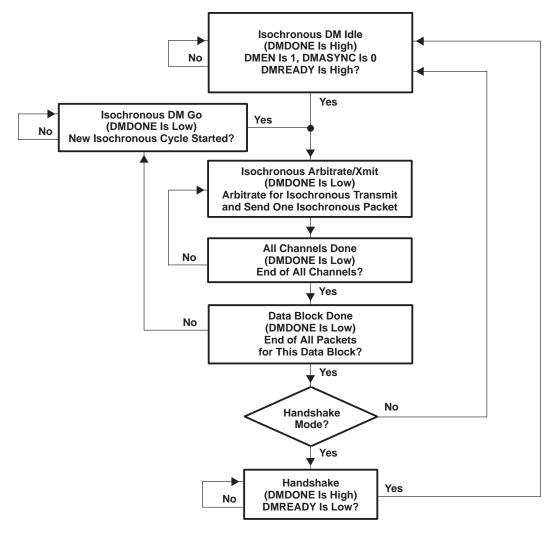

| 5-4 Asynchronous Transmit DM Flow Control (TSB12LV32 Transmit to 1394 Bus) (DMASYNC = 1) 47 5-5 Isochronous Receive With Auto Header and Trailer Removal 48 5-6 Isochronous Receive With Header and Trailer 48 5-7 Isochronous Transmit With Auto Header Insertion 49 5-8 Isochronous Transmit Without Auto Header Insertion 50 5-9 Asynchronous Receive Without Header and Trailer Removal 51 5-10 Asynchronous Receive With Headers and Trailer 52 5-11 Asynchronous Transmit With Auto Header Insertion 53 5-12 Asynchronous Transmit Without Auto Header Insertion 54 5-13 Isochronous Transmit With Auto Header Insertion at 400 Mbps 55 5-14 Isochronous Transmit With Auto Header Insertion at 200 Mbps 55 5-15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | •                                                             | ,                |      |

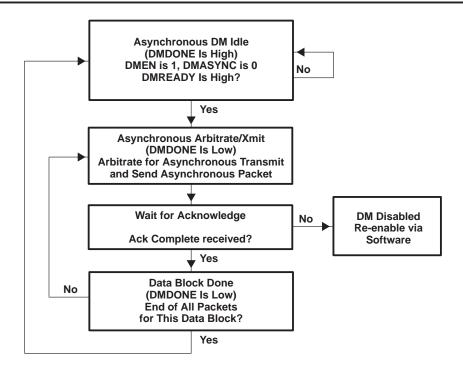

| 5–5 Isochronous Receive With Auto Header and Trailer Removal485–6 Isochronous Receive With Header and Trailer485–7 Isochronous Transmit With Auto Header Insertion495–8 Isochronous Transmit Without Auto Header Insertion505–9 Asynchronous Receive Without Header and Trailer Removal515–10 Asynchronous Receive With Headers and Trailer525–11 Asynchronous Transmit With Auto Header Insertion535–12 Asynchronous Transmit Without Auto Header Insertion545–13 Isochronous Transmit With Auto Header Insertion at 400 Mbps555–14 Isochronous Transmit With Auto Header Insertion at 200 Mbps555–15 Isochronous Transmit With Auto Header Insertion at 100 Mbps56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                               |                  |      |

| 5–6 Isochronous Receive With Header and Trailer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                               |                  |      |

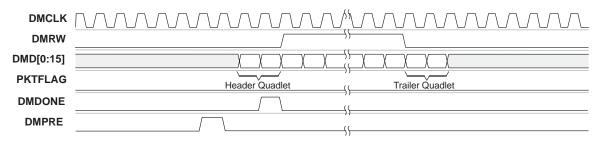

| 5–7 Isochronous Transmit With Auto Header Insertion495–8 Isochronous Transmit Without Auto Header Insertion505–9 Asynchronous Receive Without Header and Trailer Removal515–10 Asynchronous Receive With Headers and Trailer525–11 Asynchronous Transmit With Auto Header Insertion535–12 Asynchronous Transmit Without Auto Header Insertion545–13 Isochronous Transmit With Auto Header Insertion at 400 Mbps555–14 Isochronous Transmit With Auto Header Insertion at 200 Mbps555–15 Isochronous Transmit With Auto Header Insertion at 100 Mbps56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 5-5 Isochronous Receive With Auto Header and Trail            | er Removal       | 48   |

| 5–8 Isochronous Transmit Without Auto Header Insertion505–9 Asynchronous Receive Without Header and Trailer Removal515–10 Asynchronous Receive With Headers and Trailer525–11 Asynchronous Transmit With Auto Header Insertion535–12 Asynchronous Transmit Without Auto Header Insertion545–13 Isochronous Transmit With Auto Header Insertion at 400 Mbps555–14 Isochronous Transmit With Auto Header Insertion at 200 Mbps555–15 Isochronous Transmit With Auto Header Insertion at 100 Mbps56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-6 Isochronous Receive With Header and Trailer               |                  | 48   |

| 5–9 Asynchronous Receive Without Header and Trailer Removal 51 5–10 Asynchronous Receive With Headers and Trailer 52 5–11 Asynchronous Transmit With Auto Header Insertion 53 5–12 Asynchronous Transmit Without Auto Header Insertion 54 5–13 Isochronous Transmit With Auto Header Insertion at 400 Mbps 55 5–14 Isochronous Transmit With Auto Header Insertion at 200 Mbps 55 5–15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                               |                  |      |

| 5–10 Asynchronous Receive With Headers and Trailer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-8 Isochronous Transmit Without Auto Header Inser            | tion             | 50   |

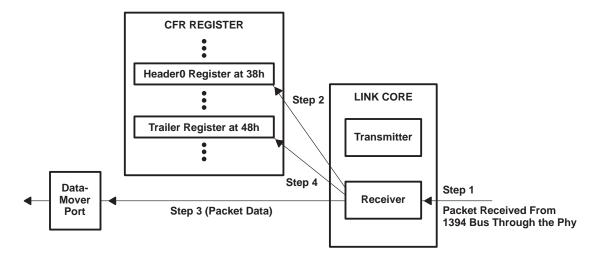

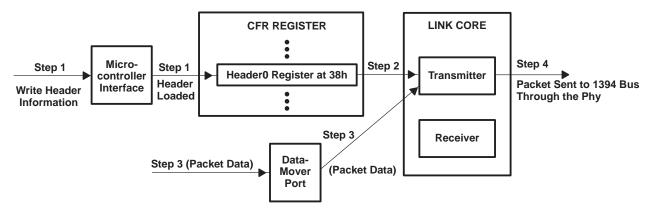

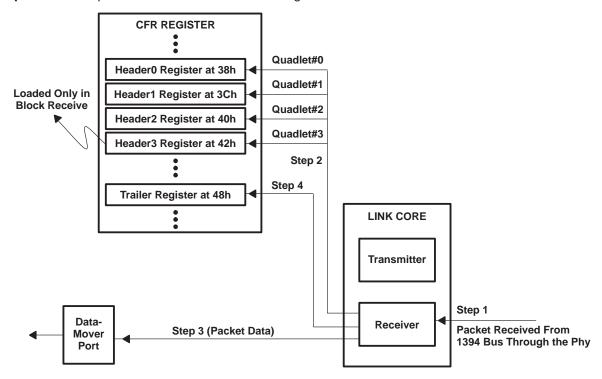

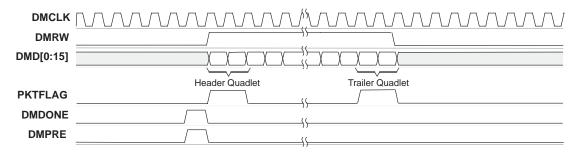

| 5–11 Asynchronous Transmit With Auto Header Insertion 53 5–12 Asynchronous Transmit Without Auto Header Insertion 54 5–13 Isochronous Transmit With Auto Header Insertion at 400 Mbps 55 5–14 Isochronous Transmit With Auto Header Insertion at 200 Mbps 55 5–15 Isochronous Transmit With Auto Header Insertion at 100 Mbps 56                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-9 Asynchronous Receive Without Header and Traile            | er Removal       | 51   |

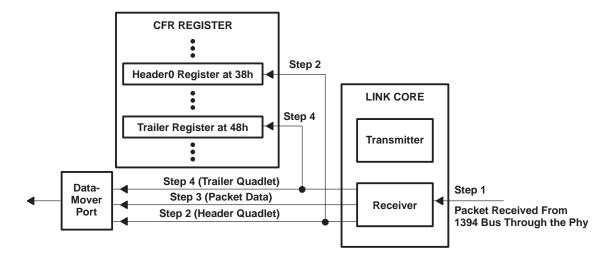

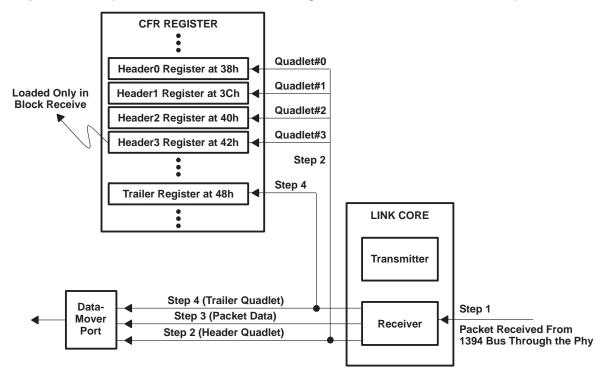

| 5–12 Asynchronous Transmit Without Auto Header Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 5-10 Asynchronous Receive With Headers and Traile             | er               | 52   |

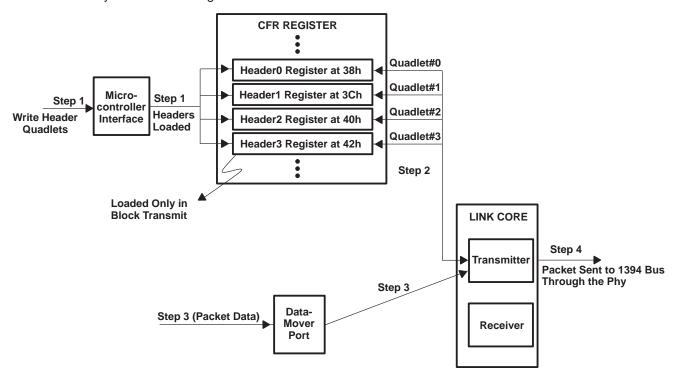

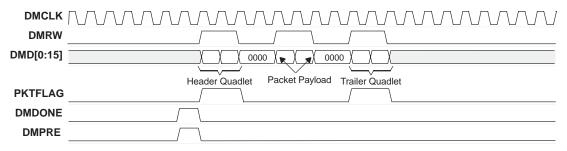

| 5-13 Isochronous Transmit With Auto Header Insertion at 400 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | •                                                             |                  |      |

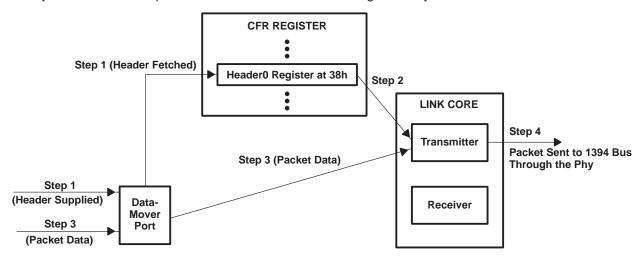

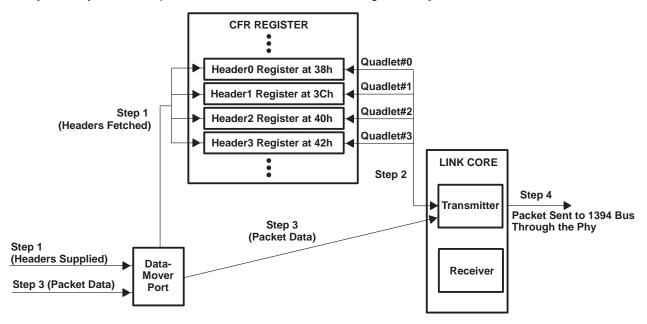

| 5-14 Isochronous Transmit With Auto Header Insertion at 200 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-12 Asynchronous Transmit Without Auto Header In             | sertion          | 54   |

| 5–15 Isochronous Transmit With Auto Header Insertion at 100 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5-13 Isochronous Transmit With Auto Header Insertic           | on at 400 Mbps   | 55   |

| ·                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 5-14 Isochronous Transmit With Auto Header Insertic           | on at 200 Mbps   | 55   |

| 5–16 Isochronous Transmit Without Auto Header Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                               | ·                |      |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                               |                  |      |

| 5–17 Isochronous Receive With Automatic Header and Trailer Removal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                               |                  |      |

| 5–18 Isochronous Receive With Header and Trailer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                               |                  |      |

| 5–19 Isochronous Receive With Header and Trailer at 200 Mbps                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                               | •                |      |

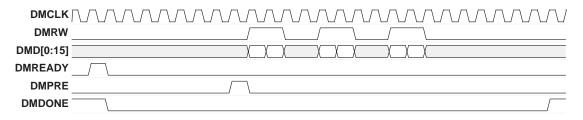

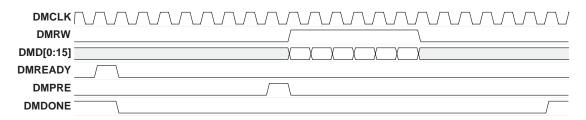

| 5–20 Asynchronous Quadlet Transmit With Automatic Header Insertion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5-20 Asynchronous Quadlet Transmit With Automatic             | Header Insertion | 59   |

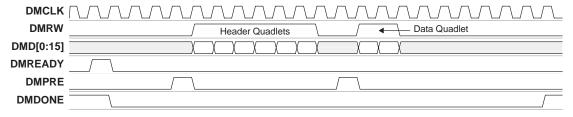

| 5–21 Asynchronous Block Transmit With Automatic Header Insertion at 200 Mbps            | 59 |

|-----------------------------------------------------------------------------------------|----|

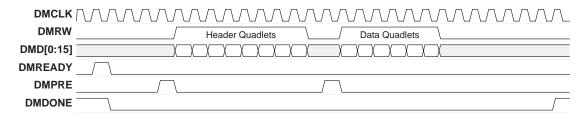

| 5–22 Asynchronous Block Transmit With Automatic Header Insertion at 400 Mbps            | 59 |

| 5-23 Asynchronous Quadlet Transmit Without Automatic Header Insertion at 400 Mbps       | 60 |

| 5–24 Asynchronous Block Transmit Without Automatic Header Insertion at 400 Mbps         | 60 |

| 5–25 Asynchronous Quadlet Receive With Headers and Trailer at 400 Mbps                  | 61 |

| 5–26 Asynchronous Block Receive With Headers and Trailer at 400 Mbps                    | 61 |

| 5–27 Asynchronous Quadlet Receive With Automatic Header and Trailer Removal at 400 Mbps | 62 |

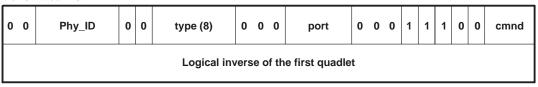

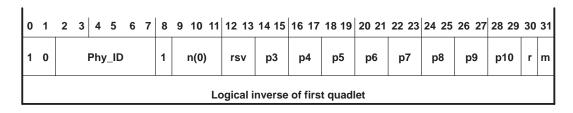

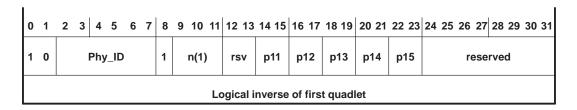

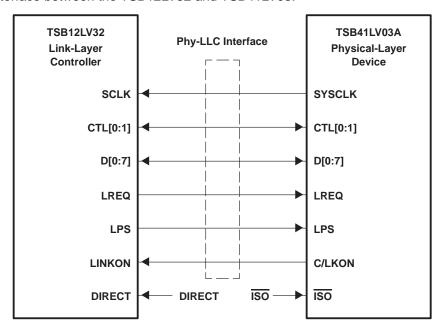

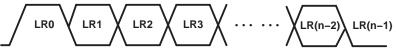

| 5–28 Asynchronous Block Receive With Automatic Header and Trailer Removal at 400 Mbps   | 62 |