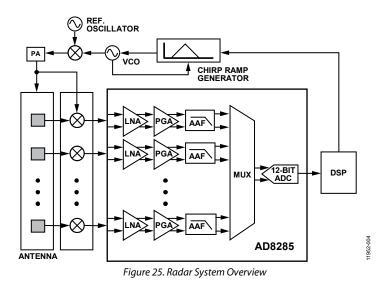

## Radar Receive Path AFE: 4-Channel LNA/PGA/AAF with ADC

### **Data Sheet**

## AD8285

#### FEATURES

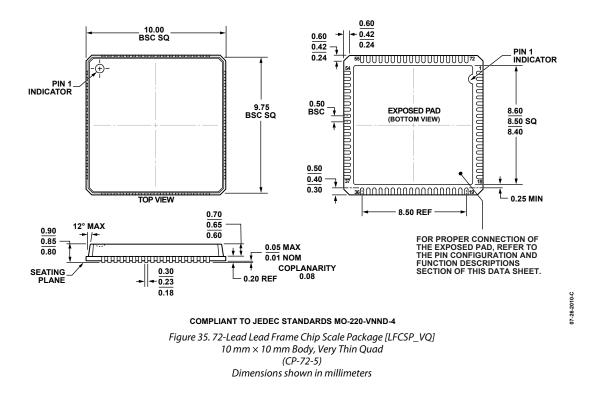

4 channel LNA, PGA, and AAF 1 direct-to-ADC channel Programmable gain amplifier (PGA) Includes low noise preamplifier (LNA) Serial peripheral interface (SPI) programmable gain 16 dB to 34 dB in 6 dB steps Antialiasing filter (AAF) Programmable third-order, low-pass elliptic filter (LPF) from 1.0 MHz to 12.0 MHz Analog-to-digital converter (ADC) 12 bits of accuracy up to 72 MSPS Signal-to-noise ratio (SNR): 68.5 dB Spurious-free dynamic range(SFDR): 68 dB at gain = 16 dB Low power: 185 mW per channel at 12 bits and 72 MSPS Low noise: 3.5 nV/√Hz maximum of input referred voltage noise Power-down mode 72-lead, 10 mm × 10 mm LFCSP package Specified from -40°C to +105°C **Qualified for automotive applications**

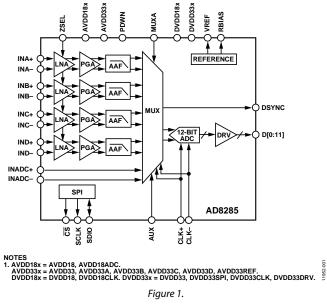

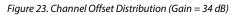

#### FUNCTIONAL BLOCK DIAGRAM

#### APPLICATIONS

Automotive radar Adaptive cruise control Collision avoidance Blind spot detection Self parking Electronic bumper

#### **GENERAL DESCRIPTION**

The AD8285 is designed for low cost, low power, compact size, flexibility, and ease of use. It contains four channels of a low noise preamplifier (LNA) with a programmable gain amplifier (PGA) and an antialiasing filter (AAF) plus one direct-to-ADC channel, all integrated with a single 12-bit analog-to-digital converter (ADC).

Each channel features a gain range of 16 dB to 34 dB in 6 dB increments and an ADC with a conversion rate of up to 72 MSPS. The combined input referred noise voltage of the entire channel

is 3.5 nV/ $\sqrt{\text{Hz}}$  at maximum gain. The channel is optimized for dynamic performance and low power in applications where a small package size is critical.

Fabricated in an advanced complementary metal oxide semiconductor (CMOS) process, the AD8285 is available in a 10 mm  $\times$  10 mm, RoHS compliant, 72-lead LFCSP that is specified over the automotive temperature range of  $-40^{\circ}$ C to  $+105^{\circ}$ C.

Rev. 0

#### Document Feedback

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2014 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

## TABLE OF CONTENTS

| SDIO Pin17                                          |

|-----------------------------------------------------|

| SCLK Pin 17                                         |

| CS Pin                                              |

| RBIAS Pin17                                         |

| Voltage Reference                                   |

| Power and Ground Recommendations                    |

| Exposed Paddle Thermal Heat Slug Recommendations 18 |

| Serial Peripheral Interface (SPI) 19                |

| Hardware Interface19                                |

| Memory Map 21                                       |

| Reading the Memory Map Table21                      |

| Logic Levels                                        |

| Reserved Locations                                  |

| Default Values                                      |

| Application Diagrams                                |

| Outline Dimensions                                  |

| Ordering Guide27                                    |

| Automotive Products                                 |

#### **REVISION HISTORY**

5/14—Revision 0: Initial Version

## **SPECIFICATIONS**

#### AC SPECIFICATIONS

AVDD18 = AVDD18ADC = 1.8 V, AVDD33 = AVDD33x<sup>1</sup> = AVDD33REF = 3.3 V, DVDD18 = DVDD18CLK = 1.8 V, DVDD33SPI = DVDD33CLK = DVDD33DRV = 3.3 V, 1.024 V internal ADC reference,  $f_{IN}$  = 2.5 MHz,  $f_{SAMPLE}$  = 72 MSPS,  $R_S$  = 50  $\Omega$ , LNA + PGA gain = 34 dB, LPF cutoff =  $f_{SAMPLECH}/4$ , full channel mode, 12-bit operation, temperature =  $-40^{\circ}$ C to  $+105^{\circ}$ C, unless otherwise noted.

| Parameter <sup>2</sup>                                        | Test Conditions/Comments                                                                               | Min   | Тур         | Max        | Unit   |

|---------------------------------------------------------------|--------------------------------------------------------------------------------------------------------|-------|-------------|------------|--------|

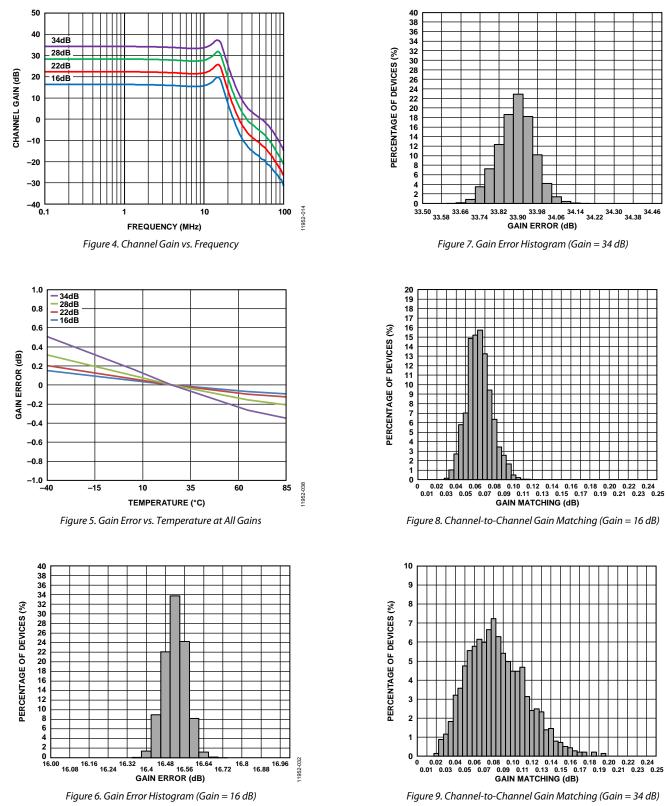

| ANALOG CHANNEL CHARACTERISTICS                                | LNA, PGA, and AAF channels                                                                             |       |             |            |        |

| Gain                                                          |                                                                                                        |       | 16/22/28/34 |            | dB     |

| Gain Range                                                    |                                                                                                        |       | 18          |            | dB     |

| Gain Error                                                    |                                                                                                        | -1.25 |             | +1.25      | dB     |

| Input Voltage Range                                           | Channel gain = 16 dB                                                                                   |       | 0.25        |            | V р-р  |

|                                                               | Channel gain = 22 dB                                                                                   |       | 0.125       |            | Vp-p   |

|                                                               | Channel gain = 28 dB                                                                                   |       | 0.0625      |            | Vp-p   |

|                                                               | Channel gain = 34 dB                                                                                   |       | 0.03125     |            | Vp-p   |

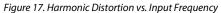

| Input Resistance                                              | 200 $\Omega$ input impedance selected                                                                  | 0.180 | 0.230       | 0.280      | kΩ     |

|                                                               | 200 k $\Omega$ input impedance selected                                                                | 160   | 200         | 240        | kΩ     |

| Input Capacitance                                             |                                                                                                        |       | 22          |            | рF     |

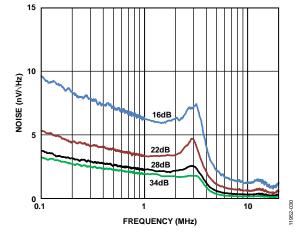

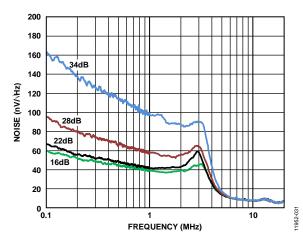

| Input Referred Voltage Noise                                  | Maximum gain at 1 MHz                                                                                  |       | 1.85        |            | nV/√H  |

|                                                               | Minimum gain at 1 MHz                                                                                  |       | 6.03        |            | nV/√H  |

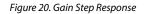

| Noise Figure                                                  | Maximum gain, $R_s = 50 \Omega$ , unterminated                                                         |       | 7.1         |            | dB     |

| J                                                             | Maximum gain, $R_s = R_{IN} = 50 \Omega$                                                               |       | 12.7        |            | dB     |

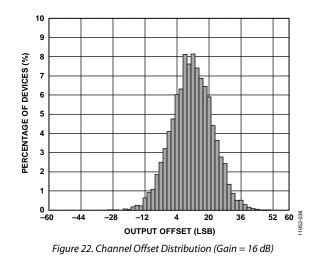

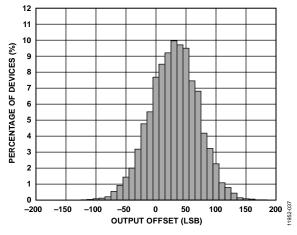

| Output Offset                                                 | Gain = 16 dB                                                                                           | -60   |             | +60        | LSB    |

|                                                               | Gain = 34 dB                                                                                           | -250  |             | +250       | LSB    |

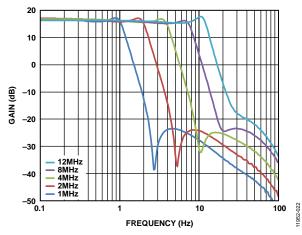

| AAF Low-Pass Filter Cutoff                                    | -3 dB, programmable                                                                                    |       | 1.0 to 12.0 |            | MHz    |

| Tolerance                                                     | After filter autotune                                                                                  | -10   | ±5          | +10        | %      |

| AAF Attenuation in Stop Band                                  | Third-order elliptic filter                                                                            |       |             |            | ,.     |

|                                                               | 2× cutoff                                                                                              |       | 30          |            | dB     |

|                                                               | 3× cutoff                                                                                              |       | 40          |            | dB     |

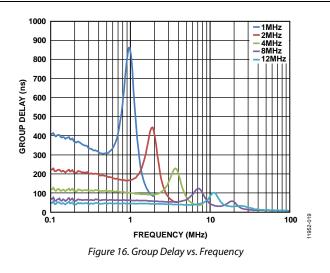

| Group Delay Variation                                         | Filter set at 2 MHz                                                                                    |       | 400         |            | ns     |

| Channel-to-Channel Phase Variation                            | Frequencies up to -3 dB                                                                                | -5    | ±0.5        | +5         | Degree |

|                                                               | $\frac{1}{4}$ of $-3$ dB frequency                                                                     | -1    | _0.0        | +1         | Degree |

| Channel-to-Channel Gain Matching                              | Frequencies up to –3 dB                                                                                | -0.5  | ±0.1        | +0.5       | dB     |

| channel to channel dair Matering                              | $\frac{1}{4}$ of $-3$ dB frequency                                                                     | -0.25 | ±0.1        | +0.25      | dB     |

| 1 dB Compression                                              | Relative to output                                                                                     | 0.25  | 9.8         | 10.25      | dBm    |

| Crosstalk                                                     |                                                                                                        |       | -70         | -55        | dBc    |

| POWER SUPPLY                                                  |                                                                                                        |       | 70          | 55         | abe    |

| AVDD18, AVDD18ADC                                             |                                                                                                        | 1.7   | 1.8         | 1.9        | v      |

| AVDD18, AVDD18ADC<br>AVDD33, AVDD33x <sup>1</sup> , AVDD33REF |                                                                                                        | 3.1   | 3.3         | 3.5        | v      |

| DVDD18, DVDD18CLK                                             |                                                                                                        | 1.7   | 1.8         | 3.5<br>1.9 | V      |

|                                                               | ,                                                                                                      | 3.1   | 3.3         | 1.9<br>3.5 | V      |

| DVDD33SPI, DVDD33CLK, DVDD33DRV                               |                                                                                                        | 5.1   | 5.5         |            |        |

| AVDD18                                                        | Full channel mode<br>Full channel mode                                                                 |       |             | 130<br>130 | mA     |

| AVDD33                                                        | Full channel mode                                                                                      |       |             |            | mA     |

| DVDD18                                                        |                                                                                                        |       |             | 22         | mA     |

| IDVDD33                                                       | Full share alwards, as signal to signal to see the                                                     |       |             | 2          | mA     |

| Total Power Dissipation Per Channel                           | Full channel mode, no signal, typical supply voltage × maximum supply current; excludes output current |       |             | 185        | mW     |

| Power-Down Dissipation                                        |                                                                                                        |       | 5           |            | mW     |

| Power Supply Rejection Ratio (PSRR)                           |                                                                                                        |       | 1.6         |            | mV/V   |

| Parameter <sup>2</sup>                   | Test Conditions/Comments                                                                           | Min | Тур   | Max | Unit |

|------------------------------------------|----------------------------------------------------------------------------------------------------|-----|-------|-----|------|

| ADC                                      |                                                                                                    |     |       |     |      |

| Resolution                               |                                                                                                    |     | 12    |     | Bits |

| Maximum Sample Rate                      |                                                                                                    |     | 72    |     | MSPS |

| Signal-to-Noise Ratio (SNR)              | $f_{IN} = 1 MHz$                                                                                   |     | 68.5  |     | dB   |

| Signal-to-Noise and Distortion (SINAD)   |                                                                                                    |     | 66    |     | dB   |

| Signal-to-Noise Ratio Full Scale (SNRFS) |                                                                                                    |     | 68    |     | dB   |

| Differential Nonlinearity (DNL)          | Guaranteed no missing codes                                                                        |     |       | 1   | LSB  |

| Integral Nonlinearity (INL)              |                                                                                                    |     |       | 10  | LSB  |

| Effective Number of Bits (ENOB)          |                                                                                                    |     | 10.67 |     | LSB  |

| ADC OUTPUT CHARACTERISTICS               |                                                                                                    |     |       |     |      |

| Maximum Capacitor Load                   | Per bit                                                                                            |     | 20    |     | рF   |

| IDVDD33 Peak Current with Capacitor Load | Peak current per bit when driving 20 pF load; can be programmed via the SPI port, if required      |     |       | 40  | mA   |

| ADC REFERENCE                            |                                                                                                    |     |       |     |      |

| Output Voltage Error                     | VREF = 1.024 V                                                                                     |     |       | ±25 | mV   |

| Load Regulation                          | At 1.0 mA, VREF = 1.024 V                                                                          |     | 2     |     | mV   |

| Input Resistance                         |                                                                                                    |     | 6     |     | kΩ   |

| FULL CHANNEL CHARACTERISTICS             | LNA, PGA, AAF, and ADC channels                                                                    |     |       |     |      |

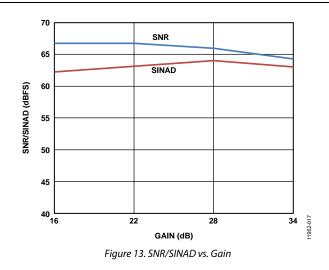

| SNRFS                                    | $f_{IN} = 1 MHz$                                                                                   |     |       |     |      |

|                                          | Gain = 16 dB                                                                                       |     | 68    |     | dB   |

|                                          | Gain = 22 dB                                                                                       |     | 68    |     | dB   |

|                                          | Gain = 28 dB                                                                                       |     | 68    |     | dB   |

|                                          | Gain = 34 dB                                                                                       |     | 66    |     | dB   |

| SINAD                                    | $f_{IN} = 1 MHz$                                                                                   |     |       |     |      |

|                                          | Gain = 16 dB                                                                                       |     | 67    |     | dB   |

|                                          | Gain = 22 dB                                                                                       |     | 68    |     | dB   |

|                                          | Gain = 28 dB                                                                                       |     | 67    |     | dB   |

|                                          | Gain = 34 dB                                                                                       |     | 66    |     | dB   |

| Spurious-Free Dynamic Range (SFDR)       | $f_{IN} = 1 MHz$                                                                                   |     |       |     |      |

|                                          | Gain = 16 dB                                                                                       |     | 68    |     | dB   |

|                                          | Gain = 22 dB                                                                                       |     | 74    |     | dB   |

|                                          | Gain = 28 dB                                                                                       |     | 74    |     | dB   |

|                                          | Gain = 34 dB                                                                                       |     | 73    |     | dB   |

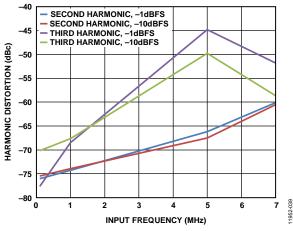

| Harmonic Distortion                      |                                                                                                    |     |       |     |      |

| Second Harmonic                          | f <sub>IN</sub> = 1 MHz at −10 dBFS, gain = 16 dB                                                  |     | -70   |     | dBc  |

| ····                                     | $f_{IN} = 1 \text{ MHz at } -10 \text{ dBFS}$ , gain = 34 dB                                       |     | -70   |     | dBc  |

| Third Harmonic                           | $f_{IN} = 1 \text{ MHz at } -10 \text{ dBFS}$ , gain = 16 dB                                       |     | -66   |     | dBc  |

|                                          | $f_{IN} = 1 \text{ MHz at } -10 \text{ dBFS}, \text{ gain} = 34 \text{ dB}$                        |     | -75   |     | dBc  |

| IM3 Distortion                           | $f_{IN1} = 1 \text{ MHz}, f_{IN2} = 1.1 \text{ MHz}, -1 \text{ dBFS}, \text{gain} = 34 \text{ dB}$ |     | -69   |     | dBc  |

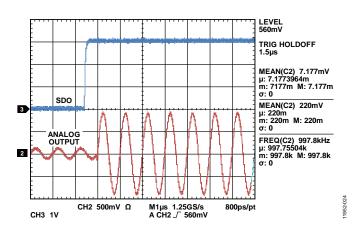

| Gain Response Time                       |                                                                                                    |     | 600   |     | ns   |

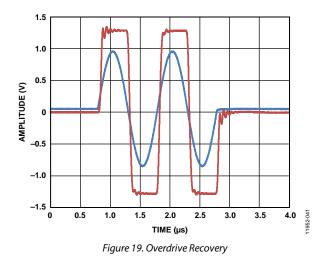

| Overdrive Recovery Time                  |                                                                                                    |     | 200   |     | ns   |

<sup>1</sup> x stands for A, B, C, or D. <sup>2</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions, and how these tests were completed.

#### **DIGITAL SPECIFICATIONS**

AVDD18 = AVDD18ADC = 1.8 V, AVDD33 = AVDD33x<sup>1</sup> = AVDD33REF = 3.3 V, DVDD18 = DVDD18CLK = 1.8 V, DVDD33SPI = DVDD33CLK = DVDD33DRV = 3.3 V, 1.024 V internal ADC reference,  $f_{IN}$  = 2.5 MHz,  $f_{SAMPLE}$  = 72 MSPS,  $R_s$  = 50  $\Omega$ , LNA + PGA gain = 34 dB, LPF cutoff =  $f_{SAMPLECH}/4$ , full channel mode, 12-bit operation, temperature =  $-40^{\circ}$ C to  $+105^{\circ}$ C, unless otherwise noted.

| Parameter <sup>2</sup>                      | Temperature | Min | Тур        | Max           | Unit   |

|---------------------------------------------|-------------|-----|------------|---------------|--------|

| CLOCK INPUTS (CLK+, CLK–)                   |             |     |            |               |        |

| Logic Compliance                            |             |     | CMOS/LVDS/ | /LVPECL       |        |

| Differential Input Voltage <sup>3</sup>     | Full        | 250 |            |               | mV p-p |

| Input Common-Mode Voltage                   | Full        |     | 1.2        |               | V      |

| Differential Input Resistance               | 25°C        |     | 20         |               | kΩ     |

| Input Capacitance                           | 25°C        |     | 1.5        |               | pF     |

| LOGIC INPUTS (PDWN, SCLK, AUX, MUXA, ZSEL)  |             |     |            |               |        |

| Logic 1 Voltage                             | Full        | 1.2 |            | 3.6           | V      |

| Logic 0 Voltage                             | Full        |     |            | 0.3           | V      |

| Input Resistance                            | 25°C        |     | 30         |               | kΩ     |

| Input Capacitance                           | 25°C        |     | 0.5        |               | рF     |

| Logic Input (CS)                            |             |     |            |               |        |

| Logic 1 Voltage                             | Full        | 1.2 |            | 3.6           | V      |

| Logic 0 Voltage                             | Full        |     |            | 0.3           | V      |

| Input Resistance                            | 25°C        |     | 70         |               | kΩ     |

| Input Capacitance                           | 25°C        |     | 0.5        |               | pF     |

| LOGIC INPUT (SDIO)                          |             |     |            |               |        |

| Logic 1 Voltage                             | Full        | 1.2 |            | DVDD33x + 0.3 | V      |

| Logic 0 Voltage                             | Full        | 0   |            | 0.3           | V      |

| Input Resistance                            | 25°C        |     | 30         |               | kΩ     |

| Input Capacitance                           | 25°C        |     | 2          |               | рF     |

| LOGIC OUTPUT (SDIO) <sup>4</sup>            |             |     |            |               |        |

| Logic 1 Voltage ( $I_{OH} = 800 \ \mu A$ )  | Full        | 3.0 |            |               | V      |

| Logic 0 Voltage (I₀∟ = 50 µA)               | Full        |     |            | 0.3           | V      |

| LOGIC OUTPUT (Dx, DSYNC)                    |             |     |            |               |        |

| Logic 1 Voltage ( $I_{OH} = 2 \text{ mA}$ ) | Full        | 3.0 |            |               | V      |

| Logic 0 Voltage ( $I_{OL} = 2 \text{ mA}$ ) | Full        |     |            | 0.05          | V      |

<sup>1</sup> x stands for A, B, C, or D.

<sup>2</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions, and how these tests were completed.

<sup>3</sup> Specified for LVDS and LVPECL only.

<sup>4</sup> Specified for 13 SDIO pins sharing the same connection.

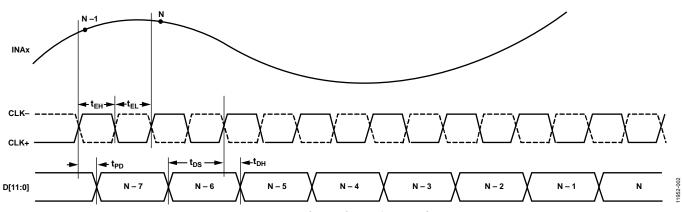

#### SWITCHING SPECIFICATIONS

$AVDD18 = AVDD18ADC = 1.8 \text{ V}, AVDD33 = AVDD33x^1 = AVDD33REF = 3.3 \text{ V}, DVDD18 = DVDD18CLK = 1.8 \text{ V}, DVDD33SPI = DVDD33CLK = DVDD33DRV = 3.3 \text{ V}, 1.024 \text{ V} \text{ internal ADC reference}, f_{IN} = 2.5 \text{ MHz}, f_{SAMPLE} = 72 \text{ MSPS}, R_S = 50 \Omega, LNA + PGA gain = 34 dB, LPF cutoff = f_{SAMPLECH}/4, full channel mode, 12-bit operation, temperature = -40°C to +105°C, unless otherwise noted.$

| Parameter <sup>2</sup>                         | Temperature | Min  | Тур  | Max  | Unit         |

|------------------------------------------------|-------------|------|------|------|--------------|

| CLOCK                                          | -           |      |      |      |              |

| Clock Rate                                     | Full        | 10   |      | 72   | MSPS         |

| Clock Pulse Width High (teh) at 72 MSPS        | Full        |      | 6.94 |      | ns           |

| Clock Pulse Width Low ( $t_{EL}$ ) at 72 MSPS  | Full        |      | 6.94 |      | ns           |

| Clock Pulse Width High ( $t_{EH}$ ) at 40 MSPS | Full        |      | 12.5 |      | ns           |

| Clock Pulse Width Low ( $t_{EL}$ ) at 40 MSPS  | Full        |      | 12.5 |      | ns           |

| OUTPUT PARAMETERS                              |             |      |      |      |              |

| Propagation Delay ( $t_{PD}$ ) at 72 MSPS      | Full        | 1.5  | 2.5  | 5.0  | ns           |

| Rise Time (t <sub>R</sub> ) <sup>3</sup>       | Full        |      | 1.9  |      | ns           |

| Fall Time (t <sub>F</sub> ) <sup>3</sup>       | Full        |      | 1.2  |      | ns           |

| Data Set-Up Time ( $t_{DS}$ ) at 72 MSPS       | Full        | 9.0  | 10.0 | 11.0 | ns           |

| Data Hold Time ( $t_{DH}$ ) at 72 MSPS         | Full        | 1.5  | 4.0  | 5.0  | ns           |

| Data Set-Up Time (t <sub>Ds</sub> ) at 40 MSPS | Full        | 21.5 | 22.5 | 23.5 | ns           |

| Data Hold Time ( $t_{DH}$ ) at 40 MSPS         | Full        | 1.5  | 4.0  | 5.0  | ns           |

| Pipeline Latency                               | Full        |      | 7    |      | Clock cycles |

<sup>1</sup> x stands for A, B, C, or D.

<sup>2</sup> See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions, and how these tests were completed. <sup>3</sup> Not shown in Figure 2.

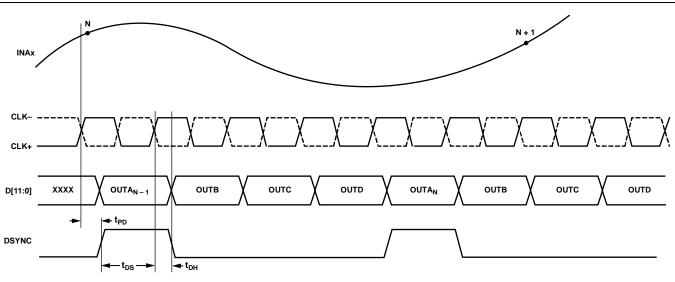

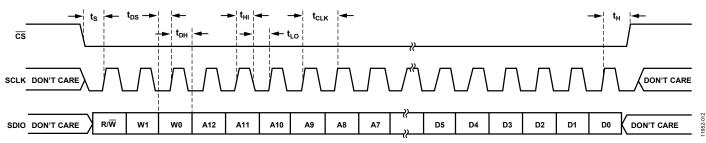

Figure 2. Timing Definitions for Switching Specifications

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 4.

| Tuble I.                                       |                  |

|------------------------------------------------|------------------|

| Parameter                                      | Rating           |

| Electrical                                     |                  |

| AVDD18x <sup>1</sup> to GND                    | –0.3 V to +2.0 V |

| AVDD33x <sup>2</sup> to GND                    | –0.3 V to +3.5 V |

| DVDD18x <sup>3</sup> to GND                    | –0.3 V to +2.0 V |

| DVDD33x <sup>4</sup> to GND                    | –0.3 V to +3.5 V |

| Analog Inputs<br>INx+, INx- to GND             | –0.3 V to +3.5 V |

| Auxiliary Inputs<br>INADC+, INADC– to GND      | –0.3 V to +2.0 V |

| Digital Outputs<br>D[11:0], DSYNC, SDIO to GND | –0.3 V to +3.5 V |

| CLK+, CLK– to GND                              | –0.3 V to +3.9 V |

| PDWN, SCLK, CS, AUX, MUXA,<br>ZSEL to GND      | –0.3 V to +3.9 V |

| RBIAS, VREF to GND                             | –0.3 V to +2.0 V |

| Environmental                                  |                  |

| Operating Temperature<br>Range (Ambient)       | –40°C to +105°C  |

| Storage Temperature<br>Range (Ambient)         | –65°C to +150°C  |

| Maximum Junction<br>Temperature                | 150°C            |

| Lead Temperature<br>(Soldering, 10 sec)        | 300°C            |

|                                                |                  |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

$^{1}$  AVDD18x = AVDD18 and AVDD18ADC.

<sup>2</sup> AVDD33x = AVDD33A, AVDD33B, AVDD33C, AVDD33D, and AVDD33REF.

<sup>3</sup> DVDD18x / DVDD18, DVDD18CLK.

<sup>4</sup> DVDD33x = DVDD33, DVDD33SPI, DVDD33CLK, DVDD33DRV.

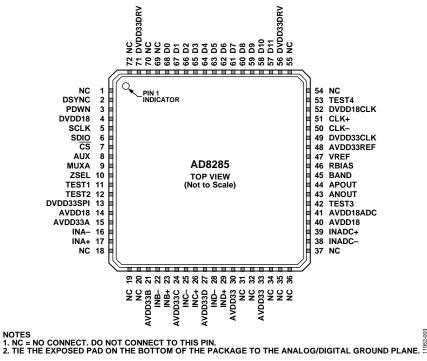

## **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

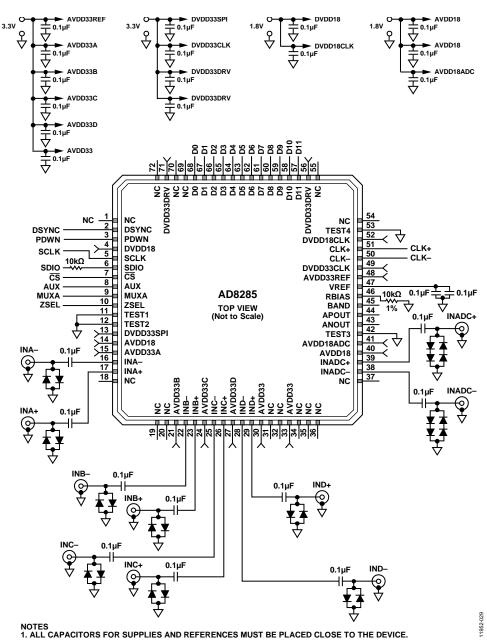

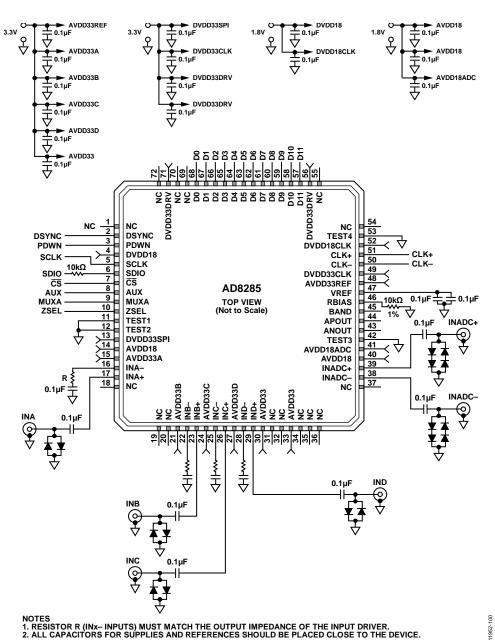

Figure 3. Pin Configuration

#### Table 5. Pin Function Descriptions

| Pin No. | Mnemonic  | Description                                                                                                                                                              |

|---------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       | EPAD      | Exposed Pad. Tie the exposed pad on the bottom of the package to the analog/digital ground plane.                                                                        |

| 1       | NC        | No Connect. Do not connect to this pin.                                                                                                                                  |

| 2       | DSYNC     | Data Output Synchronization.                                                                                                                                             |

| 3       | PDWN      | Full Power Down. Logic high overrides the SPI and powers down the device. Logic low allows selection of the power down option through the SPI.                           |

| 4       | DVDD18    | 1.8 V Digital Supply.                                                                                                                                                    |

| 5       | SCLK      | Serial Clock.                                                                                                                                                            |

| 6       | SDIO      | Serial Data Input/Output.                                                                                                                                                |

| 7       | CS        | Chip Select Bar.                                                                                                                                                         |

| 8       | AUX       | Auxiliary. A logic high on AUX switches the AUX channel (INADC+/INADC–) to the ADC. The AUX pin has a higher priority than the MUXA pin.                                 |

| 9       | MUXA      | Channel A Select. Logic high forces to Channel A unless AUX is asserted.                                                                                                 |

| 10      | ZSEL      | Input Impedance Select. Logic high overrides the SPI and sets the input impedance to 200 k $\Omega$ . Logic low allows selection of the input impedance through the SPI. |

| 11      | TEST1     | Test. Do not use the TEST1 pin; tie it to ground.                                                                                                                        |

| 12      | TEST2     | Test. Do not use the TEST2 pin; tie it to ground.                                                                                                                        |

| 13      | DVDD33SPI | 3.3 V Digital Supply for SPI Port.                                                                                                                                       |

| 14      | AVDD18    | 1.8 V Analog Supply.                                                                                                                                                     |

| 15      | AVDD33A   | 3.3 V Analog Supply for Channel A.                                                                                                                                       |

| 16      | INA-      | Negative LNA Analog Input for Channel A.                                                                                                                                 |

| 17      | INA+      | Positive LNA Analog Input for Channel A.                                                                                                                                 |

| 18      | NC        | No Connect. Do not connect to this pin.                                                                                                                                  |

| 19      | NC        | No Connect. Do not connect to this pin.                                                                                                                                  |

| 20      | NC        | No Connect. Do not connect to this pin.                                                                                                                                  |

| 21      | AVDD33B   | 3.3 V Analog Supply for Channel B.                                                                                                                                       |

| 22      | INB-      | Negative LNA Analog Input for Channel B.                                                                                                                                 |

| 23      | INB+      | Positive LNA Analog Input for Channel B.                                                                                                                                 |

## **Data Sheet**

| Pin No. Mnemonic Description   24 AVDD33C 3.3 V Analog Supply for Channel C.   25 INC- Negative LNA Analog Input for Channel C.   26 INC- Positive LNA Analog Input for Channel C.   27 AVDD33D 3.3 V Analog Supply for Channel D.   28 IND- Negative LNA Analog Input for Channel D.   29 IND- Positive LNA Analog Input for Channel D.   29 IND- Negative LNA Analog Supply.   30 AVDD33 3.3 V Analog Supply.   31 NC No Connect. Do not connect to this pin.   32 NC No Connect. Do not connect to this pin.   33 VADD33 3.3 V Analog Supply.   34 NC No Connect. Do not connect to this pin.   36 NC No Connect. Do not connect to this pin.   37 NC No Connect. Do not connect to this pin.   38 INADC- Negative Analog Input for Alternate Channel D (ADC Only).   40 AVDD18 1.8 V Analog Supply.   41 AVDD180 1.8 V Analog Supply for ADC.                                                                                                                                                                                                                                                                                                                                                                                          |   | NA        | Description                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|-----------|-------------------------------------------------------------------------------------|

| 25INC-Negative LNA Analog Input for Channel C.26INC+Positive LNA Analog Input for Channel D.27AVDD33D3.3V Analog Supply for Channel D.28IND-Negative LNA Analog Input for Channel D.29IND+Positive LNA Analog Input for Channel D.20AVDD333.3V Analog Supply for Channel D.21NCNo Connect. Do not connect to this pin.32NCNo Connect. Do not connect to this pin.33Analog Supply.NC34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-No Connect. Do not connect to this pin.39INADC-No connect. Do not connect to this pin.39INADC-No Sative Analog Input for Alternate Channel D (ADC Only).40AVD181.8V Analog Supply for ADC.41AVDD181.8V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it or ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46APOUTAnalog Outputs. The ANOUT pin is for ground.47VREFVoltage Reference Input/Output.<           |   | Mnemonic  | Description                                                                         |

| 26INC+Positive LNA Analog input for Channel C.27AVDD33D3.3 V Analog Supply for Channel D.28IND-Negative LNA Analog Input for Channel D.29IND4Positive LNA Analog Input for Channel D.30AVDD333.3 V Analog Supply.31NCNo Connect. Do not connect to this pin.32NCNo Connect. Do not connect to this pin.33AVDD333.3 V Analog Supply.34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-No Connect. Do not connect to this pin.39INADC-No Connect. Do not connect to this pin.39INADC-No Connect. Do not connect to this pin.31NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8V Analog Supply for ADC.41AVDD18ADC1.8V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Supply for ADC.45BANDBand Gay Voltage. The BAND pin is for debug purposes only. Leave                                                |   |           |                                                                                     |

| 27AVD033D3.3 V Analog Supply for Channel D.28IND-Negative LNA Analog Input for Channel D.29IND+Positive LNA Analog Supply for Channel D.30AVD0333.3 V Analog Supply.31NCNo Connect. Do not connect to this pin.32NCNo Connect. Do not connect to this pin.33AVD0333.3 V Analog Supply.34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC-Positive Analog Input for Alternate Channel D (ADC Only).40AVD181.8V Analog Supply for ADC.41AVD18ADC1.8V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33CK3.3 V Digital Supply for Clock.59OVD18CLK1.8 V Digital Supply for Clock.54NCNo Conn           |   |           |                                                                                     |

| 28IND-Negative LNA Analog Input for Channel D.29IND+Positive LNA Analog Input for Channel D.30AVDD333.3 V Analog Supply.31NCNo Connect. Do not connect to this pin.32NCNo Connect. Do not connect to this pin.33AVDD333.3 V Analog Supply.34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC+Positive Analog Input for Alternate Channel D (ADC Only).34AVDD18ADC1.8 V Analog Supply.41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it og grund.43ANOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.44AVDD18ADC1.8 V Analog Supply for ADC.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RIACExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Voltput.48AVDD33CLK3.3 V Analog Supply for Clock.59CLK+Clock Input True.50CLK+Clock Input True.51CLK+Clock Input True.52NCNo Connect. Do not connect to this pin.                                               |   |           |                                                                                     |

| 29IND+Positive LNA Analog Input for Channel D.30AVDD333.3 V Analog Supply.31NCNo Connect. Do not connect to this pin.32NCNo Connect. Do not connect to this pin.33AVDD333.3 V Analog Supply.34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8 V Analog Supply for ADC.41AVDD181.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD3REF3.3 V Digital Supply for Clock.59DVDD18CLK1.8 V Digital Supply for Clock.51CLK+Clock Input True.52NCNo Connect. Do not connect to this pin.54NCNo Connect. Do not connect to           |   |           |                                                                                     |

| 30AVDD333.3 V Analog Supply.31NCNo Connect. Do not connect to this pin.32NCNo Connect. Do not connect to this pin.33AVDD333.3 V Analog Supply.34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC-Positive Analog Supply.40AVDD181.8 V Analog Supply for ADC.41AVDD181.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference input/Output.48AVDD33REF3.3 V Analog Supply for Clock.53TEST4Test. Do not connect to this pin.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Clock.57D11ADC Data Output 10.58                                      |   |           |                                                                                     |

| 31NCNo Connect. Do not connect to this pin.32NCNo Connect. Do not connect to this pin.33AVDD333.3 V Analog Supply.34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Ne Sative Analog Input for Alternate Channel D (ADC Only).39INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8 V Analog Supply for ADC.41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for Clock.50CLK-Clock Input True.51CLK-Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not c           |   |           |                                                                                     |

| 32NCNo Connect. Do not connect to this pin.33AVDD333.3 V Analog Supply.34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC-Positive Analog Supply.40AVDD181.8 V Analog Supply.41AVDD181.8 V Analog Supply.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD13CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Clock.57D                                      |   |           |                                                                                     |

| 33AVDD333.3 V Analog Supply.34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8 V Analog Supply.41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33EEF3.3 V Analog Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD13CLK3.3 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Clock.57D11ADC Data Output 11 (MSB           |   |           |                                                                                     |

| 34NCNo Connect. Do not connect to this pin.35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8 V Analog Supply.41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for Clock.50CLK-Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not connect to this pin.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 10.58D10ADC Data Output 10.59D9ADC Data Output 9.59 <td></td> <td>-</td> <td></td> |   | -         |                                                                                     |

| 35NCNo Connect. Do not connect to this pin.36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC-Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8V Analog Supply.41AVDD18ADC1.8V Analog Supply.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Digital Supply for Clock.50CLK-Clock Input True.51CLK+Clock Input True.52DVDD18CLK1.8V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 10.58D10ADC Data Output 10.59D9ADC Data Output 8.60D8<                                           |   |           |                                                                                     |

| 36NCNo Connect. Do not connect to this pin.37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8 V Analog Supply.41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for Clock.50CLK+Clock Input True.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 8.60D8ADC Data Output 7.61D7ADC Data Output 7.                                                      |   |           |                                                                                     |

| 37NCNo Connect. Do not connect to this pin.38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8 V Analog Supply.41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33CLK3.3 V Analog Supply for Clock.50CLK-Clock Input True.51CLK+Clock Input True.52DVD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 49.60D8ADC Data Output 7.                                                                                                                        |   |           |                                                                                     |

| 38INADC-Negative Analog Input for Alternate Channel D (ADC Only).39INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8 V Analog Supply.41AVD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for References.49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input True.51CLK+Clock Input True.52DVD1BCLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 10.58D10ADC Data Output 9.599ADC Data Output 9.60D8ADC Data Output 7.                                                                                                      |   |           |                                                                                     |

| 39INADC+Positive Analog Input for Alternate Channel D (ADC Only).40AVDD181.8 V Analog Supply.41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for Clock.50CLK-Clock Input True.51CLK+Clock Input True.52DVDD182CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC bata Output 10.58D10ADC bata Output 19.60D8ADC bata Output 8.61D7ADC bata Output 7.                                                                                                                                                                                                                 |   |           |                                                                                     |

| 40AVDD181.8 V Analog Supply.41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 9.59D9ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                        |   |           |                                                                                     |

| 41AVDD18ADC1.8 V Analog Supply for ADC.42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 9.59D9ADC Data Output 8.60D8ADC Data Output 7.                                                                                                                                                                                                                                                                                                    |   |           |                                                                                     |

| 42TEST3Test. Do not use the TEST3 pin; tie it to ground.43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for References.49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 9.59D9ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                      | ŀ | AVDD18    |                                                                                     |

| 43ANOUTAnalog Outputs. The ANOUT pin is for debug purposes only. Leave this pin floating.44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for References.49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 10.58D10ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                          |   |           |                                                                                     |

| 44APOUTAnalog Outputs. The APOUT pin is for debug purposes only. Leave this pin floating.45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for References.49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 10.58D10ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ר | TEST3     |                                                                                     |

| 45BANDBand Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating.46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for References.49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 10.58D10ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |   |           |                                                                                     |

| 46RBIASExternal Resistor. The RBIAS pin sets the internal ADC core bias current.47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for References.49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 10.58D10ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ŀ | APOUT     |                                                                                     |

| 47VREFVoltage Reference Input/Output.48AVDD33REF3.3 V Analog Supply for References.49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | E | BAND      | Band Gap Voltage. The BAND pin is for debug purposes only. Leave this pin floating. |

| 48AVDD33REF3.3 V Analog Supply for References.49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | F | RBIAS     | External Resistor. The RBIAS pin sets the internal ADC core bias current.           |

| 49DVDD33CLK3.3 V Digital Supply for Clock.50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | ١ | VREF      | Voltage Reference Input/Output.                                                     |

| 50CLK-Clock Input Complement.51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 10.59D9ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | ŀ | AVDD33REF | 3.3 V Analog Supply for References.                                                 |

| 51CLK+Clock Input True.52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | [ | DVDD33CLK | 3.3 V Digital Supply for Clock.                                                     |

| 52DVDD18CLK1.8 V Digital Supply for Clock.53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 10.59D9ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ( | CLK–      | Clock Input Complement.                                                             |

| 53TEST4Test. Do not use the TEST4 pin; tie it to ground.54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 10.59D9ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | ( | CLK+      | Clock Input True.                                                                   |

| 54NCNo Connect. Do not connect to this pin.55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 10.59D9ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | [ | DVDD18CLK | 1.8 V Digital Supply for Clock.                                                     |

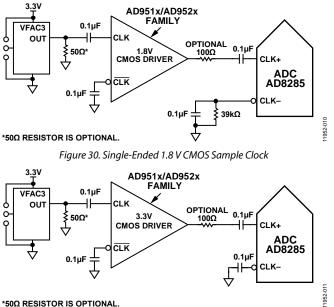

| 55NCNo Connect. Do not connect to this pin.56DVDD33DRV3.3 V Digital Supply for Output Driver.57D11ADC Data Output 11 (MSB).58D10ADC Data Output 10.59D9ADC Data Output 9.60D8ADC Data Output 8.61D7ADC Data Output 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | ר | TEST4     | Test. Do not use the TEST4 pin; tie it to ground.                                   |