# Qorivva MPC5500 Minimum Board Requirements

by: Randy Dees

Application Engineering

Austin, Texas/USA

## 1 Introduction

This application note shows recommended example circuits for the Qorivva MPC55xx family of 32-bit microcontrollers (MCU) based on the e200zx Power Architecture® cores. Many of these circuits are included on the standard evaluation board for the different devices. In most cases in this application note, the MPC5554 is used in the examples, however, unless otherwise specified, the majority apply to all devices in the family. In addition, some of the MCUs in this family support features that are not available on the MPC5554. Circuits for these options are also shown in this document.

The Qorivva MPC5500 family contains multiple MCUs that were originally designed for automotive powertrain applications and span from the low end MPC5534, with 1 MB of on-chip flash, up to the high end MPC5566 with 3MB of on-chip flash memory. In between are devices with support for a varying number of peripheral devices, including two devices that support FlexRAY. The following table highlights the features available on the different members of the MPC55xx MCU family.

#### Contents

| 1  | Introduction                                           | 1  |

|----|--------------------------------------------------------|----|

| 2  | Reset Configuration                                    |    |

| 3  | Clock Circuitry                                        |    |

| 4  | Power supply requirements                              |    |

| 5  | External pull resistors                                | 22 |

| 6  | External bus interface                                 | 22 |

| 7  | Nexus Connector Recommendation and Pin-Out Definitions | 27 |

| 8  | Example communication peripheral connections           | 31 |

| 9  | EVB Pin access                                         | 47 |

| 10 | References                                             | 48 |

Table 1. Qorivva MPC5500 Family comparison

|                                      |                                                  |                            |                                         |                          | -                    |                          |                          |                       |

|--------------------------------------|--------------------------------------------------|----------------------------|-----------------------------------------|--------------------------|----------------------|--------------------------|--------------------------|-----------------------|

|                                      |                                                  | MPC5534                    | MPC5553                                 | MPC5554                  | MPC5561              | MPC5565                  | MPC5566                  | MPC5567               |

| Power Architecture Core              |                                                  | e200z3 <sup>1</sup>        | e200z6                                  | e200z6                   | e200z6 with<br>VLE   | e200z6 with<br>VLE       | e200z6 with<br>VLE       | e200z6 with<br>VLE    |

| Packages                             |                                                  | 208<br>MAPBGA,<br>324 PBGA | 208<br>MAPBGA,<br>324 PBGA,<br>416 PBGA | 416 PBGA                 | 324 PBGA             | 324 PBGA                 | 416 PBGA                 | 324 PBGA,<br>416 PBGA |

| Unified Cache                        | Э                                                | _                          | 8 KB                                    | 32 KB <sup>3</sup>       | 32 KB <sup>4</sup>   | 8 KB <sup>2</sup>        | 32 KB                    | 8 KB <sup>2</sup>     |

| Memory Mana<br>(MMU)                 | agement Unit                                     | 16 entries                 | 32 entries                              | 32 entries               | 32 entries           | 32 entries               | 32 entries               | 32 entries            |

| Crossbar                             |                                                  | 4 x 5                      | 4 x 5                                   | 3 x 5                    | 4 x 6                | 3 x 5 <sup>5</sup>       | 4 x 5                    | 5 x 5                 |

| Core Nexus S                         | Support                                          | Class 3+                   | Class 3+                                | Class 3+                 | Class 3+             | Class 3+                 | Class 3+                 | Class 3+              |

| SRAM                                 |                                                  | 64 Kbyte                   | 64 Kbyte                                | 64 Kbyte                 | 192 Kbyte            | 80 Kbyte                 | 128 Kbyte                | 80 Kbyte              |

| Flash                                | Main Array                                       | 1 Mbyte <sup>6</sup>       | 1.5 Mbyte                               | 2 Mbyte <sup>7</sup>     | 1 Mbyte <sup>7</sup> | 2 Mbyte <sup>7</sup>     | 128 Mbyte <sup>7</sup>   | 2 Mbyte <sup>7</sup>  |

| Memory                               | Shadow<br>block                                  | 1 Kbyte                    | 1 Kbyte                                 | 1 Kbyte                  | 1 Kbyte              | 1 Kbyte                  | 1 Kbyte                  | 1 Kbyte               |

| External bus                         | Data                                             | 16-bit                     | 32-bit <sup>8</sup>                     | 32-bit                   | 32-bit               | 16-bit                   | 32-bit                   | 32-bit <sup>8</sup>   |

| interface<br>(EBI                    | Address                                          | 24-bit                     | 24-bit                                  | 24-bit                   | 26-bit               | 26-bit <sup>9</sup>      | 26-bit <sup>9</sup>      | 26-bit <sup>9</sup>   |

| Calibration bu                       | us interface                                     | Yes                        | Partial support                         | No                       | Yes                  | Yes                      | Yes                      | Yes                   |

| Enhanced direct memory access (eDMA) |                                                  | 32 channels                | 32 channels                             | 64 channels              | 32 channels          | 32 channels              | 64 channels              | 32 channels           |

| eDMA Nexus                           |                                                  | _                          | Class 3                                 | Class 3                  | Class 3              | Class 3                  | Class 3                  | Class 3               |

| Enhanced                             | Instances                                        | 2                          | 2                                       | 2                        | 4                    | 2                        | 2                        | 2                     |

| serial<br>computer                   | eSCI A                                           | Υ                          | Υ                                       | Υ                        | Υ                    | Υ                        | Υ                        | Υ                     |

| interface                            | eSCI B                                           | Υ                          | Υ                                       | Υ                        | Υ                    | Υ                        | Υ                        | Υ                     |

| (eSCI)                               | eSCI C                                           | _                          | _                                       | _                        | Υ                    | _                        | _                        | _                     |

| ļ                                    | eSCI D                                           | _                          | _                                       | _                        | Υ                    | _                        | _                        | _                     |

| Controller                           | Instances                                        | 2                          | 2                                       | 3                        | 2                    | 3 <sup>10</sup>          | 4 <sup>10</sup>          | 5 <sup>10</sup>       |

| Area<br>network                      | CAN A                                            | 64 buffers                 | 64 buffers                              | 64 buffers               | 64 buffers           | 64 buffers               | 64 buffers               | 64 buffers            |

| (FlexCAN)                            | CAN B                                            | _                          | _                                       | 64 buffers               | _                    | 64 buffers               | 64 buffers               | 64 buffers            |

|                                      | CAN C                                            | 64 buffers                 | 64 buffers                              | 64 buffers               | 64 buffers           | 64 buffers               | 64 buffers               | 64 buffers            |

|                                      | CAN D                                            | _                          | _                                       | _                        | _                    | _                        | 64 buffers               | 64 buffers            |

| ļ                                    | CAN E                                            | _                          | _                                       | _                        | _                    | _                        | _                        | 64 buffers            |

| Deserial to                          | Instances                                        | 3                          | 3                                       | 4                        | 2                    | 3                        | 4                        | 3                     |

| serial<br>peripheral                 | DSPI A                                           | _                          | _                                       | Υ                        | _                    | _                        | Υ                        | _                     |

| interface                            | DSPI A                                           | Υ                          | Υ                                       | Υ                        | Υ                    | Υ                        | Υ                        | Υ                     |

| (DSPI)                               | DSPI C                                           | Υ                          | Υ                                       | Υ                        | Υ                    | Υ                        | Υ                        | Υ                     |

| ļ                                    | DSPI D                                           | Υ                          | Υ                                       | Υ                        | _                    | Υ                        | Υ                        | Υ                     |

| ì                                    | enhanced Modular Input/<br>Output System (eMIOS) |                            | 1                                       | 1                        | <u> </u>             |                          | t                        | t                     |

|                                      | •                                                | 24 channel                 | 24 channel                              | 24 channel               | 24 channel           | 24 channel               | 24 channel               | 24 channel            |

|                                      | •                                                | 24 channel<br>32 channel   | 24 channel<br>32 channel                | 24 channel<br>64 channel | 24 channel 0 channel | 24 channel<br>32 channel | 24 channel<br>64 channel | 24 channel 32 channel |

Table continues on the next page...

Table 1. Qorivva MPC5500 Family comparison (continued)

|                                               |                   | MPC5534              | MPC5553         | MPC5554     | MPC5561               | MPC5565     | MPC5566                      | MPC5567         |

|-----------------------------------------------|-------------------|----------------------|-----------------|-------------|-----------------------|-------------|------------------------------|-----------------|

| Processing                                    | eTPU B            | _                    | _               | Υ           | _                     | _           | Υ                            | _               |

| Unit (eTPU)                                   | Code<br>Memory    | 12 Kbyte             | 12 Kbyte        | 16 Kbyte    | 0 Kbyte               | 12 Kbyte    | 20 Kbyte                     | 12 Kbyte        |

|                                               | Parameter<br>SRAM | 2.5 Kbyte            | 2.5 Kbyte       | 3 Kbyte     | 0 Kbyte               | 2.5 Kbyte   | 4 Kbyte                      | 2.5 Kbyte       |

|                                               | Nexus             | Class 3              | Class 3         | Class 3     | _                     | Class 3     | Class 3                      | Class 3         |

| Interrupt Cor                                 | ntroller (INTC)   | 210 channel          | 210 channel     | 308 channel | 231 channel           | 231 channel | 320<br>channel <sup>11</sup> | 231 channel     |

| enhanced                                      | Channels          | 40 channel           | 40 channel      | 40 channel  | 40 channel            | 40 channel  | 40 channel                   | 40 channel      |

| Queued                                        | ADC0              | Υ                    | Υ               | Υ           | Υ                     | Υ           | Υ                            | Υ               |

| Analog-to-<br>Aigital<br>Converter<br>(eQADC) | ADC1              | Υ                    | Υ               | Υ           | Υ                     | Υ           | Υ                            | Y               |

| Fast<br>Ethernet<br>controller<br>(FEC)       |                   | _                    | Y <sup>12</sup> | _           | _                     | _           | Y                            | Υ13             |

| FlexRay                                       | -                 | _                    | _               | _           | Υ                     | _           | Υ                            | _               |

| FlexRay Nex                                   | rus               | _                    | _               | _           | Class 3               | _           | Class 3                      | _               |

| Phase lock loop (FMPLL)                       |                   | FM                   | FM              | FM          | FM                    | FM          | FM                           | FM              |

| Maximum system frequency                      |                   | 82 MHz <sup>14</sup> | 132 MHz         | 132 MHz     | 135 MHz <sup>15</sup> | 135 MHz     | 147 MHz <sup>16</sup>        | 135 MHz         |

| Crystal range                                 |                   | 8-20 MHz             | 8-20 MHz        | 8-20 MHz    | 8-20, 40<br>MHz       | 8-20 MHz    | 8-20 MHz                     | 8-20, 40<br>MHz |

| Voltage regu                                  | lator             | Υ                    | Υ               | Υ           | Υ                     | Υ           | Υ                            | Υ               |

- 1. All e200z3 cores support the Variable Length Encoded (VLE) Instruction set.

- 2. 2-way associative

- 3. 8-way associative

- 4. 4-way or 8-way associative

- 5. The actual crossbar is implemented as a 5 x 5 crossbar with two unused ports.

- 6. 16-byte flash page size for programming.

- 7. 32-byte flash page size for programming.

- 8. May not be externally available in all packages.

- 9. Either ADDR[8:31] or ADDR[6:29] can be selected.

- 10. Updated FlexCAN module with optional individual receive filters.

- 11. Although this device has a maximum of 329 interrupts, the logic requires that the total number of interrupts be divisible by four. Therefore, the total number of interrupts specified for this device is 332.

- 12. The FEC signals are multiplexed with data bus pins DATA[16:31].

- 13. The FEC signals are shared with the calibration bus.

- 14. 80 MHz + 2% FM

- 15. 132 MHz + 2% FM

- 16. 144 MHz + 2% FM

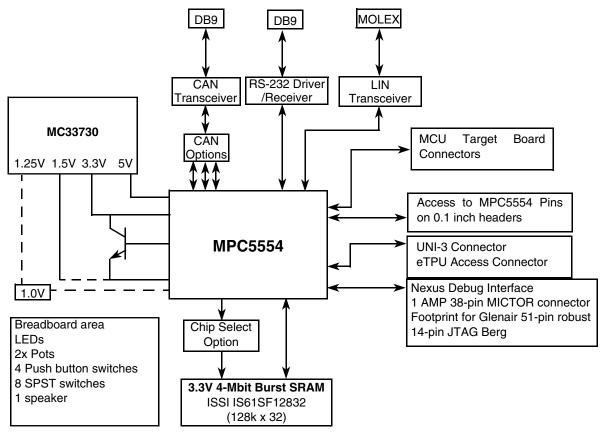

The figure below shows a block diagram of a typical evaluation board and how some of the peripherals are connected to the MCU. This also shows using the Freescale MC33730 power supply device.

#### Introduction

Figure 1. Typical evaluation board block diagram

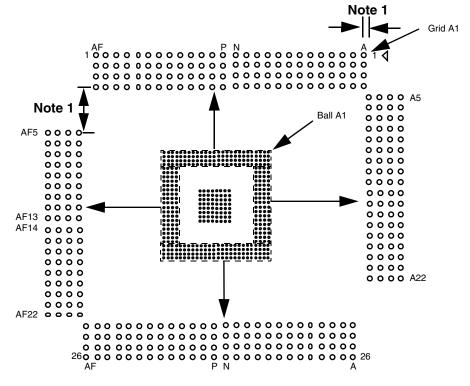

## 1.1 MPC5500 Packages

The MPC5500 devices are available in multiple packages to address the size and Input/output requirements of different types of systems. All of these packages are Plastic Ball Grid Array (PBGA) or Mold Array Process Ball Grid Array (MAP-BGA), Not all devices are available in all packages. The following table shows the package options for the different devices.

| Device  | 208 MAPBGA    | 324 PBGA      | 416 PBGA      |

|---------|---------------|---------------|---------------|

|         | 17 mm x 17 mm | 23 mm x 23 mm | 27 mm x 27 mm |

| MPC5534 | 1             | 1             | _             |

| MPC5553 | √             | 1             | 1             |

| MPC5554 | _             | _             | √             |

| MPC5561 | _             | J             | _             |

| MPC5565 | _             | J             | _             |

| MPC5566 | _             | _             | 1             |

| MPC5567 | _             | <b>√</b>      | 1             |

Table 2. MPC5500 device package options

## 2 Reset Configuration

Some operating features of the device are configured during reset. Depending on the value of the Reset Configuration pin  $(\overline{RSTCFG})$ , either a default configuration is selected or external pins provide the configuration information.  $\overline{RSTCFG}$  has an internal pull up that will select the default settings unless driven from an external circuit or pulled down with an external device strong enough to overcome the internal pull up. The following features are controllable via the reset configuration pins:

- Default configuration or externally controlled configuration (RSTCFG)

- Boot mode: internal flash, external memory, or serial boot (BOOTCFG[0:1])

- Clock Configuration: crystal oscillator or external reference clock (PLLCFG[0:1]), plus clock range (PLLCFG[2]<sup>1</sup>)

- Timer channel default pull (up or down) direction (WKPCFG)

The configuration pins (PLLCFG[0:1/2] and BOOTCFG[0:1]) are internally latched four clocks prior to the MCU negating  $\overline{RSTOUT}$  if  $\overline{RSTCFG}$  is asserted. WKPCFG is always latched four clocks prior to  $\overline{RSTOUT}$  negation and is not controlled by the  $\overline{RSTCFG}$  pin.

Depending on the system requirements, there are four recommended circuit options to support the reset configuration of the device. These are shown in the following table and are each described in later sections of this document.

**Desired Reset RSTCFG Clock Source Boot location Notes Configuration Option** value Absolute minimum reset 1 (high) Internal crystal oscillator Internal flash Uses internal crystal configuration (see oscillator, boot from Minimum (default) RESET internal flash configuration circuit (most commonly used)) Full reset configuration 0 (low) Internal crystal oscillator or Internal flash or external This configuration is control<sup>1</sup> (see External external reference clock memory (selectable based required if the **RESET** configuration with on desired configuration) configuration pins<sup>2</sup> are optional GPIO on config used for General Purpose pins) Input/Outputs (GPIO) Recommended minimum 0 (low) External reference clock Internal flash or external Optionally, GPIO can be configuration when using memory (selectable based used with additional an external reference on desired configuration) circuitry clock with GPIO on config pins (see Minimum required circuitry for external reference clock mode (with optional GPIO)) Absolute minimum 0 (low) External reference clock Internal flash or external The Pad Configuration Registers (PCR) for the configuration for an memory (selectable based external reference clock on desired configuration) configuration pins must be without GPIO on config left in their default states pins (see Absolute (GPIO not allowed on the minimum RESET configuration pins). configuration circuit for external clock (GPIO on

Table 3. Recommended configuration circuit options

config pins not allowed))

<sup>1.</sup> Not available on all devices.

#### **Reset Configuration**

- 1. Recommended for evaluation boards or initial prototypes to allow different configurations to be set.

- 2. RSTCOFG, PLLCFG[0:1], and/or BOOTCFG[0:1]

The following table shows the default configuration that is selected if  $\overline{RSTCFG}$  is negated (high).

Table 4. Default (RSTCFG = 1) configuration

| Signals      | Value | Selection                |

|--------------|-------|--------------------------|

| BOOTCFG[0:1] | 0b00  | Boot from internal flash |

| PLLCFG[0:1]  | 0b10  | Use crystal oscillator   |

RSTCFG controls selection of either the default configuration or an external configuration as shown in the following table.

Table 5. Default (internal) versus external configuration control

| RSTCFG Value | Configuration mode                                                                                                                                                |  |  |  |  |  |

|--------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|              | Default (internal) boot mode selected with a crystal oscillator reference. This provides the same configuration as setting BOOTCFG[0:1]=0b00 and PLLCFG[0:1]=0b01 |  |  |  |  |  |

| 0            | The values of BOOTCFG[0:1] and PLLCFG[0:1] control the boot and clock mode configuration                                                                          |  |  |  |  |  |

The following table shows the possible configurations of the memory boot mode.

Table 6. Boot memory configuration options

|   | BOOTCFG[0] | BOOTCFG[1] | Boot mode                                                                                                                                                          |

|---|------------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0 |            | 0          | Boot from the internal flash memory (default when $\overline{RSTCFG} = 1$ )                                                                                        |

| 0 |            | 1          | Boot from FlexCAN or eSCI                                                                                                                                          |

| 1 |            | 0          | Boot from the external memory (single master, with no arbitration)                                                                                                 |

| 1 |            |            | Boot from the external memory (multi-master mode with external bus arbitration). This mode is only supported on the MPC5554. It is not supported on other devices. |

The following table shows the options for the clock configuration that are controlled out of reset. On devices that support PLLCFG[2], PLLCFG[2] is not latched and controls the predivider value of the PLL. PLLCFG[2] should only be high if a 40 MHz crystal is used.

Table 7. PLL clock configuration

| PLLCFG[0] | PLLCFG[1] | PLL Clock mode                                                                                                                       |

|-----------|-----------|--------------------------------------------------------------------------------------------------------------------------------------|

| 0         | 0         | Bypass mode                                                                                                                          |

| 0         | 1         | Normal mode with external reference clock                                                                                            |

| 1         |           | Normal mode with external crystal reference (uses internal oscillator). This is the default mode if $\overline{\text{RSTCFG}} = 1$ . |

| 1         | 1         | 1:1 mode <sup>1</sup>                                                                                                                |

1. This mode is intended for use in dual controller systems only.

The default state of the enhanced Timing Processing Unit (eTPU) and the enhanced Modular Input/Output System (eMIOS) timer pins is controlled by the weak pull configuration pin (WKPCFG) as shown in the following table.

| WKPCFG | Weak Pull Configuration                           |  |  |  |  |

|--------|---------------------------------------------------|--|--|--|--|

| 0      | eTPU and eMIOS pins have weak pull downs enabled. |  |  |  |  |

| 1      | eTPU and eMIOS pins have weak pull ups enabled.   |  |  |  |  |

#### **NOTE**

Not all eTPU and eMIOS pins are controlled by the WKPCFG pins. See the pin descriptions in the device Data Sheet and Reference Manual.

During the internal power on reset (POR) of the MPC5500 devices, the reset output pin ( $\overline{RSTOUT}$ ) floats. A pull resistor on  $\overline{RSTOUT}$  is required to control external circuitry during POR. Normally, a pull down should be used on  $\overline{RSTOUT}$  to hold external circuitry in reset during POR. However, if an external configuration is required (for PLLCFG[1:0] and BOOTCFG[1:0]), then care needs to be taken. A possible, but extremely rare, misconfiguration can occur when the internal POR negates<sup>2</sup>. There are multiple ways to address the requirements for external configuration depending on the system requirements such as external clock use and GPIO on the configuration pins. The examples in the external configuration subsections of this document ensure that the errata will not be seen in the target system. Depending on the external configuration circuitry, if  $\overline{RSTOUT}$  has a pull up resistor to pull  $\overline{RSTOUT}$  up during POR, then a conditioned external reset out ( $\overline{ERSTOUT}$ ) may be required for external devices that require  $\overline{RSTOUT}$  to be low even during the internal POR time of the MCU. Freescale evaluation boards provide  $\overline{ERSTOUT}$  that ANDs  $\overline{RESET}$  and  $\overline{RSTOUT}$  together. (The  $\overline{ERSTOUT}$  circuit is shown in external reset configuration sections, but can be used with the default [internal] reset configuration.)

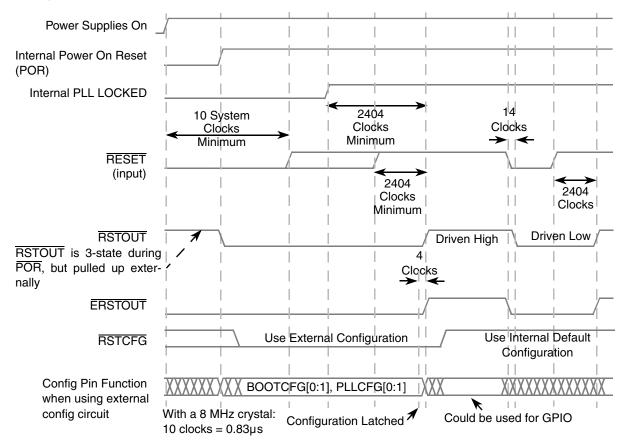

The following figure shows the configuration pins under different power up scenarios. During POR, RSTOUT floats. The RESET input to the MCU must be driven low by external Low Voltage Detect circuit before POR negates. The POR voltage trip point is specified in the device data sheet (POR will negate on the MPC5554 between 1.1 and 1.35 volts for the 1.5 V (nominal) supply. Additionally, the device will be kept in the POR state until both the RESET pin power supply (VDDEH6³) and VDDSYN are between 2.0 V and 2.85 V. (VDDSYN will also assert the internal POR once it is powered to 0.3 volts.)

#### NOTE

External low voltage detect (LVD) circuits must be used on all of the external power supplies to ensure proper operation of the device. The external LVD circuitry must ensure that the power supplies are within the recommended operating voltage prior to releasing the  $\overline{\text{RESET}}$  input to the MCU.

<sup>2.</sup> See errata number e488 (ERR000488/e488) on the device errata list.

<sup>3.</sup> Although VDDEH6 is normally a 5 V supply, it can be used at a nominal voltage of 3.3 volts. Therefore the POR low voltage detect must support 3.3 V operation, as well as 5 V operation.

#### **Reset Configuration**

Figure 2. External reset configuration and conditioned RSTOUT timing

In the figure above, both a default configuration ( $\overline{RSTCFG} = 1$ ) and an external configuration ( $\overline{RSTCFG} = 0$ ) are shown.

$\overline{\text{RESET}}$  must be asserted for at least 10 clocks and includes a two clock glitch filter circuit.  $\overline{\text{RSTOUT}}$  will negate 2404 clocks after either  $\overline{\text{RESET}}$  is negated or the system Phase Lock Loop (PLL) locks, whichever occurs last. If the device is out of reset ( $\overline{\text{RSTOUT}}$  negated) and  $\overline{\text{RESET}}$  is asserted,  $\overline{\text{RSTOUT}}$  will assert after 14 system clocks (two clock glitch filter + 10 clock minimum  $\overline{\text{RESET}}$  assertion time + two clocks for the reset state machine).

#### **NOTE**

All reset timing is based on the internal system clock. The internal system clock can either be the "limp" clock (Self-clock mode [SCM] frequency) or the PLL frequency depending on which is active and selected for use by the device.

## 2.1 Internal Power On Reset

Internal to each of the MPC55xx devices, a Power On Reset circuit is included to ensure that the internal logic of the device and the states of all of the device pins is in a predictable state until a minimum set of the power supplies are near to an operational voltage. Not every power supply input to the device is monitored, only the three most critical supplies are monitored. These supplies are shown in the following table.

Table 9. Critical POR power supplies

| Power Supply Pin(s) | Power supply description                   |

|---------------------|--------------------------------------------|

| VDD                 | Device internal low voltage circuit supply |

| VDDSYN              | Phase Lock Loop and Crystal power supply   |

| VDDEH6              | Power supply for the Reset pin             |

Below is an extract from a typical<sup>4</sup> data sheet for the specifications for the voltage requirements for each of the critical power supplies. The actual and latest device data sheet should be consulted. Until all of these supplies are greater than the specifications shown, the internal circuitry and the pads are kept in a safe state.

Table 10. POR specifications

| Specification | Charac                                       | cteristic            | Symbol             | Minimum | Maximum | Units |

|---------------|----------------------------------------------|----------------------|--------------------|---------|---------|-------|

| 1             | 1.5 C (V <sub>DD</sub> )<br>POR <sup>1</sup> | Negated (ramp up)    | V <sub>POR15</sub> | 1.1     | 1.35    | V     |

|               |                                              | Asserted (ramp down) |                    | 1.1     | 1.35    |       |

| 2             | 3.3 V (VDDSYN)<br>POR <sup>2</sup>           | Asserted (ramp up)   | V <sub>POR33</sub> | 0.0     | 0.30    | V     |

|               |                                              | Negated (ramp up)    |                    | 2.0     | 2.85    |       |

|               |                                              | Asserted (ramp down) |                    | 2.0     | 2.85    |       |

|               |                                              | Negated (ramp down)  |                    | 0.0     | 0.30    |       |

| 3             | RESET pin<br>Supply (V <sub>DDEH6</sub> )    | Negated (ramp up)    | V <sub>POR</sub> 5 | 2.0     | 2.85    | V     |

|               | POR                                          | Asserted (ramp down) |                    | 2.0     | 2.85    |       |

- The internal POR signals are V<sub>POR15</sub>, V<sub>POR33</sub>, and V<sub>POR5</sub>. On power up, assert RESET before the internal POR negates.

RESET must remain asserted until the power supplies are within the operating conditions as specified in DC Electrical

Specifications table of the Data Sheet. On power down, assert RESET before any power supplies fall outside the operating conditions and until the internal POR asserts.

- The input low voltage (VIL\_S) is guaranteed to scale with V<sub>DDEH6</sub> down to V<sub>POR5</sub>

There are no power supply sequencing requirements, however, the state of the Input/output pins does depend on the order of the power supplies and the state of the internal POR<sup>5</sup>. This may dictate a power supply sequence if the pin state shown in the tables below (a typical extract is shown) is not desired. These states are shown in the device data sheet. The high voltage (medium and slow speed) pins have different supply requirements than the higher speed, low voltage pins. This first table is for the high speed pins (low voltage pins [generally 3.3 V typical or less]).

Table 11. Pin status for Fast Pads During the Power Sequence

| V <sub>DDE</sub> | V <sub>DD33</sub> | V <sub>DD</sub> | POR      | Pin state for the fast pads |

|------------------|-------------------|-----------------|----------|-----------------------------|

| Low              | _                 | _               | Asserted | Low                         |

| V <sub>DDE</sub> | Low               | Low             | Asserted | High                        |

| V <sub>DDE</sub> | Low               | $V_{DD}$        | Asserted | High                        |

| V <sub>DDE</sub> | V <sub>DD33</sub> | Low             | Asserted | High impedance (Hi-Z)       |

| V <sub>DDE</sub> | V <sub>DD33</sub> | $V_{DD}$        | Asserted | Hi-Z                        |

| $V_{DDE}$        | V <sub>DD33</sub> | $V_{DD}$        | Negated  | Functional                  |

This table shows the medium and slow pins.

### Qorivva MPC5500 Minimum Board Requirements, Rev 0, August 21, 2013

<sup>4.</sup> This extract is from the MPC5554 Data sheet, revision 4, dated May 2012.

<sup>5.</sup> The POR state is determined by the table able.

Table 12. Pin status for Medium and Slow Pads During the Power Sequence

| V <sub>DDEH</sub> | V <sub>DD</sub> | POR      | Pin status for Medium and<br>Slow Pad Output Driver<br>mad_mh (medium) pad_sh<br>(slow) |

|-------------------|-----------------|----------|-----------------------------------------------------------------------------------------|

| Low               | _               | Asserted | Low                                                                                     |

| V <sub>DDEH</sub> |                 | Asserted | Hi-Z                                                                                    |

| V <sub>DDEH</sub> | V <sub>DD</sub> | Asserted | Hi-Z                                                                                    |

| V <sub>DDEH</sub> | $V_{DD}$        | Negated  | Functional                                                                              |

## 2.2 Minimum (default) RESET configuration circuit (most commonly used)

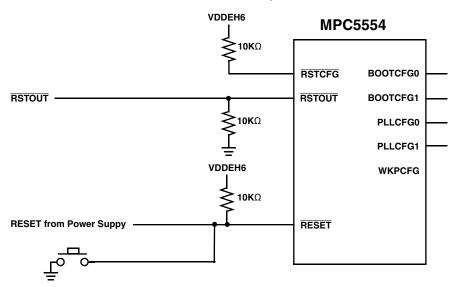

The figure below shows the minimum circuitry required if the internal default reset configuration is used ( $\overline{RSTCFG} = 1$ ). This is the most commonly used configuration. The default reset configuration uses an internal crystal oscillator (with an external crystal reference) and searches the internal flash for a valid reset configuration half word (RCHW) BOOTID (RCHW[BOOTID] = 0x5A). If no valid RCHW is found, the device attempts a serial boot (either CAN or SCI). A pull down should be included on  $\overline{RSTOUT}$  since this pin floats during the internal power on reset (POR). This allows  $\overline{RSTOUT}$  to be low during POR for external devices. A pull up resistor must be included on  $\overline{RESET}$  since it could be driven from multiple open drain/open collector devices. The internal pull up on  $\overline{RESET}$  may not be sufficient to pull up all external devices or even to ensure that that  $\overline{RESET}$  will negate in time for proper configuration of the device. The circuit in this figure is for devices without a PLL Config 2 (PLLCFG[2]) pin using an 8 to 20 MHz crystal. This circuit can also be used on devices with a PLLCFG[2] pin, if PLLCFG[2] is tied low (to use an 8 to 20 MHz crystal).

Figure 3. Absolute minimum reset configuration circuit for the MPC5500 devices (without FlexRAY)

On devices with a PLLCFG[2] pin (MPC5567 and MPC5561), the following minimum circuit can be used with a 40 MHz crystal.

Figure 4. Absolute minimum reset configuration for a 40 MHz crystal

#### **NOTE**

The PLLCFG[2] pin can not be used as a general purpose I/O pin. It is always the PLLCFG[2] function, the feature is not latched by reset.

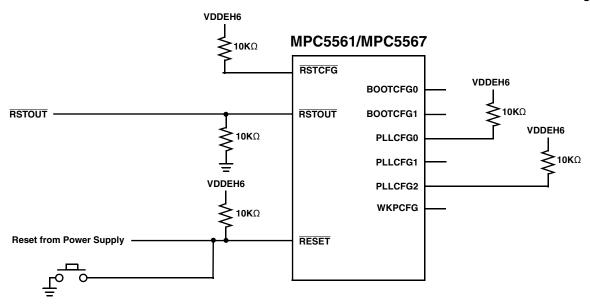

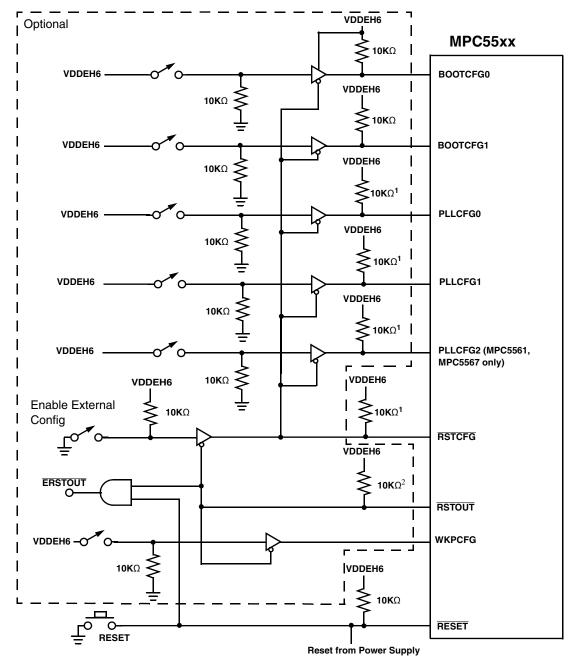

## 2.3 External RESET configuration with optional GPIO on config pins

The figure below shows the circuitry required to use an external configuration, especially when using the external configuration and using the configuration pins as General Purpose Input/Output (GPIO) after reset. An external configuration is required when using an external clock reference source or when booting from external memory (feature not available on all devices). This circuit has a pull up on  $\overline{RSTOUT}$  in order to disable driving the reset configuration during the internal POR and during normal operation. An AND gate is included in this circuit (with  $\overline{RESET}$  [in] and  $\overline{RSTOUT}$  on its inputs) to generate a reset for any other circuitry in the system that requires a reset signal. On the evaluation boards, this reset ( $\overline{ERSTOUT}$ ) only drives the reset LED and the DP83848 Ethernet Physical interface device (if applicable), but can be used if additional peripherals are added to the board that require a reset. This circuit (below) is required to sequence  $\overline{RSTCFG}$  and the PLLCFG[0:1] pins. This addresses the possible issue from errata e488.  $\overline{RSTCFG}$  is held high until the internal POR<sup>6</sup> negates and then applies the reset configuration to the configuration pins.

<sup>6.</sup> All of the MPC5500 Family devices contain a rough Power On Reset circuit to hold internal circuits in reset until sufficient voltage is available on all of the power supplies. See Internal Power On Reset.

#### **Reset Configuration**

Notes:

- 1. This pull up is required, even if the internal reset configuration word is used.

- 2. The 10K resistor on RSTOUT should be a pull down if the optional external configuration circuitry is not used.

Figure 5. External Configuration circuitry

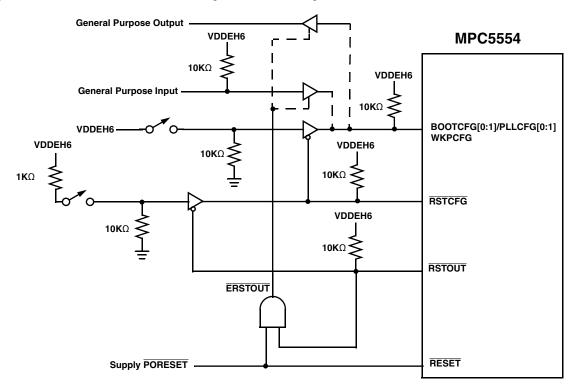

## 2.3.1 Using configuration pins as GPIO

If the external configuration pins to be used for General Purpose Input or Outputs (GPIO) and the external configuration pins are used for configuring the device modes ( $\overline{RSTCFG} = 0$ ), additional circuitry is required to that the configuration pins are in the proper state for configuring the device. The GPIO functionality should be gated by the conditioned external  $\overline{ERSTOUT}$ .

#### NOTE

Care must be taken to ensure that the configuration pins (RSTCFG, PLLCFG[0:2], and BOOTCFG[0:1]) are in the proper state while  $\overline{\text{RESET}}$  is asserted.

In the following circuit,  $\overline{RSTOUT}$  is used to gate the  $\overline{RSTCFG}$  pin. This circuit depends on the fact that  $\overline{RSTOUT}$  negates internally before  $\overline{RSTCFG}$  is asserted when using an external configuration.

Figure 6. Reset configuration with GPIO circuit (not all pins shown for simplicity)

The circuit shown on the WKPCFG is only needed if the WKPCFG pin is to be used for GPIO following reset. If the GPIO function is not required for this pin, it can just be pulled up or down depending on user requirements.

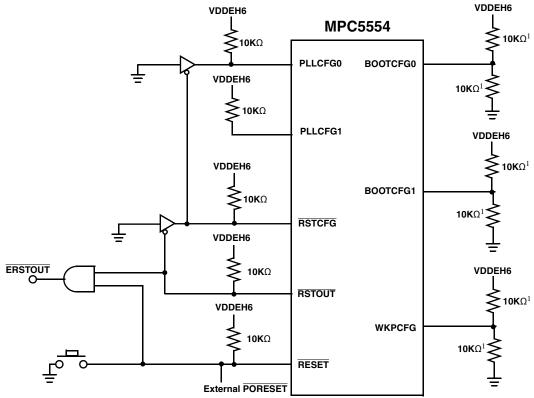

## 2.4 Minimum required circuitry for external reference clock mode (with optional GPIO)

When using the MPC5500 devices with an external reference clock (PLLCFG[0:1]=0b01), extra circuitry is required to ensure that the system clock will be configured properly out of power-on reset (POR - internal MPC5500 POR circuit). During POR, the default value (default POR configuration) of the PLLCFG[0:1] bits are set to 0b10 and RSTCFG is high. External reference clock mode requires that the PLLCFG[0:1] bits have a value of 0b01 and therefore requires the external configuration. External circuitry is required to ensure that the value of 0b00 is not seen on the internal version of the PLLCFG[0:1] pins during the change from the default POR configuration to the external configuration.

The figure below shows the minimum circuitry required to select the external reference clock mode of the PLL and optionally allows use of the configuration pins as General Purpose Input/Outputs (GPIO). The BOOTCFG[0:1] pins can be pulled up or down depending on the boot memory configuration required by the user. This circuitry initially selects the default POR configuration. After the internal POR negates, RSTOUT will begin to drive and will enable the change to the external configuration, which then switches PLLCFG[0] from a high to a low.

In the following circuit,  $\overline{RSTOUT}$  is used to gate the  $\overline{RSTCFG}$  pin. This circuit depends on the fact that  $\overline{RSTOUT}$  negates internally before  $\overline{RSTCFG}$  is asserted when using an external configuration.

Notes:

1. Populate these resistors as required to select the boot mode (BOOTCFG[0:1]) and the WKPCFG value.

Figure 7. Minimum reset configuration pin circuitry for external clock mode

See the previous section for circuitry to isolate the GPIO functions from the configuration functions.

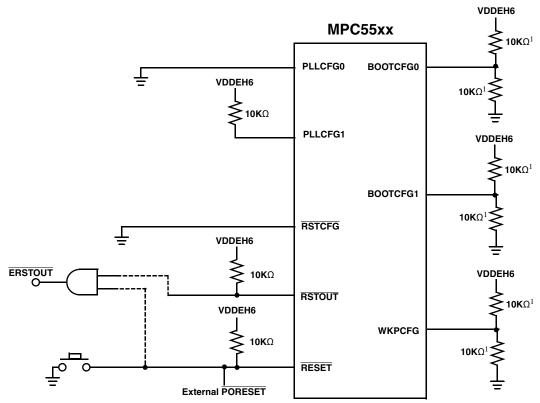

## 2.5 Absolute minimum RESET configuration circuit for external clock (GPIO on config pins not allowed)

The figure below shows the absolute minimum circuitry required when using an external clock reference. The device configuration pins cannot be used as General Purpose Input/Output (GPIO) when using this absolute minimum circuitry. Software must not change the default settings of the Pad Configuration Registers (PCR) for the Phase Lock Loop (PLL) configuration pins (PLLCFG[2:0]). In this case, the reset configuration pin (RSTCFG) can be pulled low all of the time.

#### NOTE

With this configuration, the GPIO circuitry on the PLLCFG[0:1] configuration pins must not be enabled by software.

Notes:

1. Populate these resistors as required to select the boot mode (BOOTCFG[0:1]) and the WKPCFG value.

Figure 8. Absolute minimum reset configuration circuit for the MPC5500 devices (No GPIO on config pins)

ERSTOUT is an optional signal depending on system requirements. Some systems may use this signal to disable external devices while the MCU is in reset such as external memories or even external driver circuits.

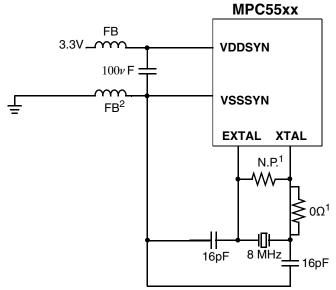

## 3 Clock Circuitry

The external crystal for the Frequency Modulated Phase Lock Loop (FMPLL) must be in the range of 8 to 20 MHz for most of the MPC5500 devices and connected to the EXTAL and XTAL pins. The Freescale evaluation boards for these devices typically have an 8 MHz crystal oscillator, which is multiplied by the FMPLL internal circuitry to obtain the desired operating speed. Some boards (devices that support FlexRay) use a 40 MHz crystal. Typical connections are shown in the following figure.

- 1. Provisions for an external feedback resistor and a series resistors should be made on board layouts. The feedback resistor is not currently required and should not be populated. The series resistor should be a 0  $\Omega$  resistor. On the Freescale evaluation boards, the series resistor is implemented as a cut-away options with pads for a resistor.

- 2. The VSSSYN Ferrite Bead (FB) is not required if VSSSYN is connected directly to a ground plane (not just a ground signal trace).

Figure 9. MPC5500 VDDSYN and crystal connections (8-20 MHz crystals)

### **NOTE**

The oscillator circuit should be placed as close as possible to the MCU. In order to minimize signal degradation, the circuitry should all be placed on the same PCB layer avoiding unnecessary vias where possible. The VSSSYN trace should be used as a shield around the crystal components.

VSSSYN should be used as a shield for the oscillator and then connected to the ground plane at the crystal load capacitors.

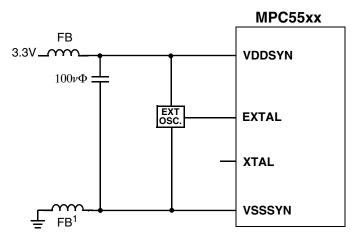

The figure below shows the connections when using an external reference clock. When using an external reference clock, XTAL should be left open.

1. The VSSSYN Ferrite Bead (FB) is not required if VSSSYN is connected to a ground plane (not just a ground signal trace).

Figure 10. External Clock reference example

Some devices, such as the MPC5567 and the MPC5561 that support FlexRAY, also allow for a 40 MHz external crystal configuration. These devices include an additional configuration pin (PLLCFG[2]) to select between the 8-20 MHz crystal or the 40 MHz crystal. PLLCFG2 does not exist and was used as VRCVSS on other devices (that do not support the 40 MHz option). To select the 40 MHz option, PLLCFG[2] should be pulled or driven high.

Setting PLLCFG[2] high forces the Predivider (set to divide-by-two) in the PLL to be selected by default, making the input to the PLL the same as the 8-20 MHz option.

When using the 40 MHz crystal, the buffered crystal frequency is available to be selected for the FlexRAY protocol clock. Similarly, the FlexCAN can also use the buffered crystal as a reference.

When a ferrite bead is used, it should have a low resistance at DC voltage with an increasing resistance at higher frequencies (100 MHz). The following table shows a recommended ferrite bead.

Manufacturer Part number DC resistance Impedance at **Rated current** Package size Operating 100 Mhz, 20°C temperature range 2000<sup>1</sup> mA BLM31PG391S  $0.05\Omega$ -55 to +125°C Murata  $3900 \pm 25\%$ 1206

Table 13. Recommended ferrite bead

1. 1000 mA at 125°C

## **Power supply requirements**

The MPC5500 devices require 5V, 3.3V, and 1.5V power supplies. The 1.5V can be generated using an on-chip regulator controller with a linear external pass transistor.

The table below lists the supplies required by the MPC5500. Many of the supply pins can be used over a wide voltage range.

Low voltage supplies generally can be used at nominal voltage ranges from 1.8 to 3.3 V and high voltage supplies can use a nominal 3.3 or 5 V supply. There are several supplies that must be a particular voltage (either 3.3 V or 5 V). The simplest board configuration uses 3.3 V and 5 V as the main external supplies and uses the internal 1.5 V regulator controller. The most commonly used configuration uses a bus voltage of 3.3 V and all peripheral I/O modules at 5.0 V. Due to power supply segmenting, some peripheral power supplies can be used at 3.3 V and some at 5 V if required, as long as the pins are on different power supply segments. The I/O voltage is the same for all pins sharing a common power supply segment. In addition, if standby SRAM operation is required (SRAM is kept powered while all of the other supplies are off), a 1.0 V SRAM standby supply should be provided.

**Symbol** Description Voltage range<sup>1</sup> Maximum current<sup>2</sup> VDDE H External I/O Supply Input 40 mA<sup>3</sup> 3.3V-5.0V **VPP** Flash program/erase supply 5.0V 35 mA input Analog power input 5.0V 25 mA **VDDA** VDDE, VDD33, VDDSYN External "low" voltage I/O 1.8V-3.3V 15 mA supply input VRC33 Voltage Regulator Control 3.3V 320 mA supply **VFLASH** Flash read supply input 3.3V 4 mA

Table 14. MPC5500 power supply requirements

Table continues on the next page...

#### Power supply requirements

Table 14. MPC5500 power supply requirements (continued)

| Symbol | Description                 | Voltage range <sup>1</sup> | Maximum current <sup>2</sup> |

|--------|-----------------------------|----------------------------|------------------------------|

| VDD    | Internal logic supply input | 1.5V                       | 450 - 875 mA <sup>4</sup>    |

| VSTBY  | SRAM standby power input    | 1.0                        | <300µA <sup>5</sup>          |

- 1. Nominal voltage

- 2. Consult the electrical specifications in the device Data Sheet for the latest specifications.

- 3. I/O current required for driving external loads are not included. See the device Data Sheet for calculating required based on the load and switching frequency.

- 4. Maximum current depends on the device. See the individual device data sheet.

- 5. At the maximum specified device junction temperature of 150°C.

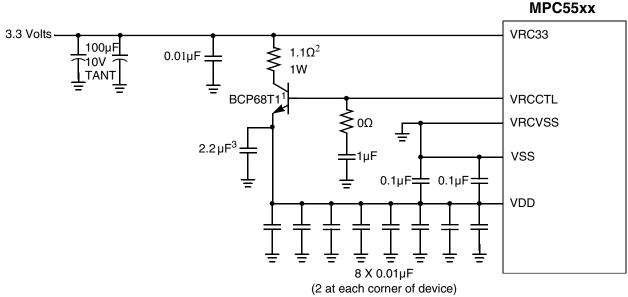

## 4.1 Internal regulator control, VDD, bypassing

The MPC5500 MCUs contain an internal regulator control circuit for the 1.5 V internal core supply. The control circuit requires an external pass transistor. The recommended pass transistor for the internal regulator is the On Semiconductor BCP68T1 NPN medium power transistor.

#### **NOTE**

The BCP68 transistor requires more heat-sinking than the minimum SOT223 footprint board layout. Extra area is required.

An alternate transistor is the On Semiconductor NJD2873T4G<sup>7</sup>. This transistor is in a DPAK package and allows for higher power dissipation. The NJD2873T4G is recommended for the MPC5554, MPC5561, and MPC5566. All of the other devices in the MPC5500 family can use the BCP68.

Table 15. Pass transistor requirements

| Symbol Description |                             | Value              | Unit  |  |

|--------------------|-----------------------------|--------------------|-------|--|

| h <sub>FE</sub>    | DC current gain             | > 85 <sup>1</sup>  | _     |  |

| $P_{D}$            | Power Dissipation           | > 1.0 <sup>2</sup> | Watts |  |

| I <sub>C</sub>     | Collector current (maximum) | 1.0                | A     |  |

- 1. The maximum gain should be less than 550.

- 2. 1.5W preferred

The table below shows the recommended pass transistors for the different MPC5500 devices.

Table 16. Recommended pass transistors by device

| Device  | Recommended pass transistor |

|---------|-----------------------------|

| MPC5534 | BCP68 or NJD2873T4G         |

| MPC5553 | BCP68 or NJD2873T4G         |

| MPC5554 | NJD2873T4G                  |

| MPC5561 | NJD2873T4G                  |

| MPC5565 | BCP68 or NJD2873T4G         |

Table continues on the next page...

<sup>7.</sup> Also available from On Semiconductor is the MJVNJD2873T4G that provides full Automotive AEC-Q101 qualification and Unique Site and Control Change requirements.

Table 16. Recommended pass transistors by device (continued)

| Device Recommended pass transistor |                     |

|------------------------------------|---------------------|

| MPC5566                            | NJD2873T4G          |

| MPC5567                            | BCP68 or NJD2873T4G |

When using the on-chip 1.5-V regulator, the following bypass capacitors should be used on the VDD pins: one  $2.2\mu F$ , two 100nF, and eight 10nF capacitors. These should be the only bypass capacitors on the VDD supply pins. A higher value collector bulk capacitor may be required in some board layouts to reduce regulator oscillation. Board layouts should accommodate the option of a base resistor and allow for a collector capacitor in the range of 1 to 22  $\mu F$ .

Table 17. VDD bypass capacitors

| Quantity | Value  |

|----------|--------|

| 1        | 2.2 μF |

| 2        | 100 nF |

| 8        | 10 nF  |

The  $2.2 \,\mu\text{F}$  capacitor should be located near the emitter of the NPN transistor. The  $10 \,\text{nF}$  should be placed as close as possible to the device pins.

The following figure shows the recommended configuration of the internal 1.5 V regulator controller, including the recommended bypass capacitors.

### Notes:

- 1. Alternate pass transistor NJD2873T4. The NJD2873T4 does not require a collector resistor.

- 2. Power dissipation resistor (size 2512, 1 Watt).

- 3. This bulk capacitor should be near the emitter of the BCP68T1/NJT2873T4.

Figure 11. MPC5500 internal regulator supply connections

## 4.2 VDDSYN considerations

VDDSYN is the power supply for the oscillator and the clock Frequency Modulated Phase Lock Loop (FMPLL or PLL for short). VDDSYN should be filtered separately from the rest of the 3.3 V power supplies to reduce both noise on the main 3.3 V supply and to prevent noise from the 3.3 V supply affecting the stability of the PLL.

## 4.3 External memory power requirements

If external memories are included in the final system, the currents need to be provided from the system power supply. The maximum currents for the SRAM devices included in this application note are shown in the following table.

Table 18. External memory power requirements

| Memory       | Part number | Voltage (V) | Maximum Current (mA) |

|--------------|-------------|-------------|----------------------|

| Cypress SRAM | CY7C1338    | 3.3V        | 375 mA               |

| ISSI SRAM    | IS61SF12832 | 3.3V        | 280 mA               |

| ISSI SRAM    | IS61SF25618 | 3.3V        | 170 mA               |

## 4.4 Decoupling capacitors

Local decoupling capacitors should be used on every MCU power supply pin. Many of the capacitors can be mounted on the underside of the PCB and should be located as close as possible to the respective power pins. In addition to the MCU, all other IC devices should have decoupling capacitors close to each power supply pin. Although not used on the MPC5500 evaluation boards, Dupont<sup>TM</sup> has developed an embedded capacitor board process that uses the entire power and ground places of the PCB for capacitors. This uses their Interra<sup>TM</sup> HK 10 planar capacitor laminate (approximately 2nF per square inch) and could be used to eliminate some of the localized bypass capacitors<sup>8</sup>. See AN2705 "Signal Integrity Considerations with MPC5500-based systems" and AN2706 "EMC Guidelines for MPC5500-based Systems" for more information on bypass capacitors for the power supplies.

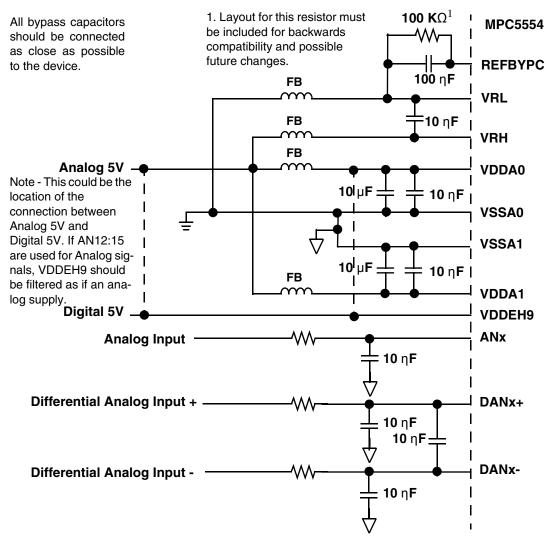

## 4.5 Enhanced Queued Analog to Digital Converter supply connections

The enhanced Queued Analog to Digital Converter (eQADC) should use a filtered power supply separate from the digital 5V. On the MPC5500 evaluation boards, a separate 5 V supply is used as a separate filtered analog supply for the eQADC. Filtered reference supplies should be provided for high and low voltage references (VRH and VRL). The impedance of the traces of the following analog differential pairs should be matched: AN0/AN1, AN2/AN3, AN4/AN5 and AD6/AN7.

Unused Analog inputs should be pulled to ground.

The following figure shows the proper connections of the eQADC power supply connections. For best noise performance, the voltage reference high and low pins (VRH, VRL) should be filtered and kept clean.

<sup>8.</sup> Due to cost, these typically are not used in Automotive applications, but is mentioned for other types of applications that may need a reduced set of external components.

Figure 12. MPC5500 Preferred eQADC supply bypassing

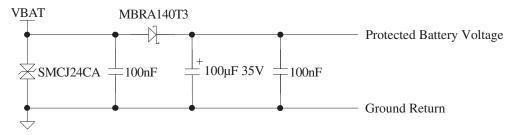

## 4.6 Miscellaneous power requirements

Additional board components also require current from the supplies. The power supply should be designed to support the current requirements of all external devices. The table below shows the maximum current ratings for the major contributing devices (in addition to the MPC5500 MCU and the external SRAM).

|                             |             | -                   |                      |

|-----------------------------|-------------|---------------------|----------------------|

| Device                      | Part Number | Nominal Voltage (V) | Maximum current (mA) |

| Ethernet Physical Interface | DP83848     | 3.3V                | 375 mA               |

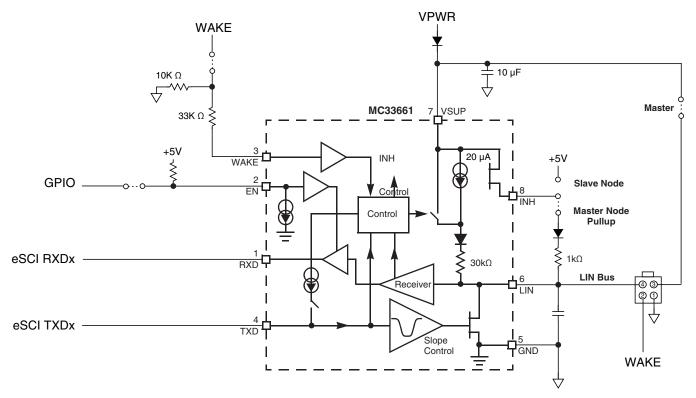

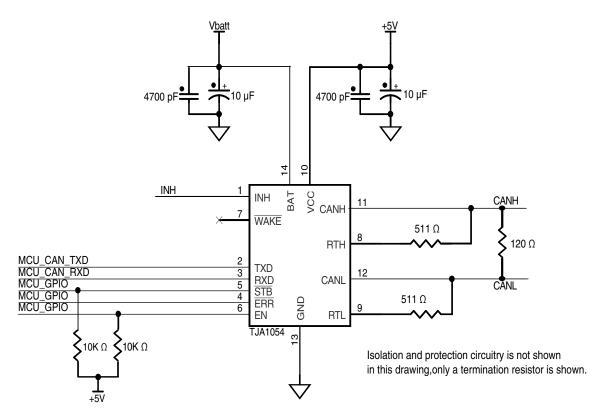

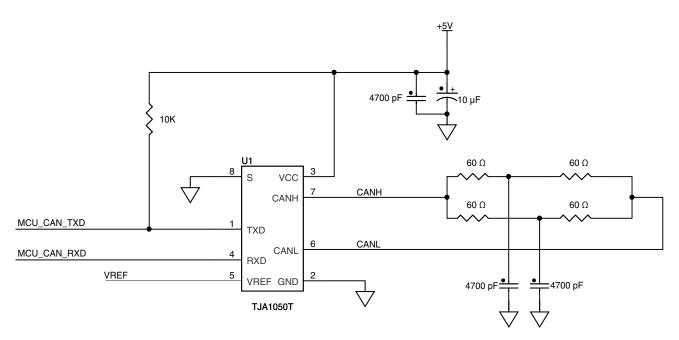

| LIN Transceiver             | MC33661     | 12V                 | 8 mA                 |

| CAN Transceiver             | TJA1050T    | 5V                  | 75 mA                |

| FlexRAY transceiver         | TJA1080AT   | 3.3V - 5V           | 62 mA                |

| RS232 Transceiver           | HIN202      | 5V                  | 15 mA                |

Table 19. External device power requirements

## 5 External pull resistors

Except in the cases documented in this application note, external pull up or down resistors are not required on any pins, except to over ride the default state of the pins. After reset, the state of the pull device is controlled by the pad configuration register in the System Integration Unit (SIU\_PCR0-SIU\_PCR230) for that pin. The direction of the internal pull device is documented in the device Data Sheet and Reference Manual, however, the setting can be changed by software in the PCR register for each pin.

## 5.1 Bus control pins

Unless the MPC5500 device is not in multi-processor mode (BOOTCFG[0:1] = 0b11,  $\overline{RSTCFG}$  = 0b0), the bus control pins are not enabled. This allows minimum configuration boards to eliminate pull up resistors on the Bus request ( $\overline{BR}$ ), Bus Grant ( $\overline{BG}$ ), and Bus Busy ( $\overline{BB}$ ) pins. Normally, external pull ups are not required on the Transfer Acknowledge ( $\overline{TA}$ ) and Transfer Error Acknowledge ( $\overline{TEA}$ ) signals, but pull ups have been included on the MPC5500 evaluation board to handle situations where they might be required.

## 5.2 Timer pins

Following reset, all of the enhanced Modular Input/Output System (eMIOS) and enhanced Timing Processor Unit (eTPU) pins have a default state based on the WKPCFG pin. If WKPCFG is high, then the timer pins have pull ups and pull downs if WKPCFG is low. If the state of some of these pins needs to be over-ridden during reset, an external pull is required that has a value strong enough to overcome the internal  $130\mu$ A pull current. WKPCFG is latched 4 clocks prior to the negation of  $\overline{\text{RSTOUT}}$  by the MCU.

## 5.3 Other pins

To ensure that the internal factory test modes are not entered accidentally, a strong pull up  $(1-2K\Omega)$  can be placed on the TEST pin to VDDE7 (usually 3.3 V). This is the same power supply as the Nexus pins. Unused pins should be configured with both the input and the output buffers turned off, but with the weak pull downs enabled.

## 6 External bus interface

The MPC5500 devices in most packages include a 32-bit wide external data bus with up to a 26-bit address bus. On some devices, however, the package limits the data bus to only 16-bits and in other cases, does not support any access to an external data or address bus. An address bus of 20-bits is supported on all devices that support an external bus, however, some devices support an address bus of up to 24-bits and in some cases 26-bit, for the external address bus. On the Freescale evaluation boards, the external bus is used for access to SRAM only. The external bus could also be connected to a variety of other devices, such as stand-alone Flash memories or peripherals (either fast or slow<sup>9</sup>). When using the Ethernet interface on the MPC5553 and MPC5566 on the MPC5553 evaluation board, only a 16-bit data bus is available. The MPC5534 and MPC5565 always have only a 16-bit data bus. The address bus width for the different devices in the MPC5500 family is shown in the following table.

<sup>9.</sup> Keep in mind, however, that accesses to the external bus stalls the core CPU any time data is read from the external bus.

Table 20. Address bus width support

| Device  | Maximum Address<br>bus signals | External Address signals available <sup>1</sup>     |

|---------|--------------------------------|-----------------------------------------------------|

| MPC5534 | 24-bit                         | ADDR[8:31]                                          |

| MPC5553 | 24-bit                         | ADDR[8:31]                                          |

| MPC5554 | 24-bit                         | ADDR[8:31]                                          |

| MPC5561 | 26-bit                         | ADDR[12:31], ADDR[8:31], or ADDR[6:29]              |

| MPC5565 | 26-bit                         | ADDR[10:31] <sup>3</sup>                            |

| MPC5566 | 26-bit                         | ADDR[12:31], ADDR[8:31], or ADDR[6:29]              |

| MPC5567 | 26-bit                         | ADDR[12:31], ADDR[8:31], or ADDR[6:29] <sup>2</sup> |

- 1. The number of address signals may depend on the package size. All ADDR signals may not be available on pins.

- 2. ADDR[10:31] in the 324 PBGA package.

- 3. Limited by package.

#### NOTE

ADDR[31] is the least significant bit of the MCU external address. Depending on the memory size (by-32, by-16, or by-8), ADDR[29], ADDR[30], or ADDR[31] may be connected to the least significant address line of the memory (ADDR0).

#### NOTE

Likewise, on memories that require the data bus (DATA) be connected in a particular order (primarily external Flash memories that require programming via specific data bus access values), DATA[31] is the least significant bit of the data and DATA[0] is the most significant bit of the data.

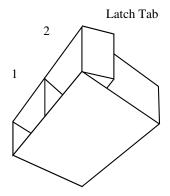

Some devices support a separate Calibration Bus Interface that is independent from the External Bus Interface. This document does not cover use of the calibration bus interface. On the MPC5500 MCUs, the Calibration Bus Interface is 16-bit data bus. The address bus can be from 19 to 21 bits depending on the number of chip selects required. The Calibration Bus is only available in a special "VertiCal" package. The VertiCal package fits in the same footprint (a small additional footprint is required for alignment keys) as the standard production device. See the VertiCal documentation for each device. The following table shows the calibration bus configurations available on the MPC5500 devices.

Table 21. Calibration Bus Support

| MCU     | Calibration Bus Interface supported |

|---------|-------------------------------------|

| MPC5534 | Yes (ADDR[10:30])                   |

| MPC5553 | Partial <sup>1</sup>                |

| MPC5554 | No                                  |

| MPC5561 | No                                  |

| MPC5565 | Yes (ADDR[10:30])                   |

| MPC5566 | Yes (ADDR[10:30])                   |

| MPC5567 | Yes (ADDR[10:30])                   |

ADDR[12:26] are shared with the normal external address bus interface signals. ADDR[10:11] and ADDR[27:30] are separate calibration bus signals. Calibration data bus uses the External Bus Interface DATA[16:31]. See appendix B "Calibration" of the MPC5553/MPC5554 Microcontroller Reference Manual.

#### External bus interface

### 6.1 External SRAM

The MPC5500 evaluation boards provide 512 KB of SRAM (either 256K by 16 or 128K by 32) that can be used for calibration overlay or program development. Only CS0 and CS1 are available on the evaluation boards for the SRAM chip select, however, in target systems, any chip select pin could be used. The IS61SF25618/IS61SF12832-10TQI (ISSI) is the preferred SRAM; however, the Cypress CY7C1338 is pin compatible. An access time of 10 nS is sufficient for the MPC5500 devices since the external bus runs at 1/2 the system frequency of 132 MHz (66 MHz bus maximum). The by-18 device is recommended instead of the by-16 since it seems to be more widely available. The following table shows suggested SRAMs.

| Table 22. | Example | <b>SRAM</b> | part | numbers |

|-----------|---------|-------------|------|---------|

|-----------|---------|-------------|------|---------|

| Manufacturer | Part number         | Size                  | Supply<br>Voltage | Speed      | Burst | Temperature range | Comments                     |

|--------------|---------------------|-----------------------|-------------------|------------|-------|-------------------|------------------------------|

| ISSI         | 61SF12832-10T<br>QI | 4 Mbit (128k x<br>32) | 3.3V <sup>1</sup> | 100<br>MHz | Yes   | Industrial        | Pin compatible to<br>Cypress |

| ISSI         | 61SF25618-10T<br>QI | 4 Mbit (256k x<br>18) | 3.3V <sup>2</sup> | 100<br>MHz | Yes   | Industrial        |                              |

| Cypress      | CY7C1338            | 4 Mbit (128k x<br>32) | 3.3/2.6V          | 100<br>MHz | Yes   | Industrial        | Flow through<br>SRAM         |

- 1. 2.6V version available, 61SLF12832-10TQI

- 2. 2.6V version available, 61SLF25618-10TQI

All of the listed SRAMs are burstable, flow-through (non-pipelined) devices that operate in 32-bit mode and can also be addressed as bytes or half-words. This is preferable over the CY7C1339 as it allows better emulation of different wait states for benchmarking and flash emulation. The CY7C1339 is a pipelined access and requires a minimum of 1 wait state, regardless of the operating speed.

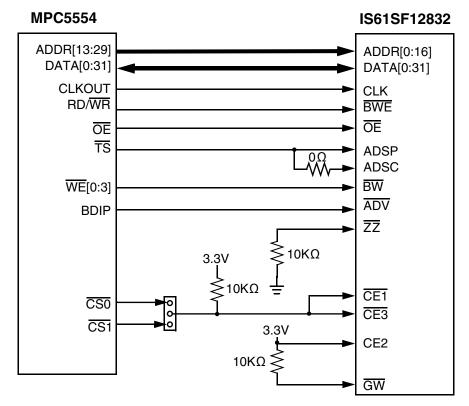

The figure below shows a typical 32-bit SRAM interface. For a 32-bit bus, address lines ADDR[30] and ADDR[31] may not need to be connected to the memory if byte selection uses the WE/BE enables. If two by-16 memories are connected to form a 32-bit data patch, ADDR[30] selects which 16-bit memory will be selected.

Figure 13. MPC5554 to ISSI 61SF12832 interface (32-bit bus)

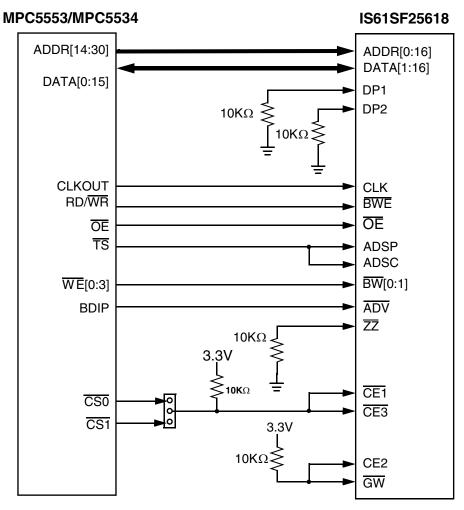

The figure below shows a typical 16-bit SRAM interface. Connection of ADDR31 may not be required for 16-bit memories that use WE[0:1] to select between bytes of the 16-bit word.

Figure 14. MPC5534 to ISSI 61SF25618 SRAM interface

Many memory devices allow the data bus to be connected as required for the best board routing, however, it is extremely important to ensure that the proper Write Enable/Byte Enable<sup>10</sup> pins are connected with the proper bytes of the data bus pins. Many SRAM devices name each byte of the data bus DATAa and do not number the actual SRAM bits. The associated Write Enable would also be WEa. The following table shows the mapping of the Data bus pin to write enable pin for the data bus.

Table 23. Data Bus to Write Enable/Byte Enable (WE/BE) mapping

| Data Bus Pins | Write Enable/Byte Enable |

|---------------|--------------------------|

| DATA[0:7]     | WE[0]                    |

| DATA[8:15]    | WE[1]                    |

| DATA[16:23]   | WE[2]                    |

| DATA[24:31]   | WE[3]                    |

Asynchronous SRAMs may also be used, but are not covered in this application note.

<sup>10.</sup> Selection of whether the WE[0:3]/BE[0:3] pins act as a Write Enable or a Byte Enable is controlled by a bit in the Memory Controller control registers and is settable on a chip select basis.

## 6.2 External bus termination

High speed signals should either be terminated or laid out with a fixed impedance of approximately  $33\Omega$ . On the MPC5500 evaluation boards, only the Clock Out (CLKOUT) pin is terminated. CLKOUT runs in two directions on the evaluation board, through a series terminating resistor (in a very short trace to the SRAM) and is fully terminated at the end of the trace that runs to the Nexus connectors. The Engineering Clock (ENGCLK) has series termination only.

## 7 Nexus Connector Recommendation and Pin-Out Definitions

For the MPC5500 family, Freescale recommends that a single 38-pin MICTOR connector be used on all boards for both reduced- and full-port Nexus modes (M38C). In cases where a more robust connector is required, Freescale recommends that the 51-pin Glenair connector be used (R51C).

The table below shows the possible connectors that can be used for the MPC5500 family devices.

| Connector             | Designation | Part number (for target system) | Total number of pins | Maximum message<br>data out signals (per<br>Nexus standard) |

|-----------------------|-------------|---------------------------------|----------------------|-------------------------------------------------------------|

| 3M MICTOR             | M38C        | 767054-1                        | 38 (+ 5)             | 8 (12 by extension)                                         |

| 3M MICTOR             | M38-2C      | 767054-1 <sup>1</sup> X 2       | 76 (+ 10)            | 16                                                          |

| Glenair MicroD Robust | R51C        | MR7580-51P2BNU                  | 51                   | 8 (12 by extension) <sup>2</sup>                            |

- 1. Other compatible part numbers are 2-5767004-2 (RoHS compliant), 2-767004-2, 767061-1, and 767044-1.

- 2. Although the Nexus standard definition normally only allows eight MDO signals, Freescale has extended the definition to include an extra four MDO signals.

Since full-port mode requires twelve MDO pins and both of these connectors<sup>11</sup> support only eight MDO pins, Freescale redefined some of the Vendor\_IO and Tool\_IO pins for the additional MDO signals (MDO[8:11]) on the MPC5500 family devices. The MICTOR connector option in the Nexus standard defined five vendor-defined pins (Freescale uses four of these signals for the extra MDO signals and left one extra pin), but the 51-pin robust connector only has three Vendor\_IO pins. Therefore, to support the full twelve MDO signals, two Tool\_IO pins were also defined as MDO signals on the robust connector option. The table below shows the recommended signal usage for the vendor-defined I/O pins, as well as tool vendor-defined I/O pins. Freescale has worked with tool vendors to ensure minimal impact to tool needs on these pins.

Table 25. Extended MDO definition to the Nexus Standard Connector using IO for additional MDO Signals

| Nexus pin designation | MPC5500 MICTOR definition | MPC5500 robust definition |

|-----------------------|---------------------------|---------------------------|

| VEN_IO0               | MDO9/GPIO80               | MDO9/GPIO80               |

| VEN_IO1               | MDO11/GPIO82              | MDO11/GPIO82              |

| VEN_IO2               | BOOTCFG1/IRQ3/GPIO212     | RSTOUT <sup>1</sup>       |

| VEN_IO3               | MDO8/GPIO70               | 2                         |

| VEN_IO4               | MDO10/GPIO81              | _                         |

| TOOL_IO0              | _3                        | _                         |

| TOOL_IO1              | _                         | _                         |

Table continues on the next page...

Qorivva MPC5500 Minimum Board Requirements, Rev 0, August 21, 2013

<sup>11.</sup> per the IEEE-ISTO 5001-2003 "Nexus" standard

Table 25. Extended MDO definition to the Nexus Standard Connector using IO for additional MDO Signals (continued)

| Nexus pin designation | MPC5500 MICTOR definition | MPC5500 robust definition |

|-----------------------|---------------------------|---------------------------|

| TOOL_IO2              | _                         | MDO8/GPIO70               |

| TOOL_IO3              | RSTOUT                    | MDO10/GPIO81              |

- 1. This pin has been redefined since the original definition in 2004. Customers may want to make this signal selectable (via a 0 Ω resistor option) between RSTOUT and BOOTCFG1/IRQ3/GPIO212.

- 2. This signal is not available on the 51-pin robust connector

- 3. This pin is defined for use by tool vendors and has no defined connection to the MPC5500 device for the MICTOR connector option.

## 7.1 MICTOR Connector Definition for the MPC5500 Family

The following table shows the complete signal usage for the MPC5500 full-port mode MICTOR connector. This uses the Vendor\_IO pins 1–4 as MDO[11:8]. This connector may also be used for reduced-port mode (which only uses MDO[3:0]). While only one MICTOR connector is recommended, some tools may not support this configuration. For maximum tool compatibility, a second MICTOR connector may need to be added for the upper four MDO signals (MDO[11:8]).

Table 26. MPC5500 Family MICTOR Connector M38C

| MPC5500 signal            | Combined M38C<br>or M38-2C |     |    |        |    |     | Combined M38C<br>or M38-2C | MPC5500 signal |

|---------------------------|----------------------------|-----|----|--------|----|-----|----------------------------|----------------|

| -                         | Reserved                   | -   | 1  | Þ      | 2  | -   | Reserved <sup>1</sup>      | -              |

| -                         | Reserved <sup>1</sup>      | -   | 3  | Ground | 4  | -   | Reserved <sup>1</sup>      | -              |

| MDO9/GPIO80               | VEN_IO0                    | Out | 5  | G      | 6  | Out | CLOCKOUT                   | CLKOUT         |

| BOOTCFG1/IRQ3/<br>GPIO212 | VEN_IO2                    | In  | 7  |        | 8  | Out | VEN_IO3                    | MDO8/GPIO70    |

| RESET                     | /RESET                     | In  | 9  |        | 10 | In  | /EVTI                      | EVTI           |

| TDO                       | TDO                        | Out | 11 |        | 12 |     | VTREF                      | VDDE7          |

| MDO10/GPIO81              | VEN_IO4                    | Out | 13 |        | 14 | Out | /RDY                       | RDY            |

| TCK                       | TCK                        | In  | 15 |        | 16 | Out | MDO7                       | MDO7/GPIO78    |

| TMS                       | TMS                        | In  | 17 | þ      | 18 | Out | MDO6                       | MDO6/GPIO77    |

| TDI                       | TDI                        |     | 19 | Ground | 20 | Out | MDO5                       | MDO5/GPIO76    |

| JCOMP                     | /TRST                      | In  | 21 | g      | 22 | Out | MDO4                       | MDO4/GPIO75    |

| MDO11/GPIO82              | VEN_IO1                    | Out | 23 | Þ      | 24 | Out | MDO3                       | MDO3           |

| RSTOUT                    | TOOL_IO3                   | Out | 25 | Ground | 26 | Out | MDO2                       | MDO2           |

| -                         | TOOL_IO2                   |     | 27 | ပ      | 28 | Out | MDO1                       | MDO1           |

| _2<br>                    | TOOL_IO1                   |     | 29 |        | 30 | Out | MDO0                       | MDO0           |

| 12 volts                  | UBATT                      |     | 31 |        | 32 | Out | /EVTO                      | EVTO           |

| 12 volts                  | UBATT                      |     | 33 |        | 34 | Out | MCKO                       | MCKO           |

| _2                        | TOOL_IO0                   |     | 35 |        | 36 | Out | /MSEO1                     | MSEO1          |

| VSTBY                     | VALTREF                    |     | 37 |        | 38 | Out | /MSEO0                     | MSEO0          |

- 1. Pins 1 through 4 should be considered "reserved" and may be used by some logic analyzers as ground connections. If care is taken (and the proper cables are used), these pins could be used for customer I/O signals. However, check with the tool vendors used. These pins are defined on devices that require 16 MDO signals.

- This optional Nexus signal is defined for use by tool vendors and has no defined connection to the MPC5500 family device.

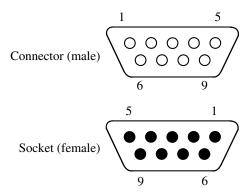

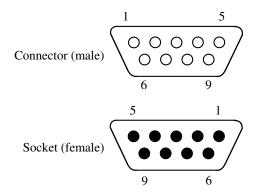

## 7.2 MPC5500 JTAG connector

The figure below shows the pin-out of the recommended JTAG connector to support the MPC5500 devices. If there is enough room allowed in the target system, a full Nexus connector is preferred over the simple 14-pin JTAG connector since it allows a higher degree of debug capability. It can be used as a minimum debug access or for BSDL board testing.

The recommended connector for the target system is the Tyco part number 2514-6002UB and the pin-out is shown in the following table.

### NOTE

This pin-out is similar to the Freescale MCORE and DSP JTAG/OnCE connector definitions.

| Description       | Pin | Pin | Description |

|-------------------|-----|-----|-------------|

| TDI               | 1   | 2   | GND         |

| TDO               | 3   | 4   | GND         |

| TCK               | 5   | 6   | GND         |

| EVTI <sup>1</sup> | 7   | 8   | _           |

| RESET             | 9   | 10  | TMS         |

| VREF              | 11  | 12  | GND         |

| RDY <sup>2</sup>  | 13  | 14  | JCOMP       |

Table 27. Recommended JTAG connector pinout

- 1. EVTI is optional and was not included in the original (very early) definitions of the JTAG-only connector.

- 2. The RDY signal is not available on all packages or on all devices. Check the device pinout specification. In general it is not available in packages with 208 signals or less.

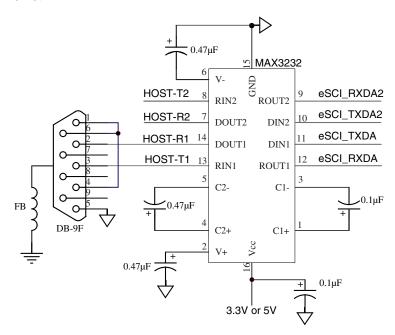

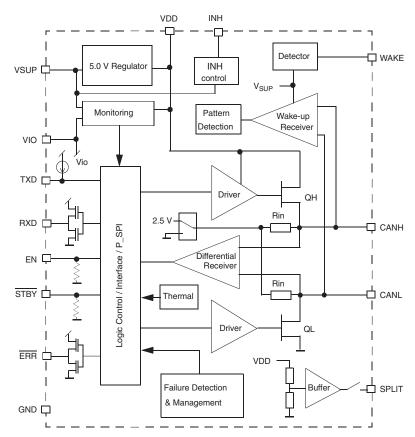

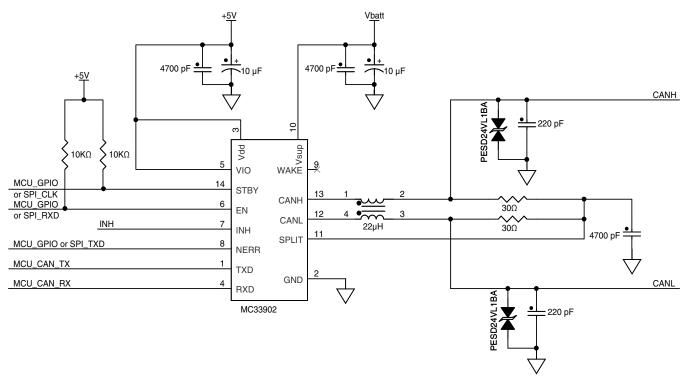

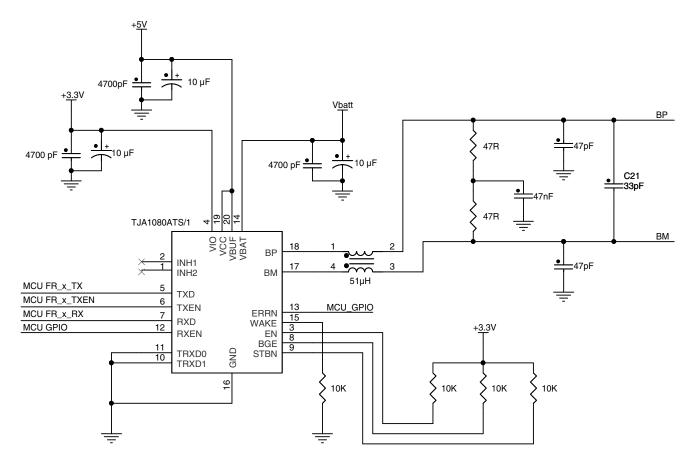

#### NOTE