## **Application Note**

Document Number: AN3155 Rev. 1.1, 01/2010

# **Battery Management for the MC13783**

by: Power Management and Audio Application Team

## 1 Introduction

The purpose of this application note is show the battery management and charging of the MC13783.

# 2 Charging Path

The MC13783 supports up to three types of charge path: dual, single and separate path and two kinds of input configuration: common and separate input. The configuration choice is performed by connecting or not connecting the CHRGMOD pins of the MC13783 as described in the Table 1, on page 3 to ground or to VATLAS; and by the presence of external transistors used for current regulation and trickle charging.

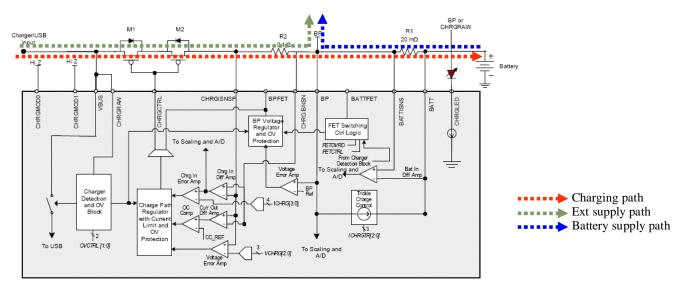

## 2.1 Single Path Configuration

In this configuration, which is the simplest one (i.e., the most cost effective solution), the entire chipset is always supplied from the battery. The battery always has to be present and charged to be able to run the application. In this configuration, the charge current is also used to supply the phone, so the battery charge algorithm has to

### **Contents**

| 1 | Introduction                                   | 1  |

|---|------------------------------------------------|----|

| 2 | Charging Path                                  | 1  |

| 3 | Charger Detection                              | 4  |

| 1 | Charger Control Logic                          | 4  |

| 5 | Charger SPI Tables                             | 9  |

| 3 | <b>Example of Charging Flow Diagram to the</b> |    |

|   | Baseband                                       | 10 |

© Freescale Semiconductor, Inc., 2006-2010. All rights reserved.

### **Charging Path**

measure the real battery charge current. The standalone trickle charge is activated for a depleted battery (wall charger and USB). Figure 1 shows the single path configuration.

Figure 1. Single Path Configuration

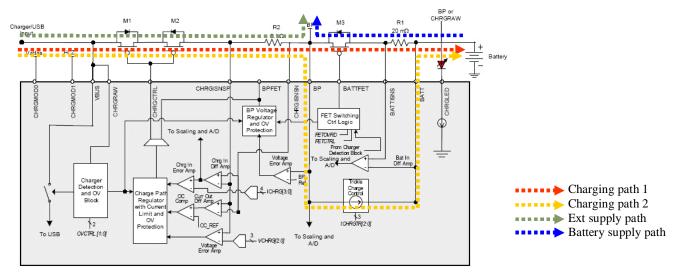

## 2.2 Serial Path Configuration

In this configuration a power switch, M3, is added to allow the chipset to be supplied by the charger even if the battery is completely discharged (dead battery operation). The charge current is still shared between the battery and the application (complex battery charging algorithm). The standalone trickle charge is activated for USB charging only. Figure 2 shows the serial path configuration.

Figure 2. Serial Path Configuration

Battery Management for the MC13783 Application Note, Rev. 1.1

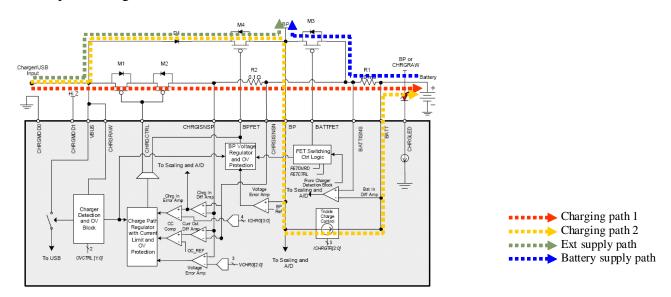

## 2.3 **Dual Path Configuration**

In this configuration, a second power MOS (M4) is added and acts as an independent power voltage regulator to supply the application. The charging current is fully used to charge the battery pack to simplify the charging algorithm. The standalone trickle charge is activated for USB charging only. Figure 3 shows the dual path configuration.

Figure 3. Dual Path Configuration

Table 1 shows the configuration choice that is performed by connecting or not connecting the CHRGMOD pins of the MC13783 to ground or to VATLAS; and by the presence of external transistors used for current regulation and trickle charging.

| CHRGMOD1 | CHRGMOD0 | Charge Mode                    | Pros                                                | Cons                                                                                                           |

|----------|----------|--------------------------------|-----------------------------------------------------|----------------------------------------------------------------------------------------------------------------|

| Hi Z     | GND      | Common input-<br>Dual Path     | Simpler charge algorithm     Dead battery supported | Most expansive solution: 4 MOS<br>FET                                                                          |

| Hi Z     | Hi Z     | Common input-<br>Single Path   | Simplest one     Cost effective                     | Dead battery not supported     Battery charge algorithm has to monitor the real battery charge current         |

| Hi Z     | VATLAS   | Common input-<br>Serial Path   | Dead battery supported                              | Additional power switch M3     Complex charge algorithm                                                        |

| VATLAS   | GND      | Separate input-<br>Dual Path   |                                                     | Does not support USB charging<br>except with an external circuitry<br>controlled by a GPIO of the<br>processor |

| VATLAS   | Hi Z     | Separate input-<br>Single Path |                                                     |                                                                                                                |

| VATLAS   | VATLAS   | Separate input-<br>Serial Path |                                                     |                                                                                                                |

**Table 1. Charge Mode Settings**

Battery Management for the MC13783 Application Note, Rev. 1.1

**Table 1. Charge Mode Settings (continued)**

| CHRGMOD1 | CHRGMOD0 | Charge Mode | Pros | Cons |  |  |  |

|----------|----------|-------------|------|------|--|--|--|

| GND      | GND      |             | Б    |      |  |  |  |

| GND      | Hi Z     | Reserved    |      |      |  |  |  |

| GND      | VATLAS   |             |      |      |  |  |  |

# 3 Charger Detection

The application of a charger or USB host will cause the CHGDETI and USBI interrupts to go high. In addition, if a charger is attached, the SE1I will also go high. These interrupts can be used to detect the application of a charger in the system by looking at the CHRGDETS, USB4V4S, and SE1S bits.

In addition, when the charge path regulator is enabled, the charge current is sensed across the R2 resistor to generate the CHGCURRI and CHGCURRS bits.

### NOTE

If the charge current falls below the CHGCURR threshold, the CHGCURRS bit goes low.

The CHGCURRS bit is set to 1 whenever the charge path regulator is disabled. If the charger is removed while the charge path regulator is enabled, the software removal detection of the charger can be determined by a combination of the CHRGCURRS, CHGDETS, and USB4V4S bits.

When in separate input charging configuration, the hardware detection of removal of a charger is based on CHRGDETSEP and CHGCURR thresholds. When in common input charging configuration, the hardware detection of removal of a charger is based on CHRGDET and CHGCURR thresholds.

### NOTE

The hardware detection of the charger removal with clear ICHRG[3:0] bits causes the charger path regulator to shut off.

# 4 Charger Control Logic

It should be noted that in the MC13783, the charger is controlled through combinatory logic. Table 2, on page 5 through Table 7, on page 8 define the behavior of the MC13783 autonomous charger. When SPI bits are noted, this means it should be programmed by the processor.

**Table 2. Dual Path Logic Table**

| CHRGRAW | ID      | RESETB | DP | DM | FET<br>OVRD | FET<br>CTRL | BATT                                                                                   | BP<br>Regulator | BATTFET | Charge<br>Path<br>Regulator | Trickle<br>Charger | Charger<br>Turn<br>On |

|---------|---------|--------|----|----|-------------|-------------|----------------------------------------------------------------------------------------|-----------------|---------|-----------------------------|--------------------|-----------------------|

| Н       | <3      | L      | L  | L  | Х           | Х           | <batton< td=""><td>OFF</td><td>Н</td><td>TRICKLEL</td><td>OFF</td><td>L</td></batton<> | OFF             | Н       | TRICKLEL                    | OFF                | L                     |

|         | V       |        | L  | Н  |             |             |                                                                                        |                 |         |                             |                    |                       |

|         |         |        | Н  | L  |             |             |                                                                                        |                 |         |                             |                    |                       |

|         |         |        | L  | L  | Х           | Х           | >BATTON                                                                                | OFF             | L       | TRICKLEL                    | OFF                | Н                     |

|         |         |        | L  | Н  |             |             |                                                                                        |                 |         |                             |                    |                       |

|         |         |        | Н  | L  |             |             |                                                                                        |                 |         |                             |                    |                       |

|         |         |        | Н  | Н  | Х           | Х           | Х                                                                                      | ON              | Н       | OFF                         | OFF                | Н                     |

|         |         | Н      | L  | L  | 0           | Х           | X X                                                                                    | OFF             | L       | ICHRG NA<br>[3:0]           | Н                  |                       |

|         |         |        | L  | Н  |             |             |                                                                                        |                 |         |                             |                    |                       |

|         |         |        | Н  | L  |             |             |                                                                                        |                 |         |                             |                    |                       |

|         |         |        | Н  | Н  | 0           | Х           | Х                                                                                      | ON              | Н       | ICHRG<br>[3:0]              | ICHRGTR<br>[2:0]   | Н                     |

|         |         |        | Х  | Х  | 1           | 0           | Х                                                                                      | ON              | Н       | ICHRG<br>[3:0]              | ICHRGTR<br>[2:0]   | Н                     |

|         |         |        | Х  | Х  | 1           | 1           | Х                                                                                      | OFF             | L       | ICHRG<br>[3:0]              | NA                 | Н                     |

|         | >3<br>V | Х      | Х  | Х  | Х           | Х           | Х                                                                                      | ON              | Н       | ICHRG<br>[3:0]              | ICHRGTR<br>[2:0]   | Н                     |

| L       | Х       | Х      | Х  | Х  | Х           | Х           | Х                                                                                      | OFF             | L       | OFF                         | OFF                | L                     |

**Table 3. Serial Path Logic Table**

| CHRGRAW | ID  | RESETB | DP  | DM | FETOVRD | FETCTRL | BATT                                                                       | BATTFET | Charge<br>Path<br>Regulator | Trickle<br>Charger | Charger<br>Turn On |

|---------|-----|--------|-----|----|---------|---------|----------------------------------------------------------------------------|---------|-----------------------------|--------------------|--------------------|

| Н       | <3V | L      | L   | L  | Х       | Х       | <batton< td=""><td>L</td><td>TRICKLEL</td><td>OFF</td><td>L</td></batton<> | L       | TRICKLEL                    | OFF                | L                  |

|         |     |        | L   | Н  |         |         |                                                                            |         |                             |                    |                    |

|         |     |        | Н   | L  |         |         |                                                                            |         |                             |                    |                    |

|         |     |        | L   | L  | Х       | Х       | >BATTON                                                                    | L       | TRICKLEL                    | OFF                | Н                  |

|         |     |        | L   | Н  |         |         |                                                                            |         |                             |                    |                    |

|         |     |        | Н   | L  |         |         |                                                                            |         |                             |                    |                    |

|         |     |        | Н   | Н  | Х       | Х       | Х                                                                          | Н       | Full Rate                   | OFF                | Н                  |

|         |     | Н      | L   | L  | 0       | Х       | Х                                                                          | L       | ICHRG[3:0]                  | NA                 | Н                  |

|         |     |        | L   | Н  |         |         |                                                                            |         |                             |                    |                    |

|         |     |        | H L |    |         |         |                                                                            |         |                             |                    |                    |

|         |     |        | Н   | Н  | 0       | Х       | Х                                                                          | * H     | Full Rate                   | OFF                | Н                  |

|         |     |        |     |    |         |         |                                                                            | * L     | ICHRG[3:0]                  | ICHRGTR<br>[2:0]   | Н                  |

|         |     |        | Х   | Х  | 1       | 0       | Х                                                                          | Н       | ICHRG[3:0]                  | ICHRGTR<br>[2:0]   | Н                  |

|         |     |        | Х   | Х  | 1       | 1       | Х                                                                          | L       | ICHRG[3:0]                  | NA                 | Н                  |

|         | >3V | Х      | Х   | Х  | Х       | Х       | Х                                                                          | Н       | Full Rate                   | ICHRGTR<br>[2:0]   | Н                  |

| L       | Х   | Х      | Х   | Х  | Х       | Х       | Х                                                                          | L       | OFF                         | OFF                | L                  |

<sup>(\*) &#</sup>x27;H / Full Rate / OFF / H' if already Full Rate before entering this mode, 'L / ICHRG[3:0] / ICHRGTR[2:0] / H' in the other cases.

**Table 4. Single Path Logic Table**

| CHRGRAW      | ID     | RESETB   | DP   | DM   | FET OVRD        | FET CTRL   | BATT                                                                   | Charge Path Regulator     | Charger<br>Turn On |

|--------------|--------|----------|------|------|-----------------|------------|------------------------------------------------------------------------|---------------------------|--------------------|

| Н            | <3V    | L        | L    | L    | Х               | Х          | <batton< td=""><td>TRICKLEL</td><td>L</td></batton<>                   | TRICKLEL                  | L                  |

|              |        |          | L    | Н    |                 |            |                                                                        |                           |                    |

|              |        |          | Н    | L    |                 |            |                                                                        |                           |                    |

|              |        |          | L    | L    | Х               | Х          | >BATTON                                                                | TRICKLEL                  | Н                  |

|              |        |          | L    | Н    |                 |            |                                                                        |                           |                    |

|              |        |          | Н    | L    |                 |            |                                                                        |                           |                    |

|              |        |          | Н    | Н    | Х               | Х          | <batton< td=""><td>**TRICKLEL / TRICKLEM</td><td>L</td></batton<>      | **TRICKLEL / TRICKLEM     | L                  |

|              |        |          | Н    | Н    | Х               | Х          | >BATTON                                                                | TRICKLEM                  | Н                  |

|              |        | Н        | L    | L    | 0               | Х          | Х                                                                      | ICHRG[3:0]                | Н                  |

|              |        |          | L    | Н    |                 |            |                                                                        |                           |                    |

|              |        |          | Н    | L    |                 |            |                                                                        |                           |                    |

|              |        |          | Н    | Н    | 0               | Х          | Х                                                                      | ICHRG[3:0]                | Н                  |

|              |        |          | Х    | Х    | 1               | 0          | Х                                                                      | ICHRG[3:0]                | Н                  |

|              |        |          | Х    | Х    | 1               | 1          | Х                                                                      | ICHRG[3:0]                | Н                  |

|              | >3V    | Х        | Х    | Х    | Х               | Х          | <batton< td=""><td>** TRICKLEL /<br/>TRICKLEM</td><td>L</td></batton<> | ** TRICKLEL /<br>TRICKLEM | L                  |

|              |        | Х        | Х    | Х    | Х               | Х          | >BATTON                                                                | ** TRICKLEM /<br>TRICKLEH | Н                  |

| L            | Χ      | Х        | Х    | Х    | Х               | Х          | Х                                                                      | OFF                       | L                  |

| (**) TRICKLE | L, TRI | CKLEM or | TRIC | KLEI | H level is used | based on B | ATT voltage.                                                           |                           |                    |

**Table 5. Separate Input Dual Path Logic Table**

| CHRGRAW | RESETB | FET OVRD | FET CTRL | BP<br>Regulator | BATTFET | Charge Path<br>Regulator | Trickle<br>Charger | Charger<br>Turn On |

|---------|--------|----------|----------|-----------------|---------|--------------------------|--------------------|--------------------|

| Н       | L      | Х        | Х        | ON              | Н       | OFF                      | OFF                | Н                  |

| Н       | Н      | 0        | Х        | ON              | Н       | ICHRG[3:0]               | ICHRGTR[2:0]       | Н                  |

| Н       | Н      | 1        | 0        | ON              | Н       | ICHRG[3:0]               | ICHRGTR[2:0]       | Н                  |

| Н       | Н      | 1        | 1        | OFF             | L       | ICHRG[3:0]               | NA                 | Н                  |

| L       | Х      | Х        | Х        | OFF             | L       | OFF                      | OFF                | L                  |

Table 6. Separate Input Serial Path Logic Table

| CHRGRAW | RESETB | FET OVRD | FET CTRL | BATTFET | Charge Path<br>Regulator | Trickle<br>Charger | Charger<br>Turn On |

|---------|--------|----------|----------|---------|--------------------------|--------------------|--------------------|

| Н       | L      | Х        | Х        | Н       | Full Rate                | OFF                | Н                  |

| Н       | Н      | 0        | Х        | * H     | Full Rate                | OFF                | Н                  |

|         |        |          |          | * L     | ICHRG[3:0]               | ICHRGTR[2:0]       | Н                  |

| Н       | Н      | 1        | 0        | Н       | ICHRG[3:0]               | ICHRGTR[2:0]       | Н                  |

| Н       | Н      | 1        | 1        | L       | ICHRG[3:0]               | NA                 | Н                  |

| L       | Х      | Х        | Х        | L       | OFF                      | OFF                | L                  |

<sup>(\*) &#</sup>x27;H / Full Rate / OFF / H' if already Full Rate before entering this mode, 'L / ICHRG[3:0] / ICHRGTR[2:0] / H' in the other cases.

**Table 7. Separate Input Single Path Logic Table**

| CHRGRAW      | RESETB     | FETOVRD      | FETCTRL    | BATT                                                                  | Charge Path<br>Regulator | Charger<br>Turn On |

|--------------|------------|--------------|------------|-----------------------------------------------------------------------|--------------------------|--------------------|

| Н            | L          | Х            | Х          | <batton< td=""><td>**TRICKLEL /<br/>TRICKLEM</td><td>L</td></batton<> | **TRICKLEL /<br>TRICKLEM | L                  |

| Н            | L          | Х            | Х          | >BATTON                                                               | TRICKLEM                 | Н                  |

| Н            | Н          | 0            | Х          | Х                                                                     | ICHRG[3:0]               | Н                  |

| Н            | Н          | 1            | 0          | Х                                                                     | ICHRG[3:0]               | Н                  |

| Н            | Н          | 1            | 1          | Х                                                                     | ICHRG[3:0]               | Н                  |

| L            | Х          | Х            | Х          | Х                                                                     | OFF                      | L                  |

| (**) TRICKLE | L or TRICK | LEM level is | used based | on BATT volt                                                          | age                      |                    |

# 5 Charger SPI Tables

Charger SPI tables are shown Table 8 and Table 9.

**Table 8. Charger Programming Table**

| Bit # | Bit Name    | Reset Signal | Reset<br>State | Туре | Description                                                                                                                           |

|-------|-------------|--------------|----------------|------|---------------------------------------------------------------------------------------------------------------------------------------|

| 0     | VCHRG0      | RESETB       | 0              | R/W  | Sets the output voltage of charge regulator.                                                                                          |

| 1     | VCHRG1      | RESETB       | 0              | R/W  |                                                                                                                                       |

| 2     | VCHRG2      | RESETB       | 0              | R/W  |                                                                                                                                       |

| 3     | ICHRG0      | RESETB       | 0              | R/W  | Sets the current of the main charger DAC.                                                                                             |

| 4     | ICHRG1      | RESETB       | 0              | R/W  |                                                                                                                                       |

| 5     | ICHRG2      | RESETB       | 0              | R/W  |                                                                                                                                       |

| 6     | ICHRG3      | RESETB       | 0              | R/W  |                                                                                                                                       |

| 7     | ICHRGTR0    | RESETB       | 0              | R/W  | Sets the current of the trickle charger.                                                                                              |

| 8     | ICHRGTR1    | RESETB       | 0              | R/W  |                                                                                                                                       |

| 9     | ICHRGTR2    | RESETB       | 0              | R/W  |                                                                                                                                       |

| 10    | FETOVRD     | RESETB       | 0              | R/W  | 0 = BATTFET and BPFET outputs are controlled by hardware. 1 = BATTFET and BPFET are controlled by the state of the FETCTRL bit.       |

| 11    | FETCTRL     | RESETB       | 0              | R/W  | 0 = BPFET is driven low, BATTFET is driven high if FETOVRD is set. 1 = BPFET is driven high, BATTFET is driven low if FETOVRD is set. |

| 12    | Reserved    | RESETB       | 0              | R/W  | For future use.                                                                                                                       |

| 13    | RVRSMODE    | RESETB       | 0              | R/W  | 0 = Reverse mode disabled.<br>1 = Reverse mode enabled.                                                                               |

| 14    | Reserved    | RESETB       | 0              | R/W  | For future use.                                                                                                                       |

| 15    | OVCTRL0     | RESETB       | 0              | R/W  | Overvoltage threshold select bit.                                                                                                     |

| 16    | OVCTRL1     | RESETB       | 0              | R/W  |                                                                                                                                       |

| 17    | UCHEN       | RESETB       | 0              | R/W  | Unregulated charge enable bit.                                                                                                        |

| 18    | CHRGLEDEN   | RESETB       | 0              | R/W  | 0 = CHRGLED disabled.<br>1 = CHRGLED enabled.                                                                                         |

| 19    | CHRGRAWPDEN | RESETB       | 0              | R/W  | Enables a 5K pull down at CHRGRAW. To be used in the dual path charging configuration.                                                |

| 20    | Reserved    | RESETB       | 0              | R/W  | For future use.                                                                                                                       |

| 21    | Reserved    | RESETB       | 0              | R/W  | For future use.                                                                                                                       |

| 22    | Unused      |              | 0              | R    | Not available.                                                                                                                        |

| 23    | Unused      |              | 0              | R    | Not available.                                                                                                                        |

**Table 9. Charger Related Interrupts**

| Interrupt bit | Mask bit             | Sense bit | Description                                                                                                                                                                                                                                                                 |  |  |  |

|---------------|----------------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| CHGDETI       | CHGDETM              | CHGDETS   | Charger detection interrupt, dual edge, debounce 32 msec                                                                                                                                                                                                                    |  |  |  |

| CHGOVI        | CHGOVM               | CHGOVS    | Charger overvoltage detection interrupt, dual edge, 7.8 msec rising edge debounce                                                                                                                                                                                           |  |  |  |

| CHGREVI       | REVI CHGREVM CHGREVS |           | Charger path reverse current interrupt, rising edge, 2.9 msec debounc                                                                                                                                                                                                       |  |  |  |

| CHGSHORTI     | CHGSHORTM            | CHGSHORTS | Charger path short circuit in reverse supply mode interrupt, rising edge, 150 $\mu s$ or 2.9 msec debounce depending on threshold                                                                                                                                           |  |  |  |

| CCCVI         | CCCVM                | CCCVS     | CCCV interrupt logic high indicates that the charger has switched its mode from CC to CV or from CV to CC. CCVS = 0 for constant current charging, CCCVS = 1 for constant voltage charging. Write a "1" to this location to clear the interrupt. Dual Edge, 2 sec debounce. |  |  |  |

| CHGCURRI      | CHGCURRM             | CHGCURRS  | CHGCURR interrupt logic high indicates that the charge current has dropped below its threshold. Falling edge, debounce 16 msec.                                                                                                                                             |  |  |  |

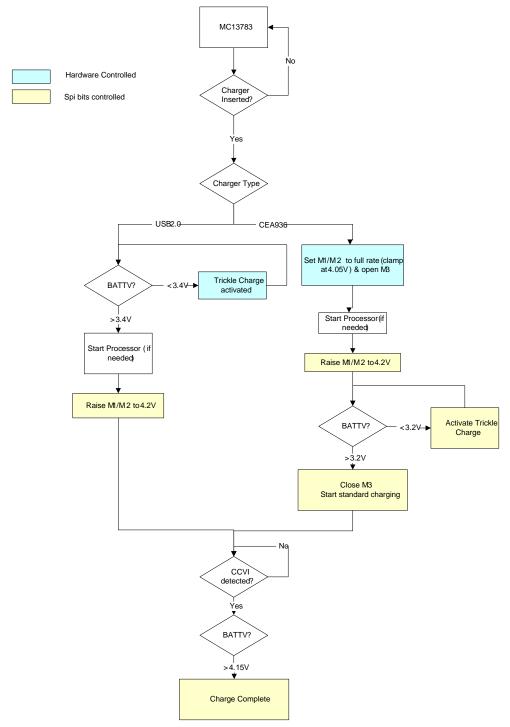

# 6 Example of Charging Flow Diagram to the Baseband

Figure 4 is an example of the MC13783 charging flow to the baseband.

Figure 4. Example of the MC13783 Charging Flow to the Baseband

## 6.1 Example of CEA936 Charging

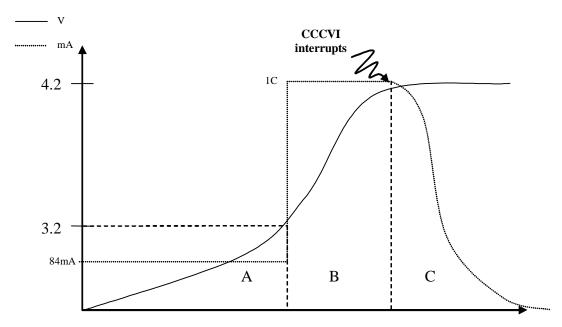

If the MC13783 detects the CEA936, then the battery FET (M3) is opened, the charge register VCHRG[3:0] is set to the desired value and the processor powers. Upon powering, the processor determines the state of the battery. If less than 3.4 V, it activates the internal trickle charger (processor must program this rate). If greater than 3.4 V, the processor closes the M3 and sets for a higher charge rate between 0.5 and 1C and it also reprograms VCHRG[3:0] to 4.2 V. With high rate charging, current rate will vary in order to maintain the power dissipation rate of M1 somewhere below the maximum dissipation rate of the M1 FET over the acceptable ambient temperature range for charging (typically 1W). It depends on the type of M1 FET chosen, the layout and the ambient temperature range whereby charging is allowed. Figure 5 shows the CEA936 charging curve.

Figure 5. CEA936 Charging Curve

• Step A (small charge): If the battery is dead, the processor programs trickle charge circuitry to a small current (e.g., 84 mA through ICHRGTR[2:0] register).

### NOTE

The processor must poll battery voltage to go to step B.

- Step B (fast charge): The charge is set to 1C (e.g., 900 mA in the case of a 900 mA charger) through ICHRG[3:0].

- Step C: The processor doesn't reprogram ICHRG[3:0] to reduce current, it is automatically done in the hardware by the MC13783 because current regulation is automatic when battery voltage approaches 4.2 V. During this step, if the processor checks a voltage less than 4.15 V, it should wait for another CCCVI interrupt. As a safety reason, the processor should also ensure that the battery voltage doesn't exceed 4.2 V.

## 6.2 Example of USB 2.0 Charging - 100 and 500 mA Profile

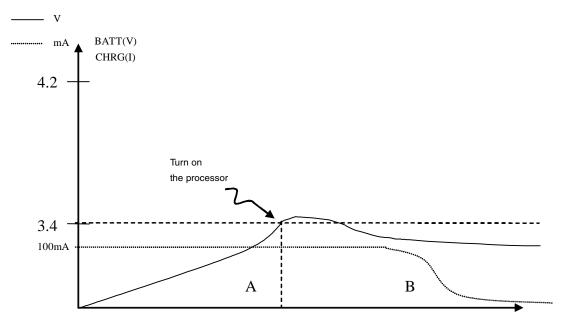

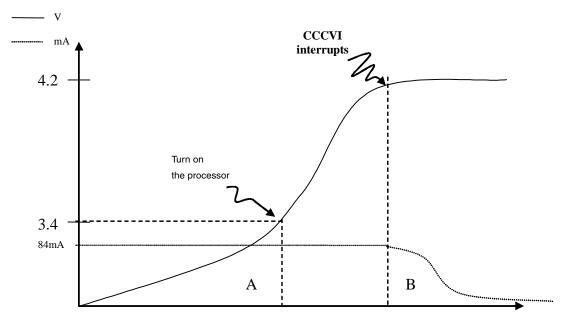

If USB 2.0 is detected, the charge rate is set to 70 mA and the 90 minute timer starts. With USB 2.0, charging will always be 100 mA maximum and the processor will turn on when BATT = 3.4 V and not 3.2 V to avoid oscillation around 3.2 V because when the processor starts, it will consume more power than the USB can provide. When the processor starts, it can take over charging and change the termination method, but the charger will only deliver 100 mA maximum. If the processor does not take control, charging will stop either when the 90 minute timer expires or BATT = 4.05. Figure 6 shows the USB 2.0 charging curve with the 100 mA profile and Figure 7 shows the USB 2.0 charging curve with 500 mA profile.

Figure 6. USB 2.0 Charging Curve with the 100 mA Profile

- Step A: The maximum charger available current passes through M1/M2 (100 mA).

- Step B: The processor doesn't reprogram ICHRG[3:0] to reduce current. It is automatically done in the hardware by the MC13783 because current regulation is automatic when battery voltage approaches 4.2 V.

### **Example of Charging Flow Diagram to the Baseband**

Figure 7. USB 2.0 Charging Curve with 500 mA Profile

## NOTES

Battery Management for the MC13783 Application Note, Rev. 1.1

### How to Reach Us:

### Home Page:

www.freescale.com

#### Web Support:

http://www.freescale.com/support

#### **USA/Europe or Locations Not Listed:**

Freescale Semiconductor, Inc. Technical Information Center, EL516 2100 East Elliot Road Tempe, Arizona 85284 1-800-521-6274 or +1-480-768-2130 www.freescale.com/support

### Europe, Middle East, and Africa:

Freescale Halbleiter Deutschland GmbH Technical Information Center Schatzbogen 7 81829 Muenchen, Germany +44 1296 380 456 (English) +46 8 52200080 (English) +49 89 92103 559 (German) +33 1 69 35 48 48 (French) www.freescale.com/support

### Japan:

Freescale Semiconductor Japan Ltd. Headquarters ARCO Tower 15F 1-8-1, Shimo-Meguro, Meguro-ku, Tokyo 153-0064 Japan 0120 191014 or +81 3 5437 9125 support.japan@freescale.com

### Asia/Pacific:

Freescale Semiconductor China Ltd. Exchange Building 23F No. 118 Jianguo Road Chaoyang District Beijing 100022 China +86 10 5879 8000 support.asia@freescale.com

### For Literature Requests Only:

Freescale Semiconductor Literature Distribution Center 1-800-441-2447 or +1-303-675-2140 Fax: +1-303-675-2150 LDCForFreescaleSemiconductor@hibbertgroup.co

Information in this document is provided solely to enable system and software implementers to use Freescale Semiconductor products. There are no express or implied copyright licenses granted hereunder to design or fabricate any integrated circuits or integrated circuits based on the information in this document.

Freescale Semiconductor reserves the right to make changes without further notice to any products herein. Freescale Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does Freescale Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation consequential or incidental damages. "Typical" parameters that may be provided in Freescale Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals", must be validated for each customer application by customer's technical experts. Freescale Semiconductor does not convey any license under its patent rights nor the rights of others. Freescale Semiconductor products are not designed, intended, or authorized for use as components in systems intended for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the Freescale Semiconductor product could create a situation where personal injury or death may occur. Should Buyer purchase or use Freescale Semiconductor products for any such unintended or unauthorized application, Buyer shall indemnify and hold Freescale Semiconductor and its officers, employees, subsidiaries, affiliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use, even if such claim alleges that Freescale Semiconductor was negligent regarding the design or manufacture of the part.

Freescale™ and the Freescale logo are trademarks of Freescale Semiconductor, Inc. All other product or service names are the property of their respective owners.

© Freescale Semiconductor, Inc. 2006-2010. All rights reserved.