## Freescale Semiconductor Application Note

AN3867 Rev. 3.0, 4/2013

# **MC13892** Functional Pin Description

## 1 Overview

This document is intended to show how to design a schematic using the MC13892, by describing the functionality of each one of its pins, as well as how to connect them for a specific application.

#### Contents

- 1 Overview

- 2 Scope

- **3** Typical Application Diagram

- **4** Typical Connections

- **5** References

© Freescale Semiconductor, Inc., 2009 - 2013. All rights reserved.

Scope

## 2 Scope

The typical connection of each pin is presented in the following table. It is common that some of the pins have different functionalities, so more than one typical connections are presented, and the applications explained. This table also shows how to connect the pins when they are not used.

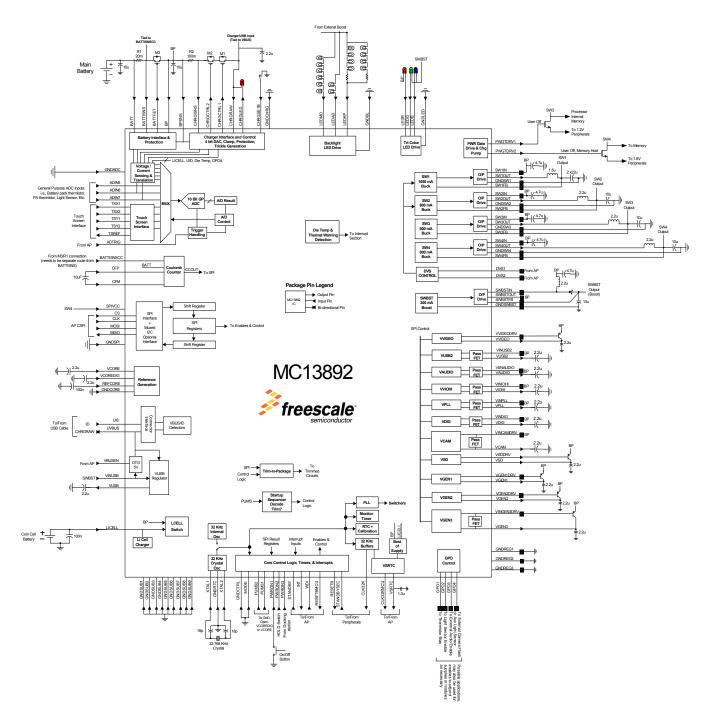

## **3** Typical Application Diagram

**Typical Connections**

| Pin       | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Typical Connection                                                                                                                                       | Connection if Unused                                                                                                                                     |  |  |  |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Charger   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                                          |                                                                                                                                                          |  |  |  |

| CHRGRAW   | IRGRAW1. Charger input. The charger voltage<br>is measured through an ADC at this<br>pin. The minimum voltage for this pin<br>depends on BATTMIN threshold<br>value.Connect the wall charger/USB<br>charger here. This pin must be<br>shorted to the UVBUS pin in cas<br>where the charger is being supplied<br>accessories. The battery voltage can<br>be applied to an accessory by<br>enabling the charge path for the<br>accessory via the CHRGRAW pin.Connect the wall charger/USB<br>charger here. This pin must be<br>shorted to the UVBUS pin in cas<br>where the charger is being supplied<br>from the USB cable. |                                                                                                                                                          | Unconnected                                                                                                                                              |  |  |  |

| CHRGCTRL1 | Driver output for charger path FET M1.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Base of MOSFET M1.                                                                                                                                       | Unconnected                                                                                                                                              |  |  |  |

| CHRGCTRL2 | Driver output for charger path FET M2.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Base of MOSFET M2.                                                                                                                                       | Unconnected                                                                                                                                              |  |  |  |

| CHRGISNS  | Charge current sensing point 1. The<br>charge current is read by monitoring<br>the voltage drop over the charge<br>current 100 mOhm sense resistor<br>connected between the CHRGISNS<br>and BPSNS pins.                                                                                                                                                                                                                                                                                                                                                                                                                    | Connect this pin directly to one of the terminals of the 100 mOhm sense resistor.                                                                        | Connect to BP pin                                                                                                                                        |  |  |  |

| BPSNS     | <ol> <li>BP sense point. The BP voltage is<br/>sensed at this pin and compared with<br/>the voltage at CHRGRAW.</li> <li>Charge current sensing point 2.<br/>The charge current is read by<br/>monitoring the voltage drop over the<br/>charge current 100 mOhm sense<br/>resistor. This resistor is connected<br/>between this pin and CHRGISNS.</li> </ol>                                                                                                                                                                                                                                                               | Connect this pin directly to the other<br>terminal of the 100 mOhm sense<br>resistor.                                                                    | Connect to BATT pin                                                                                                                                      |  |  |  |

| BP        | This pin is the application supply<br>point, which is the input supply to the<br>IC core circuitry. The application<br>supply voltage is sensed through an<br>ADC at this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                             | This pin will provide the charging<br>voltage of the battery and the supply<br>voltage of all the switchers and LDOs.<br>Connect it to their input pins. | Connect to BATT pin                                                                                                                                      |  |  |  |

| BATTFET   | Driver output for battery path FET M3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Connected to the base of M3 FET.                                                                                                                         | If no charging system is<br>required, the pin<br>BATTFET must be<br>floating. When a single<br>path is implemented, it<br>must be connected to<br>Ground |  |  |  |

| Pin         | Description                                                                                                                                                                                                                                                                                                                                                                                           | Typical Connection                                                                                  | Connection if Unused                                                                                     |  |  |  |

|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|--|--|--|

| Charger     |                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                     |                                                                                                          |  |  |  |

| BATTISNS    | Battery current sensing point 1. The<br>current flowing out of and into the<br>battery can be read via the ADC by<br>monitoring the voltage drop over the<br>sense resistor between BATT and<br>BATTISNS.                                                                                                                                                                                             | Connect this pin directly to one of the terminals of the 20 mOhm sense resistor.                    | Connect to BATT pin.                                                                                     |  |  |  |

| BATT        | <ol> <li>Battery positive terminal. The<br/>supply voltage of the battery is sensed<br/>through an ADC on this pin.</li> <li>Battery current sensing point 2. The<br/>current flowing out of and into the<br/>battery can be read via the ADC by<br/>monitoring the voltage drop over the<br/>sense resistor between BATT and<br/>BATTISNS.</li> </ol>                                                |                                                                                                     | It is mandatory to<br>connect the positive<br>terminal of the battery or<br>power supply on this<br>pin. |  |  |  |

| BATTISNSCC  | Coulomb Counter current sense point.                                                                                                                                                                                                                                                                                                                                                                  | It should be connected directly to the 0.020 Ohm sense resistor via a separate route from BATTISNS. | Connect to BATT pin                                                                                      |  |  |  |

| CFP and CFM | Accumulated current filter cap plus and minus terminals respectively.                                                                                                                                                                                                                                                                                                                                 |                                                                                                     |                                                                                                          |  |  |  |

| CHRGSE1B    | This pin is to indicate to the device if<br>the charger is being supplied through<br>a wall charger or USB.<br>An unregulated wall charger<br>configuration can be built, in<br>case this pin must be pulled<br>When charging through a US<br>be left open, since it is interna<br>up to VCORE. The recomm<br>is to place an external FET<br>pull it low or leave it open, d<br>on the charge method. |                                                                                                     | Unconnected                                                                                              |  |  |  |

| CHRGLED     | Trickle LED driver output 1. Since<br>normal LED control via the SPI bus is<br>not always possible in the standalone<br>operation, a current sink is provided at<br>the CHRGLED pin. This LED is to be<br>connected between this pin and<br>CHRGRAW.                                                                                                                                                  | is is charger LED.<br>one<br>ed at                                                                  |                                                                                                          |  |  |  |

| GNDCHRG     | Ground for charger interface.                                                                                                                                                                                                                                                                                                                                                                         | Ground                                                                                              | Ground                                                                                                   |  |  |  |

| Pin                       | Description                                                                                                                                                                                                                                                              | Typical Connection                                                                                                                                                                                                                       | Connection if Unused                             |  |

|---------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|--|

| LED Drivers               |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                          |                                                  |  |

| GNDBL                     | Ground for backlighting LED drivers                                                                                                                                                                                                                                      | Ground                                                                                                                                                                                                                                   | Ground                                           |  |

| LEDMD,<br>LEDAD,<br>LEDKP | LEDMD: Main display backlight LED<br>driver output.<br>LEDAD: Auxiliary display backlight<br>LED driver output.<br>LEDKP: Keypad lighting LED driver<br>output.<br>Independent programmable current<br>sink channels.                                                    | LED strings must be connected from<br>SWLEDOUT (anodes) to these pins<br>(cathodes). When parallel strings are<br>ganged together on a driver channel,<br>ballast resistance is recommended to<br>help balance the currents in each leg. | Unconnected                                      |  |

| LEDR, LEDG,<br>and LEDB   | General purpose LED driver output<br>Red, Green, and Blue respectively.<br>Each channel provides flexible LED<br>intensity control. These pins can also<br>be used as general purpose open<br>drain outputs for logic signaling, or as<br>generic PWM generator outputs. | d, Green, and Blue respectively.<br>ch channel provides flexible LED<br>ensity control. These pins can also<br>used as general purpose open<br>ain outputs for logic signaling, or as                                                    |                                                  |  |

| GNDLED                    | Ground for LED drivers.                                                                                                                                                                                                                                                  | round for LED drivers. Ground                                                                                                                                                                                                            |                                                  |  |

| IC Core                   |                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                          |                                                  |  |

| VCORE                     | Regulated supply output for the IC analog core circuitry.                                                                                                                                                                                                                | Place a 2.2 $\mu$ F capacitor from this pin<br>to GNDCORE. It will also have to be<br>connected to other pins as reference<br>or for configuration (i.e. PUMSx for<br>initialization configuration).                                     | It is mandatory to place a 2.2 $\mu F$ capacitor |  |

| VCOREDIG                  | Regulated supply output for the IC digital core circuitry. No external DC loading is allowed on VCOREDIG.                                                                                                                                                                | Place a 2.2 $\mu$ F capacitor from this pin to GNDCORE.                                                                                                                                                                                  | It is mandatory to place a 2.2 $\mu F$ capacitor |  |

| REFCORE                   | Main bandgap reference. All<br>regulators use the main bandgap as<br>the reference. The main bandgap is<br>bypassed with a capacitor at<br>REFCORE. No external DC loading is<br>allowed on REFCORE.                                                                     | Place a 0.1 μF capacitor from this pin to GNDCORE.                                                                                                                                                                                       | It is mandatory to place<br>a 0.1 μF capacitor   |  |

| GNDCORE                   | Ground for the IC core circuitry.                                                                                                                                                                                                                                        | Ground                                                                                                                                                                                                                                   | Ground                                           |  |

| Pin                                     | Description Typical Connection                                                                                                                                                                                                                       |                                                                                                                                                                                                                | Connection if Unused |  |  |

|-----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|

| Power Gating                            |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                |                      |  |  |

| PWRGTDRV1<br>and<br>PWRGTDRV2           | PWGTDRV1 is provided for power<br>gating peripheral loads sharing the<br>processor core supply domain(s)<br>SW1, and/or SW2, and/or SW3. In<br>addition, PWGTDRV2 is provided to<br>support power gate peripheral loads<br>on the SW4 supply domain. | The SW1, SW2, and SW3 power<br>gating FET drive would typically be<br>connected to PWGTDRV1 (for<br>parallel NMOS switches). The SW4<br>power gating FET drive would<br>typically be connected to<br>PWGTDRV2. | Unconnected          |  |  |

| Switchers                               |                                                                                                                                                                                                                                                      |                                                                                                                                                                                                                |                      |  |  |

| SW1IN,<br>SW2IN,<br>SW3IN, and<br>SW4IN | Switchers 1, 2, 3, and 4 input.                                                                                                                                                                                                                      | d 4 input.<br>Connect these pins to BP to supply<br>Switchers 1, 2, 3, and 4 respectively.<br>Place a 4.7 μF capacitor from each of<br>these pins to GND for decoupling.                                       |                      |  |  |

| SW1FB,<br>SW2FB,<br>SW3FB, and<br>SW4FB | Switchers 1, 2, 3, and 4 feedback.<br>Switchers 1, 2, 3, and 4 output voltage<br>sense respectively.                                                                                                                                                 | Connect these pins to the farther point<br>of each of their respective SWxOUT<br>pins, in order to sense and maintain<br>voltage stability.                                                                    | Ground               |  |  |

| SW1OUT                                  | Switcher 1 output. Buck switcher for processor core(s).                                                                                                                                                                                              |                                                                                                                                                                                                                |                      |  |  |

| GNDSW1                                  | Ground for switcher 1.                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                         | Ground               |  |  |

| SW2OUT                                  | Switcher 2 output. Buck switcher for processor SOG, etc.                                                                                                                                                                                             |                                                                                                                                                                                                                |                      |  |  |

| GNDSW2                                  | Ground for switcher 2.                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                         | Ground               |  |  |

| SW3OUT                                  | Switcher 3 output. Buck switcher for<br>internal processor memory and<br>peripherals.         Connect this pin to switcher 3 load.         Unconnect                                                                                                 |                                                                                                                                                                                                                | Unconnected          |  |  |

| GNDSW3                                  | Ground for switcher 3.                                                                                                                                                                                                                               | Fround for switcher 3. Ground                                                                                                                                                                                  |                      |  |  |

| SW4OUT                                  | Switcher 4 output. Buck switcher for external memory and peripherals.                                                                                                                                                                                | r Connect this pin to switcher 4 load. Unconnected                                                                                                                                                             |                      |  |  |

| GNDSW4                                  | Ground for switcher 4.                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                         | Ground               |  |  |

| Pin                  | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Typical Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | Connection if Unused |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|

| Switchers            |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| DVS1 and<br>DVS2     | Switcher 1 and 2 DVS input pins.<br>Provided for pin controlled DVS on the<br>buck switchers targeted for processor<br>core supplies (SW1 and 2<br>respectively). When the output<br>voltage of the switchers transition<br>from one voltage to another, its slope<br>is controlled in steps of 25 mV per<br>time step. The DVS pins may be<br>reconfigured for Switcher<br>Increment/Decrement (SID) mode<br>control.<br>These pins must be set high in order<br>for the DVS feature to be enabled for<br>each of switchers 1 or 2, or low to<br>disable it.<br>These pins are referenced to<br>SPIVCC, a logic one means<br>0.7*SPIVCC, however, the maximum<br>voltage of these pins is 3.1 V. They<br>are internally pulled low, so the<br>system will interpret that no DVS<br>function is desired when left<br>Unconnected. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Unconnected          |

| SWBSTIN              | Switcher BST input. This is the switching node of SWBST.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | The 2.2 $\mu$ H switcher BST inductor must be connected from BP to this pin.                                                                                                                                                                                                                                                                                                                                                                                                                                                 | Unconnected          |

| SWBSTOUT             | Power supply for gate driver for the internal power NMOS that charges SWBST inductor.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | It must be connected to BP.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Unconnected          |

| SWBSTFB              | Switcher BST feedback. When<br>SWBST is configured to supply the<br>UVBUS pin in OTG mode, the<br>feedback will be internally switched to<br>sense the UVBUS pin instead of the<br>SWBSTFB.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Connect this pin to the farthest point<br>of SWBSTOUT in order to sense this<br>voltage.<br>Note: No need to connect it to UVBUS<br>since this sensing is made internally<br>when working in OTG mode.                                                                                                                                                                                                                                                                                                                       | Ground               |

| GNDSWBST             | Reference ground for SWBST.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Ground               |

| Regulators           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                      |

| VINIOHI              | Supply input of VIOHI regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | Connect this pin to BP in order to supply VIOHI regulator.                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | Connect to BP pin    |

| VIOHI                | Output regulator for high voltage IO. A fixed 2.775 V output for high voltage level interface.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | An output 2.2 $\mu F$ capacitor is needed from this pin to Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Unconnected          |

| VINPLL and<br>VINDIG | Input of regulators for processor PLL<br>and Digital respectively.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | VINDIG and VINPLL can be<br>connected either to BP or a 1.8 V<br>switched mode power supply rail<br>(such as from SW4) for the two lower<br>set points of each regulator (1.2 V and<br>1.25 V output for VPLL, and 1.05 and<br>1.25 V output for VDIG). In addition,<br>when the two upper set points are<br>used (1.50 and 1.8 V output for VPLL,<br>and 1.65 and 1.8 V for VDIG), they<br>can be connected to either BP or a<br>2.2 V nominal external switched mode<br>power supply rail to improve power<br>dissipation. | Connect to BP pin    |

| VPLL                 | Output of regulator for processor PLL.<br>Quiet analog supply (PLL, GPS).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | An output 2.2 $\mu$ F capacitor is needed from this pin to Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                            | Unconnected          |

| Pin        | Description Typical Connection                                                                                                                           |                                                                                                                                                                                                                                                                                                                           | Connection if Unused |  |  |  |

|------------|----------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Regulators |                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                           |                      |  |  |  |

| VDIG       | Output regulator Digital. Low voltage digital (DPLL, GPS).                                                                                               | An output 2.2 $\mu F$ capacitor is needed from this pin to Ground                                                                                                                                                                                                                                                         | Unconnected          |  |  |  |

| VVIDEODRV  | Drive output for VVIDEO external<br>PNP transistor.                                                                                                      | Connect this pin to the base of the external PNP transistor of VVIDEO in order to drive it.                                                                                                                                                                                                                               | Unconnected          |  |  |  |

| VVIDEO     | Output regulator for TV DAC.                                                                                                                             | This pin must be connected to the collector of the external PNP transistor of the VVIDEO regulator. An output 2.2 µF capacitor is needed from this pin to Ground                                                                                                                                                          | Unconnected          |  |  |  |

| VINAUDIO   | VAUDIO regulator input .                                                                                                                                 | Typically connected to BP in order to supply VAUDIO regulator.                                                                                                                                                                                                                                                            | Connect to BP pin    |  |  |  |

| VAUDIO     | Output regulator for audio supply.                                                                                                                       | An output 2.2 $\mu F$ capacitor is needed from this pin to Ground                                                                                                                                                                                                                                                         | Unconnected          |  |  |  |

| VINUSB2    | Supply input for regulator VUSB2.                                                                                                                        | Connect this pin to BP in order to<br>supply the VINUSB2 regulator.                                                                                                                                                                                                                                                       | Connect to BP pin    |  |  |  |

| VUSB2      | Output regulator for powering USB PHY.                                                                                                                   | An output 2.2 $\mu F$ capacitor is needed from this pin to Ground                                                                                                                                                                                                                                                         | Unconnected          |  |  |  |

| VINCAMDRV  | Input of the camera regulator when<br>using the internal pass device and<br>drive output of the VCAM transistor, in<br>case of external PNP pass device. | This regulator has the option of using<br>either internal or external pass device.<br>When using internal pass device, this<br>pin has to be connected to BP in order<br>to supply the VCAM regulator. When<br>using external, this is the pin that<br>drives the PNP transistor, so in must<br>be connected to its base. | Unconnected          |  |  |  |

| VCAM       | Output regulator for camera module.                                                                                                                      | When using external PNP device, this pin must be connected to its collector.       Unconnected         An output 2.2 μF capacitor is needed from this pin to ground in both internal and external pass device cases.       Unconnected                                                                                    |                      |  |  |  |

| VSDDRV     | Drive output for VSD external PNP transistor.                                                                                                            | Connect this pin to the base of the Unconnected VSD external PNP in order to drive it.                                                                                                                                                                                                                                    |                      |  |  |  |

| VSD        | Output regulator for multi-media cards, such as micro SD.                                                                                                | $ \begin{array}{c} \mbox{This pin must be connected to the} \\ \mbox{collector of the external PNP} \\ \mbox{transistor of the VSD regulator. An} \\ \mbox{output 2.2 } \mu\mbox{F capacitor is needed} \\ \mbox{from this pin to Ground} \end{array} $                                                                   |                      |  |  |  |

| VGEN1DRV   | Drive output for VGEN1 external PNP transistor.                                                                                                          | Connect this pin to the base of VGEN1 external PNP in order to drive it.                                                                                                                                                                                                                                                  | Unconnected          |  |  |  |

| Pin        | Description Typical Connection                                                                                                                                                                                                                         |                                                                                                                                                                                                                                                                                                                                   | Connection if Unused |  |  |  |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------|--|--|--|

| Regulators |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                   |                      |  |  |  |

| VGEN1      | Output of general purpose 1 regulator.                                                                                                                                                                                                                 | This pin must be connected to the collector of the external PNP transistor of the VGEN1 regulator. An output 2.2 $\mu$ F capacitor is needed from this pin to Ground                                                                                                                                                              | Unconnected          |  |  |  |

| VGEN2DRV   | Drive output for VGEN2 external PNP transistor.                                                                                                                                                                                                        | Connect this pin to the base of VGEN2 external PNP in order to drive it.                                                                                                                                                                                                                                                          | Unconnected          |  |  |  |

| VGEN2      | Output of general purpose 2 regulator.                                                                                                                                                                                                                 | This pin must be connected to the collector of the external PNP transistor of the VGEN2 regulator. An output 2.2 $\mu$ F capacitor is needed from this pin to Ground                                                                                                                                                              | Unconnected          |  |  |  |

| VGEN3DRV   | Input for the VGEN3 regulator when<br>internal pass device is used and drive<br>output of VGEN3 transistor in case of<br>external PNP pass device.                                                                                                     | This regulator has the option of using<br>either the internal or external pass<br>device. When using the internal pass<br>device, this pin has to be connected to<br>BP in order to supply the VCAM<br>regulator. When using external, this is<br>the pin that drives the PNP transistor,<br>so in must be connected to its base. | Unconnected          |  |  |  |

| VGEN3      | Output of general purpose 3 regulator.                                                                                                                                                                                                                 | When using external PNP device, this pin must be connected to its collector. An output 2.2 $\mu$ F capacitor is needed from this pin to ground in both internal and external pass device cases.                                                                                                                                   | Unconnected          |  |  |  |

| VSRTC      | Output regulator for SRTC module on<br>processor. The VSRTC regulator<br>provides the CLK32KMCU output<br>level (1.2 V). Additionally, it is used to<br>bias the Low Power SRTC domain of<br>the SRTC module, integrated on<br>certain FSL processors. | from this pin to Ground the 1.0 $\mu$ F capac                                                                                                                                                                                                                                                                                     |                      |  |  |  |

| GNDREG1    | Ground for regulators 1.                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                                                                                                                                            | Ground               |  |  |  |

| GNDREG2    | Ground for regulators 2.                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                                                                                                                                            | Ground               |  |  |  |

| GNDREG3    | Ground for regulators 3.                                                                                                                                                                                                                               | Ground                                                                                                                                                                                                                                                                                                                            | Ground               |  |  |  |

| GPO1       | General purpose output 1.                                                                                                                                                                                                                              | Intended to be used for battery therm-<br>istor biasing. In this case, connect a<br>10 kOhm resistor from GPO1 to<br>ADIN5, and another one from ADIN5<br>to GND.                                                                                                                                                                 |                      |  |  |  |

| GPO2       | General purpose output 2.                                                                                                                                                                                                                              |                                                                                                                                                                                                                                                                                                                                   | Unconnected          |  |  |  |

|            |                                                                                                                                                                                                                                                        |                                                                                                                                                                                                                                                                                                                                   | 1                    |  |  |  |

| Pin                | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | Typical Connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Connection if Unused                                    |  |  |  |

|--------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|--|--|--|

| Regulators         |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                         |  |  |  |

| GPO3               | General purpose output 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Unconnected                                             |  |  |  |

| GPO4               | General purpose output 4. A second<br>general purpose input ADIN7B is<br>available on channel 7 of the ADC.<br>This input is muxed on the GPO4 pin.                                                                                                                                                                                                                                                                                                                                                      | On a typical application, a second<br>ambient light sensor is supposed to<br>be connected at ADIN7B (another one<br>should be connected to ADIN7,<br>please check the ADIN7 pin).                                                                                                                                                                                                                                                                                                                        | Unconnected                                             |  |  |  |

| Control Logic      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                         |  |  |  |

| LICELL             | Coin cell supply input and charger output. If the main battery is deeply discharged, removed, or contact-bounced (i.e., during a power cut), the RTC system and coin cell maintained logic will switch over to the LICELL for backup power. This pin also works as a current-limited voltage source for battery charging. The LICELL pin provides a connection for a coin cell backup battery or supercap. A small 0.1 $\mu$ F capacitor should be placed from LICELL to ground under all circumstances. |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 0.1 μF capacitor to<br>Ground                           |  |  |  |

| XTAL1 and<br>XTAL2 | 32.768 kHz crystal oscillator connections.                                                                                                                                                                                                                                                                                                                                                                                                                                                               | The 32.768 kHz crystal oscillator must<br>be connected between these pins,<br>also an 18 pF capacitor from each pin<br>to ground in this case.<br>The oscillator accepts a clock signal<br>from an external source. This clock<br>signal is to be applied to the XTAL1<br>pin, the signal can be DC or AC<br>coupled. A capacitive divider can be<br>used to adapt the source signal to the<br>XTAL1 input levels. When applying an<br>external source, the XTAL2 pin is to<br>be connected to VCOREDIG. | Connect XTAL1 to<br>ground and XTAL2 to<br>VCOREDIG pin |  |  |  |

| GNDRTC             | Ground for the RTC block.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | Ground for the RTC block. Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                         |  |  |  |

| CLK32K             | 32 kHz clock output for peripherals. At<br>system startup, the 32 kHz clock is<br>driven to CLK32K (provided as a<br>peripheral clock reference), which is<br>referenced to SPIVCC. CLK32K is<br>restricted to state machine activation<br>in normal On mode.                                                                                                                                                                                                                                            | Connect this pin to the clock input of the peripheral devices of the system.                                                                                                                                                                                                                                                                                                                                                                                                                             | Unconnected                                             |  |  |  |

| Pin                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Typical Connection                                                                                                                                                                                                                                              | Connection if Unused                                                                                                                                             |  |  |  |  |