#### Freescale Semiconductor

Data Sheet: Advanced Information

Document Number: LS102MA

Rev. 1, 10/2014

## QorlQ LS102MA Data Sheet

The high-performance embedded low-power processor LS10xMA, addresses a wide variety of applications ranging from high-end VoIP enabled home gateways, Small-Medium Business (SMB) high performance security appliances, and Ethernet powered 802.11n Enterprise Access Points (EAP).

LS10xMA delivers scalability, superior packet handling capabilities, Quality of Service (QoS) hardware features, increased Virtual Private Network (VPN) and Secure Sockets Layer (SSL) throughput. In order to provide performance scalability and maximum flexibility, the processor includes single and dual ARM®11 core devices from 450 MHz to 650 MHz delivering up to 1600 DMIPS.

The chip leverages the energy efficient ARM core technology and Freescale's low-power design process to achieve the lowest power consumption in its class (<2W typical @ 650 MHz). Additionally, the companion board support package software provides a rich set of power management features to address the energy saving goals of service providers and product manufacturers.

The I/O interfaces in conjunction with multi-layer bus architecture allows non-blocking concurrent transactions across all data interfaces, thus minimizing on-chip packet processing latency.

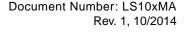

The OpenWRT Linux-based SDK is optimized for both single-core and dual-core operation. Figure 1-1 shows the block diagram of LS10xMA.

# Table of Contents

| Product Applications                        | PCI Express Interface                       |

|---------------------------------------------|---------------------------------------------|

| Features by Device Summary                  | Overview                                    |

| Technical Overview                          | PCI Express Features                        |

| Hardware Interfaces and Functional Blocks 3 | PCIe Configuration Options                  |

| Software Interfaces and Functional Blocks 9 | PCIe Signals                                |

| Pinlist and Signal Summary                  | Serial Peripheral Interface                 |

|                                             | Overview                                    |

| Pin List                                    | Features                                    |

| Design Notes                                | Functional Description                      |

| Input/Output PAD Types                      | Signal Descriptions                         |

| Signal Summary                              | SPI Timing                                  |

| Power and Ground                            | Transmit and Receive FIFO Buffers 83        |

| Expansion Bus Interface                     | SPI Interrupts                              |

| Features                                    | Transfer Modes                              |

| Expansion Bus Functional Description 40     | Operational Modes                           |

| Signal Description                          | SPI Clock Polarity and Phase Settings 90    |

| Modes of Operation                          | Clock Ratios                                |

| Boot Flash Configurations 54                | Security Accelerator                        |

| Clocks                                      |                                             |

| Reset                                       | Overview                                    |

| Expansion Interface AC Timing               | Features 93                                 |

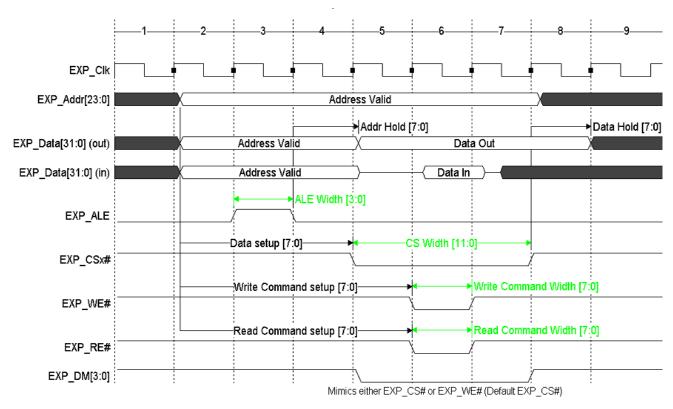

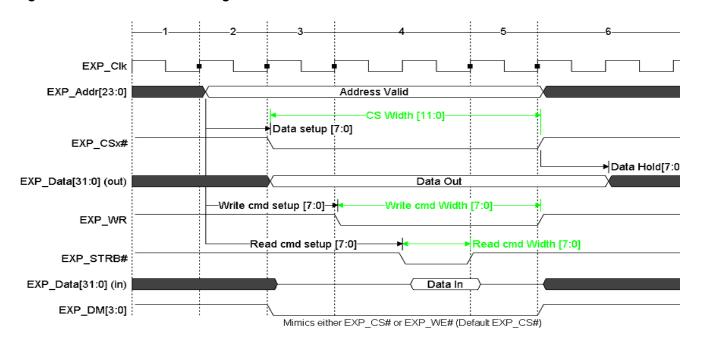

| Asynchronous Interface                      | Functional Description                      |

| DDR2 SDRAM Interface 57                     | TDM Bus Interface                           |

|                                             | Overview                                    |

| DDR2 SDRAM Features                         | Features                                    |

| Signal Descriptions                         | Signal Description                          |

| DDR2 SDRAM Interface Bus Timing 58          | Functional Description                      |

| Ethernet Interface 61                       | TDM Bus Interface Timing                    |

| Overview                                    | TDM Interface Timing                        |

| Features                                    | TDM Loopback Timing                         |

| Functional Description 62                   | Universal Asynchronous Receiver Transmitter |

| Ethernet Configuration Options 64           | 105                                         |

| Signal Descriptions                         | Overview                                    |

| Ethernet Signal Multiplexing 67             |                                             |

| Ethernet Interface Bus Timing 69            | Features                                    |

| · ·                                         | Functional Description                      |

|        | Signal Description                                                                                                    |

|--------|-----------------------------------------------------------------------------------------------------------------------|

| Inter- | IC Interface                                                                                                          |

|        | Features. 107 Functional Description 107 Signal Descriptions 107 I2C Timing 108 High Speed Mode 109                   |

|        | Clock Synchronization         109           Bus Arbitration         109                                               |

|        | Interface                                                                                                             |

|        | Overview                                                                                                              |

| Gener  | ral Purpose Input Output 115                                                                                          |

|        | Overview                                                                                                              |

| Interr | upt Controller                                                                                                        |

|        | Overview         119           Interrupt Controller Features         119           Functional Description         119 |

| Time   | rs                                                                                                                    |

|        | Overview121Timer Features121Functional Description121Timer Interface Signals124                                       |

| Test a | and Debug Interface                                                                                                   |

|        | Overview125Test and Debug Interface Signals125JTAG Interface Timing126Test Mode Configuration126                      |

| Powe   | r Management                                                                                                          |

|        | Overview                                                                                                              |

This figure shows the major functional units within LS10xMA.

Figure 1-1 LS10xMA Block Diagram

# **Product Applications**

The LS10xMA can be used as a general purpose processor with the following Data and Voice products applications:

- Intelligent and secure Triple-play wired and wireless home broadband gateways.

- Single or dual concurrent 802.11n EAP using Power-Over-Ethernet (POE).

- SMB router with IPSec VPN / SSL and firewall.

- Micro IP-PBX and Digital Enhanced Cordless Telecommunications (DECT) base stations.

#### 1.1 **Features by Device Summary**

The LS10xMA devices differ in the number of complex voice channels they support in Data and Voice mode.

**CAUTION:**

The device is screened for the specified frequency. Freescale cannot guarantee the operation if any changes are made in software. Any changes made without prior approval from Freescale may cause unexpected results and void in the warranty.

Table 1-1 lists the LS10xMA features by device numbers.

QorlQ LS10xMA Data sheet, Rev 1

#### **Product Applications**

Table 1-1 Features By Device Number

| ARM 11 <sup>TM</sup><br>Frequency | Number of Cores | Device Number | VoIP | Security | Ext Temp. |

|-----------------------------------|-----------------|---------------|------|----------|-----------|

| 533 MHz                           | 1               | LS101MASN7DFA | N    | N        | N         |

|                                   |                 | LS101MASE7DFA | Y    | Υ        | N         |

|                                   |                 | LS101MAXE7DFA | Y    | Υ        | Y         |

| 650 MHz                           | 1               | LS101MASN7EHA | N    | N        | N         |

|                                   |                 | LS101MASE7EHA | Y    | Υ        | N         |

| 450 MHz                           | 2               | LS102MASN7BFA | N    | N        | N         |

|                                   |                 | LS102MASE7BFA | Y    | Υ        | N         |

| 650 MHz                           | 2               | LS102MASN7EHA | N    | N        | N         |

|                                   |                 | LS102MASE7EHA | Y    | Υ        | N         |

3

## 2 Technical Overview

This section gives an overview of LS10xMA device hardware interfaces, functional blocks, and software interfaces.

CAUTION:

Freescale provides schematic and layout review. However, Freescale HIGHLY RECOMMENDS customers to submit their designs to Freescale for a complete confidential review.

## 2.1 Hardware Interfaces and Functional Blocks

The LS10xMA device provides the following external interfaces and functional blocks:

- Ethernet Interfaces

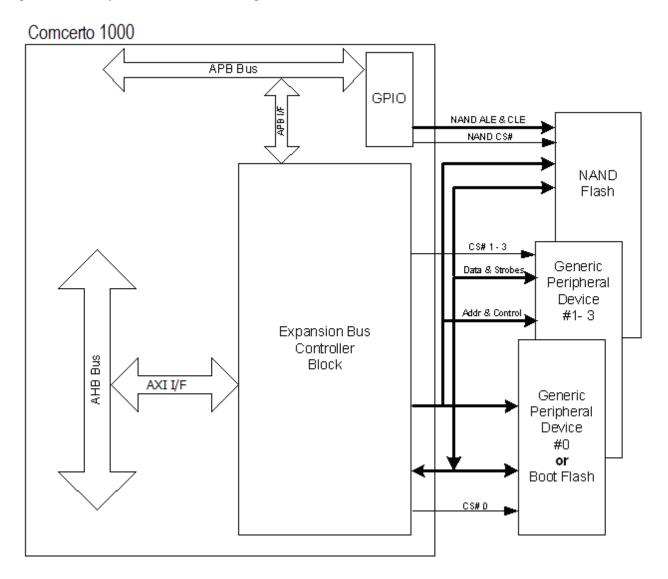

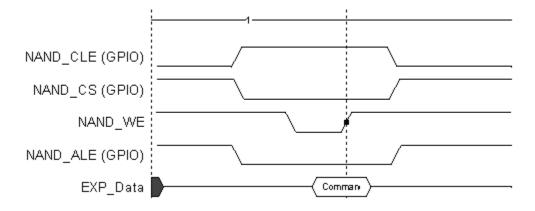

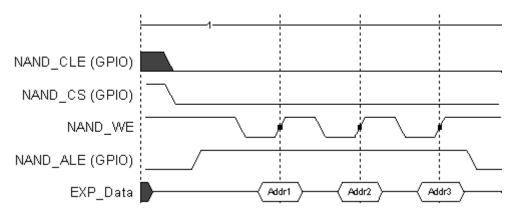

- Expansion Bus (EXPBUS) provides interfaces to NOR flash, NAND flash, and any other peripheral device that

uses a parallel configuration bus

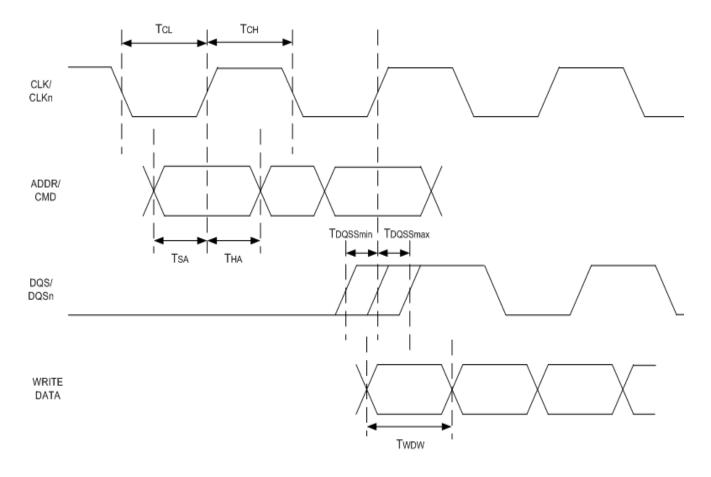

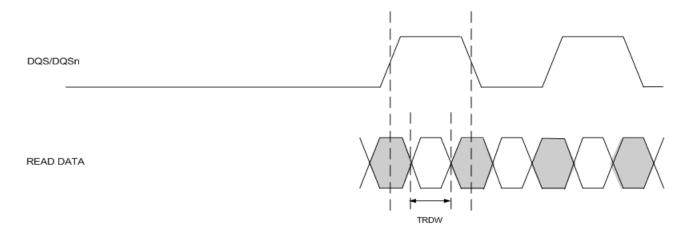

- DDR2 SDRAM Interface—16-Bit/32-Bit DDR2 interface, running at frequencies up to 400 MHz (data rate 800 Mbps per data bit)

- Peripheral Component Interface Express (PCIe)

- Time-Division Multiplexing (TDM) Bus

- Universal Serial Bus (USB) 2.0 Interface—USB 2.0 Host controller with integrated PHY

- Inter-IC Bus (I2C) Master/Slave Interface

- Serial Peripheral Interface (SPI)

- General Purpose Input Output (GPIO) Interface

- Universal Asynchronous Receiver/Transmitter (UART) Serial Interface Port

- Joint Test Action Group (JTAG) Interface—JTAG Interface for Test and debugging

- Timer Interface

- Reference Clock and Reset Controller

- Security Co-Processor

- ARM 1136J-S Processors

- Internal SRAM (ARAM)

- AMBA Advanced High Performance Bus (AHB)

- AHB to APB Bus Bridge

- Memory DMA Engine (MDMA)

- Internal Boot ROM (IBR)

- Interrupt Controller

### 2.1.1 Ethernet Interfaces

The LS10xMA includes two ethernet ports: WAN (ETH0) and LAN (ETH2). Both Ethernet interfaces support MII, RMII, RGMII. There is a single MDIO interface for both Ethernet ports. These configurations conform to IEEE 802.3 and support full-duplex and half-duplex operation at 10/100/1000 Mbps. For additional information, see Section 6 Ethernet Interface.

#### **Technical Overview**

### 2.1.2 Expansion Bus

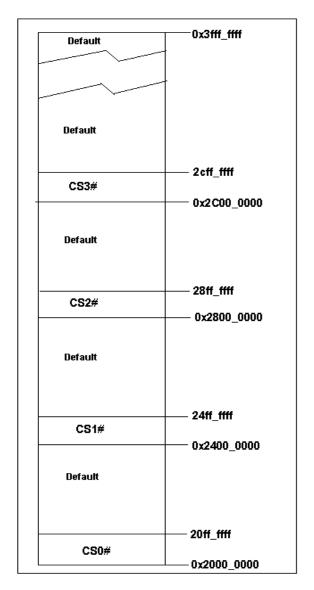

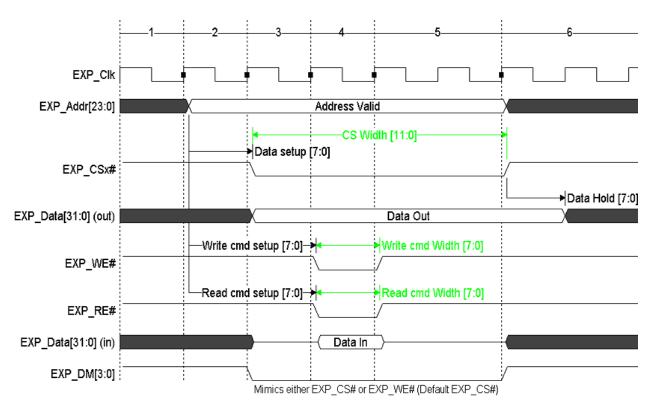

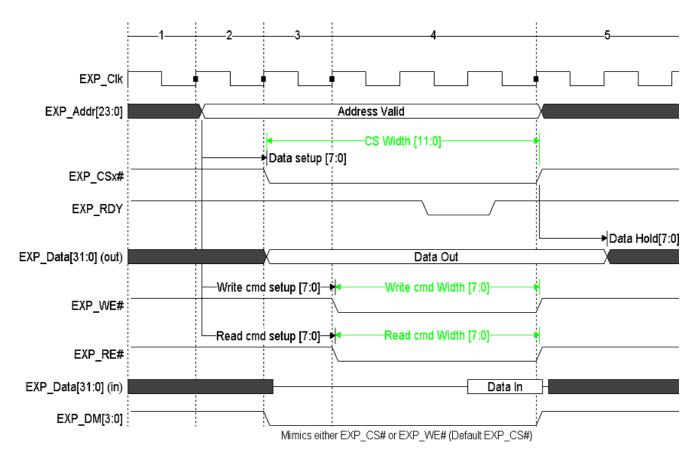

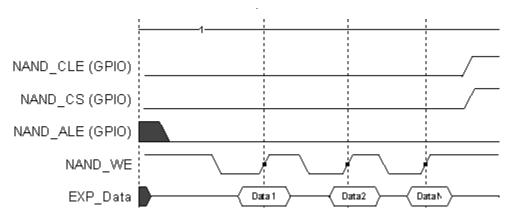

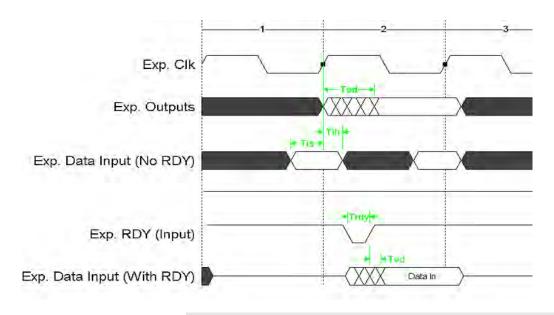

The LS10xMA Expansion Bus (EXPBUS) provides address, data, and control lines for connection to system peripheral devices. The EXP Bus provides chip selects for system peripheral devices such as Flash memory, Boot ROM, and so on. Expansion Bus provides support up to 5 peripheral devices: NAND flash and 4 general-purpose device interfaces, that is NOR flash devices. NAND flash chip-select is controlled by software and driven on a GPIO pin. EXPBUS chip selects are configurable and can support up to 16 M of address space. By default, it is configured to 4 M of address space. The Expansion Bus is synchronous and can be driven with the AHB clock using a divide down of 3, 4, 5, 6, or 7, hence providing a maximum of 66 MHz. The expansion bus provides the following features:

- Provides support for multiplexed address-data mode with address latch enable.

- Provides support for Ready/Busy# acknowledge signal for terminating transactions. Detecting the de-assertion

of Read/Busy# signal will over-ride the Chip-Select and Write Enable/ Read Enable to be de-asserted for the

current transaction. Detection of Ready signal on rising/falling edge is configurable.

For more information, see Chapter 4, Expansion Bus Interface.

#### 2.1.3 DDR2 SDRAM Interface

The LS10xMA device provides address, data, and control lines for connection to DDR2 Synchronous Dynamic Random Access Memory (SDRAM). The DDR2 interface supports the following:

- 32-Bit or 16-Bit data bus interfacing to x8 and x16 memories (x4 not supported)

- Address bus supports up to 1 GB of memory with one chip select

- Supports up to SDRAM at the frequency of 125 MHz up to 400 MHz

- Support for DDR2 power saving modes: Power down mode and self refresh mode

- Supports burst lengths of 4 cycles

- Supports for 4 or 8 internal banks for concurrent operation

- 1.8V I/O (SSTL\_18 compatible)

For more information, see Chapter 5, DDR2 SDRAM Interface.

## 2.1.4 Peripheral Component Interface Express (PCIe)

The LS10xMA device includes two single-lane PCIe interfaces conforming to the *PCI Express Base Specification*, *Revision 1.1*. Each PCIe interface can be independently configured to operate in Root Mode. PCIe interface share the same reference clock inputs, which must be provided by an external source. For more information, see Chapter 7, PCI Express Interface.

## 2.1.5 Time-Division Multiplexing (TDM) Bus

The TDM Bus interface provides one full-duplex, serial TDM bus providing a maximum of 24/32/64/128 timeslots (running at 1.5444 MHz, 2.048 MHz, 4.096 MHz, or 8.192 MHz, accordingly) for digital data transfer between devices such as Subscriber Line Interface Circuits (SLICs), and the LS10xMA. The TDM Interface timing parameters are programmable. For more information, see Chapter 10, TDM Bus Interface.

#### 2.1.6 Universal Serial Bus (USB) 2.0 Interface

The USB 2.0 Host Interface supports High Speed (480 Mbps) mode, and is backward compatible with USB1.1. USB interface handles all of the USB 2.0 protocol and provides a simple Read/Write protocol to the application software. Some of the features of the USB Controller are:

- USB 2.0 compliance

- Low Speed (LS)—1.5 Mbps, Full Speed (FS)—12 Mbps, and High Speed (HS)—480 Mbps

- External HUB support

- Integrated PHY

- · Supports up to four end points, when configured in device mode

For more information, see Chapter 13, USB Interface.

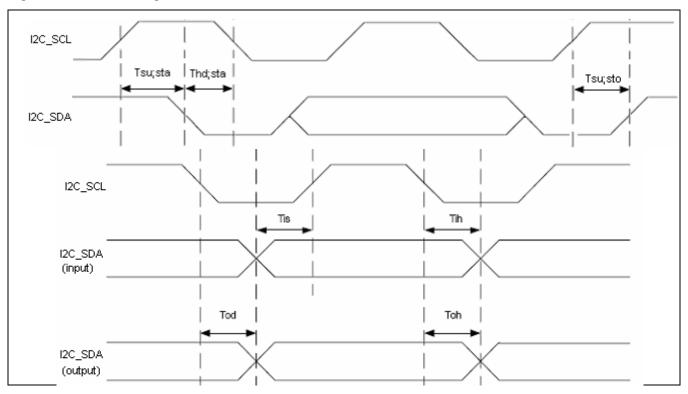

## 2.1.7 Inter-IC Bus (I<sup>2</sup>C) Master/Slave Interface

The LS10xMA device supports I<sup>2</sup>C interface in master, slave, or in multi-master mode. Available Freescale drivers allow LS10xMA device to boot from a serial EEPROM through the I<sup>2</sup>C interface. The I<sup>2</sup>C Bus is a low-bandwidth, short distance protocol for on board communications. The devices are connected through two wires: Serial data (SDA) and Serial clock (SCL).

All devices must have a unique address to identify it on the bus. Slave devices have a predefined address, but the lower bits of the address can be assigned to allow for multiples of the same devices on the bus. The I<sup>2</sup>C EEPROM can be used for booting by assigning 000 address for it.

The I<sup>2</sup>C Bus supports multiple data speeds: standard (100 kbps), fast (400 kbps) and High Speed (3.4 Mbps) communications. Other features include:

- Built in collision detection

- Support for 7-Bit and 10-Bit addressing

- Operates as a master, a slave, or in multi-master mode

For more information, see Chapter 12, Inter-IC Interface.

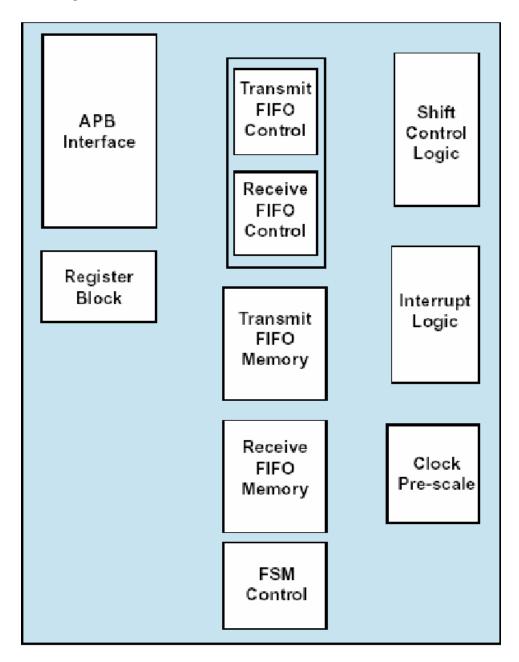

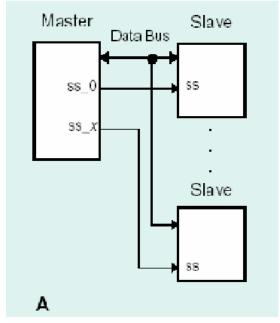

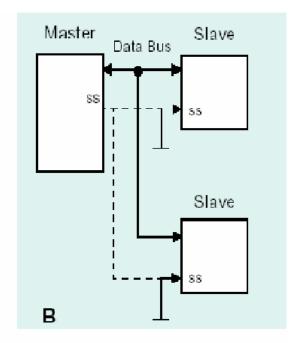

## 2.1.8 Serial Peripheral Interface (SPI)

A multi-chain SPI provides a common interface mechanism for controlling peripheral devices. For example, SLICs from multiple vendors can be controlled on the SPI Bus. The LS10xMA device supports SPI and can be configured for booting. For more information, see Chapter 8, Serial Peripheral Interface.

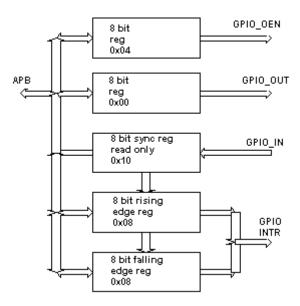

## 2.1.9 General Purpose Input Output (GPIO) Interface

The LS10xMA device provides up to 31 GPIO signals. Of those 31, only 7 can be programmed to create interrupts with rising or falling or both edges of input signals. The interface signals are also level sensitive and can generate interrupt as long as the input is high. The GPIO block holds the configuration registers for the GPIO lines, the block also holds configuration registers for other blocks and input signals. For details, see Chapter 14, General Purpose Input Output.

NOTE:

Freescale firmware utilities and example software drivers use GPIOs. To make optimal use of the GPIOs, review planned use of Freescale utilities and drivers with your Freescale representative.

QorlQ LS10xMA Data sheet, Rev 1

#### **Technical Overview**

# 2.1.10 Universal Asynchronous Receiver/Transmitter (UART) Serial Interface Port

The LS10xMA device provides two UART interfaces, with FIFOs. Only the Rx and Tx signals are provided, which can be connected to an RS232 driver for standard serial port operation. The UART interfaces provide a useful console port and can also be used as a software debug port. It is recommended to connect the UART pins to standard connectors such as RJ45, 9-pin DIN for easy access. For more information, see Section 11 Universal Asynchronous Receiver Transmitter.

## 2.1.11 Joint Test Action Group (JTAG) Interface

The LS10xMA device provides one JTAG interface, which can access both ARM® cores. The JTAG interface provides access to the ARM11 embedded In-Circuit Emulator (ICE) unit and supports IEEE 1149.1 Boundary Scan for manufacturing and test. For more information, see Chapter 17, Test and Debug Interface.

## 2.1.12 Timer Interface

The LS10xMA timer block includes six general purpose timers each of which can generate an interrupt when the upper limit is reached. Two of the general purpose timers can link to I/O pins and either drive an external output or allow external signals to increment the timer. This block also contains TDM frame sync timer and a watchdog timer.

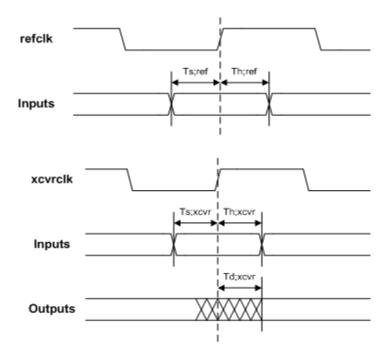

#### 2.1.13 Reference Clock and Reset Controller

A 24 MHz clock oscillator drives the reference clock interface. The single-clock requirement reduces EMI and system design complexity. For detailed requirements see Section 20.4 Reference Clock.

A Clock and Reset Controller block supports three independent PLLs. The Clock and Reset Controller supports alternative derivations of AHB clock from the reference clock. It also supports independent configuration of clock frequencies for the two ARMs and clock power-down of both ARMs. The Clock and Reset Controller has the following functions:

- 1. Generates two external GEM Reference clocks

- 2. Generates external TDM clock

- 3. Generates ARM and AHB clocks

- 4. Generates DDR clock synchronous, pseudo-synchronous, or asynchronous to AHB

- 5. Independent clock power down for various blocks

- Independent reset for various blocks

- 7. Watchdog reset with enable and disable mechanism

- 8. Global software reset

## 2.1.14 Security Co-Processor

The LS10xMA has an integrated hardware crypto engine, which can be used for IPSEC and SSL/TLS offloads, key generation acceleration, and random number generation. The security co-processor enables support of NIST-certified VPN technology and supports SSL sessions. As a co-processor, the main advantage this logic core offers over simple cryptographic accelerators is that it can perform crypto operation (cipher + digest) as well as processes IPSec Encapsulating Security Payload (ESP) and Authentication Header (AH) protocols for IPv4 and IPv6.

The co-processor's capabilities include:

- Performs AES128/192/256, DES, 3DES, cipher operation

- Performs MD5, SHA-1, SHA-256 digest operation

- · Inserts or removes ESP/AH headers and trailers

- Updates IP header (protocol, length, checksum)

- Manages Security Association Database

- Performs TTL update and anti-replay checks

- Inbound and outbound operation fully processed in parallel

- Uses DMA for packets and contexts (SA)

- Hardware support for SSL

- Concurrent support for SSL sessions and IPSec tunnels

- True Random Number Generation (TRNG) capabilities

- · Key acceleration hardware offload

The Security co-processor's DMA can be configured to handle up to 64 packets for ciphering and 64 more for deciphering without any processor intervention. It can also perform "raw cryptographic" processing through the AHB slave interface and an internal Security Resource Manager (SRM). This feature can be used to encrypt/decrypt any non IPSec block of data (AES or SHA1 for voice cipher) in parallel with any IPSec task.

The LS10xMA dual-processor architecture allows the IPSec core to be used by both the Media Stream Processor (MSP) and Application Control Processor (ACP). For example, the MSP can use the IPSec co-processor for a raw cryptographic task such as SRTP helper, or SSL services, while the ACP can use it for IPSec off-loading. For a list of features and complete details, see Chapter 9, Security Accelerator.

#### 2.1.15 ARM 1136J-S Processors

The LS10xMA centers around two ARM1136J-S processors, symmetric in hardware architecture, supporting the ARM DSP extensions. Processor performance is improved by separate 64 KB instruction and data caches, as well as by 32 KB tightly-coupled data memory (DTCM). The DTCM is essentially a private SRAM attached to the ARM processor and mapped to a configurable 32 KByte contiguous address space. It is a software-managed, very fast (ARM speed) scratch pad memory.

The ARM 11's virtual memory system involves translations to physical addresses on each access supported by a hierarchy of Translation Lookaside Buffers (TLBs) and micro-TLBs. Both the physical address and an Application Space Identifier (ASID) index tag, cache entries. The use of both physical addresses and ASIDs, has demonstrated acceleration of context switching in Linux benchmarks.

Each ARM processor provides three 64-Bit AHB master (Instruction, data read and data write) ports. These AHB master ports operate at AMBA AHB interface clock frequency.

## 2.1.16 Internal SRAM (ARAM)

The ARAM functions as an AHB slave. It provides 128 KB of dual-ported memory arranged as 64-Bit words and is accessible in 8-Bit, 16-Bit, 32-Bit, and 64-Bit widths. The ARAM provides fast internal storage for timing critical data structures. The ARAM controller is used for the following purposes:

- Control and manage the read and writes accesses through the 2 AHB ports to the SRAM

- Control and manage the semaphores mechanism for up to 16K ARAM configurable sections

#### **Technical Overview**

Up to two masters can access from the AHB at the same time with different transactions at different memory addresses. Only when the access is done to the same address, one of the masters will be delayed until the other master is done. The decision of which master waits for the other to finish will be done according to a fixed or round robin priority, which is set through configuration.

## 2.1.17 AMBA Advanced High Performance Bus (AHB)

The AMBA Bus from ARM provides a central bus through which all AHB masters must access AHB slaves. This bus connects 14 master-capable and 10 slave-only devices. The AHB block has the following basic functionalities and features:

- · Multi-master fixed system with an increased available bus bandwidth

- Multiple layers of arbitration. Controlled by host accessible registers

- 64-bit data bus for most Master/Slaves

- Re-mapping address regions

## 2.1.18 AHB to APB Bus Bridge

The AHB to APB Bus Bridge (AAB) connects the AHB to the APB. The AAB block converts AHB transfers into a suitable format for the slave devices or peripheral registers on the APB. The bus bridge always functions as a slave on the AHB bus and as a master on the APB bus.

### **2.1.19 Memory DMA Engine (MDMA)**

A Memory DMA (MDMA) block is included to facilitate in inter-CPU data communication (virtual Ethernet interface) and in memory-to-memory data copies. All of these interfaces are connected to the CPU cores with appropriate control logic and DMA controllers. The MDMA block performs low-latency transfers of data blocks from or to ARAM and DDR memories. The MDMA block has the following basic functionalities:

- Performs data copy from one memory region to another

- Supports data management using an array-type list of descriptors

- Support for multiple virtual paths

- Independently set up and serviced by receive side and by transmit side (each possibly controlled by a different CPU)

- · Congestion control assistance

## 2.1.20 Internal Boot ROM (IBR)

A 4096-word by 32-Bit Internal Boot Rom (IBR) provides startup initialization and BIST testing.

## 2.1.21 Interrupt Controller

The Interrupt Controller block provides multiple status and mask registers to handle all device peripheral interrupts and generates IRQs and FIQs for the two ARM CPUs. It also contains inter-processor signaling features. The Interrupt Controller device requires multiple interrupt status registers and associated mask registers.

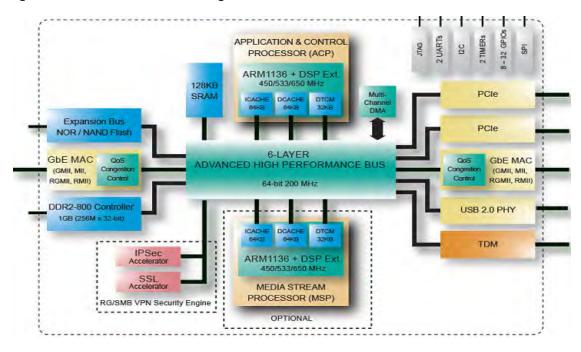

## 2.2 Software Interfaces

The LS10xMA user applications interface to the hard real time voice code by means of a shared memory interface within the device. This partitioning allows deterministic execution of the voice processing channels, at the same time providing the flexibility and performance to applications.

In the dual ARM11 architecture, one CPU runs the router software and the other CPU handles the Fast Packet Processing (FPP) firmware. The CPU that runs Linux is referred to as the ACP, and the CPU that runs FPP is referred to as the MSP. Figure 1-1 illustrates the dual core architecture and the overall partition between the ACP and MSP in LS10xMA devices. The VoIP module runs on the MSP, in parallel to the FPP module.

Figure 2-1 Software Architecture

#### 2.2.1 Embedded Host Controller Firmware

The LS10xMA device is provided with a Board Support Package (BSP) for popular Operating Systems (OS) that provides the kernel operating environment for the host application. Applications are built and debugged on this device using standard third party ARM tool chains and debuggers.

## 2.2.2 Voice Channel Firmware

Voice channel firmware is provided in ARM AXF format for downloading to SDRAM, at boot time. This image contains code for FPP, signal processing, and encryption (if applicable).

## 2.2.3 Development Tools

The development tools include:

- JTAG-based ICE

- U-Boot commands and diagnostics

- Core dump procedures

**Technical Overview**

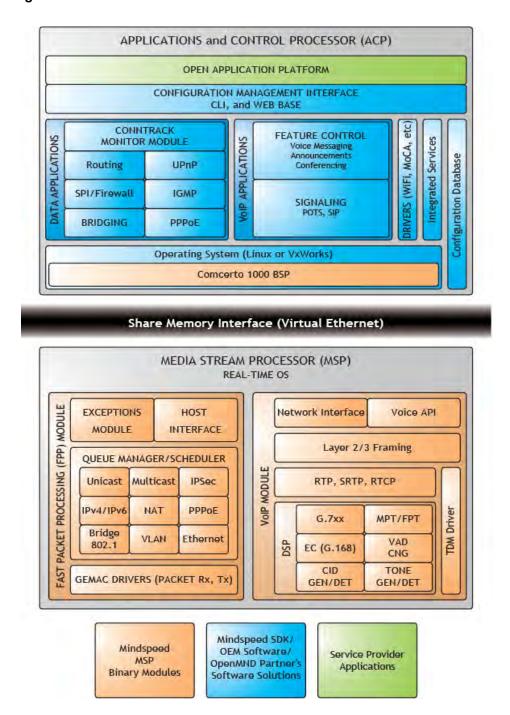

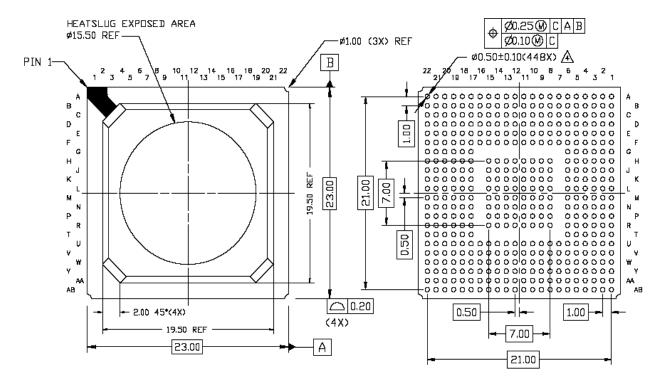

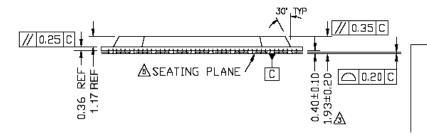

This section presents pin information, I/O pad details, and signal descriptions of the LS10xMA device. For a LS10xMA pin list as in '.txt' or '.xls' format, contact your Freescale sales representative. Figure 3-1illustrates the LS10xMA device top view.

Figure 3-1 Device Top View

Table 3-1 lists the Pin details of LS10xMA device. For description about I/O pad types see Table 3-2, I/O Type Descriptions.

## 3.1 Pin List

Table 3-1 Landing List

| Location | Signal Symbol                      | Dir        | I/O Type  |

|----------|------------------------------------|------------|-----------|

| A1       | I2C_SCL/GPIO_18                    | Both (B)   | Ihu/Ots8  |

| A2       | GPIO_1                             | В          | Ihu/Ots16 |

| A3       | GPIO_0                             | В          | Ihu/Ots16 |

| A4       | GPIO_3                             | В          | Ihu/Ots16 |

| A5       | UART1_RX / GPIO_22                 | В          | Ihu/Ots16 |

| A6       | UART0_TX                           | Output (O) | Ots8      |

| A7       | JTAG_TRST_N                        | Input (I)  | Ihu       |

| A8       | JTAG_TDO                           | 0          | Ots8      |

| A9       | EXP_A_2 /TM_ETH0_MODE_0            | В          | Id/Ots8   |

| A10      | EXP_A_5 /TM_ETH1_MODE_1            | В          | Id/Ots8   |

| A11      | EXP_A_17 /GPIO_10                  | В          | Ihd/Ots8  |

| A12      | EXP_WE_N                           | 0          | Ots8      |

| A13      | EXP_A_8 /TM_TDM_CLKSRC_<br>EN      | В          | Id/Ots8   |

| A14      | EXP_A_11 /TM_GPBT_OP1              | В          | Id/Ots8   |

| A15      | EXP_A_14 /GPIO_14                  | В          | Ihd/Ots8  |

| A16      | EXP_NAND_RE_N /EXP_A_22            | В          | Ihu/Ots8  |

| A17      | EXP_DQ_7                           | В          | I/Ots8    |

| A18      | EXP_DQ_13                          | В          | I/Ots8    |

| A19      | EXP_DQ_12                          | В          | I/Ots8    |

| A20      | EXP_DQ_3                           | В          | I/Ots8    |

| A21      | EXP_DQ_9                           | В          | I/Ots8    |

| A22      | EXP_DQ_8                           | В          | I/Ots8    |

| B1       | I2C_SDA /GPIO_19                   | В          | Ihu/Ots8  |

| B2       | TIM_EVNT1 /GPIO_16                 | В          | Ihu/Ots8  |

| В3       | TM_EXT_RESET /GPIO_17              | В          | Ihd/Ots8  |

| B4       | GPIO_2                             | В          | Ihu/Ots16 |

| B5       | EXP_IRQ / GPIO_7                   | В          | Ihu/Ots16 |

| В6       | UART0_RX                           | I          | Ihu       |

| В7       | JTAG_TCK                           | I          | Ihu       |

| B8       | JTAG_TMS                           | I          | Ihu       |

| В9       | EXP_A_3 /TM_ETH0_MODE_1            | В          | Id/Ots8   |

| B10      | EXP_A_6/TM_BOOT_OP1                | В          | Id/Ots8   |

| B11      | EXP_NAND_CS /EXP_A_18 /<br>GPIO_29 | В          | Ihu/Ots8  |

## QorlQ LS10xMA Data sheet, Rev 1

Table 3-1 Landing List (continued)

| Location | Signal Symbol                       | Dir | I/O Type  |

|----------|-------------------------------------|-----|-----------|

| B12      | EXP_NAND_CLE /EXP_A_20 /GPIO_31     | В   | Ihu/Ots8  |

| B13      | EXP_A_9 /TM_EXP_NAND_SEL            | В   | Id/Ots8   |

| B14      | EXP_A_12 /TM_PCIE_EXT_<br>REFCLK    | В   | Id/Ots8   |

| B15      | EXP_A_15 /GPIO_8                    | В   | Ihd/Ots8  |

| B16      | EXP_A_16 /GPIO_9                    | В   | Ihd/Ots8  |

| B17      | EXP_DQ_14                           | В   | I/Ots8    |

| B18      | EXP_DQ_5                            | В   | I/Ots8    |

| B19      | EXP_DQ_4                            | В   | I/Ots8    |

| B20      | EXP_DQ_10                           | В   | I/Ots8    |

| B21      | EXP_DQ_1                            | В   | I/Ots8    |

| B22      | EXP_DQ_0                            | В   | I/Ots8    |

| C1       | TDM_DR                              | I   | Ihd       |

| C2       | TIM_EVNT0/GPIO_15                   | В   | Ihu/Ots8  |

| C3       | RESET_N                             | I   | Ih        |

| C4       | TM_BSCANMODE                        | I   | Id        |

| C5       | GPIO_5 /EXP_CS3_N                   | В   | Ihu/Ots16 |

| C6       | UART1_TX /GPIO_23                   | В   | Ihu/Ots16 |

| C7       | JTAG_TDI                            | I   | Ihu       |

| C8       | EXP_A_1 /TM_PCIE1_MODE              | В   | Id/Ots8   |

| С9       | EXP_A_4 /<br>TM_ETH1_MODE_0         | В   | Id/Ots8   |

| C10      | EXP_A_7/TM_BOOT_OP_0                | В   | Id/Ots8   |

| C11      | EXP_NAND_RDY/EXP_A_21 /<br>GPIO_6   | В   | Ihu/Ots8  |

| C12      | EXP_NAND_ALE /EXP_A_19 /<br>GPIO_30 | В   | Ihu/Ots8  |

| C13      | EXP_A_10 /TM_GPBT_OP0               | В   | Id/Ots8   |

| C14      | EXP_A_13 /GPIO_11                   | В   | Ihd/Ots8  |

| C15      | EXP_NAND_WE_N /EXP_A_23             | В   | Ihu/Ots8  |

| C16      | EXP_DQ_15                           | В   | I/Ots8    |

| C17      | EXP_DQ_6                            | В   | I/Ots8    |

| C18      | EXP_DQ_11                           | В   | I/Ots8    |

| C19      | EXP_DQ_2                            | В   | I/Ots8    |

| C20      | EXP_DM_1                            | О   | Ots8      |

| C21      | EXP_DM_0                            | 0   | Ots8      |

| C22      | EXP_CLK                             | 0   | Ot8       |

Table 3-1 Landing List (continued)

| Location                | Signal Symbol                          | Dir | I/O Type |

|-------------------------|----------------------------------------|-----|----------|

| D1                      | TDM_FS                                 | В   | Ih/Ot8   |

| D2                      | TDM_DX                                 | O*  | Id/Ots8  |

| D3                      | TM_TESTMODE_N                          | I   | Iu       |

| D4                      | VSS                                    | _   | GND      |

| D5                      | VSS                                    | _   | GND      |

| D6                      | VSS                                    | _   | GND      |

| D7                      | VDDO_EXP                               | _   | PWR      |

| D8                      | VSS                                    | _   | GND      |

| D9                      | VDDO_EXP                               | _   | PWR      |

| D10                     | VSS                                    | _   | GND      |

| D11                     | VDDO_EXP                               | _   | PWR      |

| D12                     | VSS                                    | _   | GND      |

| D13                     | VDDO_EXP                               | _   | PWR      |

| D14                     | VSS                                    | _   | GND      |

| D15                     | VDDO_EXP                               | _   | PWR      |

| D16                     | VSS                                    | _   | GND      |

| D17                     | VSS                                    | _   | GND      |

| D18                     | VSS                                    | _   | GND      |

| D19                     | VSS                                    | _   | GND      |

| D20                     | EXP_RE_N                               | 0   | Ots8     |

| D21                     | EXP_RDY/BSY_N /GPIO_21                 | В   | Ihu/Ots8 |

| D22                     | EXP_ALE /<br>GPIO_20                   | В   | Ihd/Ots8 |

| E1                      | SPI_SCLK /GPIO_24                      | В   | Ihu/Ots8 |

| E2                      | SPI_RXD /GPIO_12                       | В   | Ihd/Ots8 |

| E3                      | TDM_CK                                 | В   | Ih/Ot16  |

| E4                      | VSS                                    | _   | GND      |

| E5                      | VSS                                    | _   | GND      |

| E6                      | VSS                                    | _   | GND      |

| E7                      | VDDO_EXP                               | _   | PWR      |

| E8                      | VSS                                    | _   | GND      |

| - Though it has bidired | tional pad, it is used as output only. | l   |          |

| E9                      | VDDO_EXP                               | _   | PWR      |

| E10                     | VSS                                    | _   | GND      |

| E11                     | VDDO_EXP                               | _   | PWR      |

| E12                     | VSS                                    | _   | GND      |

QorlQ LS10xMA Data sheet, Rev 1

Table 3-1 Landing List (continued)

| Location | Signal Symbol          | Dir | I/O Type |

|----------|------------------------|-----|----------|

| E13      | VDDO_EXP               | _   | PWR      |

| E14      | VSS                    | _   | GND      |

| E15      | VDDO_EXP               | _   | PWR      |

| E16      | VSS                    | _   | GND      |

| E17      | VSS                    | _   | GND      |

| E18      | VSS                    | _   | GND      |

| E19      | VSS                    | _   | GND      |

| E20      | EXP_CS2_N              | 0   | Ots8     |

| E21      | EXP_CS1_N              | 0   | Ots8     |

| E22      | EXP_CS0_N              | 0   | Ots8     |

| F1       | SPI_SS1_N /GPIO_26     | В   | Ihu/Ots8 |

| F2       | SPI_SS2_N /GPIO_27     | В   | Ihu/Ots8 |

| F3       | SPI_TXD /GPIO_25       | В   | Ihu/Ots8 |

| F4       | VSS                    | _   | GND      |

| F5       | VSS                    | _   | GND      |

| F6       | VSS                    | _   | GND      |

| F7       | VDDO_EXP               | _   | PWR      |

| F8       | VDD                    | _   | PWR      |

| F9       | VDDO_EXP               | _   | PWR      |

| F10      | VDD                    | _   | PWR      |

| F11      | VDDO_EXP               | _   | PWR      |

| F12      | VDD                    | _   | PWR      |

| F13      | VDDO_EXP               | _   | PWR      |

| F14      | VDD                    | _   | PWR      |

| F15      | VDDO_EXP               | _   | PWR      |

| F16      | VDDO_EXP               | _   | PWR      |

| F17      | VSS                    | _   | GND      |

| F18      | VSS                    | _   | GND      |

| F19      | VSS                    | _   | GND      |

| F20      | EXP_A_0 /TM_PCIE0_MODE | В   | Id/Ots8  |

| F21      | DDR_DATA_5             | В   | MEMIO    |

| F22      | DDR_DATA_2             | В   | MEMIO    |

| G1       | USB_VBUS_STAT          | I   | I        |

| G2       | SPI_SS0_N /GPIO_13     | В   | Ihu/Ots8 |

| G3       | GPIO_28                | В   | Ihu/Ots8 |

| G4       | VSS                    | _   | GND      |

### QorlQ LS10xMA Data sheet, Rev 1

Table 3-1 Landing List (continued)

| Location | Signal Symbol  | Dir | I/O Type  |

|----------|----------------|-----|-----------|

| G5       | VSS            | _   | GND       |

| G6       | VDD            | _   | PWR       |

| G7       | _              | _   | _         |

| G8       | _              | _   | _         |

| G9       | _              | _   | _         |

| G10      | _              | _   | _         |

| G11      | _              | _   | _         |

| G12      | _              | _   | _         |

| G13      | _              | _   | _         |

| G14      | _              | _   | _         |

| G15      | _              | _   | _         |

| G16      | _              | _   | _         |

| G17      | VDD            | _   | PWR       |

| G18      | VSS            | _   | GND       |

| G19      | VSS            | _   | GND       |

| G20      | DDR_DATA_0     | В   | MEMIO     |

| G21      | DDR_DATA_7     | В   | MEMIO     |

| G22      | DDR_DQS0_N     | В   | MEMIODIF  |

| H1       | USB_DM         | В   | USBDATA   |

| H2       | Do Not Connect | В   | USBANALOG |

| НЗ       | USB_REF        | _   | USBANALOG |

| H4       | VDDO_EXP       | _   | PWR       |

| Н5       | VDDO_EXP       | _   | PWR       |

| Н6       | VDDO_EXP       | _   | PWR       |

| Н7       | _              | _   | _         |

| Н8       | VSS            | _   | GND       |

| Н9       | VSS            | _   | GND       |

| H10      | VSS            | _   | GND       |

| H11      | VSS            | _   | GND       |

| H12      | VSS            | _   | GND       |

| H13      | VSS            | _   | GND       |

| H14      | VSS            | _   | GND       |

| H15      | VSS            | _   | GND       |

| H16      | _              | _   | _         |

| H17      | VDDO_DDR2      | _   | PWR       |

| H18      | VDDO_DDR2      | _   | PWR       |

### QorlQ LS10xMA Data sheet, Rev 1

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                      | Dir | I/O Type |

|----------|----------------------------------------------------|-----|----------|

| H19      | VDDO_DDR2                                          | _   | PWR      |

| H20      | DDR_DQS_0                                          | В   | MEMIODIF |

| H21      | DDR_DM_0                                           | 0   | MEMIO    |

| H22      | DDR_DATA_6                                         | В   | MEMIO    |

| J1       | USB_DP                                             | В   | USBDATA  |

| J2       | GMII0_RXD4                                         | I   | I        |

| Ј3       | GMII0_RXD0 /RGMII0_RXD0 /MII0_RXD0 /RMII0_RXD0     | I   | I        |

| J4       | VDDA25_USB                                         | _   | PWR      |

| J5       | VDDA25_USB                                         | _   | PWR      |

| J6       | VDDA25_USB                                         | _   | PWR      |

| J7       | _                                                  | _   | _        |

| J8       | VSS                                                | _   | GND      |

| J9       | VSS                                                | _   | GND      |

| J10      | VSS                                                | _   | GND      |

| J11      | VSS                                                | _   | GND      |

| J12      | VSS                                                | _   | GND      |

| J13      | VSS                                                | _   | GND      |

| J14      | VSS                                                | _   | GND      |

| J15      | VSS                                                | _   | GND      |

| J16      | _                                                  | _   | _        |

| J17      | VDD                                                | _   | PWR      |

| J18      | VSS                                                | _   | GND      |

| J19      | VSS                                                | _   | GND      |

| J20      | DDR_DATA_1                                         | В   | MEMIO    |

| J21      | DDR_DATA_3                                         | В   | MEMIO    |

| J22      | DDR_DATA_4                                         | В   | MEMIO    |

| K1       | GMII0_RXD2/RGMII0_RXD2/<br>MII0_RXD2/RMII0_PHY_DPX | I   | I        |

| K2       | GMII0_RXD5                                         | I   | I        |

| К3       | GMII0_RXD1 /RGMII0_RXD1/<br>MII0_RXD1/RMII0_RXD1   | I   | I        |

| K4       | VDDA33_USB                                         | _   | PWR      |

| K5       | VDDA33_USB                                         | _   | PWR      |

| K6       | VDDA33_USB                                         | _   | PWR      |

| K7       | _                                                  | _   | _        |

| K8       | VSS                                                | _   | GND      |

| К9       | VSS                                                | _   | GND      |

### QorlQ LS10xMA Data sheet, Rev 1

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                       | Dir | I/O Type |

|----------|-----------------------------------------------------|-----|----------|

| K10      | VSS                                                 | _   | GND      |

| K11      | VSS                                                 | _   | GND      |

| K12      | VSS                                                 | _   | GND      |

| K13      | VSS                                                 | _   | GND      |

| K14      | VSS                                                 | _   | GND      |

| K15      | VSS                                                 | _   | GND      |

| K16      | _                                                   | _   | _        |

| K17      | VDDO_DDR2                                           | _   | PWR      |

| K18      | VDD_REF                                             | _   | PWR      |

| K19      | VDD_REF                                             | _   | PWR      |

| K20      | DDR_DATA_13                                         | В   | MEMIO    |

| K21      | DDR_DATA_10                                         | В   | MEMIO    |

| K22      | DDR_DATA_8                                          | В   | MEMIO    |

| L1       | GMII0_RXD7                                          | I   | I        |

| L2       | GMII0_RXD3 /RGMII0_RXD3 /MII0_RXD3 /RMII0_PHY_SPEED | I   | I        |

| L3       | GMII0_RXD6                                          | I   | I        |

| L4       | VSS                                                 | _   | GND      |

| L5       | VSS                                                 | _   | GND      |

| L6       | VDD                                                 | _   | PWR      |

| L7       | _                                                   | _   | _        |

| L8       | VSS                                                 | _   | GND      |

| L9       | VSS                                                 | _   | GND      |

| L10      | VSS                                                 | _   | GND      |

| L11      | VSS                                                 | _   | GND      |

| L12      | VSS                                                 | _   | GND      |

| L13      | VSS                                                 | _   | GND      |

| L14      | VSS                                                 | _   | GND      |

| L15      | VSS                                                 | _   | GND      |

| L16      | _                                                   | _   | _        |

| L17      | VDD                                                 |     | PWR      |

| L18      | VSS                                                 | _   | GND      |

| L19      | VSS                                                 | _   | GND      |

| L20      | DDR_DATA_15                                         | В   | MEMIO    |

| L21      | DDR_DQS_1_N                                         | В   | MEMIODIF |

| L22      | DDR_DQS_1                                           | В   | MEMIODIF |

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                                    | Dir | I/O Type |

|----------|------------------------------------------------------------------|-----|----------|

| M1       | GMII0_RX_DV /<br>RGMII0_RX_CTL /<br>MII0_RX_DV /<br>RMII0_CRS_DV | I   | I        |

| M2       | GMII0_RX_ER /<br>MII0_RX_ER                                      | I   | Ι        |

| M3       | GMII0_RX_CLK /<br>RGMII0_RXC /<br>MII0_RX_CLK /<br>RMII0_CLK     | I   | I        |

| M4       | VDDO_ETH0                                                        | _   | PWR      |

| M5       | VDDO_ETH0                                                        | _   | PWR      |

| M6       | VDDO_ETH0                                                        | _   | PWR      |

| M7       | _                                                                | _   | _        |

| M8       | VSS                                                              | _   | GND      |

| M9       | VSS                                                              | _   | GND      |

| M10      | VSS                                                              | _   | GND      |

| M11      | VSS                                                              | _   | GND      |

| M12      | VSS                                                              | _   | GND      |

| M13      | VSS                                                              | _   | GND      |

| M14      | VSS                                                              | _   | GND      |

| M15      | VSS                                                              | _   | GND      |

| M16      | _                                                                | _   | _        |

| M17      | VDDO_DDR2                                                        | _   | PWR      |

| M18      | VDDO_DDR2                                                        | _   | PWR      |

| M19      | VDDO_DDR2                                                        | _   | PWR      |

| M20      | DDR_DM_1                                                         | 0   | MEMIO    |

| M21      | DDR_DATA_14                                                      | В   | MEMIO    |

| M22      | DDR_DATA_9                                                       | В   | MEMIO    |

| N1       | GMII0_CRS /<br>MII0_CRS                                          | I   | I        |

| N2       | GMII0_REFCLK/RGMII0_REFCLK/<br>MII0_REFCLK/<br>RMII0_REFCLK      | 0   | Ot16     |

| N3       | GMII0_COL/MII0_COL                                               | I   | I        |

| N4       | VSS                                                              | _   | GND      |

| N5       | VSS                                                              | _   | GND      |

| N6       | VDD                                                              | _   | PWR      |

| N7       | _                                                                | _   | _        |

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                        | Dir | I/O Type |  |  |  |

|----------|------------------------------------------------------|-----|----------|--|--|--|

| N8       | VSS                                                  | _   | GND      |  |  |  |

| N9       | VSS                                                  | _   | GND      |  |  |  |

| N10      | VSS                                                  | _   | GND      |  |  |  |

| N11      | VSS                                                  | _   | GND      |  |  |  |

| N12      | VSS                                                  | _   | GND      |  |  |  |

| N13      | VSS                                                  | _   | GND      |  |  |  |

| N14      | VSS                                                  | _   | GND      |  |  |  |

| N15      | VSS                                                  | _   | GND      |  |  |  |

| N16      | _                                                    | _   | _        |  |  |  |

| N17      | VDD                                                  | _   | PWR      |  |  |  |

| N18      | VSS                                                  | _   | GND      |  |  |  |

| N19      | VSS                                                  | _   | GND      |  |  |  |

| N20      | DDR_DATA_11                                          | В   | MEMIO    |  |  |  |

| N21      | DDR_DATA_12                                          | В   | MEMIO    |  |  |  |

| N22      | DDR_CLK_N                                            | 0   | MEMIODIF |  |  |  |

| P1       | GMII0_TXER /<br>RGMII0_TX_CTL /MII0_TX_ER            | 0   | Ot16     |  |  |  |

| P2       | GMII0_TX_CLK /<br>MII0_TX_CLK                        | I   | I        |  |  |  |

| Р3       | GMII0_TX_EN /RGMII0_TXC /<br>MII0_TX_EN /RMII0_TX_EN | 0   | Ot16     |  |  |  |

| P4       | VDDO_ETH0                                            | _   | PWR      |  |  |  |

| P5       | VDDO_ETH0                                            | _   | PWR      |  |  |  |

| P6       | VDDO_ETH0                                            | _   | PWR      |  |  |  |

| P7       | _                                                    | _   | _        |  |  |  |

| P8       | VSS                                                  | _   | GND      |  |  |  |

| P9       | VSS                                                  | _   | GND      |  |  |  |

| P10      | VSS                                                  | _   | GND      |  |  |  |

| P11      | VSS                                                  | _   | GND      |  |  |  |

| P12      | VSS                                                  | _   | GND      |  |  |  |

| P13      | VSS                                                  | _   | GND      |  |  |  |

| P14      | VSS                                                  | _   | GND      |  |  |  |

| P15      | vss —                                                |     |          |  |  |  |

| P16      | _                                                    | _   | _        |  |  |  |

| P17      | VDDO_DDR2                                            | _   | PWR      |  |  |  |

| P18      | VDDO_DDR2                                            | _   | PWR      |  |  |  |

| P19      | VDDO_DDR2                                            | _   | PWR      |  |  |  |

QorlQ LS10xMA Data sheet, Rev 1

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                      | Dir | I/O Type |  |  |

|----------|----------------------------------------------------|-----|----------|--|--|

| P20      | DDR_RAS_N                                          | 0   | MEMIO    |  |  |

| P21      | DDR_ODT                                            | 0   | MEMIO    |  |  |

| P22      | DDR_CLK                                            | 0   | MEMIODIF |  |  |

| R1       | GMII0_TXD4                                         | 0   | Ot16     |  |  |

| R2       | GMII0_TXD0 /RGMII0_TXD0 /<br>MII0_TXD0 /RMII0_TXD0 | 0   | Ot16     |  |  |

| R3       | GMII0_TXD5                                         | 0   | Ot16     |  |  |

| R4       | VSS                                                | _   | GND      |  |  |

| R5       | VSS                                                | _   | GND      |  |  |

| R6       | VDD                                                | _   | PWR      |  |  |

| R7       | _                                                  | _   | _        |  |  |

| R8       | VSS                                                | _   | GND      |  |  |

| R9       | VSS                                                | _   | GND      |  |  |

| R10      | VSS                                                | _   | GND      |  |  |

| R11      | VSS                                                | _   | GND      |  |  |

| R12      | VSS                                                | _   | GND      |  |  |

| R13      | VSS                                                | _   | GND      |  |  |

| R14      | VSS                                                | _   | GND      |  |  |

| R15      | VSS                                                | _   | GND      |  |  |

| R16      | _                                                  | _   | _        |  |  |

| R17      | VDD                                                | _   | PWR      |  |  |

| R18      | VSS                                                | _   | GND      |  |  |

| R19      | VSS                                                | _   | GND      |  |  |

| R20      | DDR_CAS_N                                          | 0   | MEMIO    |  |  |

| R21      | DDR_CLKE                                           | 0   | MEMIOPL  |  |  |

| R22      | DDR_WE_N                                           | 0   | MEMIO    |  |  |

| T1       | GMII0_TXD1/RGMII0_TXD1/<br>MII0_TXD1 /RMII0_TXD1   | 0   | Ot16     |  |  |

| T2       | GMII0_TXD6                                         | 0   | Ot16     |  |  |

| Т3       | GMII0_TXD2/RGMII0_TXD2/<br>MII0_TXD2/RMII0_RX_ER   | В   | I/Ot16   |  |  |

| T4       | VDDO_ETH1                                          | _   | PWR      |  |  |

| T5       | VDDO_ETH1                                          | _   | PWR      |  |  |

| Т6       | VDDO_ETH1                                          | _   | PWR      |  |  |

| T7       |                                                    |     |          |  |  |

| Т8       | _                                                  | _   | _        |  |  |

| Т9       | _                                                  | _   | _        |  |  |

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                       | Dir | I/O Type |  |

|----------|-----------------------------------------------------|-----|----------|--|

| T10      | _                                                   | _   | _        |  |

| T11      | _                                                   | _   | _        |  |

| T12      | _                                                   | _   | _        |  |

| T13      | _                                                   | _   | _        |  |

| T14      | _                                                   | _   | _        |  |

| T15      | _                                                   | _   | _        |  |

| T16      | _                                                   | _   | _        |  |

| T17      | VDDO_DDR2                                           | _   | PWR      |  |

| T18      | VDDO_DDR2                                           | _   | PWR      |  |

| T19      | VDDO_DDR2                                           | _   | PWR      |  |

| T20      | DDR_A_10                                            | О   | MEMIO    |  |

| T21      | DDR_BA_0                                            | 0   | MEMIO    |  |

| T22      | DDR_CS0_N                                           | О   | MEMIO    |  |

| U1       | GMII0_TXD7                                          | О   | Ot16     |  |

| U2       | GMII0_TXD3/RGMII0_TXD3/<br>MII0_TXD3/RMII0_PHY_LINK | В   | I/Ot16   |  |

| U3       | GMII0_GTX_CLK                                       | О   | Ot16     |  |

| U4       | VSS                                                 | _   | GND      |  |

| U5       | VSS                                                 | _   | GND      |  |

| U6       | VSS                                                 | _   | GND      |  |

| U7       | VDD                                                 | _   | PWR      |  |

| U8       | VDDO_ETH1                                           | _   | VDD      |  |

| U9       | VDD                                                 | _   | PWR      |  |

| U10      | VDDO_PCIE_2.5                                       | _   | PWR      |  |

| U11      | VSS                                                 | _   | GND      |  |

| U12      | VDD_PCIE_1                                          | _   | PWR      |  |

| U13      | VDDO_DDR2                                           | _   | PWR      |  |

| U14      | VDD                                                 | _   | PWR      |  |

| U15      | VDDO_DDR2                                           | _   | PWR      |  |

| U16      | VDD                                                 | _   | PWR      |  |

| U17      | VSS                                                 | _   | GND      |  |

| U18      | VSS                                                 | _   | GND      |  |

| U19      | VSS                                                 | _   | GND      |  |

| U20      | DDR_A_6                                             | 0   | MEMIO    |  |

| U21      | DDR_A_3                                             | 0   | MEMIO    |  |

| U22      | DDR_A_2                                             | 0   | MEMIO    |  |

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                       | Dir | I/O Type |  |  |

|----------|-----------------------------------------------------|-----|----------|--|--|

| V1       | GEM_MDC                                             | О   | Ots8     |  |  |

| V2       | GEM_MDIO                                            | В   | I/Ots8   |  |  |

| V3       | GMII1_GTX_CLK                                       | О   | Ot16     |  |  |

| V4       | VSS                                                 | _   | GND      |  |  |

| V5       | VSS                                                 | _   | GND      |  |  |

| V6       | VSS                                                 | _   | GND      |  |  |

| V7       | VSS                                                 | _   | GND      |  |  |

| V8       | VDDO_ETH1                                           | _   | PWR      |  |  |

| V9       | VSS                                                 | _   | GND      |  |  |

| V10      | VSS                                                 | _   | GND      |  |  |

| V11      | VSS                                                 | _   | GND      |  |  |

| V12      | VSS                                                 | _   | GND      |  |  |

| V13      | VDDO_DDR2                                           | _   | PWR      |  |  |

| V14      | VSS                                                 | _   | GND      |  |  |

| V15      | VDD_REF                                             | _   | _        |  |  |

| V16      | VSS                                                 | _   | GND      |  |  |

| V17      | VSS                                                 | _   | GND      |  |  |

| V18      | VSS                                                 | _   | GND      |  |  |

| V19      | VSS                                                 | _   | GND      |  |  |

| V20      | DDR_A_7                                             | 0   | MEMIO    |  |  |

| V21      | DDR_A_11                                            | 0   | MEMIO    |  |  |

| V22      | DDR_A_13                                            | 0   | MEMIO    |  |  |

| W1       | GMII1_TXD3/RGMII1_TXD3/<br>MII1_TXD3/RMII1_PHY_LINK | В   | I/Ot16   |  |  |

| W2       | GMII1_TXD7                                          | 0   | Ot16     |  |  |

| W3       | GMII1_TX_EN/RGMII1_TXC/<br>MII1_TX_EN/RMII1_TX_EN   | 0   | Ot16     |  |  |

| W4       | VSS                                                 | _   | GND      |  |  |

| W5       | VSS                                                 | _   | GND      |  |  |

| W6       | VSS                                                 | _   | GND      |  |  |

| W7       | VSS                                                 | _   | GND      |  |  |

| W8       | VDDO_ETH1                                           | _   | PWR      |  |  |

| W9       | VSS                                                 | _   | GND      |  |  |

| W10      | PCIE_RESREF                                         | _   | PCIE     |  |  |

| W11      | PCIE1_HSI_P I                                       |     |          |  |  |

| W12      | PCIE0_HSI_P                                         | I   | PCIE     |  |  |

| W13      | VDDO_DDR2                                           | _   | PWR      |  |  |

#### QorlQ LS10xMA Data sheet, Rev 1

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                                   | Dir    | I/O Type |  |  |  |  |

|----------|-----------------------------------------------------------------|--------|----------|--|--|--|--|

| W14      | VSS                                                             | _      | GND      |  |  |  |  |

| W15      | VDD_REF                                                         | _      | PWR      |  |  |  |  |

| W16      | VSS                                                             | _      | GND      |  |  |  |  |

| W17      | VSS                                                             | _      | GND      |  |  |  |  |

| W18      | VSS                                                             | _      | GND      |  |  |  |  |

| W19      | VSS                                                             | _      | GND      |  |  |  |  |

| W20      | DDR_A_8                                                         | 0      | MEMIO    |  |  |  |  |

| W21      | DDR_A_12                                                        | 0      | MEMIO    |  |  |  |  |

| W22      | DDR_A_9                                                         | 0      | MEMIO    |  |  |  |  |

| Y1       | GMII1_TXD2/RGMII1_TXD2 /<br>MII1_TXD2/RMII1_RX_ER               | В      | I/Ot16   |  |  |  |  |

| Y2       | GMII1_TXD5                                                      | 0      | Ot16     |  |  |  |  |

| Y3       | GMII1_TX_CLK/MII1_TX_CLK                                        | I      | I        |  |  |  |  |

| Y4       | GMII1_REFCLK/RGMII1_REFCLK/<br>MII1_REFCLK/<br>RMII1_REFCLK     | О      | Ot16     |  |  |  |  |

| Y5       | GMII1_RX_ER /<br>MII1_RX_ER                                     | I      | I        |  |  |  |  |

| Y6       | GMII1_RXD3 /<br>RGMII1_RXD3 /<br>MII1_RXD3 /<br>RMII1_PHY_SPEED | I      | I        |  |  |  |  |

| Y7       | GMII1_RXD4                                                      | I      | I        |  |  |  |  |

| Y8       | TM_PLL_XO                                                       | 0      | OSCL     |  |  |  |  |

| Y9       | VDD_PLL_2                                                       | _      | PWR      |  |  |  |  |

| Y10      | VSS                                                             | _      | GND      |  |  |  |  |

| Y11      | PCIE1_HSI_M                                                     | I      | PCIE     |  |  |  |  |

| Y12      | PCIE0_HSI_M                                                     | I      | PCIE     |  |  |  |  |

| Y13      | VSS                                                             | _      | GND      |  |  |  |  |

| Y14      | DDR_DM_3                                                        | 0      | MEMEIO   |  |  |  |  |

| Y15      | DDR_DATA_31                                                     | В      | MEMEIO   |  |  |  |  |

| Y16      | DDR_DATA_29                                                     | В      | MEMEIO   |  |  |  |  |

| Y17      | DDR_DATA_17                                                     | MEMEIO |          |  |  |  |  |

| Y18      | DDR_DQS_2 B MEI                                                 |        |          |  |  |  |  |

| Y19      | DDR_A_14 O MEM                                                  |        |          |  |  |  |  |

| Y20      | DDR_A_0 O MEM                                                   |        |          |  |  |  |  |

| Y21      | DDR_A_5 O MEMIO                                                 |        |          |  |  |  |  |

| Y22      | DDR_A_4                                                         | 0      | MEMIO    |  |  |  |  |

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                              | Dir | I/O Type |  |  |

|----------|------------------------------------------------------------|-----|----------|--|--|

| AA1      | GMII1_TXD6                                                 | О   | Ot16     |  |  |

| AA2      | GMII1_TXD0 /<br>RGMII1_TXD0 /<br>MII1_TXD0 /<br>RMII1_TXD0 | 0   | Ot16     |  |  |

| AA3      | GMII1_COL /<br>MII1_COL                                    | I   | I        |  |  |

| AA4      | GMII1_CRS /<br>MII1_CRS                                    | I   | I        |  |  |

| AA5      | GMII1_RX_CLK/RGMII1_RXC /MII1_RX_CLK/RMII1_CLK             | I   | I        |  |  |

| AA6      | GMII1_RXD6                                                 | I   | I        |  |  |

| AA7      | GMII1_RXD1/RGMII1_RXD1 /<br>MII1_RXD1/RMII1_RXD1           | I   | I        |  |  |

| AA8      | TM_PLL_XI                                                  | I   | OSCL     |  |  |

| AA9      | VDD_PLL_1                                                  | _   | PWR      |  |  |

| AA10     | PCIE_REFCLK_M                                              | I   | PCIE     |  |  |

| AA11     | PCIE1_HSO_P                                                | 0   | PCIE     |  |  |

| AA12     | PCIE0_HSO_P                                                | 0   | CIE      |  |  |

| AA13     | DDR_DATA_27                                                | В   | MEMIO    |  |  |

| AA14     | DDR_DATA_30                                                | В   | MEMIO    |  |  |

| AA15     | DDR_DQS_3_N                                                | В   | MEMIODIF |  |  |

| AA16     | DDR_DATA_26 B N                                            |     |          |  |  |

| AA17     | DDR_DATA_19 B MI                                           |     | MEMIO    |  |  |

| AA18     | DDR_DM_2                                                   | 0   | MEMIO    |  |  |

| AA19     | DDR_DATA_23                                                | В   | MEMIO    |  |  |

| AA20     | DDR_DATA_18                                                | В   | MEMIO    |  |  |

| AA21     | DDR_BA_1                                                   | 0   | MEMIO    |  |  |

| AA22     | DDR_A_1                                                    | 0   | MEMIO    |  |  |

| AB1      | GMII1_TXD1/RGMII1_TXD1/<br>MII1_TXD1/RMII1_TXD1            | 0   | Ot16     |  |  |

| AB2      | GMII1_TXD4                                                 | О   | Ot16     |  |  |

| AB3      | GMII1_TX_ER/RGMII1_TX_CTL/ O Ot16  MII1_TX_ER              |     |          |  |  |

| AB4      | GMII1_RX_DV /RGMII1_RX_CTL / I  MII1_RX_DV /  RMII1_CRS_DV |     |          |  |  |

| AB5      | GMII1_RXD7                                                 | I   | I        |  |  |

Table 3-1 Landing List (continued)

| Location | Signal Symbol                                                 | Dir | I/O Type |  |  |

|----------|---------------------------------------------------------------|-----|----------|--|--|

| AB6      | GMII1_RXD2 /<br>RGMII1_RXD2 /<br>MII1_RXD2 /<br>RMII1_PHY_DPX | I   | I        |  |  |

| AB7      | GMII1_RXD5                                                    | I   | I        |  |  |

| AB8      | GMII1_RXD0 /RGMII1_RXD0/<br>MII1_RXD0 /RMII1_RXD0             | I   | I        |  |  |

| AB9      | VDD_PLL_0                                                     | _   | PWR      |  |  |

| AB10     | PCIE_REFCLK_P                                                 | I   | PCIE     |  |  |

| AB11     | PCIE1_HSO_M                                                   | O   | PCIE     |  |  |

| AB12     | PCIE0_HSO_M                                                   | О   | PCIE     |  |  |

| AB13     | DDR_DATA_28                                                   | В   | MEMIO    |  |  |

| AB14     | DDR_DATA_25                                                   | В   | MEMIO    |  |  |

| AB15     | DDR_DQS_3                                                     | В   | MEMIODIF |  |  |

| AB16     | DDR_DATA_24                                                   | В   | MEMIO    |  |  |

| AB17     | DDR_DATA_20                                                   | В   | MEMIO    |  |  |

| AB18     | DDR_DATA_22                                                   | В   | MEMIO    |  |  |

| AB19     | DDR_DQS_2_N                                                   | В   | MEMIODIF |  |  |

| AB20     | DDR_DATA_16                                                   | В   | MEMIO    |  |  |

| AB21     | DDR_DATA_21 B ME                                              |     |          |  |  |

| AB22     | DDR_BA_2                                                      | О   | MEMIO    |  |  |

## 3.2 Design Notes

The LS10xMA device requires four DC power levels. Analog power and ground connections to PCIe, USB and PLL pins require separate treatment. For details on power sequencing, refer to Section 19.1 Power Supply Sequencing.

No Connect pins must remain unconnected. Pull Low pins must be connected to ground.

#### **Unused Interface Termination Recommendations**

In case the following interfaces/signals are unused, leave them unconnected.

- I<sup>2</sup>C, SPI, UART, Timer, GPIO, and JTAG

- EXP. Unused signals can be left unconnected.

- DDR 16 bit: The most significant bits, such as DDR\_DM[3:2], DDR\_DQ[31:16], DDR\_DQS[3:2], and DDR\_DQS#[3:2] should be left open.

- TDM—If TDM port is unused then all signals could be left unconnected, and block should not be taken out of reset (software configuration).

- GEM—If GEM port is unused then all signals could be left unconnected, and block should not be taken out of reset (software configuration).

- Miscellaneous

TM\_EXT\_RESET, GEM0\_REFCLK, GEM1\_REFCLK. Unused signals can be left unconnected.

#### PCle and USB

- Keep all the power connection and power to spec levels. Use software to put unused lanes to power down or sleep mode to save power.

- Float all unused I/O pins, except PCIE\_RESREF or USB\_REF pins that still need to be connected to

external resistors. But the Resistor value and precision can differ from the exact spec if it can lower the

cost. If the resistor is shared with any used lane or channel, then it still needs to be exactly as specified in

value and precision.

NOTE:

The Freescale LS10xMA Device is a multi-core System-on-Chip (SOC) device operating at very high frequencies. Appropriate power supply and layout considerations are required to guarantee optimum performance.

Freescale provides schematic and layout review. Freescale **HIGHLY RECOMMENDS** customers submit their designs to Freescale for a complete and confidential review.

## 3.3 Input/Output PAD Types

NOTE:

Freescale provides IBIS files for LS10xMA devices. Contact the FAE or sales representative for more details.

Table 3-2 gives the I/O pad descriptions.

Table 3-2 I/O Type Descriptions

| I/O Type  | Description                                                                       |  |  |  |

|-----------|-----------------------------------------------------------------------------------|--|--|--|

| USBDATA   | USB 2.0 compliant analog data                                                     |  |  |  |

| USBANALOG | USB 2.0 compliant analog                                                          |  |  |  |

| PCIE      | PCI Express compliant                                                             |  |  |  |

| I         | Digital input                                                                     |  |  |  |

| Id/Ots8   | Digital input, pull down/ Digital output, 3-state, Slew rate, 8mA                 |  |  |  |

| Ihd/Ots8  | Digital input with hysteresis, pull down/ Digital output, 3-state, Slew rate, 8mA |  |  |  |

| Ihu/Ots8  | Digital input with hysteresis, pull up / Digital output, 3-state, Slew rate, 8mA  |  |  |  |

| Ihu/Ots16 | Digital input with hysteresis, pull up / Digital output, 3-state, Slew rate, 16mA |  |  |  |

| I/Ot8     | Digital input / Digital output, 3-state, 8mA                                      |  |  |  |

| Ih/Ot8    | Digital input with hysteresis / Digital output, 3-state, 8mA                      |  |  |  |

| I/Ot16    | Digital input / Digital output, 3-State, 16mA                                     |  |  |  |

| Ih/Ot16   | Digital input with hysteresis / Digital output, 3-state, 16mA                     |  |  |  |

| I/Ots8    | Digital input / Digital output, 3-state, Slew rate, 8mA                           |  |  |  |

| Id        | Digital input, pull down                                                          |  |  |  |

| Ihd       | Digital input with hysteresis, pull down                                          |  |  |  |

| Iu        | Digital input, pull up                                                            |  |  |  |

QorlQ LS10xMA Data sheet, Rev 1

Table 3-2 I/O Type Descriptions (continued)

| I/O Type | Description                                        |  |  |  |

|----------|----------------------------------------------------|--|--|--|

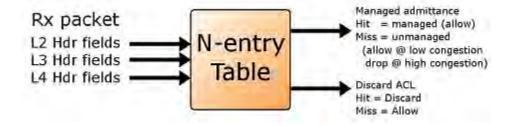

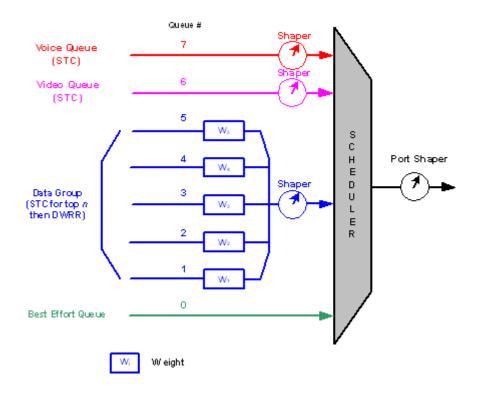

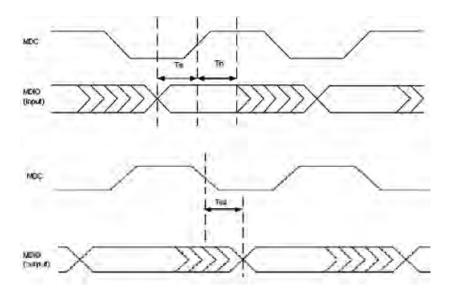

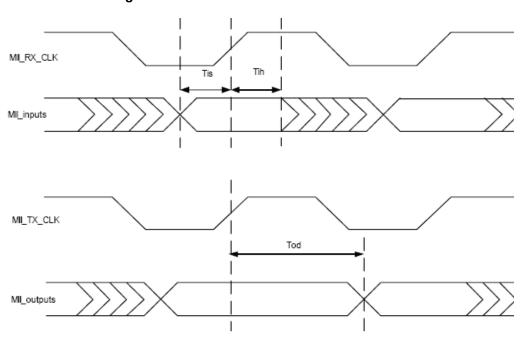

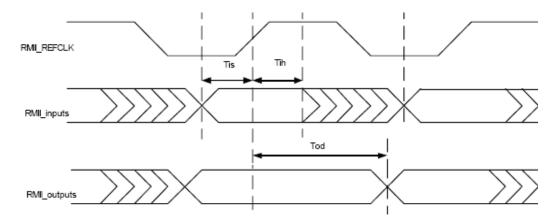

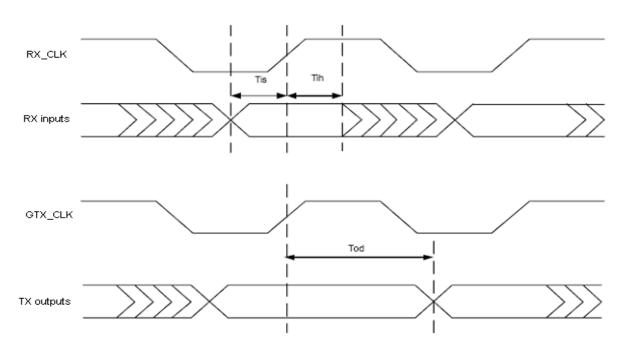

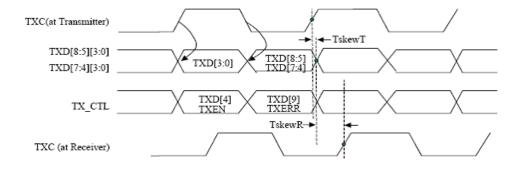

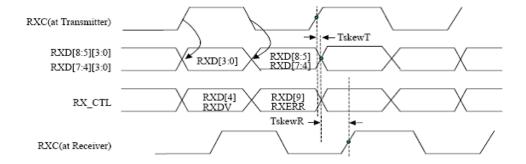

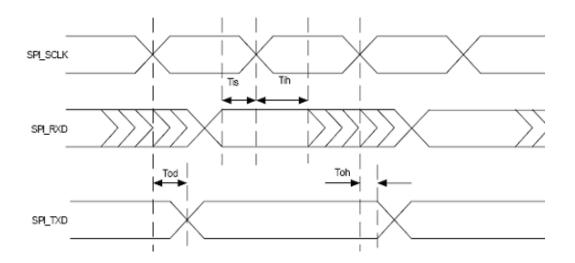

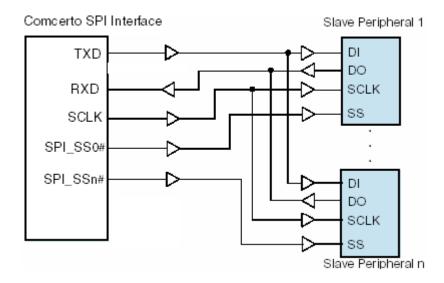

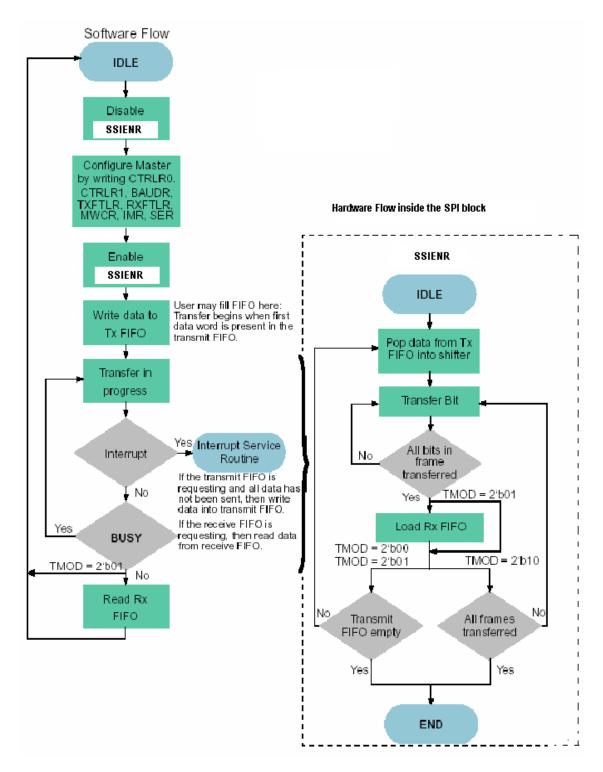

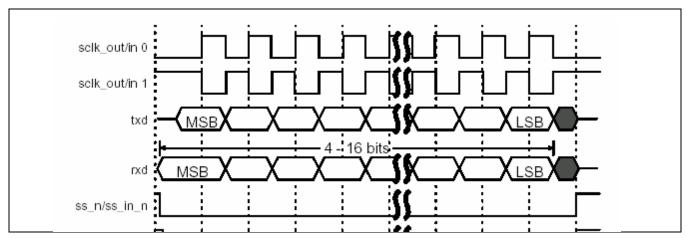

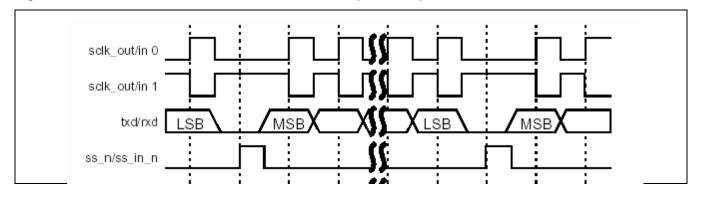

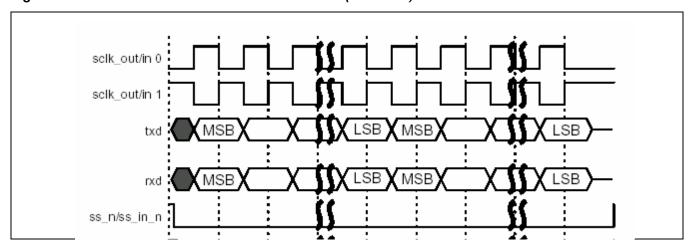

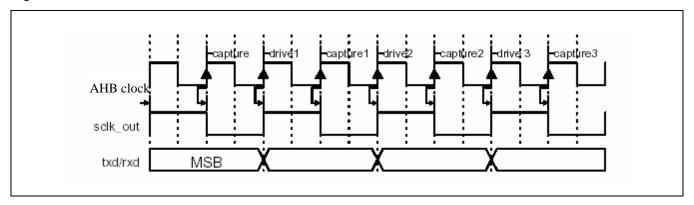

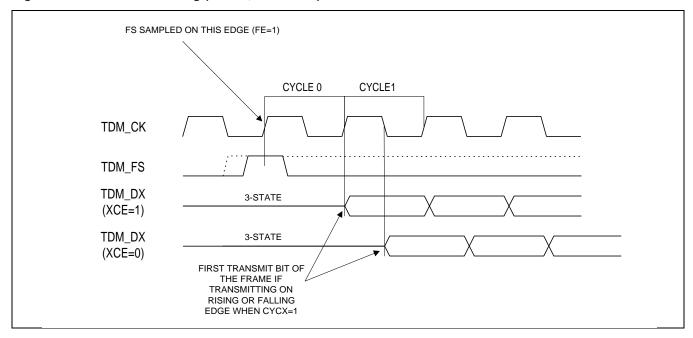

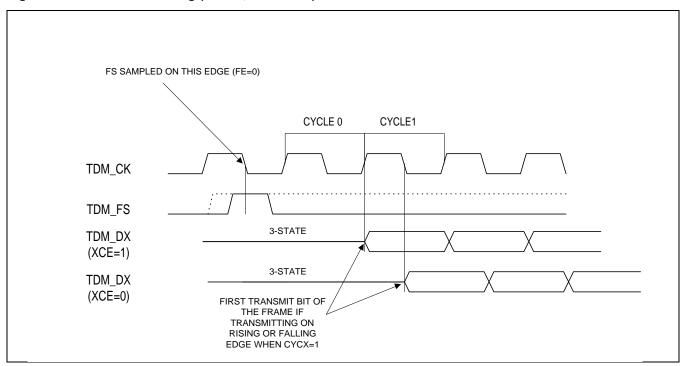

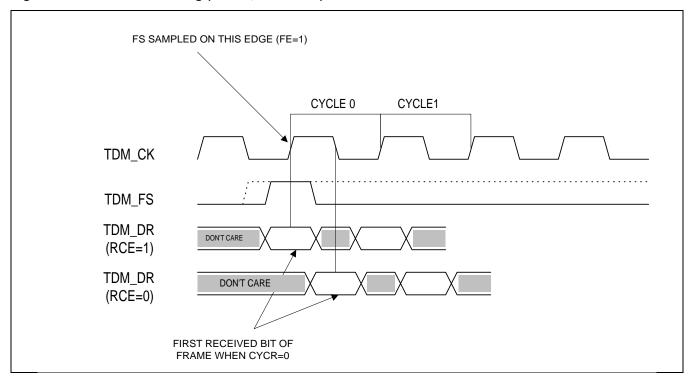

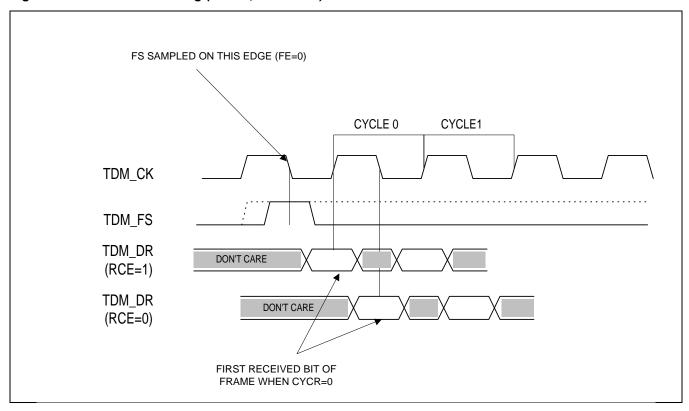

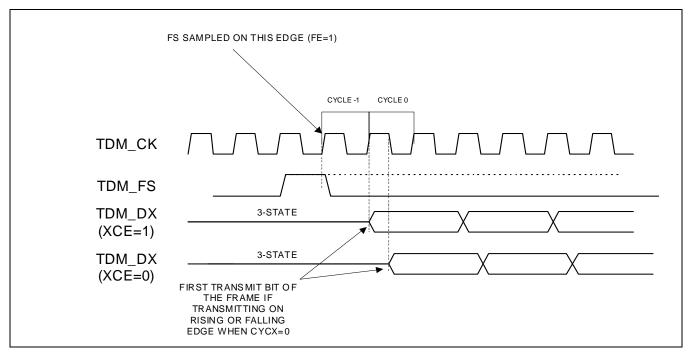

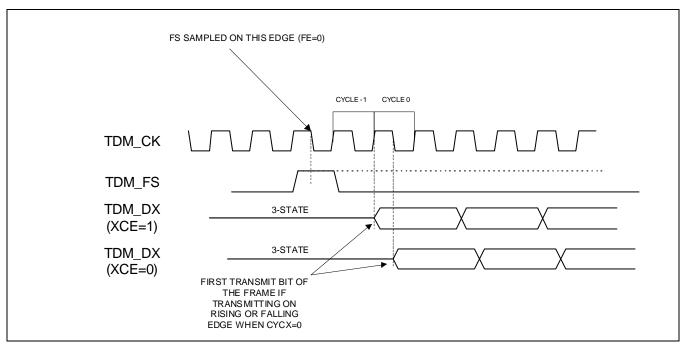

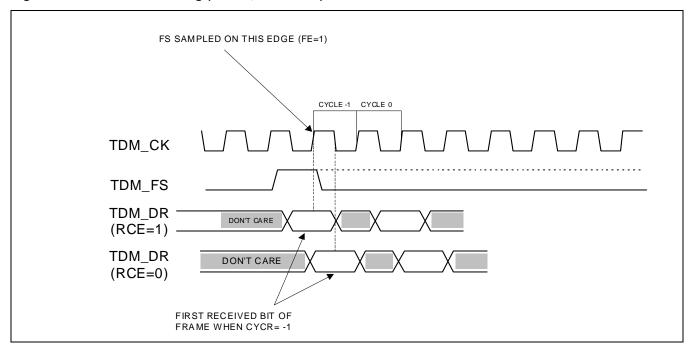

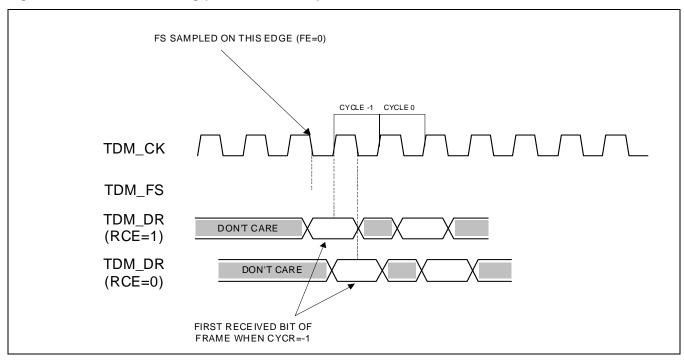

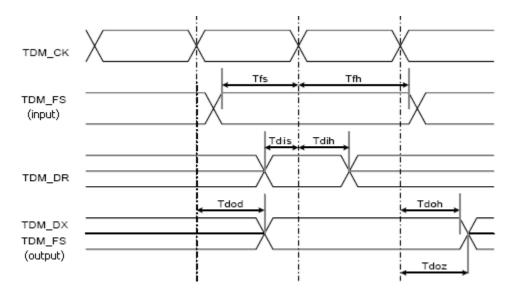

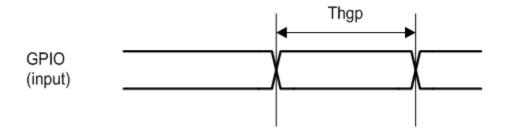

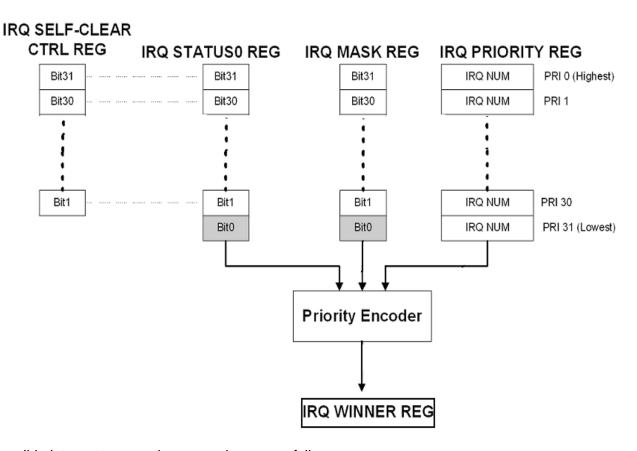

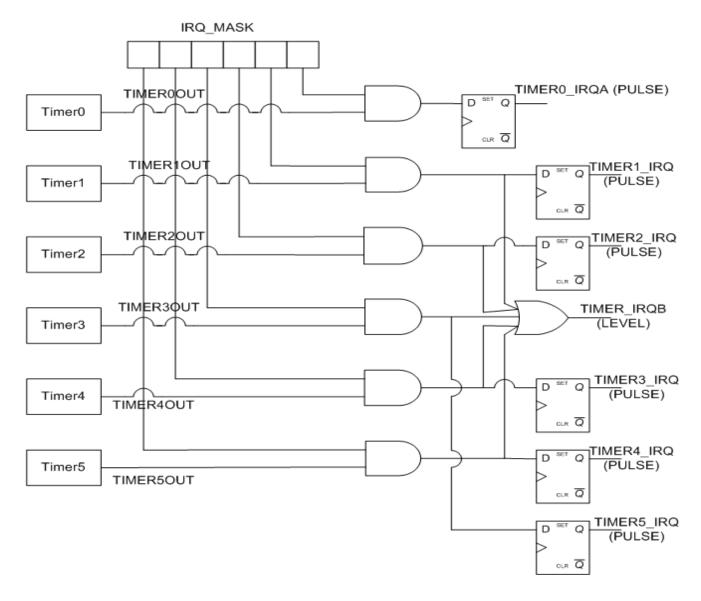

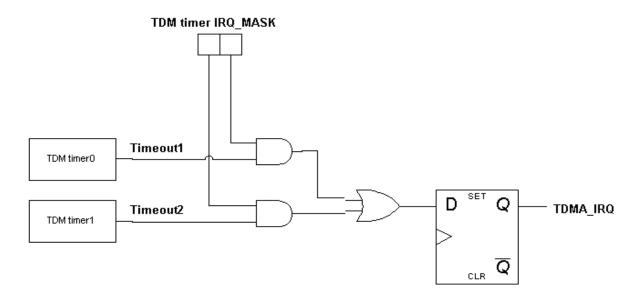

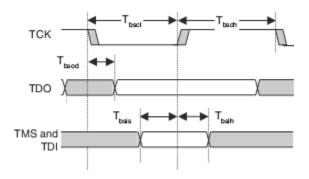

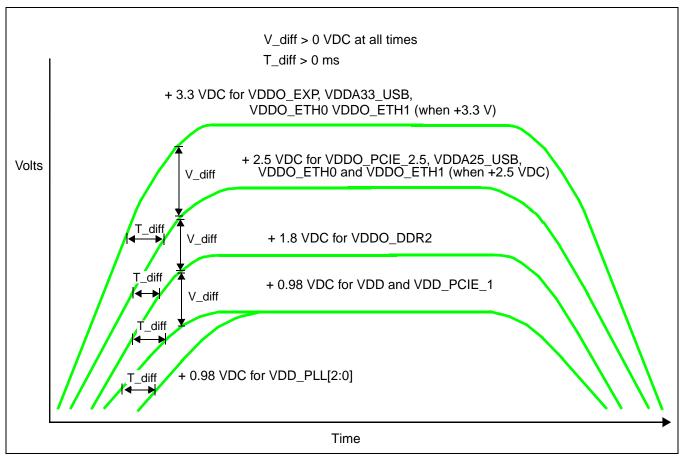

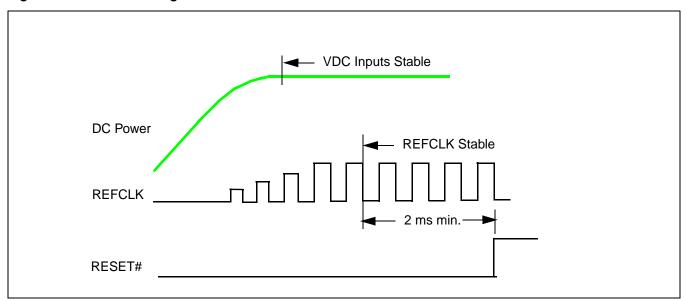

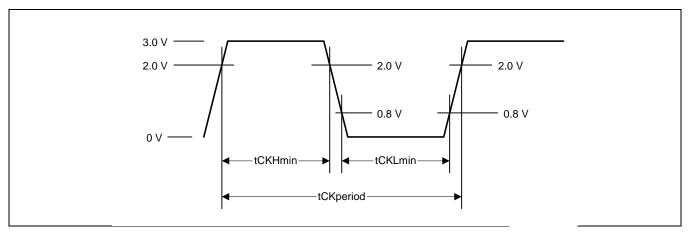

| Ihu      | Digital input with hysteresis, pull up             |  |  |  |