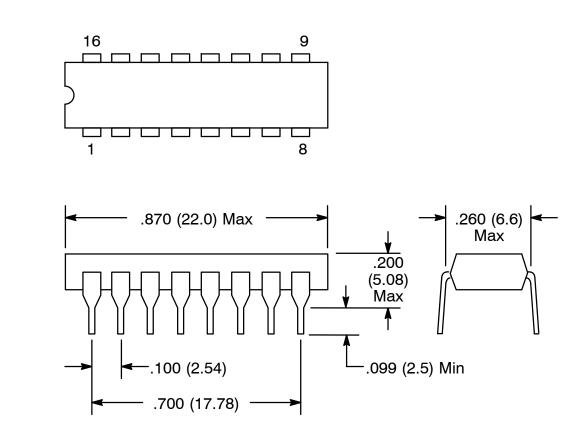

## NTE4164 Integrated Circuit NMOS, 64K Dynamic RAM, 150ns 16-Lead DIP Type Package

### **Description:**

The NTE4164 is a high speed Dynamic Random Access Memory (DRAM) in a 16-Lead DIP type package organized as 65,536 words of one bit each.

Refresh period is extended to 4 milliseconds, and during this period each of the 256 rows must be strobed with  $\overline{RAS}$  in order to retain data.  $\overline{CAS}$  can remain high during the refresh sequence to conserve power.

All inputs and outputs, including clocks, are compatible with Series 74TTL. All address lines and data-in are latched on chip to simplify system design. Data-out is unlatched to allow greater system flexibility. Pin1 has no internal connections to allow compatibility with other 64K RAMs using this pin for an additional function.

#### Features:

- 65,536 x 1 Organization

- Single +5V Supply (10% Tolerance)

- Upward Pin Compatible with 4116 (16K Dynamic RAM)

- Max Access Time from RAS: Less than 150ns

- Min Cycle Time (Read or Write): Less than 260ns

- Long Refresh Period: 4 milliseconds

- Low Refresh Overhead Time: As Low As 1.8% of Total Refresh Period

- All Inputs, Outputs, Clocks Fully TTL Compatible

- 3-State Unlatched Outputs

- Page–Mode Operation for Faster Access

- Low Power Dissipation:

Operating .... 135mW (Typ) Standby ..... 17.5mW (Typ)

###

Note 1. All voltage values in this data sheet are with respect to  $V_{SS}$ .

### **Recommended Operating Conditions:**

| Parameter                     | Symbol               | Test Conditions | Min | Тур | Max                   | Unit |

|-------------------------------|----------------------|-----------------|-----|-----|-----------------------|------|

| Supply Voltage                | $V_{DD}$             |                 | 4.5 | 5.0 | 5.5                   | V    |

|                               | $V_{SS}$             |                 | -   | 0   | _                     | V    |

| High-Level Input Voltage      | V <sub>IH</sub>      |                 | 2.4 | _   | V <sub>DD</sub> +00.3 | V    |

| Low-Level Input Voltage       | $V_{IL}$             |                 | -1  | _   | 0.8                   | V    |

| Refresh Time                  | t <sub>refresh</sub> |                 | -   | _   | 4                     | ms   |

| Operating Ambient Temperature | T <sub>A</sub>       |                 | 0   | _   | +70                   | °C   |

# <u>Electricall Characteristics:</u> (Over full ranges of recommended operating conditions unless otherwise specified)

| Parameter                                               | Symbol           | Test Conditions                                  | Min | Тур | Max | Unit |

|---------------------------------------------------------|------------------|--------------------------------------------------|-----|-----|-----|------|

| High-Level Outpu Voltage                                | V <sub>OH</sub>  | I <sub>OH</sub> = -5mA                           | 2.4 | -   | _   | V    |

| Low-Level Output Voltage                                | V <sub>OL</sub>  | I <sub>OL</sub> = 4.2mA                          | 1   | _   | 0.4 | V    |

| Input Current (Leakage)                                 | I <sub>I</sub>   | V <sub>I</sub> = 0V to 5.8V, All Other Pins = 0V | -10 | -   | +10 | μΑ   |

| Output Current (Leakage)                                | Ι <sub>Ο</sub>   | V <sub>O</sub> = 0.4V to 5.5V, CAS High          | -10 | -   | +10 | μΑ   |

| Average Operating Current during<br>Read or Write Cycle | I <sub>DD1</sub> | Minimum Cycle Time                               | -   | 40  | 48  | mA   |

| Standby Current                                         | I <sub>DD2</sub> | After 1 Memory Cycle, RAS and CAS High           | -   | 3.5 | 5.0 | mA   |

| Average Refresh Current                                 | I <sub>DD3</sub> | Minimum Cycle Time, RAS Low, CAS High            | -   | 28  | 40  | mA   |

| Average Page-Mode Current                               | I <sub>DD4</sub> | Minimum Cycle Time, RAS Low, CAS Cycling         | ı   | 28  | 40  | mA   |

### <u>Capacitance:</u> $(T_A = +25^{\circ}C, V_{DD} = 5V, f = 1MHz unless otherwise specified)$

| Parameter                              | Symbol             | Test Conditions | Min | Тур | Max | Unit |

|----------------------------------------|--------------------|-----------------|-----|-----|-----|------|

| Input Capacitance, Address Inputs      | C <sub>I(A)</sub>  |                 | _   | 4   | 5   | pF   |

| Input Capacitance, Data Inputs         | C <sub>I(D)</sub>  |                 | -   | 4   | 5   | pF   |

| Input Capacitance, Strobe Inputs       | C <sub>I(RC)</sub> |                 | -   | 6   | 8   | pF   |

| Input Capacitance, Write Enable Inputs | C <sub>I(W)</sub>  |                 | -   | 6   | 8   | pF   |

| Output Capacitance                     | Co                 |                 | ı   | 5   | 6   | pF   |

## $\underline{\textbf{Switching Characteristics:}} \ \ (T_{A} = +25^{\circ}\text{C}, \ V_{DD} = 5\text{V}, \ C_{L} = 100 \text{pF unless otherwise specified})$

| Parameter                              | Symbol           | Test Conditions                                         | Min | Тур | Max | Unit |

|----------------------------------------|------------------|---------------------------------------------------------|-----|-----|-----|------|

| Access Time from Column Address Strobe | t <sub>CAC</sub> | Load = 2 Series 74TTL Gates                             | _   | _   | 70  | ns   |

| Access Time from Row Address Strobe    | t <sub>RAC</sub> | t <sub>RACL</sub> = Max,<br>Load = 2 Series 74TTL Gates | -   | _   | 120 | ns   |

| Output Disabl Time                     | t <sub>OFF</sub> | Load = 2 Series 74TTL Gates                             | 0   | -   | 40  | ns   |

## <u>Timing Requirements:</u> $(T_A = +25^{\circ}C, V_{DD} = 5V \text{ unless otherwise specified})$

| Parameter            | Symbol          | Min | Тур | Max | Unit |

|----------------------|-----------------|-----|-----|-----|------|

| Page Mode Cycle Time | t <sub>PC</sub> | 130 | -   | -   | ns   |

| Read Cycle Time      | t <sub>RC</sub> | 230 | -   | _   | ns   |

## $\underline{\textbf{Timing Requirements (Cont'd):}} \ \, (T_A = +25^{\circ}C,\, V_{DD} = 5V \text{ unless otherwise specified)}$

| Parameter                                                                                                              | Symbol           | Min | Тур | Max    | Unit |

|------------------------------------------------------------------------------------------------------------------------|------------------|-----|-----|--------|------|

| Write Time Cycle                                                                                                       | t <sub>WC</sub>  | 230 | -   | _      | ns   |

| Read-Write/Read-Modify-Write Cycle Time                                                                                | t <sub>RWC</sub> | 256 | _   | _      | ns   |

| Pulse Width, Column Address Strobe High (Precharge Time, Note 2)                                                       | t <sub>CP</sub>  | 50  | _   | _      | ns   |

| Pulse Width, Column Address Strobe Low                                                                                 | t <sub>CAS</sub> | 70  | _   | 10,000 | ns   |

| Pulse Width, Row Address Strobe High (Precharge Time)                                                                  | t <sub>RP</sub>  | 80  | _   | _      | ns   |

| Pulse Width, Row Address Strobe Low                                                                                    | t <sub>RAS</sub> | 120 | _   | 10,000 | ns   |

| Write Pulse Width                                                                                                      | t <sub>SP</sub>  | 40  | _   | _      | ns   |

| ransition Times (Rise and Fall) for RAS and CAS                                                                        | t <sub>T</sub>   | 3   | _   | 50     | ns   |

| Column Address Setup Time                                                                                              | t <sub>ASC</sub> | -5  | _   | _      | ns   |

| Row Address Setup Time                                                                                                 | t <sub>ASR</sub> | 0   | _   | _      | ns   |

| Data Setup Time                                                                                                        | t <sub>DS</sub>  | 0   | _   | _      | ns   |

| Read Command Setup Time                                                                                                | t <sub>RCS</sub> | 0   | _   | -      | ns   |

| Write Command Setup Time before CAS High                                                                               | t <sub>CWL</sub> | 50  | _   | _      | ns   |

| Write Command Setup Time before RAS High                                                                               | t <sub>RWL</sub> | 50  | _   | -      | ns   |

| Column Address Hold Time after CAS Low                                                                                 | t <sub>CAH</sub> | 40  | _   | -      | ns   |

| Row Address Hold Time                                                                                                  | t <sub>RAH</sub> | 15  | _   | -      | ns   |

| Column Address Hold Time after RAS Low                                                                                 | t <sub>AR</sub>  | 95  | _   | -      | ns   |

| CAS Hold Time after RAS Low                                                                                            | t <sub>CSH</sub> | 150 | _   | -      | ns   |

| Data Hold Time after CAS Low                                                                                           | t <sub>DHS</sub> | 40  | _   | -      | ns   |

| Data Hold Time after RAS Low                                                                                           | t <sub>DHR</sub> | 85  | _   | -      | ns   |

| Data Hold Time after W Low                                                                                             | t <sub>DHC</sub> | 40  | _   | -      | ns   |

| Read Command Hold Time                                                                                                 | t <sub>RCH</sub> | 0   | _   | -      | ns   |

| Write Command Hold Time after CAS Low                                                                                  | t <sub>WCH</sub> | 40  | _   | -      | ns   |

| Write Command Hold Time after RAS Low                                                                                  | t <sub>WCR</sub> | 85  | _   | -      | ns   |

| Delay Time, Column Address Strobe High to Row Address Strobe Low                                                       | t <sub>CRP</sub> | 0   | _   | -      | ns   |

| Delay Time, Column Address Strobe Low to Row Address Strobe High                                                       | t <sub>RSH</sub> | 70  | _   | -      | ns   |

| Delay Time, Column Address Strobe Low to $\overline{W}$ Low (Read, Modify–Write–Cycle Only)                            | t <sub>CWD</sub> | 40  | -   | _      | ns   |

| Delay Time, Row Address Strobe Lo to Column Address Strobe Low (Maximum Value Specified Only to Guarantee Access Time) | t <sub>RCD</sub> | 15  | -   | 50     | ns   |

| Delay Time, Row Address Strobe Low to W Low (Read, Modify-Write-Cycle Only)                                            | t <sub>RWD</sub> | 11  | _   | -      | ns   |

| Delay Time, W Low to Column Address Strobe Low (Early Write Cycle)                                                     | t <sub>WCS</sub> | -5  | _   | -      | ns   |

Note 2. Page Mode Only.

#### Operation:

### Address (A0 through A7)

Sixteen address bits are required to decode 1 of 65,536 storage cell locations. Eight row–address bits are set up on pins A0 through A7 and latched onto the chip by the row–address strobe ( $\overline{RAS}$ ). Then the eight column–address bits are set up on pins A0 through A7 and latched onto the chip by the column–address strobe ( $\overline{CAS}$ ). All addresses must be stable on or before the falling edges of  $\overline{RAS}$  and  $\overline{CAS}$ .  $\overline{RAS}$  is similar to a chip enable in that it activates the sense amplifiers as well as the row decoder.  $\overline{CAS}$  is used as a chip select activating the column decoder and the input and output buffers.

### Write Enable (W)

The read or write mode is selected through the write enable ( $\overline{W}$ ) input. A logic high on the  $\overline{W}$  input selects the read mode and a logic low selects the write mode. The write enable pin can be driven from standard TTL circuits without a pull-up resistor. The data input is disabled when the read mode is selected. When  $\overline{W}$  goes low prior to  $\overline{CAS}$ , data-out will remain in the high-impedance state for the entire cycle permitting common I/O operation.

### Data-In (D)

Data is written during a write or read–modify write cycle. The falling edge of  $\overline{CAS}$  or  $\overline{W}$  strobes data into the on–chip data latch. This latch can be driven from standard TTL circuits without a pull–up resistor. In an early write cycle  $\overline{W}$  is brought low prior to  $\overline{CAS}$  and the data is strobed in by  $\overline{CAS}$  with setup and hold times referenced to this signal. In a delayed write or read–modify write cycle,  $\overline{CAS}$  will already be low, thus the data will be strobed in by  $\overline{W}$  with setup and hold times referenced to this signal.

### Data-Out (Q)

The three state output buffer provides direct TTL compatibility (no pull–up resistor required) with a fan–out of two Series 74TTL loads. Data–out is the same polarity as data–in. The output is in the high–impedance (floating) state until  $\overline{\text{CAS}}$  is brought low. In a read cycle the output goes active after the access time interval  $t_{a(C)}$  that begins with the negative transition of  $\overline{\text{CAS}}$  as long as  $t_{a(R)}$  is satisfied. The output becomes valid after the access time has elapsed and remains valid while  $\overline{\text{CAS}}$  is low;  $\overline{\text{CAS}}$  going high returns it to a high–impedance state. In an early write cycle, the output is always in the high–impedance state. In a delayed write or read–modify–write cycle, the output will follow the sequence for the read cycle.

#### Refresh

A refresh operation must be performed at least every four milliseconds to retain data. Since the output buffer is in the high–impedance state unless  $\overline{CAS}$  is applied, the  $\overline{RAS}$  only refresh sequence avoids any output during refresh. Strobing each of the 256 row addresses (A0 through A7) with  $\overline{RAS}$  causes all bits in each row to be refreshed.  $\overline{CAS}$  can remain high (inactive) for this refresh sequence to conserve power.

### Page Mode

Page mode operation allows effectively faster memory access by keeping the same row address and strobing successive column addresses onto the chip. Thus, the time required to setup and strobe sequential row addresses for the same page is eliminated. To extend beyond the 256 column locations on a single RAM, the row address and RAS are applied to multiple 64K RAMs. CAS is then decoded to select the proper RAM.

## **Pin Connection Diagram** V<sub>BB</sub> 1 16 V<sub>SS</sub> D<sub>IN</sub> 2 15 CAS WRITE 3 14 D<sub>OUT</sub> RAS 4 **13** A6 A0 5 **12** A3 A2 6 **11** A4 A1 7 **10** A5 9 V<sub>CC</sub> GND 8