# Power Management Solution for Application Processors

## **FEATURES**

- Quad I<sup>2</sup>C Adjustable High Efficiency Step Down DC/DC Converters: 2.5A, 2.5A, 1.5A, 1.5A

- Three 300mA LDO Regulators (Two Adjustable)

- DDR Power Solution with V<sub>TT</sub> and VTTR Reference

- Pushbutton ON/OFF Control with System Reset

- Independent Enable Pin-Strap or I<sup>2</sup>C Sequencing

- Programmable Autonomous Power-Down Control

- Dynamic Voltage Scaling

- Power Good and Reset Functions

- Selectable 2.25MHz or 1.12MHz Switching Frequency

- Always Alive 25mA LDO Regulator

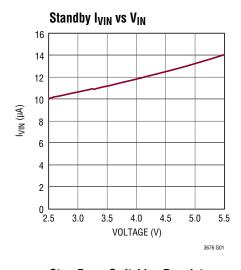

- 12µA Standby Current

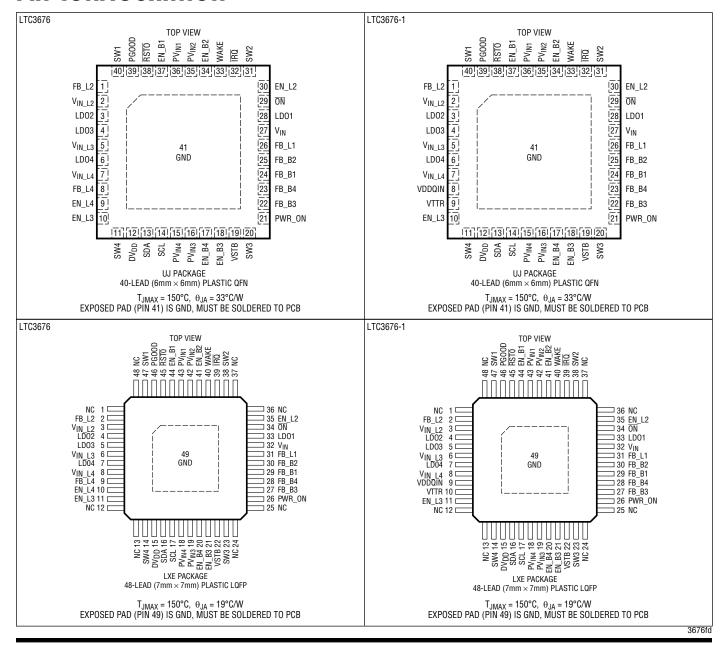

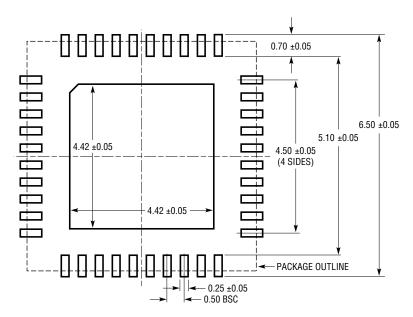

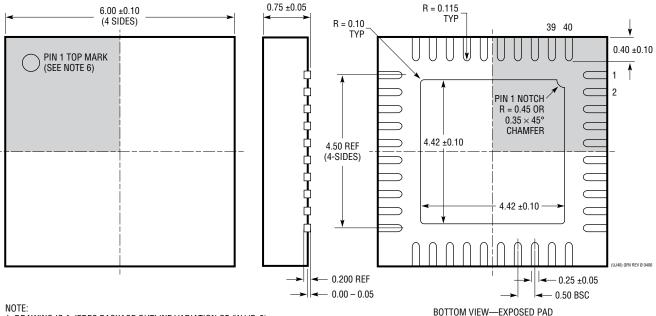

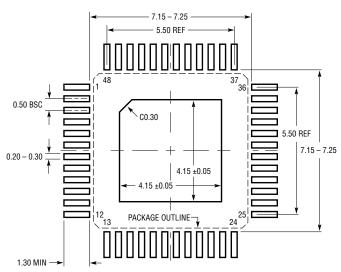

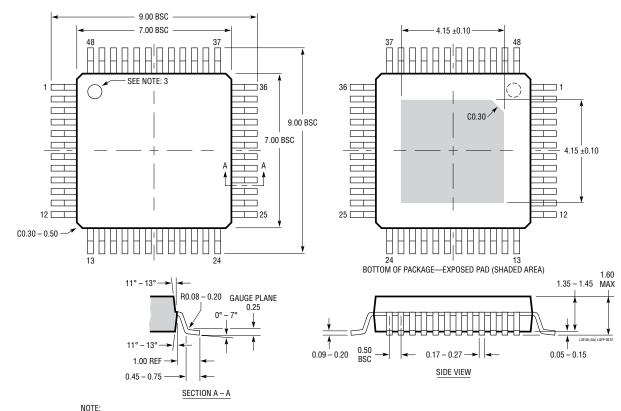

- Low Profile 40-Lead 6mm × 6mm QFN and 48-Lead Exposed Pad LQFP

## **APPLICATIONS**

- Supports Freescale i.MX6, ARM Cortex, and Other Application Processors

- Handheld Instruments and Scanners

- Portable Industrial and Medical Devices

- Automotive Infotainment

- High End Consumer Devices

- Multi-Rail Systems

## DESCRIPTION

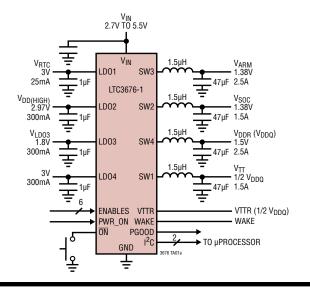

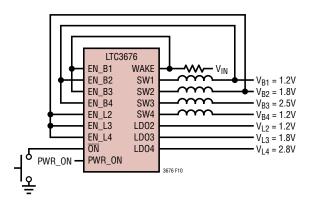

The LTC®3676 is a complete power management solution for advanced portable application processor-based systems. The device contains four synchronous step-down DC/DC converters for core, memory, I/O, and system on-chip (SoC) rails and three 300mA LDO regulators for low noise analog supplies. The LTC3676-1 has a  $\pm 1.5$ A buck regulator configured to support DDR termination plus a VTTR reference output. An I²C serial port is used to control regulator enables, power-down sequencing, output voltage levels, dynamic voltage scaling, operating modes and status reporting.

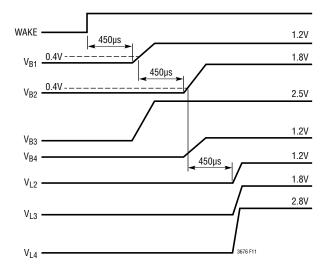

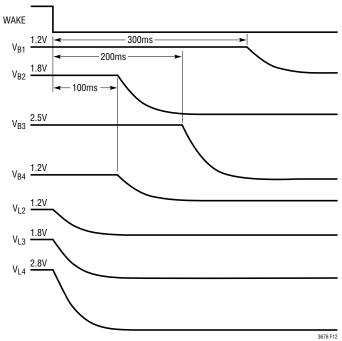

Regulator start-up is sequenced by connecting outputs to enable pins in the desired order or via the  $I^2C$  port. System power-on, power-off and reset functions are controlled by pushbutton interface, pin inputs, or  $I^2C$ .

The LTC3676 supports i.MX, PXA and OMAP processors with eight independent rails at appropriate power levels. Other features include interface signals such as the VSTB pin that toggles between programmed run and standby output voltages on up to four rails simultaneously. The device is available in a 40-lead 6mm  $\times$  6mm QFN and 48-lead exposed pad LQFP packages.

T, LT, LTC, LTM, Linear Technology, the Linear logo and Burst Mode are registered trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

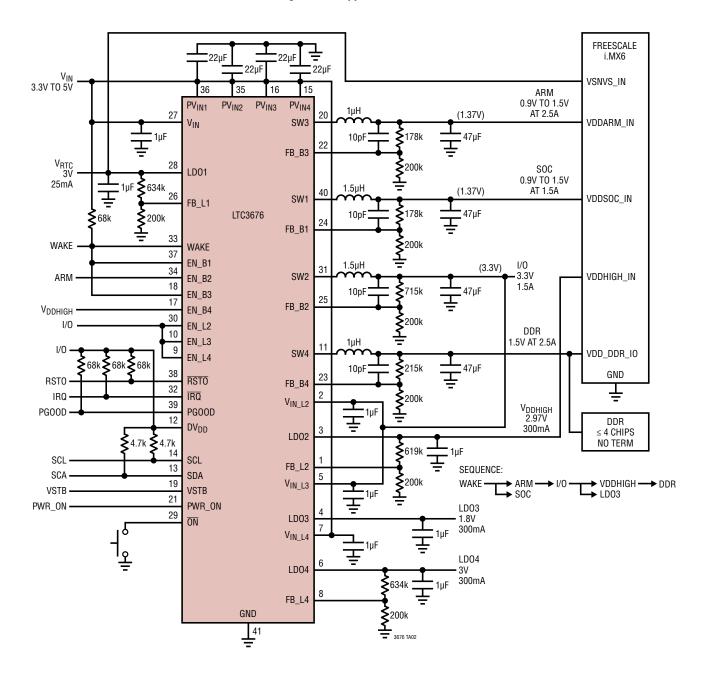

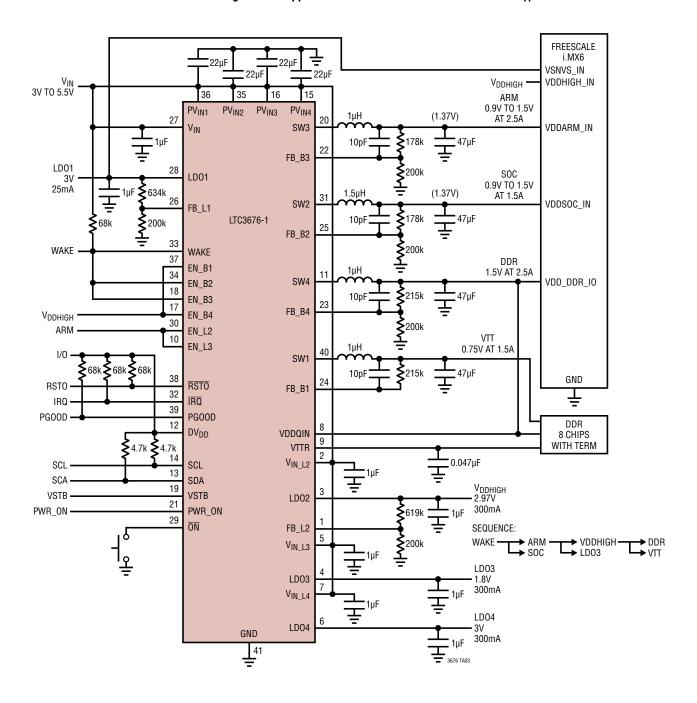

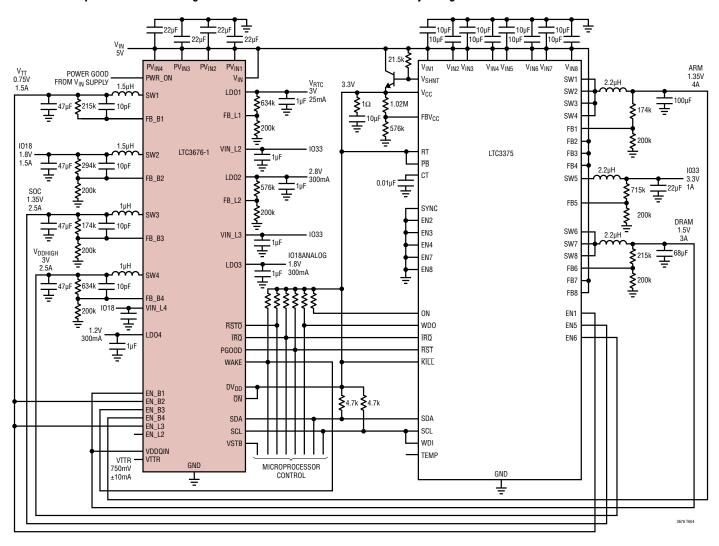

## TYPICAL APPLICATION

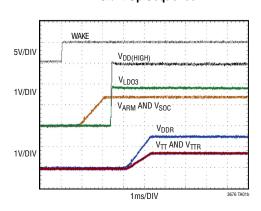

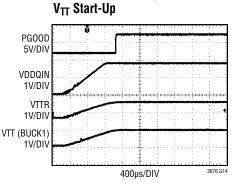

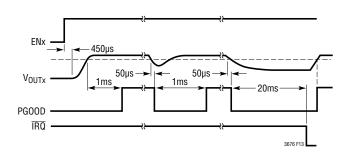

#### Start-Up Sequence

# **ABSOLUTE MAXIMUM RATINGS** (Note 1)

$\begin{array}{l} V_{IN}, \, DV_{DD}, \, SW1, \, SW2, \, SW3, \, SW4 \dots -0.3V \ to \ 6V \\ SW1, \, SW2, \, SW3, \, SW4 \\ (Transient \ t < 1\mu s, \, Duty \, Cycle < 5\%) \dots -2V \ to \ 7V \\ PV_{IN1}, \, PV_{IN2}, \, PV_{IN3}, \, PV_{IN4}, \, V_{IN\_L2}, \\ V_{IN\_L3}, \, V_{IN\_L4} \dots -0.3V \ to \, V_{IN} + 0.3V \\ LDO1, \, FB\_L1, \, LDO2, \, FB\_L2, \, LDO3, \, LDO4, \, FB\_L4, \\ FB\_B1, \, FB\_B2, \, FB\_B3, \, FB\_B4, \, PGOOD, \, VSTB, \, EN\_B1, \\ EN\_B2, \, EN\_B3, \, EN\_B4, \, EN\_L2, \, EN\_L3, \, EN\_L4, \, \overline{ON}, \end{array}$

WAKE, RSTO, PWR\_ON, IRQ, VTTR,

VDDQIN ......-0.3V to 6V

SDA, SCL ....-0.3V to DV<sub>DD</sub> + 0.3V

Operating Junction Temperature Range

(Notes 2, 3) ....-40°C to 150°C

Storage Temperature Range ....-65 to 150°C

## PIN CONFIGURATION

# **ORDER INFORMATION**

| LEAD FREE FINISH | TAPE AND REEL      | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|------------------|--------------------|---------------|---------------------------------|-------------------|

| LTC3676EUJ#PBF   | LTC3676EUJ#TRPBF   | LTC3676UJ     | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3676IUJ#PBF   | LTC3676IUJ#TRPBF   | LTC3676UJ     | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3676HUJ#PBF   | LTC3676HUJ#TRPBF   | LTC3676UJ     | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 150°C    |

| LTC3676EUJ-1#PBF | LTC3676EUJ-1#TRPBF | LTC3676UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3676IUJ-1#PBF | LTC3676IUJ-1#TRPBF | LTC3676UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 125°C    |

| LTC3676HUJ-1#PBF | LTC3676HUJ-1#TRPBF | LTC3676UJ-1   | 40-Lead (6mm × 6mm) Plastic QFN | -40°C to 150°C    |

| LEAD FREE FINISH  | TRAY              | PART MARKING* | PACKAGE DESCRIPTION               | TEMPERATURE RANGE |

|-------------------|-------------------|---------------|-----------------------------------|-------------------|

| LTC3676ELXE#PBF   | LTC3676ELXE#PBF   | LTC3676LXE    | 48-Lead (7mm × 7mm) Plastic eLQFP | -40°C to 125°C    |

| LTC3676ILXE#PBF   | LTC3676ILXE#PBF   | LTC3676LXE    | 48-Lead (7mm × 7mm) Plastic eLQFP | -40°C to 125°C    |

| LTC3676HLXE#PBF   | LTC3676HLXE#PBF   | LTC3676LXE    | 48-Lead (7mm × 7mm) Plastic eLQFP | -40°C to 150°C    |

| LTC3676ELXE-1#PBF | LTC3676ELXE-1#PBF | LTC3676LXE-1  | 48-Lead (7mm × 7mm) Plastic eLQFP | -40°C to 125°C    |

| LTC3676ILXE-1#PBF | LTC3676ILXE-1#PBF | LTC3676LXE-1  | 48-Lead (7mm × 7mm) Plastic eLQFP | -40°C to 125°C    |

| LTC3676HLXE-1#PBF | LTC3676HLXE-1#PBF | LTC3676LXE-1  | 48-Lead (7mm × 7mm) Plastic eLQFP | -40°C to 150°C    |

$Consult\ LTC\ Marketing\ for\ parts\ specified\ with\ wider\ operating\ temperature\ ranges.\ {}^*The\ temperature\ grade\ is\ identified\ by\ a\ label\ on\ the\ shipping\ container.$

Consult LTC Marketing for information on nonstandard lead based finish parts.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at $T_A = 25^{\circ}C$ (Note 2). $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_L2} = V_{IN\_L3} = V_{IN\_L4} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| PARAMETER                                                                                                    | CONDITIONS                                                                           |   | MIN                | TYP           | MAX             | UNITS                    |

|--------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---|--------------------|---------------|-----------------|--------------------------|

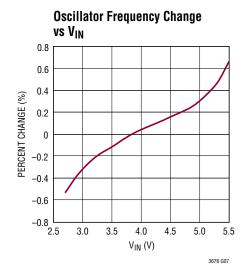

| Operating Input Supply Voltage, V <sub>IN</sub>                                                              |                                                                                      | • | 2.7                |               | 5.5             | V                        |

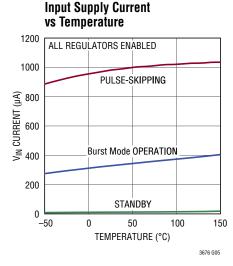

| V <sub>IN</sub> Standby Current                                                                              | PWR_ON = 0V                                                                          | • |                    | 12            | 21              | μΑ                       |

| Step-Down Switching Regulators 1, 2, 3 and                                                                   | 4                                                                                    |   |                    |               |                 |                          |

| Output Voltage Range                                                                                         |                                                                                      |   | $V_{FB}$           |               | $PV_{IN}$       | V                        |

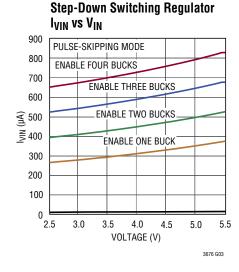

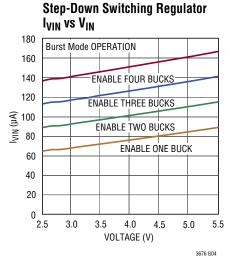

| Burst Mode <sup>®</sup> V <sub>IN</sub> Quiescent Current                                                    | V <sub>FB</sub> = 850mV (Note 5)                                                     | • |                    | 23            | 50              | μΑ                       |

| Pulse-Skipping Mode V <sub>IN</sub> Quiescent Current<br>Forced Continuous V <sub>IN</sub> Quiescent Current | V <sub>FB</sub> = 850mV (Note 5)<br>V <sub>FB</sub> = 0V (Note 5)                    | • |                    | 120<br>170    | 200<br>300      | μ <i>Α</i><br>μ <i>Α</i> |

| Feedback Pin Input Current                                                                                   | V <sub>FB</sub> = 850mV                                                              |   | -0.05              |               | 0.05            | μΑ                       |

| Maximum Duty Cycle                                                                                           | V <sub>FB</sub> = 0V                                                                 |   | 100                |               |                 | %                        |

| SW Pull-Down Resistance                                                                                      | Regulator Disabled                                                                   |   |                    | 625           |                 | Ω                        |

| Feedback Reference Soft-Start Rate                                                                           | (Note 6)                                                                             |   |                    | 0.8           |                 | V/ms                     |

| High Feedback Regulation Voltage (V <sub>FB</sub> )                                                          | DVBxA[4:0] = DVBxB[4:0] = 11111,<br>V <sub>IN</sub> = 2.7V to 5.5V                   | • | 788                | 800           | 812             | m۷                       |

| Default Feedback Regulation Voltage (V <sub>FB</sub> )                                                       | DVBxA[4:0] = DVBxB[4:0] = 11001,<br>V <sub>IN</sub> = 2.7V to 5.5V                   | • | 714                | 725           | 736             | m۷                       |

| Low Feedback Regulation Voltage (V <sub>FB</sub> )                                                           | DVBxA[4:0] = DVBxB[4:0] = 00000,<br>V <sub>IN</sub> = 2.7V to 5.5V                   | • | 404                | 412.5         | 421             | m۷                       |

| Feedback LSB Step Size                                                                                       |                                                                                      |   |                    | 12.5          |                 | m۷                       |

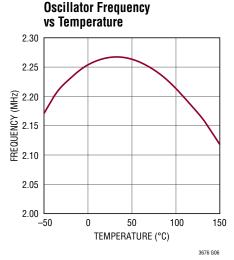

| Switching Frequency                                                                                          | BUCKx[2] = 0<br>BUCKx[2] = 1                                                         | • | 1.7<br>0.85        | 2.25<br>1.125 | 2.7<br>1.35     | MHz<br>MHz               |

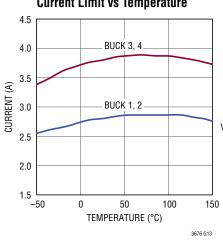

| 1.5A Step-Down Switching Regulators 1 and                                                                    | 2                                                                                    |   |                    |               |                 |                          |

| PMOS Current Limit                                                                                           |                                                                                      | • | 2                  |               |                 | Α                        |

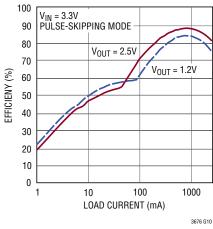

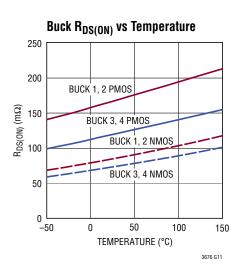

| PMOS On-Resistance (Note 7)                                                                                  |                                                                                      |   |                    | 160           |                 | mΩ                       |

| NMOS On-Resistance (Note 7)                                                                                  |                                                                                      |   |                    | 80            |                 | mΩ                       |

| 2.5A Step-Down Switching Regulators 3 and                                                                    | 4                                                                                    |   |                    |               |                 |                          |

| PMOS Current Limit                                                                                           |                                                                                      | • | 3.0                |               |                 | P                        |

| PMOS On-Resistance (Note 7)                                                                                  |                                                                                      |   |                    | 120           |                 | mΩ                       |

| NMOS On-Resistance (Note 7)                                                                                  |                                                                                      |   |                    | 70            |                 | mΩ                       |

| Step-Down Switching Regulator 1 and VITR                                                                     | (LTC3676-1)                                                                          |   |                    |               |                 |                          |

| Buck 1 Feedback Regulation Voltage                                                                           | VDDQIN = 1.5V                                                                        | • | VTTR – 10          | VTTR          | VTTR + 10       | m۱                       |

| VTTR Output Voltage                                                                                          | VDDQIN = 1.5V                                                                        | • | 0.49•VDDQIN        | 0.5•VDDQIN    | 0.51•VDDQIN     | m۷                       |

| VTTR Maximum Output Current                                                                                  |                                                                                      | • | -10                |               | 10              | mA                       |

| I <sub>VIN</sub> VTTR Enabled                                                                                |                                                                                      |   |                    | 1             |                 | m <i>P</i>               |

| LDO Regulators 2, 3 and 4                                                                                    |                                                                                      |   |                    |               |                 |                          |

| Feedback Reference Soft-Start Rate                                                                           |                                                                                      |   |                    | 10            |                 | V/ms                     |

| Output Pull-Down Resistance                                                                                  | Regulator Disabled                                                                   |   |                    | 625           |                 | Ω                        |

| LDO Regulator 1                                                                                              |                                                                                      |   |                    |               |                 |                          |

| Output Voltage Range                                                                                         |                                                                                      |   | V <sub>FB_L1</sub> |               | V <sub>IN</sub> |                          |

| Feedback Regulation Voltage (V <sub>FB_L1</sub> )                                                            |                                                                                      | • | 689                | 725           | 761             | m۷                       |

| Line Regulation                                                                                              | I <sub>LD01</sub> = 1mA, V <sub>LD01</sub> = 1.2V,<br>V <sub>IN</sub> = 2.7V to 5.5V |   |                    | 0.15          |                 | %/\                      |

| Load Regulation                                                                                              | I <sub>LD01</sub> = 0.1mA to 25mA,<br>V <sub>LD01</sub> = 3.3V                       |   |                    | 0.1           |                 | %                        |

**TLINEAR**

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_L2} = V_{IN\_L3} = V_{IN\_L4} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| PARAMETER                                                                   |                                                                                                            | MIN | TYP                             | MAX                      | UNITS                           |             |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|-----|---------------------------------|--------------------------|---------------------------------|-------------|

| Available Output Current                                                    |                                                                                                            | •   | 25                              |                          |                                 | mA          |

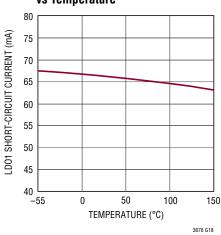

| Short-Circuit Output Current Limit                                          |                                                                                                            |     |                                 | 65                       | 100                             | mA          |

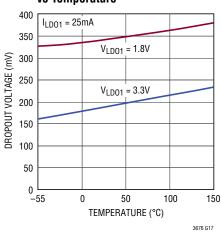

| Dropout Voltage (Note 4)                                                    | I <sub>LD01</sub> = 25mA, V <sub>LD01</sub> = 3.3V                                                         |     |                                 | 200                      | 280                             | mV          |

| Feedback Pin Input Current                                                  | V <sub>FB_L1</sub> = 850mV                                                                                 |     | -0.05                           |                          | 0.05                            | μА          |

| LDO Regulator 2                                                             |                                                                                                            |     |                                 |                          |                                 |             |

| V <sub>IN_L2</sub> Input Voltage                                            |                                                                                                            | •   | 1.7                             |                          | V <sub>IN</sub>                 | V           |

| LD02 Output Voltage Range                                                   | I <sub>LD02</sub> = 1mA                                                                                    |     | V <sub>FB_L2</sub>              |                          | V <sub>IN_L2</sub>              | V           |

| Available Output Current                                                    |                                                                                                            | •   | 300                             |                          |                                 | mA          |

| V <sub>IN_L2</sub> Quiescent Current<br>V <sub>IN_L2</sub> Shutdown Current | Regulator Enabled, I <sub>LD02</sub> = 0A<br>Regulator Disabled                                            | •   |                                 | 12<br>0                  | 25<br>1                         | μA<br>μA    |

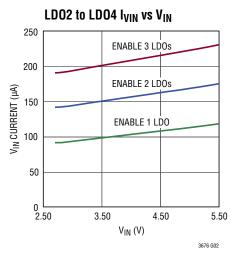

| V <sub>IN</sub> Quiescent Current                                           | Regulator Enabled                                                                                          | •   |                                 | 50                       | 85                              | μА          |

| Feedback Regulation Voltage (V <sub>FB_L2</sub> )                           |                                                                                                            | •   | 0.707                           | 0.725                    | 0.743                           | V           |

| Line Regulation                                                             | $I_{LD02}$ =1mA, $V_{IN}$ = 2.7V to 5.5V                                                                   |     |                                 | 0.01                     |                                 | %/V         |

| Load Regulation                                                             | I <sub>LD02</sub> = 1mA to 300mA                                                                           |     |                                 | 0.01                     |                                 | %           |

| Short-Circuit Current Limit                                                 |                                                                                                            |     |                                 |                          | 770                             | mA          |

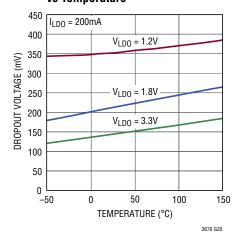

| Dropout Voltage (Note 4)                                                    | I <sub>LD02</sub> = 300mA, V <sub>LD02</sub> = 2.5V<br>I <sub>LD02</sub> = 300mA, V <sub>LD02</sub> = 1.2V |     |                                 | 210<br>450               | 260<br>615                      | mV<br>mV    |

| Feedback Pin Input Current                                                  | V <sub>FB_L2</sub> = 725mV                                                                                 |     | -0.05                           |                          | 0.05                            | μА          |

| LDO Regulator 3                                                             |                                                                                                            |     |                                 |                          |                                 |             |

| V <sub>IN_L3</sub> Input Voltage                                            |                                                                                                            | •   | 2.35                            |                          | V <sub>IN</sub>                 | V           |

| Output Voltage                                                              | V <sub>IN_L3</sub> = V <sub>IN</sub> , I <sub>LDO3</sub> = 1mA                                             | •   | 1.746                           | 1.8                      | 1.854                           | V           |

| Available Output Current                                                    |                                                                                                            | •   | 300                             |                          |                                 | mA          |

| V <sub>IN_L3</sub> Quiescent Current<br>V <sub>IN_L3</sub> Shutdown Current | Regulator Enabled, I <sub>LD03</sub> = 0A<br>Regulator Disabled                                            | •   |                                 | 14<br>0                  | 25<br>1                         | μA<br>μA    |

| V <sub>IN</sub> Quiescent Current                                           | Regulator Enabled                                                                                          | •   |                                 | 50                       | 85                              | μА          |

| Line Regulation                                                             | $I_{LD03} = 1 \text{ mA}, V_{IN} = 2.7 \text{V to } 5.5 \text{V}$                                          |     |                                 | 0.01                     |                                 | %/V         |

| Load Regulation                                                             | I <sub>LD03</sub> = 1mA to 300mA                                                                           |     |                                 | 0.05                     |                                 | %           |

| Short-Circuit Current Limit                                                 |                                                                                                            |     |                                 |                          | 770                             | mA          |

| Dropout Voltage (Note 4)                                                    | $I_{LD03} = 300 \text{mA}, V_{LD03} = 1.8 \text{V}$                                                        |     |                                 | 280                      | 350                             | mV          |

| LDO Regulator 4                                                             |                                                                                                            |     |                                 |                          |                                 |             |

| V <sub>IN_L4</sub> Input Voltage                                            |                                                                                                            | •   | 1.7                             |                          | $V_{IN}$                        | V           |

| LDO4 Output Voltage Range (LTC3676)                                         | I <sub>LD04</sub> = 1mA                                                                                    |     | $V_{FB\_L4}$                    |                          | $V_{IN\_L4}$                    | V           |

| Feedback Regulation Voltage (LTC3676) ( $V_{FB\_L4}$ )                      |                                                                                                            | •   | 0.707                           | 0.725                    | 0.743                           | V           |

| Output Voltage (LTC3676-1)                                                  | I <sub>LD04</sub> = 1mA, LD0B[4:3] = 00<br>LD0B[4:3] = 01<br>LD0B[4:3] = 10<br>LD0B[4:3] = 11              | •   | 1.164<br>2.425<br>2.716<br>2.91 | 1.2<br>2.5<br>2.8<br>3.0 | 1.236<br>2.575<br>2.884<br>3.09 | V<br>V<br>V |

| Available Output Current                                                    | 1 -1                                                                                                       |     | 300                             |                          |                                 | mA          |

| V <sub>IN_L4</sub> Quiescent Current<br>V <sub>IN_L4</sub> Shutdown Current | Regulator Enabled, I <sub>LDO4</sub> = 0A<br>  Regulator Disabled                                          | •   |                                 | 12<br>0                  | 25<br>1                         | μΑ<br>μΑ    |

| V <sub>IN</sub> Quiescent Current                                           | Regulator Enabled                                                                                          | •   |                                 | 50                       | 85                              | μA          |

| Line Regulation                                                             | I <sub>LD04</sub> =1mA, V <sub>IN</sub> = 2.7V to 5.5V                                                     |     |                                 | 0.01                     |                                 | %/V         |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_L2} = V_{IN\_L3} = V_{IN\_L4} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| PARAMETER                                                             | CONDITIONS                                                                                                 |   | MIN   | TYP          | MAX        | UNITS    |

|-----------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|---|-------|--------------|------------|----------|

| Load Regulation (LTC3676)<br>Load Regulation (LTC3676-1)              | I <sub>LD04</sub> = 1mA to 300mA                                                                           |   |       | 0.01<br>0.05 |            | %<br>%   |

| Short-Circuit Current Limit                                           |                                                                                                            |   |       |              | 770        | mA       |

| Dropout Voltage (Note 4)                                              | I <sub>LD04</sub> = 300mA, V <sub>LD04</sub> = 2.5V<br>I <sub>LD04</sub> = 300mA, V <sub>LD04</sub> = 1.2V |   |       | 210<br>450   | 260<br>615 | mV<br>mV |

| Feedback Pin Input Current (LTC3676)                                  | V <sub>FB_L4</sub> = 725mV                                                                                 |   | -0.05 |              | 0.05       | μА       |

| Enable Inputs                                                         |                                                                                                            | ' |       |              |            |          |

| Threshold Rising                                                      | All Enables Low                                                                                            | • |       | 0.75         | 1.2        | V        |

| Threshold Falling                                                     | One Enable High                                                                                            | • | 0.4   | 0.7          |            |          |

| Precision Threshold                                                   | One or More Enables                                                                                        | • | 0.370 | 0.400        | 0.430      | V        |

| Input Pull-Down Resistance                                            |                                                                                                            |   |       | 4.5          |            | MΩ       |

| VSTB, PWR_ON Inputs                                                   | ·                                                                                                          |   |       |              |            |          |

| Threshold                                                             |                                                                                                            | • | 0.370 | 0.400        | 0.430      | V        |

| Pull-Down Resistance                                                  |                                                                                                            |   |       | 4.5          |            | MΩ       |

| Pushbutton Interface                                                  | ,                                                                                                          |   |       |              |            |          |

| ON Threshold Rising ON Threshold Falling                              |                                                                                                            | • | 0.4   | 0.75<br>0.7  | 1.2        | V        |

| ON Input Current                                                      | $\frac{\overline{ON}}{\overline{ON}} = V_{1N}$ $\overline{ON} = OV$                                        |   | -1    | -40          | 1          | μA<br>μA |

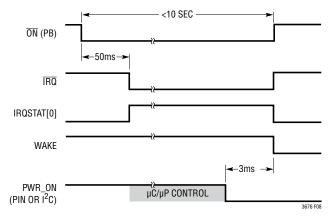

| ON Low Time to IRQ Low                                                |                                                                                                            |   |       | 50           |            | ms       |

| ON High Time to IRQ High                                              |                                                                                                            |   |       | 0.2          |            | μs       |

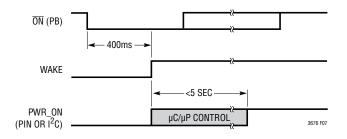

| ON Low Time to WAKE High                                              |                                                                                                            |   | 400   |              |            |          |

| ON Low Time to Hard Reset                                             | CNTRL[6] = 0                                                                                               |   | 10    |              |            |          |

| IRQ Minimum Pulse Width                                               |                                                                                                            |   |       | 50           |            | ms       |

| IRQ Blanking from WAKE Low                                            |                                                                                                            |   |       | 1            |            | sec      |

| Minimum WAKE Low Time                                                 |                                                                                                            |   |       | 1            |            | sec      |

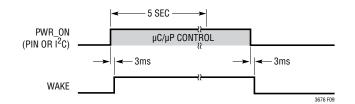

| WAKE High Time with PWR_ON = 0V                                       |                                                                                                            |   |       | 5            |            | sec      |

| PWR_ON High to WAKE High                                              |                                                                                                            |   |       | 3            |            | ms       |

| PWR_ON Low to WAKE Low                                                |                                                                                                            |   |       | 3            |            | ms       |

| Status Output Pins (WAKE, PGOOD, RSTO,                                | ĪRQ)                                                                                                       |   |       |              |            |          |

| WAKE Output Low Voltage                                               | I <sub>WAKE</sub> = 3mA                                                                                    |   |       | 0.1          | 0.4        | V        |

| WAKE Output High Leakage Current                                      | V <sub>WAKE</sub> = 3.8V                                                                                   |   | -0.1  |              | 0.1        | μА       |

| PGOOD Output Low Voltage                                              | I <sub>PGOOD</sub> = 3mA                                                                                   |   |       | 0.1          | 0.4        | V        |

| PGOOD Output High Leakage Current                                     | V <sub>PG00D</sub> = 3.8V                                                                                  |   | -0.1  |              | 0.1        | μА       |

| PGOOD Threshold Rising PGOOD Threshold Falling                        |                                                                                                            |   |       | -6<br>-8     |            | %<br>%   |

| RSTO Output Low Voltage                                               | I <sub>RSTO</sub> = 3mA                                                                                    |   |       | 0.1          | 0.4        | V        |

| RSTO Output High Leakage Current                                      | V <sub>RST0</sub> = 3.8V                                                                                   |   | -0.1  |              | 0.1        | μА       |

| LD01 Power Good Threshold Rising<br>LD01 Power Good Threshold Falling |                                                                                                            |   |       | −7.5<br>−10  |            | %<br>%   |

| IRQ Output Low Voltage                                                | I <sub>ĪRQ</sub> = 3mA                                                                                     |   |       | 0.1          | 0.4        | V        |

| IRQ Output High Leakage Current                                       | V <sub>IRQ</sub> = 3.8V                                                                                    |   | -0.1  |              | 0.1        | μА       |

**ELECTRICAL CHARACTERISTICS** The • denotes the specifications which apply over the specified operating junction temperature range, otherwise specifications are at  $T_A = 25^{\circ}C$  (Note 2).  $V_{IN} = PV_{IN1} = PV_{IN2} = PV_{IN3} = PV_{IN4} = V_{IN\_L2} = V_{IN\_L3} = V_{IN\_L4} = DV_{DD} = 3.8V$ . All regulators disabled unless otherwise noted.

| PARAMETER                    | ER CONDITI                                         |                         | TIONS                                                                  |      |                            | MIN                    | ТҮР                                                 | MAX  | UNITS             |

|------------------------------|----------------------------------------------------|-------------------------|------------------------------------------------------------------------|------|----------------------------|------------------------|-----------------------------------------------------|------|-------------------|

| Undervoltage<br>Undervoltage | Lockout Rising<br>Lockout Falling                  |                         |                                                                        | •    |                            | 2.35                   | 2.55<br>2.45                                        | 2.65 | V                 |

| CN CN                        |                                                    | CNTRL<br>CNTRL<br>CNTRL | [4:2] = 000 (POR Default)<br>[4:2] = 001<br>[4:2] = 010<br>[4:2] = 011 |      |                            |                        | 2.7<br>2.8<br>2.9<br>3.0                            |      | V<br>V<br>V       |

|                              |                                                    | CNTRL <br>CNTRL         | [4:2] = 100<br>[4:2] = 101<br>[4:2] = 110<br>[4:2] = 111               |      |                            |                        | 3.1<br>3.2<br>3.3<br>3.4                            |      | V<br>V<br>V       |

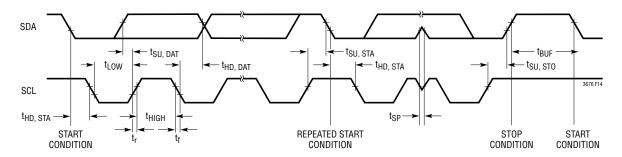

| SYMBOL                       | PARAMETER                                          |                         | CONDITIONS                                                             |      |                            | MIN                    | ТҮР                                                 | MAX  | UNITS             |

| I <sup>2</sup> C Port        |                                                    |                         |                                                                        |      |                            |                        |                                                     |      |                   |

| DV <sub>VDD</sub>            | DV <sub>DD</sub> Input Supply Voltage              |                         |                                                                        |      | •                          | 1.6                    |                                                     | 5.5  | V                 |

| $I_{DVDD}$                   | DV <sub>DD</sub> Quiescent Current                 |                         | SCL/SDA = 0kHz                                                         |      |                            |                        | 0.3                                                 | 1    | μΑ                |

| $DV_{VDD\_UVLO}$             | DV <sub>DD</sub> UVLO Level                        |                         |                                                                        |      |                            |                        | 1                                                   |      | V                 |

| ADDRESS                      | LTC3676 Device Address<br>LTC3676-1 Device Address |                         |                                                                        |      |                            |                        | 0111100[R/\overline{W}]<br>01111101[R/\overline{W}] |      |                   |

| $V_{IH}$                     | SDA/SCL Input Threshold Rising                     |                         |                                                                        |      |                            |                        | 70                                                  |      | %DV <sub>DD</sub> |

| $V_{IL}$                     | SDA/SCL Input Threshold Falling                    |                         |                                                                        |      |                            |                        | 30                                                  |      | %DV <sub>DD</sub> |

| I <sub>IH</sub>              | SDA/SCL High Input Current                         |                         | SDA = SCL = 5.5V                                                       |      |                            | -1                     | 0                                                   | 1    | μA                |

| I <sub>IL</sub>              | SDA/SCL Low Input Current                          |                         | SDA = SCL = 0V                                                         |      |                            | -1                     | 0                                                   | 1    | μА                |

| $V_{OL\_SDA}$                | SDA Output Low Voltage                             |                         | I <sub>SDA</sub> = 3mA                                                 |      |                            |                        |                                                     | 0.4  | V                 |

| f <sub>SCL</sub>             | Clock Operating Frequency                          |                         |                                                                        |      |                            |                        |                                                     | 400  | kHz               |

| t <sub>BUF</sub>             | Bus Free Time Between Stop and S<br>Condition      | Start                   |                                                                        |      |                            | 1.3                    |                                                     |      | μѕ                |

| t <sub>HD_STA</sub>          | Hold Time After Repeated Start Co                  | ndition                 |                                                                        |      |                            | 0.6                    |                                                     |      | μs                |

| t <sub>SU_STA</sub>          | Repeated Start Condition Setup Tir                 | ne                      |                                                                        |      |                            | 0.6                    |                                                     |      | μs                |

| t <sub>SU_STO</sub>          | Stop Condition Setup Time                          |                         |                                                                        |      |                            | 0.6                    |                                                     |      | μs                |

| t <sub>HD_DAT(0)</sub>       | Data Hold Time Output                              |                         |                                                                        |      |                            | 0                      |                                                     | 900  | ns                |

| t <sub>HD_DAT(I)</sub>       | Data Hold Time Input                               |                         |                                                                        |      |                            | 0                      |                                                     |      | ns                |

| t <sub>SU_DAT</sub>          | Data Setup Time                                    |                         |                                                                        |      |                            | 100                    |                                                     |      | ns                |

| t <sub>LOW</sub>             | SCL Clock Low Period                               |                         |                                                                        |      |                            | 1.3                    |                                                     |      | μs                |

| t <sub>HIGH</sub>            | SCL Clock High Period                              |                         |                                                                        |      |                            | 0.6                    |                                                     |      | μs                |

| t <sub>f</sub>               | Clock/Data Fall Time                               |                         | C <sub>B</sub> = Capacitance of BUS Line                               | (pF) | 20 + 0.1C <sub>B</sub> 300 |                        | 300                                                 | ns   |                   |

| t <sub>r</sub>               | Clock/Data Rise Time                               |                         | C <sub>B</sub> = Capacitance of BUS Line                               | (pF) |                            | 20 + 0.1C <sub>B</sub> |                                                     | 300  | ns                |

| t <sub>SP</sub>              | Input Spike Suppression Pulse Wi                   | dth                     |                                                                        |      |                            |                        |                                                     | 50   | ns                |

**Note 1:** Stresses beyond those listed Under Absolute Maximum ratings may cause permanent damage to the device. Exposure to any Absolute Maximum rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** The LTC3676 is tested under pulsed load conditions such that  $T_J \approx T_A$ . The LTC3676E is guaranteed to meet specifications from 0°C to 85°C junction temperature. Specifications over the -40°C to 125°C operating junction temperature range are assured by design, characterization and correlation with statistical process controls. The LTC3676I is guaranteed over the -40°C to 125°C operating junction temperature range and the LTC3676H is guaranteed over the full -40°C to 150°C operating junction temperature range. High junction temperatures

degrade operating lifetimes; operating lifetime is derated for junction temperatures greater than 125°C. The junction temperature ( $T_J$  in °C) is calculated from the ambient temperature ( $T_A$  in °C) and power dissipation ( $P_D$ , in Watts), and package to junction ambient thermal impedance ( $\theta J_A$  in Watts/°C) according to the formula:

$$T_J = T_A + (P_D \bullet \theta J_A).$$

Note that the maximum ambient temperature consistent with these specifications is determined by specific operating conditions in conjunction with board layout, the rated package thermal impedance and other environmental factors.

## **ELECTRICAL CHARACTERISTICS**

**Note 3:** The LTC3676 includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 150°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 4:** Dropout voltage is defined as  $(V_{IN}-V_{LDO1})$  for LDO1 or  $(V_{IN\_Lx}-V_{LDOx})$  for other LDOs when  $V_{LDOx}$  is 3% lower than  $V_{LDOx}$  measured with  $V_{IN}=V_{IN\_Lx}=4.3V$ .

**Note 5:** Dynamic supply current is higher due to the gate charge being delivered at the switching frequency.

**Note 6:** Soft-Start measured in test mode with regulator error amplifier in unity-gain mode.

**Note 7:** The switching regulator PMOS and NMOS on-resistance is guaranteed by correlation to wafer level measurements.

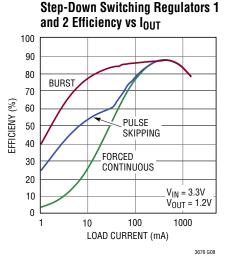

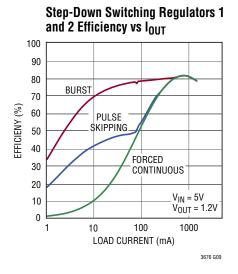

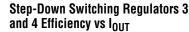

# TYPICAL PERFORMANCE CHARACTERISTICS $V_{IN}=3.8V,\,T_A=25^{\circ}C$ unless otherwise noted

## TYPICAL PERFORMANCE CHARACTERISTICS

#### Step-Down Switching Regulator Current Limit vs Temperature

LTC3676-1 VDDQIN, VTTR and

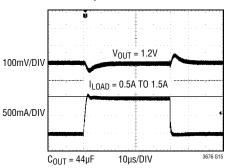

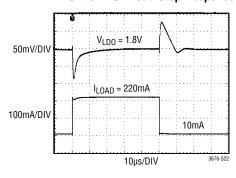

#### Step-Down Switching Regulator Load Step

## TYPICAL PERFORMANCE CHARACTERISTICS

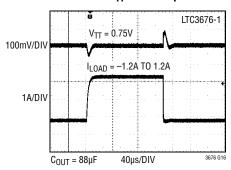

LTC3676-1  $V_{TT}$  Load Step

LDO1 Dropout Voltage vs Temperature

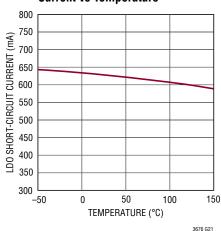

LDO1 Short-Circuit Current vs Temperature

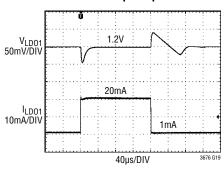

**LD01 Load Step Response**

LDO2 to LDO4 Dropout Voltage vs Temperature

LDO2 to LDO4 Short-Circuit Current vs Temperature

#### LD02 to LD04 Load Step Response

## PIN FUNCTIONS (QFN/LQFP)

**FB\_L2** (**Pin 1/Pin 2**): Feedback Input for LDO2. Set full-scale output voltage using a resistor divider connected from LDO2 to this pin to ground.

$V_{IN\_L2}$  (Pin 2/Pin 3): Power Input for LDO2. This pin should be bypassed to ground with a 1 $\mu$ F or greater ceramic capacitor.Voltage on  $V_{IN\_L2}$  should not exceed voltage on  $V_{IN}$  pin.

**LD02** (**Pin 3/Pin 4**): Output Voltage of LD02. Nominal output voltage is set with a resistor feedback divider that servos to a fixed 725mV reference. This pin must be bypassed to ground with a  $1\mu$ F or greater ceramic capacitor.

**LD03 (Pin 4/Pin 5):** Output Voltage of LD03. Nominal output voltage is a fixed 1.8V. This pin must be bypassed to ground with a 1µF or greater ceramic capacitor.

$V_{IN\_L3}$  (Pin 5/Pin 6): Power Input for LDO3. This pin should be bypassed to ground with a 1µF or greater ceramic capacitor. Voltage on  $V_{IN\_L3}$  should not exceed voltage on  $V_{IN}$  pin.

**LD04** (Pin 6/Pin 7): Output Voltage of LD04. Nominal output voltage is set with a resistor feedback divider that servos to a fixed 725mV reference. This pin must be bypassed to ground with a  $1\mu F$  or greater ceramic capacitor.

$V_{IN\_L4}$  (Pin 7/Pin 8): Power Input for LDO4. This pin should be bypassed to ground with a 1 $\mu$ F or greater ceramic capacitor.Voltage on  $V_{IN\_L4}$  should not exceed voltage on  $V_{IN}$  pin.

**FB\_L4 (Pin 8/Pin 9):** Feedback Input for LTC3676 LDO4. Set full-scale output voltage using a resistor divider connected from LDO4 to this pin to ground.

**VDDQIN (Pin 8/Pin 9):**  $V_{DD}$  Sense Input for LTC3676-1. Tie DDR memory  $V_{DD}$  supply to this pin.

**EN\_L4 (Pin 9/Pin 10):** Enable LDO4 Input for LTC3676. Active high enables LDO4. A weak pull-down pulls EN\_L4 low when left floating.

**VTTR (Pin 9/Pin 10):** DDR V<sub>REF</sub> Output Pin for LTC3676-1. Buffered reference equal to one-half VDDQIN voltage on Pin 8.

**EN\_L3 (Pin 10/Pin 11):** Enable LDO3 Input. Active high enables LDO3. A weak pull-down pulls EN\_L3 low when left floating.

**SW4 (Pin 11/Pin 14):** Switch Pin for Step-Down Switching Regulator 4. Connect one side of step-down switching regulator 4 inductor to this pin.

**DV**<sub>DD</sub> (**Pin 12/Pin 15**): Supply Voltage for I<sup>2</sup>C Serial Port. This pin sets the logic reference level of SCL and SDA I<sup>2</sup>C pins. DV<sub>DD</sub> resets I<sup>2</sup>C registers to power-on state when driven to <1V. SCL and SDA logic levels are scaled to DV<sub>DD</sub>. Connect a 0.1μF decoupling capacitor from this pin to ground.

**SDA (Pin 13/Pin 16):** Data Pin for the I<sup>2</sup>C Serial Port. The I<sup>2</sup>C logic levels are scaled with respect to DV<sub>DD</sub>.

**SCL (Pin 14/Pin 17):** Clock Pin for the I<sup>2</sup>C Serial Port. The I<sup>2</sup>C logic levels are scaled with respect to DV<sub>DD</sub>.

$PV_{IN4}$  (Pin 15/Pin 18): Power Input for Step-Down Switching Regulator 4. Tie this pin to  $V_{IN}$  supply. This pin should be bypassed to ground with a  $10\mu F$  or greater ceramic capacitor.

$PV_{IN3}$  (Pin 16/Pin 19): Power Input for Step-Down Switching Regulator 3. Tie this pin to the  $V_{IN}$  supply. This pin should be bypassed to ground with a 10µF or greater ceramic capacitor.

**EN\_B4 (Pin 17/Pin 20):** Enable Step-Down Switching Regulator 4. Active high input enables step-down switching regulator 4. A weak pull-down pulls EN\_B4 low when left floating.

**EN\_B3** (**Pin 18**//**Pin 21**): Enable Step-Down Switching Regulator 3. Active high input enables step-down switching regulator 3. A weak pull-down pulls EN\_B3 low when left floating.

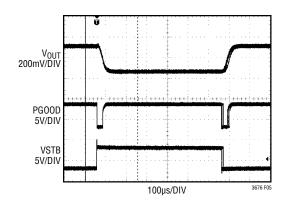

**VSTB** (**Pin 19/Pin 22**): Voltage Standby. When VSTB is low, the DAC registers are selected by command register bit DVBxA[5]. When VSTB is high, the DAC registers are forced to DVBxB registers. Tie VSTB to ground if unused.

**SW3 (Pin 20/Pin 23):** Switch Pin for Step-Down Switching Regulator 3. Connect one side of step-down switching regulator 3 inductor to this pin.

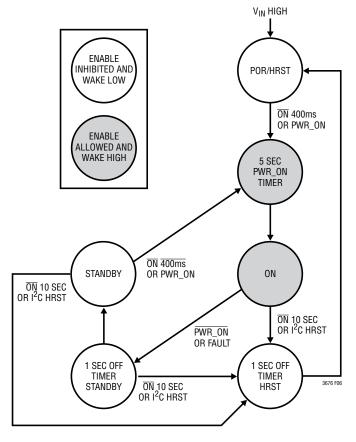

**PWR\_ON (Pin 21/Pin 26):** External Power On. Handshaking pin to acknowledge successful power-on sequence. PWR\_ON must be driven high within five seconds of WAKE going high to keep power on. PWR\_ON can be

## PIN FUNCTIONS

used to activate the WAKE output by driving high. Drive low to shut down WAKE.

**FB\_B3** (**Pin 22/Pin 27**): Feedback Input for Step-Down Switching Regulator 3. Set full-scale output voltage using resistor divider connected from the output of step-down switching regulator 3 to this pin to ground.

**FB\_B4** (**Pin 23/Pin 28**): Feedback Input for Step-Down Switching Regulator 4. Set full-scale output voltage using resistor divider connected from the output of step-down switching regulator 4 to this pin to ground.

**FB\_B1** (**Pin 24/Pin 29**): Feedback Input for Step-Down Switching Regulator 1. Set full-scale output voltage using resistor divider connected from the output of step-down switching regulator 1 to this pin to ground.

**FB\_B2** (**Pin 25/Pin 30**): Feedback Input for Step-Down Switching Regulator 2. Set full-scale output voltage using resistor divider connected from the output of step-down switching regulator 2 to this pin to ground.

**FB\_L1 (Pin 26/Pin 31):** Feedback Input for LDO1. Set output voltage using a resistor divider connected from LDO1 to this pin to ground.

$V_{IN}$  (Pin 27/Pin 32): Supply Voltage Input. This pin should be bypassed to ground with a 1 $\mu$ F or greater ceramic capacitor. All switching regulator PV<sub>IN</sub> supplies should be tied to V<sub>IN</sub>.

**LD01 (Pin 28/Pin 33):** Always On LD01 Output. This pin provides an always-on supply voltage useful for light loads such as a watchdog microprocessor or a real time clock. Connect a 1µF capacitor from LD01 to ground.

**ON** (**Pin 29/Pin 34**): Pushbutton Input. A weak internal pull-up forces **ON** high when left floating. A normally open pushbutton is connected from **ON** to ground forcing a low state when pushed.

**EN\_L2 (Pin 30/Pin 35):** Enable LDO2 Input. Active high enables LDO2. A weak pull-down pulls EN\_L2 low when left floating.

**SW2 (Pin 31/Pin 38):** Switch Pin for Step-Down Switching Regulator 2. Connect one side of step-down switching regulator 2 inductor to this pin.

$\overline{IRQ}$  (Pin 32/Pin 39): Interrupt Request Output. Open-drain driver is pulled low for power good, undervoltage, and overtemperature warning and fault conditions. Clear  $\overline{IRQ}$  by writing to the I<sup>2</sup>C CLIRQ command register.

**WAKE (Pin 33/Pin 40):** System Wake Up. Open-drain driver output releases high when signaled by pushbutton activation or PWR\_ON input. It may be used to initiate a pin-strapped power-up sequence by connecting to a regulator enable pin.

**EN\_B2** (**Pin 34/Pin 41**): Enable Step-Down Switching Regulator 2. Active high input enables step-down switching regulator 2. A weak pull-down pulls EN\_B2 low when left floating.

**PV**<sub>IN2</sub> (**Pin 35/Pin 42**): Power Input for Step-Down Switching Regulator 2. Tie this pin to  $V_{IN}$  supply. This pin should be bypassed to ground with a  $10\mu F$  or greater ceramic capacitor.

**PV**<sub>IN1</sub> (**Pin 36/Pin 43**): Power Input for Step-Down Switching Regulator 1. Tie this pin to  $V_{IN}$  supply. This pin should be bypassed to ground with a  $10\mu F$  or greater ceramic capacitor.

**EN\_B1** (Pin 37/Pin 44): Enable Step-Down Switching Regulator 1. Active high enables step-down switching regulator 1. The LTC3676-1 EN\_B1 pin enables both VTTR output and switching regulator 1. A week pull-down pulls EN B1 low when left floating.

**RSTO** (**Pin 38/Pin 45**): Reset Output. Open-drain output pulls low when the always-on regulator LDO1 is below regulation or during a hard reset initiated by a pushbutton input or command registers.

**PGOOD** (Pin 39/Pin 46): Power Good Output. Open-drain output pulls low when any enabled regulator falls below power good threshold or during dynamic voltage slew unless disabled in command register. Pulls low when all regulators are disabled.

**SW1 (Pin 40/Pin 47):** Switch Pin for Step-Down Switching Regulator 1. Connect one side of step-down switching regulator 1 inductor to this pin.

**GND** (Exposed Pad Pin 41/Pin 49): Ground. The exposed pad must be connected to a continuous ground plane of the printed circuit board by multiple interconnect vias directly under the LTC3676 to maximize electrical and thermal conduction.

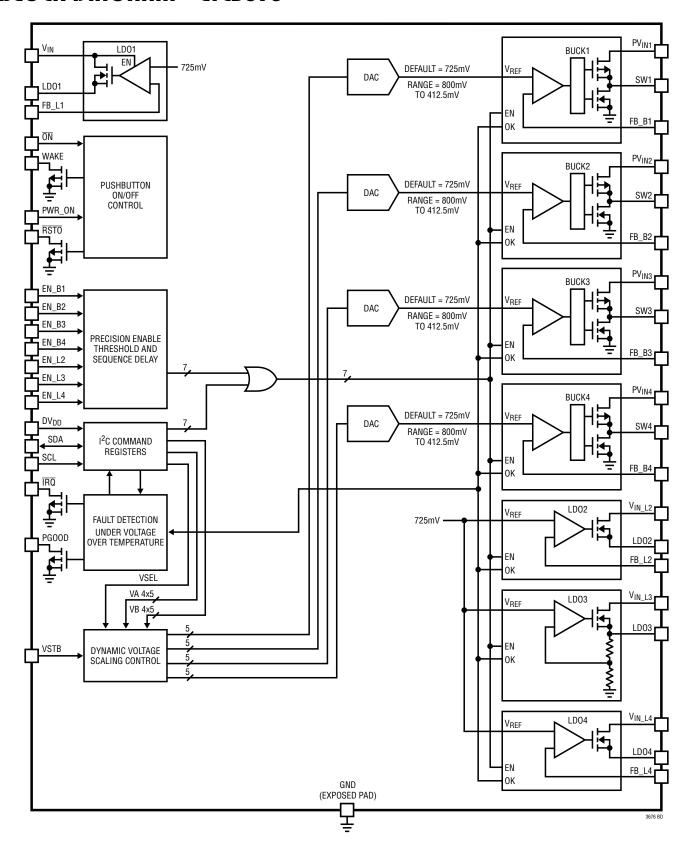

## **BLOCK DIAGRAM—LTC3676**

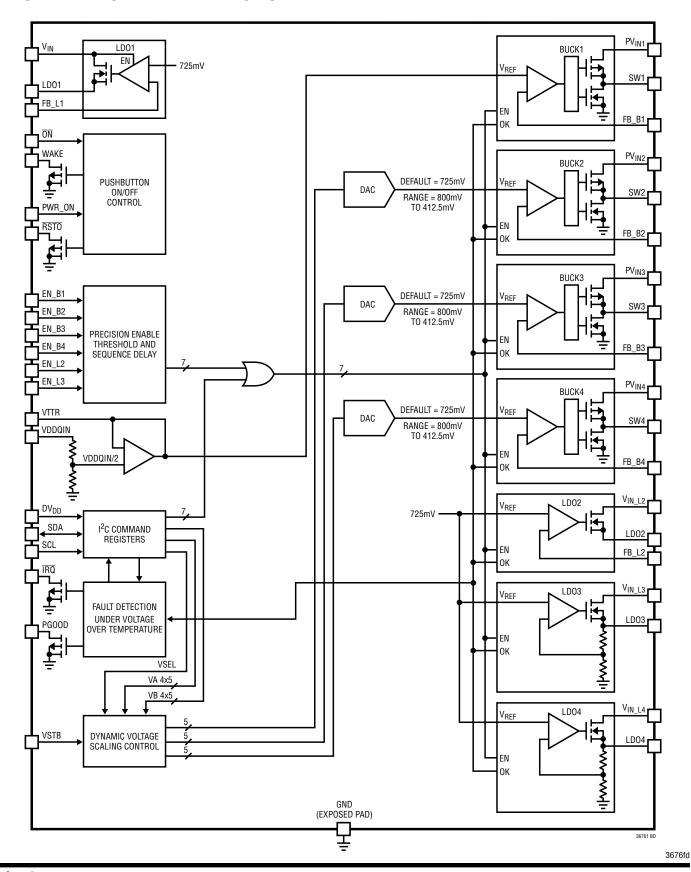

## **BLOCK DIAGRAM—LTC3676-1**

### INTRODUCTION

The LTC3676 is a complete power management solution for portable microprocessors and peripheral devices. It generates a total of eight voltage rails for supplying power to the processor core, DDR memory, I/O, always-on real-time clock and HDD functions. Supplying the voltage rails are an always-on low quiescent current 25mA LDO, two 2.5A step-down regulators, two 1.5A step-down regulators, and three 300mA low dropout regulators. Supporting the multiple regulators is a highly configurable power-on sequencing capability, dynamic voltage scaling DAC output voltage control, a pushbutton interface controller, control via an I<sup>2</sup>C interface, and extensive status and interrupt outputs.

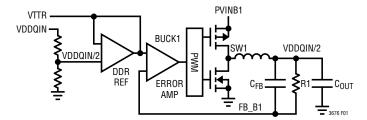

The LTC3676-1 supports DDR memory applications by replacing the LTC3676 LDO4 feedback and enable pins with VDDQIN and VTTR pins. The DDR  $V_{DD}$  supply is connected to the LTC3676-1 VDDQIN pin. A buffered DDR termination voltage equal to one half the voltage on VDDQIN is output on VTTR. The VTTR voltage is connected internally on the LTC3676-1 to the reference side of the Buck1 error amplifier. When Buck1 is configured with a gain of one, its output can be used as at DDR termination supply. Table 1 shows the functional differences between the LTC3676 and LTC3676-1.

Table 1. Functional Differences LTC3676 vs LTC3676-1

|                                    | LTC3676                                             | LTC3676-1                                       |

|------------------------------------|-----------------------------------------------------|-------------------------------------------------|

| Buck1 Default<br>Frequency         | 2.25MHz                                             | 1.125MHz                                        |

| Buck1 Default<br>Mode              | Pulse-Skipping                                      | Forced Continuous                               |

| Buck1 Output                       | External Resistor Divider.<br>Slewing DAC Reference | External Unity Gain.<br>VTTR Reference          |

| LD04 Enable                        | EN_L4 Pin or I <sup>2</sup> C                       | I <sup>2</sup> C                                |

| LDO4 Output                        | External Resistor Divider.<br>725mV Reference       | I <sup>2</sup> C Select 1 of 4 Fixed<br>Outputs |

| FB_L4 Pin                          | External Resistor Divider                           | _                                               |

| EN_L4 Pin                          | Enable LD04.                                        | _                                               |

| VDDQIN Pin                         | _                                                   | Connect to DDR Memory<br>Supply                 |

| VITR Pin                           | _                                                   | Buffered Output Equals<br>One-Half VDDQIN       |

| I <sup>2</sup> C Device<br>Address | Write = 0x78<br>Read = 0x79                         | Write = 0x7A<br>Read = 0x7B                     |

Figure 1.  $V_{TT}$  Buck Regulator and VTTR Reference Block Diagram

#### Always-On 25mA Low Dropout Regulator

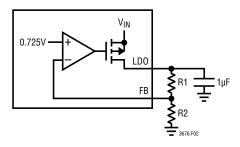

The LTC3676 includes a low quiescent current low dropout regulator that remains powered whenever a valid supply is present on V<sub>IN</sub>. The always-on LD01 remains active until V<sub>IN</sub> drops below 2.0V (typical). This is below the 2.5V undervoltage threshold in effect for the rest of the LTC3676 circuits. The always-on LDO is used to provide power to a standby microcontroller, real-time clock, or other keep-alive circuits. The LDO is guaranteed to support a 25mA load. A 1µFlow impedance ceramic bypass capacitor from LDO1 to GND is required for compensation. A power good monitor pulls RSTO low whenever LDO1 is 8% below its regulation target. LD01 has current limit circuitry to protect from short circuit and overloading. The output voltage of LDO1 is set with a resistor divider connected from LDO1 output pin to the feedback pin FB L1, as shown in Figure 2. The output voltage is calculated using the following formula:

$$V_{LD01} = 725 \cdot \left(1 + \frac{R1}{R2}\right) (mV)$$

#### **300mA Low Dropout Regulators**

Three LDO regulators on the LTC3676 will each deliver up to 300mA output. Each LDO regulator has separate input supply to help manage power loss in the LDO output devices. The LDO regulators are enabled by pin input or  $I^2C$  command register. When disabled, the regulator outputs are pulled to ground through a 625 $\Omega$  resistor. A low ESR 1 $\mu F$  ceramic capacitor should be tied from the LDO output to ground. The 300mA LDO regulators have current limit control circuits. The LDO input voltages,  $V_{IN\_L2},\,V_{IN\_L3},\,$  and  $V_{IN\_L4}$  must be at potential of  $V_{IN}$  or less.

The LDO regulator I<sup>2</sup>C command register controls are shown in Table 2 and Table 3.

### LTC3676 Resistor Programmable LDO2 and LDO4

LDO2 and LDO4 output voltages are programmed by resistor dividers tied from the LDO output pin to the feedback pin as shown in Figure 2. The output voltage is calculated using the following formula:

$$V_{LDO} = 725 \bullet \left(1 + \frac{R1}{R2}\right) (mV)$$

Figure 2. LD01, LD02 and LD04 Application Circuit

#### **Fixed Output LD03**

Regulator LD03 has a fixed voltage output of 1.8V.

Table 2. LD02 and LD03 Control Command Register Settings

|                          | uu ==   | ee common communa regioner commige                                                |

|--------------------------|---------|-----------------------------------------------------------------------------------|

| COMMAND<br>REGISTER[BIT] | VALUE   | SETTING                                                                           |

| LDOA[0]                  | 0*<br>1 | Do Not Keep Alive LD02 in Standby<br>Keep Alive LD02 in Standby                   |

| LDOA[1]                  | 0*<br>1 | Enable LDO2 at Any Output Voltage<br>Enable LDO2 Only if Output Voltage is <300mV |

| LDOA[2]                  | 0*<br>1 | LD02 Disabled if EN_L2 is Low<br>LD02 Enable                                      |

| LDOA[3]                  | 0*<br>1 | Do Not Keep Alive LD03 in Standby<br>Keep Alive LD03 in Standby                   |

| LDOA[4]                  | 0*<br>1 | Enable LDO3 at Any Output Voltage<br>Enable LDO3 Only if Output Voltage is <300mV |

| LDOA[5]                  | 0*<br>1 | LD03 Disabled if EN_L3 is Low<br>LD03 Enabled                                     |

<sup>\*</sup>denotes default power-on value.

### LDO4 Operation LTC3676-1

LDO4 on the LTC3676-1 has neither enable nor feedback pins. There are four LDO4 output voltages selectable by command register bits LDOB[4:3]. The power-on default

output is 1.2V with selectable outputs of 2.5V, 2.8V, and 3.0V. LDO4 is enabled only through the command register bit LDOB[2].

#### **LD04 Command Register Controls**

**Table 3. LD04 Control Command Register Settings**

| COMMAND<br>REGISTER[BIT] | VALUE   | SETTING                                                                           |

|--------------------------|---------|-----------------------------------------------------------------------------------|

| LDOB[0]                  | 0*<br>1 | Do Not Keep Alive LD04 in Standby<br>Keep Alive LD04 in Standby                   |

| LDOB[1]                  | 0*<br>1 | Enable LDO4 at Any Output Voltage<br>Enable LDO4 Only if Output Voltage is <300mV |

| LD0B[2]<br>(LTC3676)     | 0*<br>1 | LDO4 Disabled if EN_L4 is Low<br>LDO4 Enabled                                     |

| LD0B[2]<br>(LTC3676-1)   | 0*<br>1 | LD04 Disabled<br>LD04 Enabled                                                     |

| LD0B[4:3]<br>(LTC3676-1) | 00*     | LDO4 Output = 1.2V                                                                |

| LD0B[4:3]<br>(LTC3676-1) | 01      | LD04 Output = 2.5V                                                                |

| LD0B[4:3]<br>(LTC3676-1) | 10      | LDO4 Output = 2.8V                                                                |

| LDOB[4:3]<br>(LTC3676-1) | 11      | LDO4 Output = 3V                                                                  |

<sup>\*</sup>denotes default power-on value.

#### STEP-DOWN SWITCHING REGULATORS

The LTC3676 contains four buck regulators. Two of the buck regulators are capable of delivering up to 2.5A load current and the other two can deliver up to 1.5A each. The regulators have forward and reverse current limiting, soft-start, and switch slew rate control for lower radiated EMI.

The LTC3676 buck regulators are capable of 100% duty cycle, or dropout, regulation. When in dropout the regulator output voltage is equal to  $PV_{IN}$  minus the load current times  $R_{DS(ON)}$  of the converters PMOS device and inductor DCR.

Each buck regulator is enabled using its enable pin or  $I^2C$  command register control. Operating modes, start-up option, reference voltage, and switch slew rate are controlled using the  $I^2C$  port.

The buck converter I<sup>2</sup>C command register controls are shown in Table 4, Table 5, Table 6, and Table 7.

#### **Operating Modes**

The buck regulators can operate in either pulse-skipping, Burst Mode operation, or forced continuous mode. In pulse-skipping setting the regulator will skip pulses at light loads but will operate at constant frequency. In Burst Mode setting the regulator operates in Burst Mode operation at light loads and in constant frequency PWM mode at higher load. In forced continuous setting the inductor current is allowed to be less than zero over the full range of duty cycles. In forced continuous operation the buck regulator has the ability to sink output current. Because the regulator is switching every cycle regardless of output load, forced continuous mode results in the least output voltage ripple at light load.

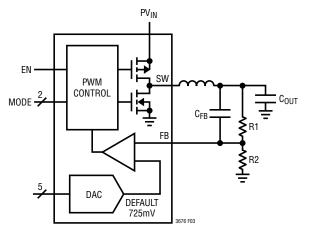

#### **Output Voltage Programming**

Each of the step-down converters uses a dynamically slewing DAC for its reference. The output voltage of the DAC reference is selectable using a 5-bit I<sup>2</sup>C command register. The output voltage is set by using a resistor divider connected from the step-down switching regulator output to its feedback pin as shown in Figure 3. The output voltage is calculated using the following formula:

$$V_{OUT} = \left(1 + \frac{R1}{R2}\right) \cdot (DVBx \cdot 12.5 + 412.5) (mV)$$

DVBx is the decimal value of the 5-bit binary number in the I<sup>2</sup>C command registers. The default DAC input code is 11001 (25 in decimal) which corresponds to a reference

Figure 3. Step-Down Switching Regulator Application Circuit

voltage of 725mV. Typical values for R1 are in the range of 40k to 1M. Capacitor  $C_{FB}$  cancels the pole created by the feedback resistors and the input capacitance on the FB pin and helps to improve load step transient response. A value of 10pF is recommended.

#### **Inductor Selection**

The choice of step-down switching regulator inductor influences the efficiency and output voltage ripple of the converter. A larger inductor improves efficiency since the peak current is closer to the average output current. Larger inductors generally have higher series resistance that counters the efficiency advantage of reduced peak current.

Inductor ripple current is a function of switching frequency, inductance,  $V_{IN}$ , and  $V_{OUT}$  as shown in this equation:

$$\Delta I_{L} = \frac{1}{f \cdot L} \cdot V_{OUT} \cdot \left( 1 - \frac{V_{OUT}}{V_{IN}} \right)$$

A good starting design point is to use an inductor that gives ripple equal to 30% output current. Select an inductor with a DC current rating at least 1.5 times larger than the maximum load current to ensure the inductor does not saturate.

## **Input and Output Capacitor Selection**

Low ESR ceramic capacitors should be used at both the output and input supply of the switching regulators. Only X5R or X7R ceramic capacitors should be used since they have better temperature and voltage stability than other ceramic types.

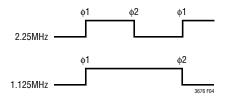

## **Operating Frequency**

The switching frequency of each of the LTC3676 switching regulators may be set using the I<sup>2</sup>C command registers. The default switching frequency is 2.25MHz and the selectable frequency is 1.125MHz. Operation at lower frequency improves efficiency by reducing internal gate charge and switching losses at the expense of a larger inductor.

The lowest duty cycle of the step-down converter is determined by minimum on-time. Minimum on-time is the shortest time duration that the converter can turn its top PMOS on and off again. The time is the sum of gate charge

time plus internal delays of the peak current sense and PWM control. If the converters duty cycle will be 20% or less at 2.25MHz it is recommended to use the 1.125MHz setting to avoid minimum duty cycle. If the duty cycle falls below the minimum on-time of the converter, the output voltage ripple will increase as the converter skips cycles.

The default setting for the LTC3676-1 Buck1 switching frequency is 1.125MHz to ensure minimum on time effects are avoided at DDR termination reference voltages.

#### Phase Selection

To reduce the cycle by cycle peak current drawn by the switching regulators, the clock phase at which each of the LTC3676 buck's PMOS switch turns on can be set using I<sup>2</sup>C command register settings.

Figure 4. Phase Settings Full- and Half-Speed Buck Clock

#### Switch Slew Rate Control

To help reduce EMI the switch rise time of each buck regulator is slew limited by default. A faster setting is selectable using the I<sup>2</sup>C buck command registers. The faster setting will improve efficiency if limited edge rate is not required.

#### Soft-Start

To reduce inrush current at start-up each buck regulator soft starts when enabled. When enabled the internal reference voltage is ramped from ground to the level of the slewing DAC output at a rate of 0.8V/ms. During soft-start the converter is forced to pulse-skipping mode regardless of command register mode settings.

Table 4. Buck1 Control Command Register

| COMMAND<br>REGISTER[BIT] | VALUE           | SETTING                                                                 |

|--------------------------|-----------------|-------------------------------------------------------------------------|

| BUCK1[0]                 | 0*<br>1         | Switch Slew Rate Normal<br>Switch Slew Rate Fast                        |

| BUCK1[1]                 | 0*<br>1         | Do Not Keep Enabled in Device Standby<br>Keep Enabled in Device Standby |

| BUCK1[2]<br>(LTC3676)    | 0*<br>1         | Switching Frequency 2.25MHz<br>Switching Frequency 1.125MHz             |

| BUCK1[2]<br>(LTC3676-1)  | 0*<br>1         | Switching Frequency 1.125MHz<br>Switching Frequency 2.25MHz             |

| BUCK1[3]                 | 0*<br>1         | Clock Phase 1<br>Clock Phase 2                                          |

| BUCK1[4]                 | 0*<br>1         | Enable at Any Output Voltage<br>Enable Only if Output Voltage Is <300mV |

| BUCK1[6:5]               | 00*<br>01<br>10 | Pulse-Skipping Mode<br>Burst Mode Operation<br>Forced Continuous Mode   |

| BUCK1[7]                 | 0*<br>1         | Buck1 Disabled if EN_B1 Pin Is Low<br>Buck1 Enabled                     |

<sup>\*</sup>denotes default power on-value.

**Table 5. Buck2 Control Command Register**

|                          | l               |                                                                         |

|--------------------------|-----------------|-------------------------------------------------------------------------|

| COMMAND<br>Register[bit] | VALUE           | SETTING                                                                 |

| BUCK2[0]                 | 0*<br>1         | Switch Slew Rate Normal<br>Switch Slew Rate Fast                        |

| BUCK2[1]                 | 0*<br>1         | Do Not Keep Enabled in Device Standby<br>Keep Enabled in Device Standby |

| BUCK2[2]                 | 0*<br>1         | Switching Frequency 2.25MHz<br>Switching Frequency 1.125MHz             |

| BUCK2[3]                 | 0*<br>1         | Clock Phase 1<br>Clock Phase 2                                          |

| BUCK2[4]                 | 0*<br>1         | Enable at Any Output Voltage<br>Enable Only if Output Voltage Is <300mV |

| BUCK2[6:5]               | 00*<br>01<br>10 | Pulse-Skipping Mode<br>Burst Mode Operation<br>Forced Continuous Mode   |

| BUCK2[7]                 | 0*<br>1         | Buck2 Disabled if EN_B2 Pin Is Low<br>Buck2 Enabled                     |

<sup>\*</sup>denotes default power-on value.

Table 6. Buck3 Control Command Register

| COMMAND<br>REGISTER[BIT] | VALUE           | SETTING                                                                 |

|--------------------------|-----------------|-------------------------------------------------------------------------|

| BUCK3[0]                 | 0*<br>1         | Switch Slew Rate Normal<br>Switch Slew Rate Fast                        |

| BUCK3[1]                 | 0*<br>1         | Do Not Keep Enabled in Device Standby<br>Keep Enabled in Device Standby |

| BUCK3[2]                 | 0*<br>1         | Switching Frequency 2.25MHz<br>Switching Frequency 1.125MHz             |

| BUCK3[3]                 | 0*<br>1         | Clock Phase 1<br>Clock Phase 2                                          |

| BUCK3[4]                 | 0*<br>1         | Enable at Any Output Voltage<br>Enable Only if Output Voltage Is <300mV |

| BUCK3[6:5]               | 00*<br>01<br>10 | Pulse-Skipping Mode<br>Burst Mode Operation<br>Forced Continuous Mode   |

| BUCK3[7]                 | 0*<br>1         | Buck3 Disabled if EN_B3 Pin Is Low<br>Buck3 Enabled                     |

<sup>\*</sup>denotes default power-on value.

Table 7. Buck4 Control Command Register

| COMMAND<br>REGISTER[BIT] | VALUE           | SETTING                                                                 |

|--------------------------|-----------------|-------------------------------------------------------------------------|

| BUCK4[0]                 | 0*<br>1         | Switch Slew Rate Normal<br>Switch Slew Rate Fast                        |

| BUCK4[1]                 | 0*<br>1         | Do Not Keep Enabled in Device Standby<br>Keep Enabled in Device Standby |

| BUCK4[2]                 | 0*<br>1         | Switching Frequency 2.25MHz<br>Switching Frequency 1.125MHz             |

| BUCK4[3]                 | 0*<br>1         | Clock Phase 1<br>Clock Phase 2                                          |

| BUCK4[4]                 | 0*<br>1         | Enable at Any Output Voltage<br>Enable Only if Output Voltage Is <300mV |

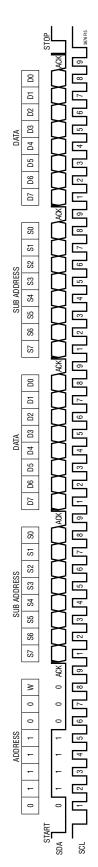

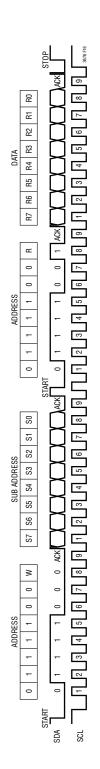

| BUCK4[6:5]               | 00*<br>01<br>10 | Pulse-Skipping Mode<br>Burst Mode Operation<br>Forced Continuous Mode   |