Midas Components Limited Electra House 32 Southtown Road Great Yarmouth Norfolk NR31 0DU England Telephone Fax Email Website +44 (0)1493 602602 +44 (0)1493 665111 sales@midasdisplays.com www.midasdisplays.com

|                          |      |      | Specification |            |  |  |  |

|--------------------------|------|------|---------------|------------|--|--|--|

| Part MCT057CA6W320240LWL |      |      |               |            |  |  |  |

| Num                      | ber: |      | 010070700000  | /202+0LVVL |  |  |  |

| Versi                    | on:  |      |               |            |  |  |  |

| Date                     | •    |      |               |            |  |  |  |

|                          |      | A    | Revision      |            |  |  |  |

| No.                      | Date |      | Description   | Item Page  |  |  |  |

|                          |      |      |               |            |  |  |  |

|                          | desi | gn • | manufacture   | e supply   |  |  |  |

# **Contents**

|     |                                   | Page |

|-----|-----------------------------------|------|

| 2.  | General Specification             | 4    |

| 3.  | Module Classification Information | 5    |

| 4.  | Interface Pin Function            | 6    |

| 5.  | Contour drawing                   | 7    |

| 6.  | Block Diagram                     | 8    |

| 7.  | Absolute Maximum Ratings          | 9    |

|     | Electrical Characteristics        | 10   |

| 9.  | DC Characteristics                | 10   |

| 10. | AC Characteristics                | 11   |

| 11. | Optical Characteristics           | 14   |

| 12. | Reliability                       | 16   |

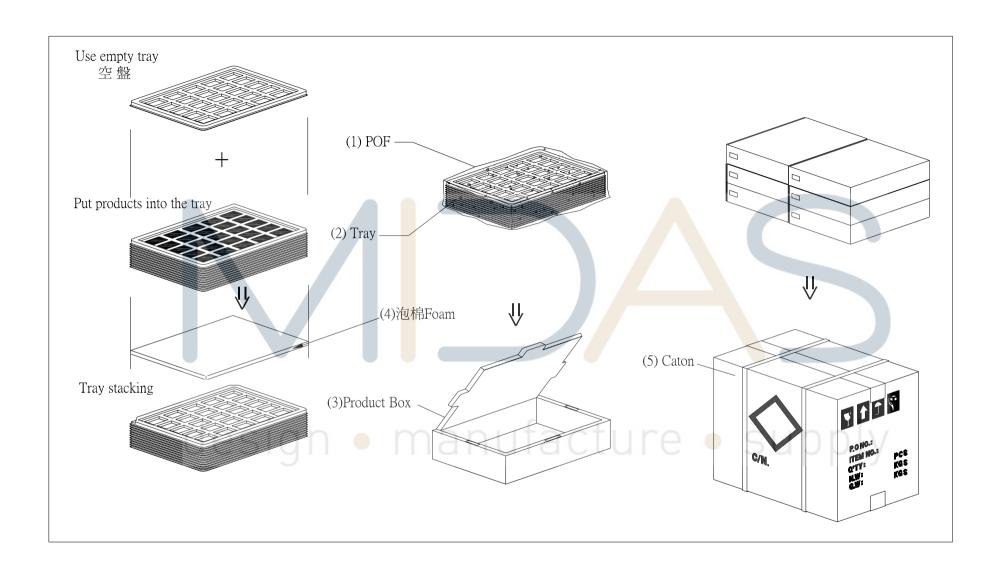

| 13. | Package specification             | 17   |

| 14. | Initial Code For Reference        | 19   |

|     |                                   |      |

design • manufacture • supply

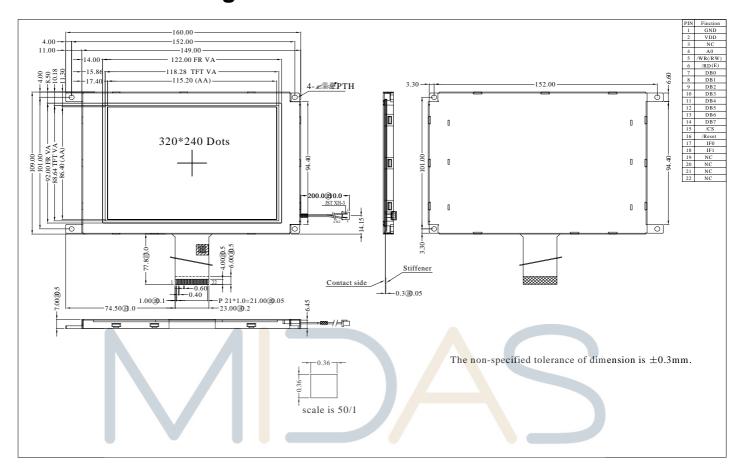

# 2. General Specification

■ Resolution: 320 x RGBx240

■ Module dimension: 160.0 x 109.0 x 7.0 mm

■ Active Area: 115.2 x 86.4mm

■ Dot pitch: 0.36 x 0.36 mm

■ LCD type: TFT, Positive, Transmissive

■ View direction: 12 o'clock

■ Gray Scale Inversion Direction: 6 o'clock

■ Backlight Type: LED, Normally White

\*Color tone slight changed by temperature and driving voltage.

design • manufacture • supply

## Midas Active Matrix Display Part Number System

MC 320240 057 3 5 6 11 2 7 9 10 12 13 15 1 8 14 16

- 1 = **MC:** Midas Components

- 2 = **T:** TFT**A:** Active Matrix OLED

- 3 = **Size**

- 4 = Series

- 5 = Viewing Angle: 6: 6 O'clock12: 12 O'clock

- 6 = **Blank:** No Touch **T:** Resistive Touchscreen **C:** Capacitive Touchscreen

- 7 = Operating Temp Range: S: 0 to 50Deg C B: -20+60Deg C

- W: -20+70Deg C E: -30+85Deg C

- 8 = No of Pixels

- 9 = **Orientation**: **P**: Portrait **L**: Landscape

- 10 = **Mode:** R: Reflective **M:** Transmissive **T:** Transflective **S:** Sunlight Readable (transmissive)

- W: White on Black (Monochrome)

- 11 = **Backlight:** Blank: None L: LED C: CCFL

- 12 = **Blank:** No Module/board **C:** Controller board module

- 13 = **Blank:** None V: Video

- 14 = **Blank:** None **B**: Bracket

- 15 = **Blank:** None **H**: Host Cable

- 16 = **Blank:** None **K**: Keyboard

## 4. Interface Pin Function

### 4.1. LCM PIN Definition

| Pin | Symbol       | Function                      | Remark |

|-----|--------------|-------------------------------|--------|

| 1   | GND          | System ground                 |        |

| 2   | VDD          | Power Supply: +3.3V           |        |

| 3   | NC           | No connect                    |        |

| 4   | A0           | Data/Command select           |        |

| 5   | /WR(R/W)     | Write strobe signal           |        |

| 6   | /RD(E)       | Read strobe signal            |        |

| 7   | DB0          | Data bus                      |        |

| 8   | DB1          | Data bus                      |        |

| 9   | DB2          | Data bus                      |        |

| 10  | DB3          | Data bus                      |        |

| 11  | DB4          | Data bus                      |        |

| 12  | DB5          | Data bus                      |        |

| 13  | DB6          | Data bus                      |        |

| 14  | DB7          | D <mark>at</mark> a bus       |        |

| 15  | /CS          | Chip select                   |        |

| 16  | /RESET(RSTB) | H <mark>a</mark> rdware reset |        |

| 17  | IF0          | Mode select                   | Note1  |

| 18  | IF1          | Wode Select                   | Note   |

| 19  | NC           | No connect                    |        |

| 20  | NC           | No connect                    |        |

| 21  | NC           | No connect                    |        |

| 22  | 1 AS NC N    | No connect                    | ) \/   |

#### Note1:

| Setting |     | MCU Type                 | Interface Pin Function |    |     |     |                        |  |  |

|---------|-----|--------------------------|------------------------|----|-----|-----|------------------------|--|--|

| IF1     | IF0 | wico rype                | CSB                    | A0 | RWR | ERD | D[7:0]                 |  |  |

| L       | L   | Parallel 8080 series MCU |                        |    | /WR | /RD | D[7:0]                 |  |  |

| L       | Н   | Parallel 6800 series MCU | CSB                    | A0 | R/W | Е   | D[7.0]                 |  |  |

| Н       | Н   | Serial 4-Line series MCU | CSB                    |    | -   | -   | D7=SCL, D0=SDA, D[6:1] |  |  |

| Н       | L   | Serial 3-Line series MCU |                        | -  | -   | -   | are not used           |  |  |

The un-used pins are marked as "-" and should be connected to "H" by VDDI.

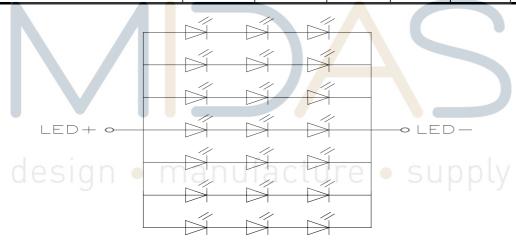

## 4.2. Backlight Unit Section(CN2)

LED Light Bar connector is used for the the integral backlight system. The recommended model is "JST XH-3" manufactured by JST.

| Pin No. | Symbol | I/O | Function                            | Remark |

|---------|--------|-----|-------------------------------------|--------|

| 1       | VLED+  | Р   | Power for LED backlight anode (A)   | Red    |

| 3       | VLED-  | Р   | Power for LED backlight cathode (K) | White  |

# 5. Contour Drawing

design • manufacture • supply

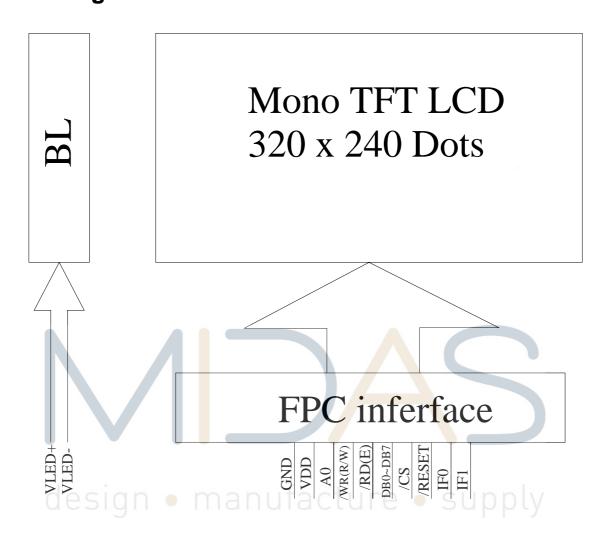

# 6. Block Diagram

# 7. Absolute Maximum Ratings

| Item                  | Symbol | Min | Тур | Max | Unit       |

|-----------------------|--------|-----|-----|-----|------------|

| Operating Temperature | TOP    | -20 | _   | +70 | $^{\circ}$ |

| Storage Temperature   | TST    | -30 | _   | +80 | $^{\circ}$ |

Note: Device is subject to be damaged permanently if stresses beyond those absolute maximum ratings listed above

1. Temp.  $\, \leq \! 60 \, ^{\circ}\! \text{C}$  , 90% RH MAX. Temp.  $\! > \! 60 \, ^{\circ}\! \text{C}$  , Absolute humidity shall be less than 90% RH at  $60 \, ^{\circ}\! \text{C}$

## **8. Electrical Characteristics**

## 8.1. Operating conditions:

| Item                   | Symbol | Condition | Min | Тур | Max | Unit | Remark |

|------------------------|--------|-----------|-----|-----|-----|------|--------|

| Supply Voltage For LCM | VDD    | _         | 3.0 | 3.3 | 3.6 | V    |        |

| Supply Current For LCM | IDD    | _         | _   | 20  | 30  | mA   | Note1  |

| Power Consumption      | _      | _         | _   | 66  | 108 | mW   |        |

Note1: This value is test for VDD=3.3V only

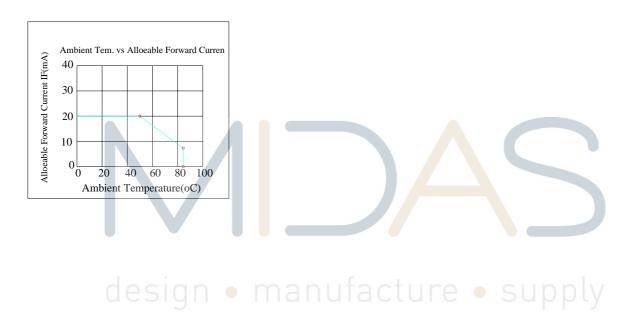

## 8.2. LED driving conditions

| Parameter         | Symbol | Min. | Тур.   | Max. | Unit | Remark     |

|-------------------|--------|------|--------|------|------|------------|

| LED current       |        | -    | 140    | -    | mA   |            |

| Power Consumption |        | 1120 | -      | 1386 | mW   |            |

| LED voltage       | VLED+  | 8.0  | 9.0    | 9.9  | V    | Note 1     |

| LED Life Time     |        | -    | 50,000 | -    | Hr   | Note 2,3,4 |

Note 1: Power supply the back light specification

Note 2 : Ta = 25 ℃

Note 3: Brightness to be decreased to 50% of the initial value

Note 4: The single LED lamp case

## 9. DC CHARATERISTICS

| Parameter                   | Symbol |        | Rating |        | Unit | Condition |  |

|-----------------------------|--------|--------|--------|--------|------|-----------|--|

| T di difficter              | Cymbol | Min    | Тур    | Max    | Onit | Condition |  |

| Low level input voltage     | VIL    | 0      | -      | 0.3VDD | V    |           |  |

| High level input<br>voltage | ViH    | 0.7VDD | -      | VDD    | V    |           |  |

## 10.AC Characteristics

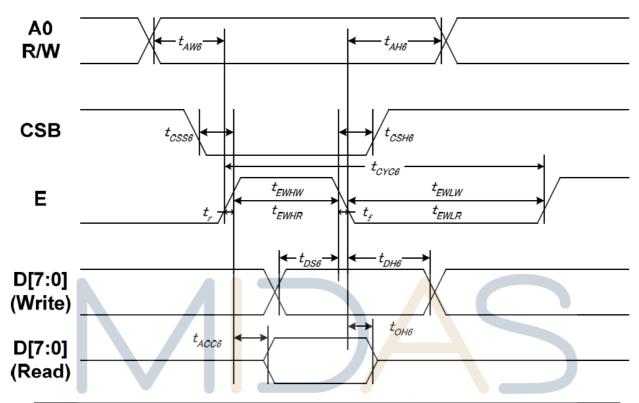

### 10.1. System Bus Timing for 6800 Series MPU

| Item                          | Signal | Symbol | Condition   | Min | Max    | Unit |

|-------------------------------|--------|--------|-------------|-----|--------|------|

| Address setup time            | A0     | tAW6   | T           | 10  |        |      |

| Address hold time             |        | tAH6   | ture •      | 50  | ) D-LV | /    |

| System cycle time             |        | tCYC6  | -           | 200 | - 7    |      |

| Enable L pulse width (WRITE)  |        | tEWLW  | -           | 100 | -      |      |

| Enable H pulse width (WRITE)  | E      | tEWHW  | -           | 100 | -      |      |

| Enable L pulse width (READ)   |        | tEWLR  | -           | 130 | -      |      |

| Enable H pulse width (READ)   |        | tEWHR  | -           | 130 | -      | ns   |

| CSB setup time                | CSB    | tCSS6  | -           | 100 | -      |      |

| CSB hold time                 | COD    | tCSH6  | -           | 100 | -      |      |

| Write data setup time         |        | tDS6   | -           | 70  | -      |      |

| Write data hold time          | D[7:0] | tDH6   | -           | 20  | -      |      |

| Read data access time         | D[7:0] | tACC6  | CL = 100 pF | -   | 80     |      |

| Read data output disable time |        | tOH6   | CL = 100 pF | 15  | 80     |      |

#### Note:

- 1. The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast,(tr + tf)  $\leq$  (tCYC8 tCCLW tCCHW) for (tr + tf)  $\leq$  (tCYC8 tCCLR tCCHR) are specified.

- 2. All timing is specified using 20% and 80% of VDDI as the reference.

- 3. tCCLW and tCCLR are specified as the overlap between CSB being "L" and /WR and /RD being at the "L" level.CSB and /WR (or /RD) cannot act at the same time and CSB should be 100ns wider than /WR (or /RD).

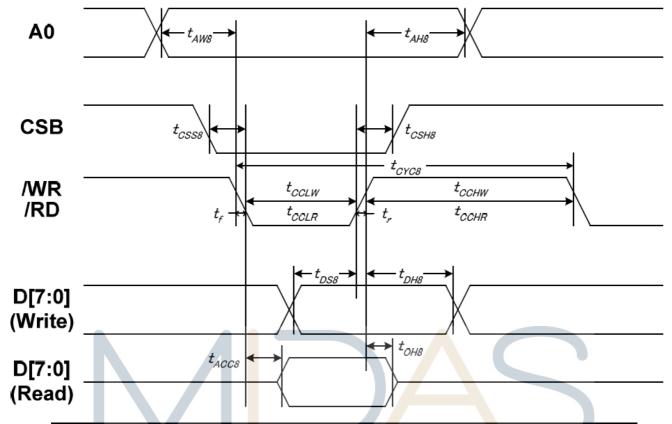

### 10.2. System Bus Timing for 8080 Series MPU

| Item                          | Signal | Symbol | Condition      | Min | Max                          | Unit |

|-------------------------------|--------|--------|----------------|-----|------------------------------|------|

| Address setup time            | A0     | tAW8   | -              | 10  | -                            |      |

| Address hold time             | AU     | tAH8   | -              | 0   | -                            |      |

| System cycle time             |        | tCYC8  | L <del>-</del> | 200 |                              |      |

| /WR L pulse width (WRITE)     | /WR    | tCCLW  | ture •         | 100 | $)$ $\bigcirc$ $\cup$ $\cup$ | /    |

| /WR H pulse width (WRITE)     |        | tCCHW  | -              | 100 | - /                          |      |

| /RD L pulse width (READ)      | /RD    | tCCLR  | -              | 120 | -                            |      |

| /RD H pulse width (READ)      | /KD    | tCCHR  | -              | 120 | -                            | ns   |

| CSB setup time                | CSB    | tCSS8  | -              | 100 | -                            |      |

| CSB hold time                 | CSB    | tCSH8  | -              | 100 | -                            |      |

| Write data setup time         |        | tDS8   | -              | 70  | -                            |      |

| Write data hold time          | D(2:01 | tDH8   | -              | 20  | -                            |      |

| Read data access time         | D[7:0] | tACC8  | CL = 100 pF    | -   | 80                           |      |

| Read data output disable time |        | tOH8   | CL = 100 pF    | 15  | 80                           |      |

#### Note:

- 1. The input signal rise time and fall time (tr, tf) is specified at 15 ns or less. When the system cycle time is extremely fast,(tr + tf)  $\leq$  (tCYC8 tCCLW tCCHW) for (tr + tf)  $\leq$  (tCYC8 tCCLR tCCHR) are specified.

- 2. All timing is specified using 20% and 80% of VDDI as the reference.

- 3. tCCLW and tCCLR are specified as the overlap between CSB being "L" and /WR and /RD being at the "L" level.CSB and /WR (or /RD) cannot act at the same time and CSB should be 100ns wider than /WR (or /RD).

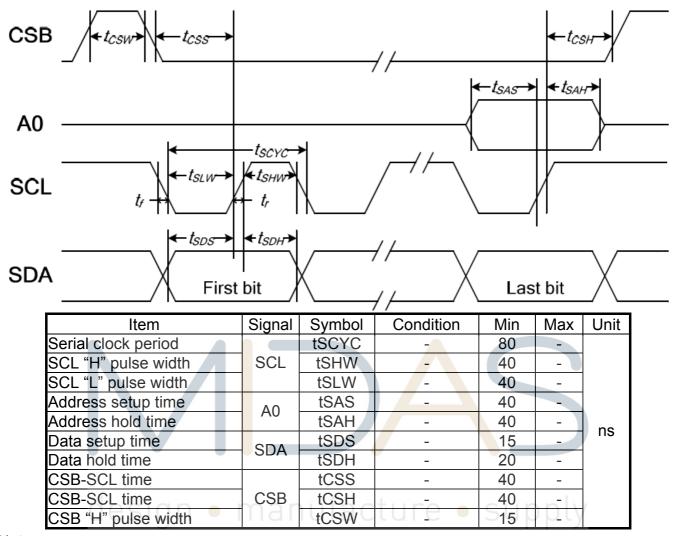

### 10.3. System Bus Timing for 4-Line Serial Interface

#### Note:

- 1. The input signal rise and fall time (tr, tf) are specified at 15 ns or less.

- 2. All timing is specified using 20% and 80% of VDDI as the standard.

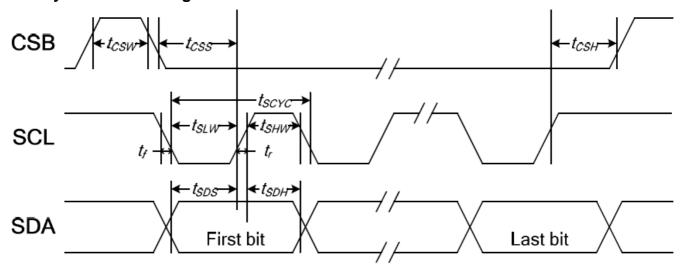

### 10.4. System Bus Timing for 3-Line Serial Interface

| Item                | Signal | Symbol | Condition | Min | Max | Unit |

|---------------------|--------|--------|-----------|-----|-----|------|

| Serial clock period |        | tSCYC  | ı         | 80  | -   |      |

| SCL "H" pulse width | SCL    | tSHW   | ı         | 40  | -   |      |

| SCL "L" pulse width |        | tSLW   | ı         | 40  | -   |      |

| Data setup time     | SDA    | tSDS   | -         | 15  | -   | nc   |

| Data hold time      | SDA    | tSDH   | -         | 20  | -   | ns   |

| CSB-SCL time        |        | tCSS   | -         | 40  | -   |      |

| CSB-SCL time        | CSB    | tCSH   | -         | 40  | -   |      |

| CSB "H" pulse width |        | tCSW   | -         | 15  | -   |      |

#### Note:

- 1. The input signal rise and fall time (tr, tf) are specified at 15 ns or less.

- 2. All timing is specified using 20% and 80% of VDDI as the standard.

## 11. OPTICAL CHARATERISTIC

| Item          |      | Symbol | Condition.                               | Min | Тур. | Max. | Unit  | Remark            |

|---------------|------|--------|------------------------------------------|-----|------|------|-------|-------------------|

| Response time |      | Tr     | θ <mark>=</mark> 0° \ Φ=0°               |     | 20   | 30   | .ms   | Note 3,5          |

|               |      | Tf     |                                          | -   | 10   | 15   | .ms   |                   |

| Contrast rat  | tio  | CR     | A <mark>t optimized viewing angle</mark> | -   | 800  | -    | •     | Note 4,5          |

| Viewing angle | Hor. | ΘR     | CR≧10                                    |     | 60   |      | Dog   | Note 1            |

|               |      | ΘL     |                                          |     | 60   |      |       |                   |

|               | Ver. | ΦТ     |                                          |     | 60   |      | Deg.  |                   |

|               |      | ΦВ     |                                          |     | 50   |      |       |                   |

| Brightness    |      | ign •  | manu                                     | 900 | 1000 | • S  | cd/m² | Center of display |

Ta=25±2℃, IL=140mA

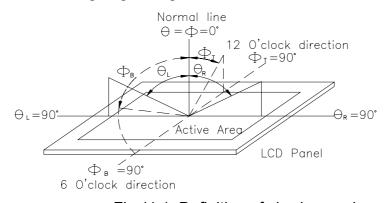

Note 1: Definition of viewing angle range

Fig.11.1. Definition of viewing angle

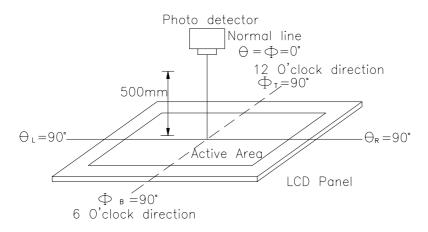

#### Note 2: Test equipment setup:

After stabilizing and leaving the panel alone at a driven temperature for 10 minutes, the measurement should be executed. Measurement should be executed in a stable, windless, and dark room. Optical specifications are measured by Topcon BM-7orBM-5 luminance meter 1.0° field of view at a distance of 50cm and normal direction.

Fig.11.2. Optical measurement system setup

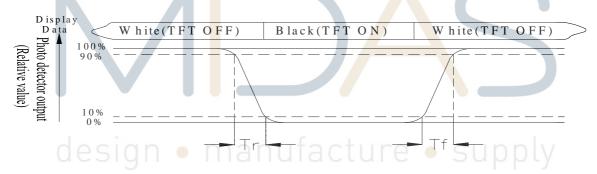

#### Note 3: Definition of Response time:

The response time is defined as the LCD optical switching time interval between "White" state and "Black" state. Rise time, Tr, is the time between photo detector output intensity changed from 90%to 10%. And fall time, Tf, is the time between photo detector output intensity changed from 10%to 90%

Note 4: Definition of contrast ratio:

The contrast ratio is defined as the following expression.

Note 5: White  $Vi = Vi50 \pm 1.5V$

Black  $Vi = Vi50 \pm 2.0V$

"±" means that the analog input signal swings in phase with VCOM signal.

"±" means that the analog input signal swings out of phase with VCOM signal.

The 100% transmission is defined as the transmission of LCD panel when all the input terminals of module are electrically opened.

Note 6: Definition of color chromaticity (CIE 1931)

Color coordinates measured at the center point of LCD

Note 7: Measured at the center area of the panel when all the input terminals of LCD panel are electrically opened.

# 12.Reliability Test

### Content of Reliability Test (Wide temperature, -20°C~70°C)

| Test Item                               | Content of Test                                                                                                                                                           | Test Condition                                                                                                             | Note |

|-----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------|------|

| High Temperature storage                | Endurance test applying the high storage temperature for a long time.                                                                                                     | 80℃<br>200hrs                                                                                                              | 2    |

| Low Temperature storage                 | Endurance test applying the low storage temperature for a long time.                                                                                                      | 200hrs                                                                                                                     | 1,2  |

| High Temperature<br>Operation           | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time.                                                    | 200hrs                                                                                                                     |      |

| Low Temperature Operation               | Endurance test applying the electric stress under low temperature for a long time.                                                                                        | 200hrs                                                                                                                     | 1    |

| High Temperature/<br>Humidity Operation | The module should be allowed to stand at 60℃,90%RH max For 96hrs under no-load condition excluding the polarizer, Then taking it out and drying it at normal temperature. | 60℃,90%RH<br>96hrs                                                                                                         | 1,2  |

| Thermal shock resistance                | The sample should be allowed stand the following 10 cycles of operation  -20°C 25°C 70°C  30min 5min 30min 1 cycle                                                        | 10 cycles                                                                                                                  |      |

| Vibration test                          | Endurance test applying the vibration during transportation and using.                                                                                                    | Total fixed amplitude: 15mm Vibration Frequency: 10~55Hz One cycle 60 seconds to 3 directions of X,Y,Z for Each 15 minutes |      |

| Static electricity test                 | Endurance test applying the electric stress to the terminal.                                                                                                              | VS=800V,RS=1.5kΩ<br>CS=100pF<br>1 time                                                                                     |      |

Note1: No dew condensation to be observed.

Note2: The function test shall be conducted after 4 hours storage at the normal Temperature and humidity after remove from the test chamber.

Note3: The packing have to including into the vibration testing.

# 14.Initial Code For Reference

```

void Initial code()

{

Write_Command(0xae);

Write Data(0xa5);

Write Command(0x61);

Write Data(0x8f);

Write Data(0x04);

Write_Data(0xa5);

Write Data(0xa5);

Write Command(0x62);

Write Data(0x36);

Write Data(0x0b);

Write_Data(0x0b);

Write Data(0xa5);

Write Command(0x33);

Write Data(0x07);

Write_Data(0x2c);

Write Data(0x09);

Write Data(0x2a);

Write Command(0x63);

Write Data(0x09);

Write Data(0x17);

Write Data(0xa5);

Write Data(0xa5);

Write Command(0x91);

Write Data(0x00);

Write Data(0x16);

Write Data(0x1B);

Write_Data(0x1C);

Write Command(0x92);

Write Data(0x1E);

Write_Data(0x1F);

Write Data(0x20);

Write Data(0x21);

```

```

Write_Command(0x93);

Write_Data(0x23);

Write_Data(0x24);

Write_Data(0x26);

Write_Data(0x28);

Write_Command(0x94);

Write_Data(0x2B);

Write Data(0x2F);

Write_Data(0x34);

Write_Data(0x3f);

Write_Command(0x99);

Write_Data(0x00);

Write_Data(0x16);

Write_Data(0x1B);

Write_Data(0x1C);

Write_Command(0x9a);

Write_Data(0x1E);

Write_Data(0x1F);

Write_Data(0x20);

Write_Data(0x21);

Write_Command(0x9b);

Write Data(0x23);

Write_Data(0x24);

Write_Data(0x26);

Write Data(0x28);

Write_Command(0x9c);

Write_Data(0x2B);

Write Data(0x2F);

Write_Data(0x34);

Write_Data(0x3F);

Write_Command(0x12);

Write_Data(0xa5);

Write_Command(0x24);

Write_Data(0x01);

Write_Data(0xa5);

Write_Data(0xa5);

Write_Data(0xa5);

```

```

Write_Command(0x22);

Write_Data(0x00);

Write_Data(0xa5);

Write_Data(0xa5);

Write_Data(0xa5);

Write_Command(0x15);

Write_Data(0xa5);

_nop_();

```

}

design • manufacture • supply