# 5A Integrated Hot Swap Controller

### **FEATURES**

- Reduced 16ms Turn-On Delay

- Small Footprint

- 33mΩ MOSFET with R<sub>SENSE</sub>

- Wide Operating Voltage Range: 2.9V to 15V

- Adjustable, 10% Accurate Current Limit

- Current and Temperature Monitor Outputs

- Overtemperature Protection

- Adjustable Current Limit Timer Before Fault

- Power Good and Fault Outputs

- Adjustable Inrush Current Control

- 2% Accurate Undervoltage and Overvoltage Protection

- Pin Compatible with LTC4217 (DFN Package Only)

- Available in 16-Lead 5mm × 3mm DFN Package

### **APPLICATIONS**

- RAID Systems, Solid State Drives

- Server I/O Cards

- PCI Express Systems

- Industrial

### DESCRIPTION

The LTC®4232-1 is an integrated solution for Hot Swap™ applications that allows a board to be safely inserted and removed from a live backplane. The part integrates a Hot Swap controller, power MOSFET and current sense resistor in a single package for small form factor applications.

The LTC4232-1 provides separate inrush current control and a 10% accurate 5A current limit with foldback current limiting. The current limit threshold can be adjusted dynamically using an external pin. Additional features include a current monitor output that amplifies the sense resistor voltage for ground referenced current sensing and a MOSFET temperature monitor output. Thermal limit, overvoltage, undervoltage and power good monitoring are also provided.

The PCI Express compliant LTC4232-1 allows faster turn-on than the LTC4232 by providing a shorter (16ms) debounce delay and external control of the GATE ramp rate.

LT, LTC, LTM, Linear Technology and the Linear logo are registered trademarks of Linear Technology Corporation. Hot Swap and PowerPath are trademarks of Linear Technology Corporation. All other trademarks are the property of their respective owners.

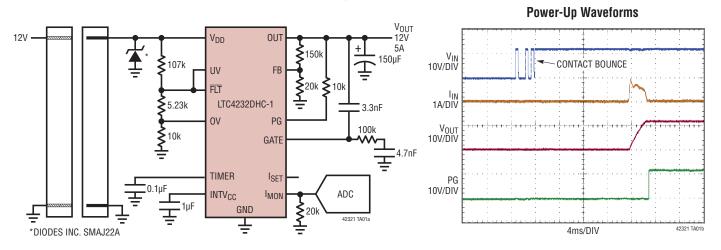

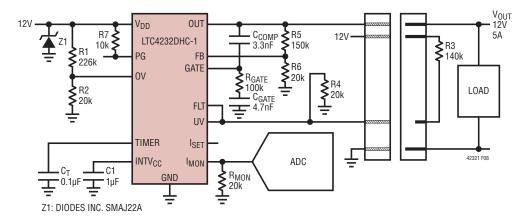

# TYPICAL APPLICATION

12V, 5A Card Resident Application with Auto-Retry

/ LINEAR

# **ABSOLUTE MAXIMUM RATINGS**

#### (Notes 1, 2)

| Supply Voltage (V <sub>DD</sub> )   | _0 3\/ to 28\/ |

|-------------------------------------|----------------|

| Input Voltages                      | 0.00 10 200    |

| . 0                                 | 0.071.407      |

| FB, OV, UV                          | 0.3V to 12V    |

| TIMER                               | 0.3V to 3.5V   |

| SENSEV <sub>DD</sub> –              |                |

| Output Voltages                     |                |

| I <sub>SET</sub> , I <sub>MON</sub> | 0.3V to 3V     |

| PG, FLT                             | 0.3V to 35V    |

| OUT                                 |                |

| INTV <sub>CC</sub>                  | 0.3V to 3.5V   |

| GATE (Note 3)                       | 0.3V to 33V    |

| Operating Temperature Range         |                |

| LTC4232C-1                          | 0°C to 70°C    |

| LTC4232I-1                          | 40°C to 85°C   |

| Junction Temperature (Notes 4, 5).  | 125°C          |

| Storage Temperature Range           | 65°C to 150°C  |

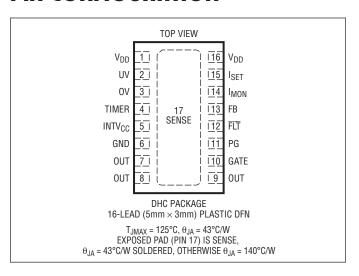

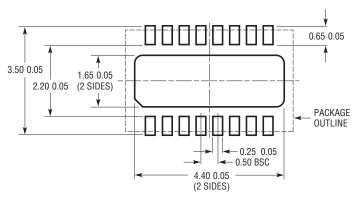

# PIN CONFIGURATION

# ORDER INFORMATION

| LEAD FREE FINISH  | TAPE AND REEL       | PART MARKING* | PACKAGE DESCRIPTION             | TEMPERATURE RANGE |

|-------------------|---------------------|---------------|---------------------------------|-------------------|

| LTC4232CDHC-1#PBF | LTC4232CDHC-1#TRPBF | 42321         | 16-Lead (5mm × 3mm) Plastic DFN | 0°C to 70°C       |

| LTC4232IDHC-1#PBF | LTC4232IDHC-1#TRPBF | 42321         | 16-Lead (5mm × 3mm) Plastic DFN | -40°C to 85°C     |

Consult LTC Marketing for parts specified with wider operating temperature ranges. \*The temperature grade is identified by a label on the shipping container.

For more information on lead free part marking, go to: http://www.linear.com/leadfree/

For more information on tape and reel specifications, go to: http://www.linear.com/tapeandreel/

# **ELECTRICAL CHARACTERISTICS** The $\bullet$ denotes those specifications which apply over the full operating temperature range, otherwise specifications are at $T_A = 25^{\circ}$ C. $V_{DD} = 12V$ unless otherwise noted.

| SYMBOL               | PARAMETER                             | CONDITIONS                                                            |   | MIN  | TYP    | MAX       | UNITS    |  |

|----------------------|---------------------------------------|-----------------------------------------------------------------------|---|------|--------|-----------|----------|--|

| DC Characte          | DC Characteristics                    |                                                                       |   |      |        |           |          |  |

| $\overline{V_{DD}}$  | Input Supply Range                    |                                                                       | • | 2.9  |        | 15        | V        |  |

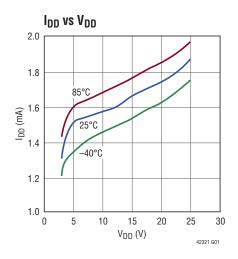

| $I_{DD}$             | Input Supply Current                  | MOSFET On, No Load                                                    | • |      | 1.6    | 3         | mA       |  |

| $V_{\rm DD(UVL)}$    | Input Supply Undervoltage Lockout     | V <sub>DD</sub> Rising                                                | • | 2.63 | 2.73   | 2.85      | V        |  |

| I <sub>OUT</sub>     | OUT Pin Leakage Current               | $V_{OUT} = V_{GATE} = 0V, V_{DD} = 15V$<br>$V_{OUT} = V_{GATE} = 12V$ | • | 1    | 0<br>2 | ±150<br>4 | μA<br>μA |  |

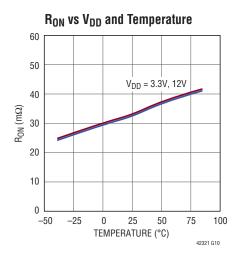

| R <sub>ON</sub>      | MOSFET + Sense Resistor On-Resistance |                                                                       | • | 15   | 33     | 50        | mΩ       |  |

| I <sub>LIM(TH)</sub> | Current Limit Threshold               | V = 1.23V, I <sub>SET</sub> Open                                      | • | 5.0  | 5.6    | 6.1       | А        |  |

|                      |                                       | V <sub>FB</sub> = 0V, I <sub>SET</sub> Open                           | • | 1.2  | 1.5    | 1.8       | А        |  |

|                      |                                       | $V_{FB}$ = 1.23V, $R_{SET}$ = 20k $\Omega$                            | • | 2.6  | 2.9    | 3.3       | А        |  |

**ELECTRICAL CHARACTERISTICS** The  $\bullet$  denotes those specifications which apply over the full operating temperature range, otherwise specifications are at  $T_A = 25^{\circ}\text{C}$ .  $V_{DD} = 12V$  unless otherwise noted.

| SYMBOL                     | PARAMETER                                                              | CONDITIONS                                                                             |   | MIN  | TYP   | MAX  | UNITS |

|----------------------------|------------------------------------------------------------------------|----------------------------------------------------------------------------------------|---|------|-------|------|-------|

| Inputs                     |                                                                        |                                                                                        |   |      |       |      |       |

| I <sub>IN</sub>            | OV, UV, FB Pin Input Current                                           | V = 1.2V                                                                               | • |      | 0     | ±1   | μА    |

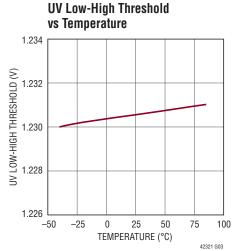

| $V_{TH}$                   | OV, UV, FB Pin Threshold Voltage                                       | V <sub>PIN</sub> Rising                                                                | • | 1.21 | 1.235 | 1.26 | V     |

| $\Delta V_{OV(HYST)}$      | OV Pin Hysteresis                                                      |                                                                                        | • | 10   | 20    | 30   | mV    |

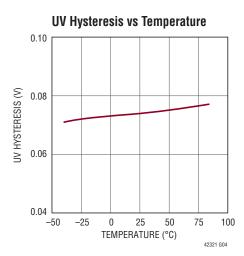

| $\Delta V_{UV(HYST)}$      | UV Pin Hysteresis                                                      |                                                                                        | • | 50   | 80    | 110  | mV    |

| V <sub>UV(RTH)</sub>       | UV Pin Reset Threshold Voltage                                         | V <sub>UV</sub> Falling                                                                | • | 0.55 | 0.62  | 0.7  | V     |

| $\Delta V_{FB(HYST)}$      | FB Pin Power Good Hysteresis                                           |                                                                                        | • | 10   | 20    | 30   | mV    |

| R <sub>ISET</sub>          | I <sub>SET</sub> Pin Internal Resistor                                 |                                                                                        | • | 19   | 20    | 21   | kΩ    |

| Outputs                    |                                                                        |                                                                                        |   |      |       |      |       |

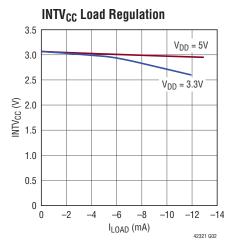

| VINTVCC                    | INTV <sub>CC</sub> Output Voltage                                      | V <sub>DD</sub> = 5V, 15V, I <sub>LOAD</sub> = 0mA, -10mA                              | • | 2.8  | 3.1   | 3.3  | V     |

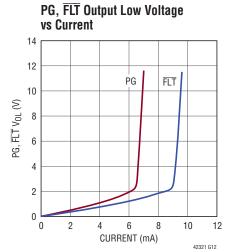

| $V_{0L}$                   | PG, FLT Pin Output Low Voltage                                         | I = 2mA                                                                                | • |      | 0.4   | 8.0  | V     |

| I <sub>OH</sub>            | PG, FLT Pin Input Leakage Current                                      | V = 30V                                                                                | • |      | 0     | ±10  | μΑ    |

| V <sub>TIMER(H)</sub>      | TIMER Pin High Threshold                                               | V <sub>TIMER</sub> Rising                                                              | • | 1.2  | 1.235 | 1.28 | V     |

| $V_{TIMER(L)}$             | TIMER Pin Low Threshold                                                | V <sub>TIMER</sub> Falling                                                             | • | 0.1  | 0.21  | 0.3  | V     |

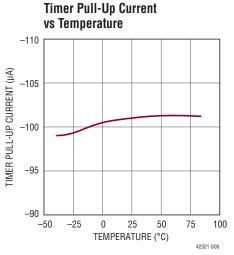

| I <sub>TIMER(UP)</sub>     | TIMER Pin Pull-Up Current                                              | V <sub>TIMER</sub> = 0V                                                                | • | -80  | -100  | -120 | μΑ    |

| I <sub>TIMER(DN)</sub>     | TIMER Pin Pull-Down Current                                            | V <sub>TIMER</sub> = 1.2V                                                              | • | 1.4  | 2     | 2.6  | μΑ    |

| I <sub>TIMER(RATIO)</sub>  | TIMER Pin Current Ratio I <sub>TIMER(DN)</sub> /I <sub>TIMER(UP)</sub> |                                                                                        | • | 1.6  | 2     | 2.7  | %     |

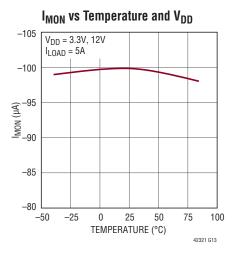

| A <sub>IMON</sub>          | I <sub>MON</sub> Pin Current Gain                                      | I <sub>OUT</sub> = 2.5A                                                                | • | 18.5 | 20    | 21.5 | μA/A  |

| I <sub>OFF(IMON)</sub>     | I <sub>MON</sub> Pin Offset Current                                    | I <sub>OUT</sub> = 150mA                                                               | • |      | 0     | ±4.5 | μΑ    |

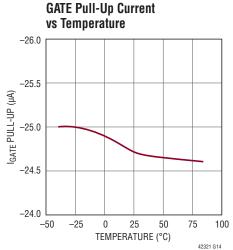

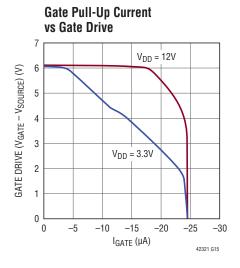

| I <sub>GATE(UP)</sub>      | Gate Pull-Up Current                                                   | Gate Drive On, V <sub>GATE</sub> = V <sub>OUT</sub> = 12V                              | • | -18  | -24   | -29  | μΑ    |

| I <sub>GATE(DN)</sub>      | Gate Pull-Down Current                                                 | Gate Drive Off, V <sub>GATE</sub> = 18V, V <sub>OUT</sub> = 12V                        | • | 180  | 250   | 400  | μΑ    |

| I <sub>GATE(FST)</sub>     | Gate Fast Pull-Down Current                                            | Fast Turn Off, V <sub>GATE</sub> = 18V, V <sub>OUT</sub> = 12V                         |   |      | 140   |      | mA    |

| AC Characteris             | etics                                                                  |                                                                                        |   |      |       |      |       |

| t <sub>PHL(GATE)</sub>     | Input High (OV), Input Low (UV) to Gate Low Propagation Delay          | V <sub>GATE</sub> < 16.5V Falling                                                      | • |      | 8     | 10   | μs    |

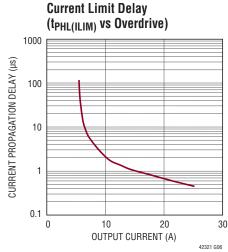

| t <sub>PHL(ILIM)</sub>     | Short-Circuit to Gate Low                                              | V <sub>FB</sub> = 0, Step I <sub>SENSE</sub> to 6A,<br>V <sub>GATE</sub> < 15V Falling | • |      | 1     | 5    | μs    |

| t <sub>D(ON)</sub>         | Turn-On Delay                                                          | Step V <sub>UV</sub> to 2V, V <sub>GATE</sub> > 13V                                    | • | 8    | 16    | 24   | ms    |

| t <sub>D(CB)</sub>         | Circuit Breaker Filter Delay Time (Internal)                           | V <sub>FB</sub> = 0V, Step I <sub>SENSE</sub> to 3A                                    | • | 1.3  | 2     | 2.7  | ms    |

| t <sub>D(AUTO-RETRY)</sub> | Auto-Retry Turn-On Delay (Internal)                                    |                                                                                        | • | 8    | 16    | 24   | ms    |

**Note 1:** Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. Exposure to any Absolute Maximum Rating condition for extended periods may affect device reliability and lifetime.

**Note 2:** All currents into pins are positive, all voltages are referenced to GND unless otherwise specified.

**Note 3:** An internal clamp limits the GATE pin to a maximum of 6.5V above OUT. Driving this pin to voltages beyond the clamp may damage the device.

**Note 4:** This IC includes overtemperature protection that is intended to protect the device during momentary overload conditions. Junction temperature will exceed 125°C when overtemperature protection is active. Continuous operation above the specified maximum operating junction temperature may impair device reliability.

**Note 5:**  $T_J$  is calculated from the ambient temperature,  $T_A$ , and power dissipation,  $P_D$ , according to the formula:

$$T_J = T_A + (P_D \cdot 43^{\circ}C/W)$$

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{DD} = 12V$ unless otherwise noted.

# TYPICAL PERFORMANCE CHARACTERISTICS $T_A = 25^{\circ}C$ , $V_{DD} = 12V$ unless otherwise noted.

### PIN FUNCTIONS

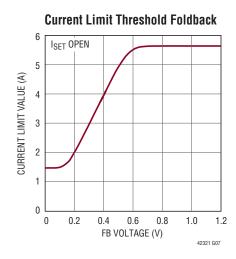

**FB:** Foldback and Power Good Input. Connect this pin to an external resistive divider from OUT. If the voltage falls below 0.6V, the current limit is reduced using a foldback profile (see the Typical Performance Characteristics section). If the voltage falls below 1.21V, the PG pin will pull low to indicate the power is bad.

**FLT**: Overcurrent Fault Indicator. Open-drain output pulls low when an overcurrent fault has occurred and the circuit breaker trips. For overcurrent auto-retry tie to UV pin (see the Applications Information section for details).

**GATE:** Gate Drive for Internal N-channel MOSFET. An internal 24µA current source charges the gate of the N-channel MOSFET. A resistor and capacitor network from this pin sets the turn-on rate. During an undervoltage or overvoltage condition a 250µA pull-down current turns the MOSFET off. During a short-circuit or undervoltage lockout condition, a 140mA pull-down current source between GATE and OUT is activated.

**GND:** Device Ground.

**I<sub>MON</sub>:** Current Monitor Output. The current in the internal MOSFET switch is divided by 50,000 and sourced from this pin. Placing a 20k resistor from this pin to GND creates a OV to 2V voltage swing when current ranges from 0A to 5A.

**INTV**<sub>CC</sub>: Internal 3.1V Supply Decoupling Output. This pin must have a  $1\mu F$  or larger bypass capacitor.

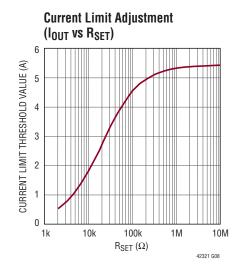

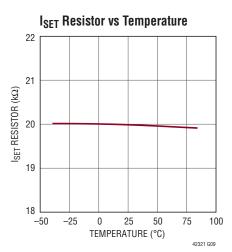

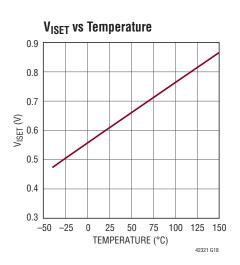

**I**<sub>SET</sub>: Current Limit Adjustment Pin. For a 5.6A current limit value open this pin. This pin is driven by a 20k resistor in series with a voltage source. The pin voltage is used to generate the current limit threshold. The internal 20k resistor and an external resistor between  $I_{SET}$  and ground create an attenuator that lowers the current limit value. Due to circuit tolerance the  $I_{SET}$  resistor should not be less than 2k. In order to match the temperature variation of the sense resistor, the voltage on this pin increases at the same rate as the sense resistance increases. Therefore the voltage at  $I_{SET}$  pin is proportional to temperature of the MOSFET switch.

**OUT:** Output of Internal MOSFET Switch. Connect this pin directly to the load.

**OV:** Overvoltage Comparator Input. Connect this pin to an external resistive divider from  $V_{DD}$ . If the voltage at this pin rises above 1.235V, an overvoltage is detected and the switch turns off. Tie to GND if unused.

**PG:** Power Good Indicator. Open-drain output pulls low when the FB pin drops below 1.21V indicating the power is bad. If the FB pin rises above 1.23V and the GATE to OUT voltage exceeds 4.2V, the open-drain pull-down releases the PG pin to go high.

**SENSE:** Current Sense Node and MOSFET Drain. The current limit circuit controls the GATE pin to limit the sense voltage between the  $V_{DD}$  and SENSE pins to 42mV (5.6A) or less depending on the voltage at the FB pin. The exposed pad on DHC packages are connected to SENSE and must be soldered to an electrically isolated printed circuit board trace to properly transfer the heat out of the package.

**TIMER:** Timer Input. Connect a capacitor between this pin and ground to set a 12ms/ $\mu$ F duration for current limit before the switch is turned off. If the UV pin is toggled low while the MOSFET switch is off, the switch will turn on again following a cooldown time of 518ms/ $\mu$ F duration. Tie this pin to INTV<sub>CC</sub> for a fixed 2ms overcurrent delay. Note that the fixed 2ms overcurrent delay is not recommended when auto-retry is enabled (see Applications Information).

**UV:** Undervoltage Comparator Input. Tie high if unused. Connect this pin to an external resistive divider from  $V_{DD}$ . If the UV pin voltage falls below 1.15V, an undervoltage is detected and the switch turns off. Pulling this pin below 0.62V resets the overcurrent fault and allows the switch to turn back on (see the Applications Information section for details). If overcurrent auto-retry is desired then tie this pin to the  $\overline{FLT}$  pin.

**V**<sub>DD</sub>: Supply Voltage and Current Sense Input. This pin has an undervoltage lockout threshold of 2.73V.

LINEAR

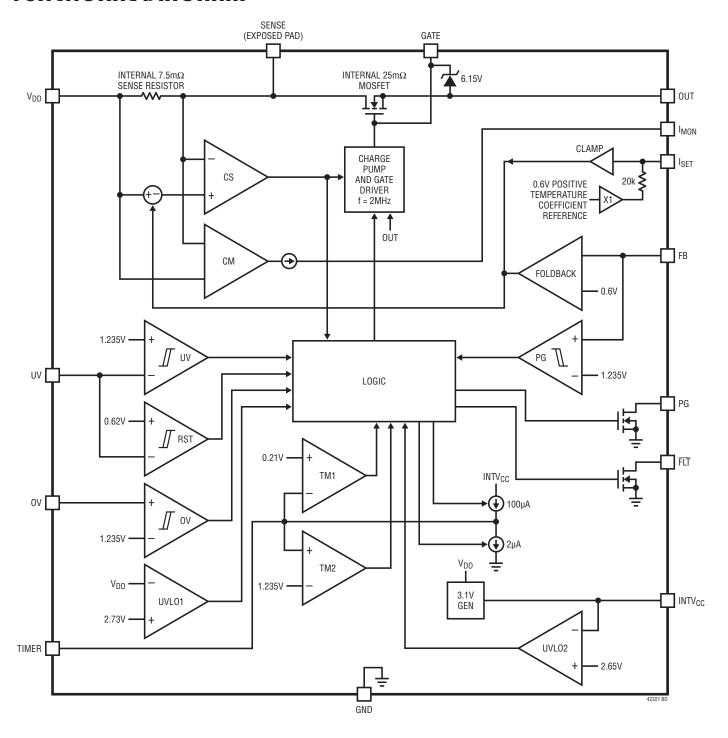

# **FUNCTIONAL DIAGRAM**

#### **OPERATION**

The Functional Diagram displays the main circuits of the device. The LTC4232-1 is designed to turn a board's supply voltage on and off in a controlled manner allowing the board to be safely inserted and removed from a live backplane. The LTC4232-1 includes a  $25m\Omega$  MOSFET and a  $7.5m\Omega$  current sense resistor. During normal operation, the charge pump and gate driver turn on the pass MOSFET's gate to provide power to the load. The inrush current control is accomplished by a resistor and capacitor network connected to the GATE pin. This circuit limits the GATE ramp rate and hence controls the voltage ramp rate of the output capacitor.

The current sense (CS) amplifier monitors the load current using the voltage sensed across the current sense resistor. The CS amplifier limits the current in the load by reducing the GATE-to-OUT voltage in an active control loop. It is simple to adjust the current limit threshold using the current setting ( $I_{SET}$ ) pin. This allows a different threshold during other times such as start-up.

A short circuit on the output to ground causes significant power dissipation during active current limiting. To limit this power, the foldback amplifier reduces the current limit value from 5.6A to 1.5A in a linear manner as the FB pin drops below 0.6V (see the Typical Performance Characteristics section).

If an overcurrent condition persists, the TIMER pin ramps up with a  $100\mu$ A current source until the pin voltage exceeds 1.235V (comparator TM2). This indicates to the

logic that it is time to turn off the pass MOSFET to prevent overheating. At this point the TIMER pin ramps down using the  $2\mu A$  current source until the voltage drops below 0.21V (Comparator TM1) which tells the logic to start an internal 16ms timer. At this point, the pass transistor has cooled and it is safe to turn it on again.

The output voltage is monitored using the FB pin and the PG comparator to determine if the power is available for the load. The power good condition is signaled by the PG pin using an open-drain pull-down transistor.

The Functional Diagram also shows the monitoring blocks of the LTC4232-1. The two comparators on the left side include the UV and OV comparators. These comparators determine if the external conditions are valid prior to turning on the MOSFET. But first the undervoltage lockout circuits UVLO1 and UVLO2 must validate the input supply and the internally generated 3.1V supply (INTV $_{\rm CC}$ ) and generate the power up initialization to the logic circuits. If the external conditions remain valid for 16ms the MOSFET is allowed to turn on.

Other features include MOSFET current and temperature monitoring. The current monitor (CM) outputs a current proportional to the sense resistor current. This current can drive an external resistor or other circuits for monitoring purposes. A voltage proportional to the MOSFET temperature is output to the  $I_{\mbox{\footnotesize SET}}$  pin. The MOSFET temperature allows external circuits to predict failure and shutdown the system.

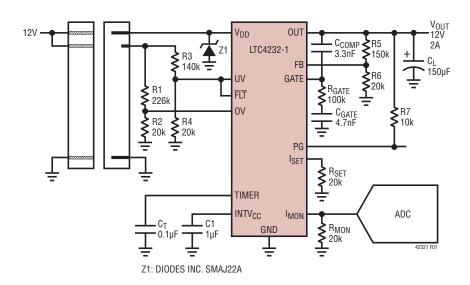

The typical LTC4232-1 application is in a high availability system that uses a positive voltage supply to distribute power to individual cards. A complete application circuit is shown in Figure 1. External component selection is discussed in detail in the following sections.

#### Turn-On Sequence

Several conditions must be present before the internal pass MOSFET can be turned on. First the supply  $V_{DD}$  must exceed its undervoltage lockout level. Next the internally generated supply INTV $_{CC}$  must cross its 2.65V undervoltage threshold. This generates a 25µs power-on-reset pulse which clears the fault register and initializes internal latches.

After the power-on-reset pulse, the LTC4232-1 will go through the following sequence. First, the UV and OV pins must indicate that the input voltage is within the acceptable range. All of these conditions must be satisfied for the duration of 16ms to ensure that any contact bounce during the insertion has ended.

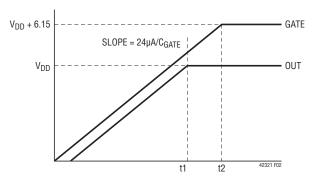

The MOSFET is turned on by charging up the GATE with a 24µA charge pump generated current source (Figure 2).

The voltage at the GATE pin rises with a slope equal to  $24\mu A/C_{GATE}$  and the supply inrush current is set at:

$$I_{\text{INRUSH}} = \frac{C_L}{C_{\text{GATE}}} \cdot 24 \mu A$$

Figure 2. Supply Turn-On

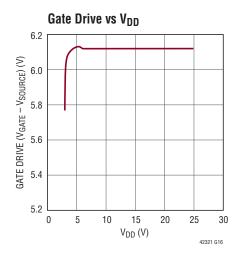

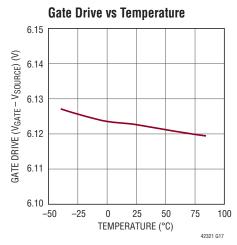

When the GATE voltage reaches the MOSFET threshold voltage, the switch begins to turn on and the OUT voltage follows the GATE voltage as it increases. Once OUT reaches  $V_{DD}$ , the GATE will ramp up until clamped by the 6.15V Zener between GATE and OUT.

As the OUT voltage rises, so will the FB pin which is monitoring it. Once the FB pin crosses its 1.235V threshold and the GATE to OUT voltage exceeds 4.2V, the PG pin will cease to pull low and indicate that the power is good.

Figure 1. 2A, 12V Card Resident Application

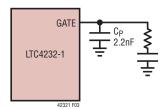

#### Parasitic MOSFET Oscillation

When the N-channel MOSFET ramps up the output during power-up it operates as a source follower. The source follower configuration may self-oscillate in the range of 25kHz to 300kHz when the load capacitance is less than 10µF, especially if the wiring inductance from the supply to the  $V_{DD}$  pin is greater than 3µH. The possibility of oscillation will increase as the load current (during power-up) increases. There are two ways to prevent this type of oscillation. The simplest way is to avoid load capacitances below 10µF. For wiring inductance larger than 20µH, the minimum load capacitance may extend to 100µF. A second choice is to connect an external gate capacitor  $C_P > 1.5$ nF as shown in Figure 3.

Figure 3. Compensation for Small CLOAD

#### **Turn-Off Sequence**

The switch can be turned off by a variety of conditions. A normal turn-off is initiated by the UV pin going below its 1.235V threshold. Additionally, several fault conditions will turn off the switch. These include an input overvoltage (OV pin), overcurrent circuit breaker (SENSE pin) or overtemperature. Normally the switch is turned off with a 250 $\mu$ A current pulling down the GATE pin to ground. With the switch turned off, the OUT voltage drops which pulls the FB pin below its threshold. PG then pulls low to indicate output power is no longer good.

If  $V_{DD}$  drops below 2.65V for greater than 5µs or INTV<sub>CC</sub> drops below 2.5V for greater than 1µs, a fast shutdown of the switch is initiated. The GATE is pulled down with a 140mA current to the OUT pin.

#### **Overcurrent Fault**

The LTC4232-1 features an adjustable current limit with foldback that protects against short-circuits or excessive load current. To prevent excessive power dissipation in the switch during active current limit, the available current is

reduced as a function of the output voltage sensed by the FB pin. A graph in the Typical Performance Characteristics curves shows the current limit versus FB voltage.

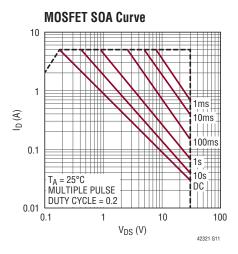

An overcurrent fault occurs when the current limit circuitry has been engaged for longer than the timeout delay set by the TIMER. Current limiting begins when the MOSFET current reaches 1.5A to 5.6A (depending on the foldback). The GATE pin is then brought down with a 140mA GATEto-OUT current. The voltage on the GATE is regulated in order to limit the current to less than 5.6A. At this point, a circuit breaker time delay starts by charging the external timing capacitor from the TIMER pin with a 100µA pull-up current. If the TIMER pin reaches its 1.235V threshold, the internal switch turns off (with a 250µA current from GATE to ground). Included in the Typical Performance Characteristics curves is a graph of the Safe Operating Area for the MOSFET. From this graph one can determine the MOSFET's maximum time in current limit for a given output power.

Tying the TIMER pin to INTV<sub>CC</sub> will force the part to use the internally generated (circuit breaker) delay of 2ms. In either case the  $\overline{FLT}$  pin is pulled low to indicate an overcurrent fault has turned off the pass MOSFET. For a given the circuit breaker time delay, the equation for setting the timing capacitor's value is as follows:

$$C_T = t_{CB} \bullet 0.083 (\mu F/ms)$$

After the switch is turned off, the TIMER pin begins discharging the timing capacitor with a  $2\mu A$  pull-down current. When the TIMER pin reaches its 0.21V threshold, an internal 16ms timer is started. After the 16ms delay, the switch is allowed to turn on again if the overcurrent fault has been cleared. Bringing the UV pin below 0.6V and then high will clear the fault. If the TIMER pin is tied to INTV<sub>CC</sub> then the switch is allowed to turn on again (after an internal 16ms delay) if the overcurrent fault is cleared.

Tying the  $\overline{FLT}$  pin to the UV pin allows the part to self-clear the fault and turn the MOSFET on as soon as TIMER pin has ramped below 0.21V. In this auto-retry mode the LTC4232-1 repeatedly tries to turn on after an overcurrent at a period determined by the capacitor on the TIMER pin. When the TIMER pin is tied to INTV<sub>CC</sub> the internal 16ms turn-on delay is not sufficient to prevent overheating during

/ LINEAR

auto-retry into a shorted load. Using an external timing capacitor is recommended when using auto-retry mode.

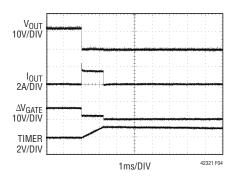

The waveform in Figure 4 shows how the output latches off following a short-circuit. The current in the MOSFET is 1.4A as the timer ramps up.

Figure 4. Short-Circuit Waveform

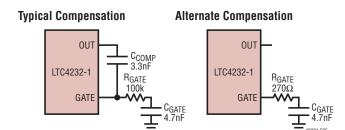

The  $R_{GATE}$ ,  $C_{GATE}$  and  $C_{COMP}$  network on the GATE pin compensates the current limit regulation loop. It is possible to eliminate  $C_{COMP}$  and use only the  $R_{GATE}$  and  $C_{GATE}$  network, which will require  $R_{GATE}$  to reduce to  $270\Omega$  (see Figure 5). This alternate compensation with one less component allows the GATE pin to undershoot during a short circuit on the output and chatter as it settles. This chatter could last about 1µs to 2µs for every nF of  $C_{GATE}$  capacitance.

Figure 5. Compensation Components on the GATE Pin

#### **Current Limit Adjustment**

The default value of the active current limit is 5.6A. The current limit threshold can be adjusted lower by placing a resistor between the  $I_{SET}$  pin and ground. As shown in the Functional Diagram the voltage at the  $I_{SET}$  pin (via the clamp circuit) sets the CS amplifier's built-in offset voltage. This offset voltage directly determines the active current limit value. With the  $I_{SET}$  pin open, the voltage at

the  $I_{SET}$  pin is determined by a positive temperature coefficient reference. This voltage is set to 0.618V at room temperature which corresponds to a 5.6A current limit at room temperature.

An external resistor placed between the  $I_{SET}$  pin and ground forms a resistive divider with the internal 20k sourcing resistor. The divider acts to lower the voltage at the  $I_{SET}$  pin and therefore lower the current limit threshold. The overall current limit threshold precision is reduced to  $\pm 12\%$  when using a 20k resistor to halve the threshold.

Using a switch (connected to ground) in series with this external resistor allows the active current limit to change only when the switch is closed. This feature can be used when the start-up current exceeds the typical maximum load current.

#### **Monitor MOSFET Temperature**

The voltage at the  $I_{SET}$  pin increases linearly with increasing temperature. The temperature profile of the  $I_{SET}$  pin is shown in the Typical Performance Characteristics section. Using a comparator or ADC to measure the  $I_{SET}$  voltage provides an indicator of the MOSFET temperature.

There is an overtemperature circuit in the LTC4232-1 that monitors an internal voltage similar to the I<sub>SET</sub> pin voltage. When the die temperature exceeds 145°C the circuit turns off the MOSFET until the temperature drops to 125°C.

#### **Monitor MOSFET Current**

The current in the MOSFET passes through a sense resistor. The voltage on the sense resistor is converted to a current that is sourced out of the  $I_{MON}$  pin. The gain of  $I_{SENSE}$  amplifier is  $20\mu\text{A/A}$  referenced from the MOSFET current. This output current can be converted to a voltage using an external resistor to drive a comparator or ADC. The voltage compliance for the  $I_{MON}$  pin is from 0V to  $INTV_{CC}-0.7V$ .

A microcontroller with a built-in comparator can build a simple integrating single-slope ADC by resetting a capacitor that is charged with this current. When the capacitor voltage trips the comparator and the capacitor is reset, a timer is started. The time between resets will indicate the MOSFET current.

#### **Monitor OV and UV Faults**

Protecting the load from an overvoltage condition is the main function of the OV pin. In Figure 1 an external resistive divider (driving the OV pin) connects to a comparator to turn off the MOSFET when the  $V_{DD}$  voltage exceeds 15.2V. If the  $V_{DD}$  pin subsequently falls back below 14.9V, the switch will be allowed to turn on immediately. In the LTC4232-1 the OV pin threshold is 1.235V when rising, and 1.215V when falling out of overvoltage.

The UV pin functions as an undervoltage protection pin or as an "ON" pin. In the Figure 1 application the MOSFET turns off when  $V_{DD}$  falls below 9.23V. If the  $V_{DD}$  pin subsequently rises above 9.88V for 100ms, the switch will be allowed to turn on again. The LTC4232-1 UV turn-on/off thresholds are 1.235V (rising) and 1.155V (falling).

In the cases of an undervoltage or overvoltage the MOSFET turns off and there is indication on the PG status pin. When the overvoltage is removed the MOSFET's gate ramps up immediately.

#### **Power Good Indication**

In addition to setting the foldback current limit threshold, the FB pin is used to determine a power good condition. The Figure 1 application uses an external resistive divider on the OUT pin to drive the FB pin. The PG comparator indicates logic high when OUT pin rises above 10.5V. If the OUT pin subsequently falls below 10.3V the comparator toggles low. On the LTC4232-1 the PG comparator drives high when the FB pin rises above 1.235V and low when it falls below 1.215V.

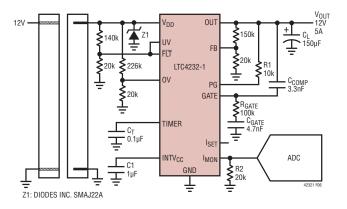

Figure 6. 5A, 12V Card Resident Application

Once the PG comparator is high the GATE pin voltage is monitored with respect to the OUT pin. Once the GATE minus OUT voltage exceeds 4.2V the PG pin goes high. This indicates to the system that it is safe to load the OUT pin while the MOSFET is completely turned "on". The PG pin goes low when the GATE is commanded off (using the UV, OV or SENSE pins) or when the PG comparator drives low.

#### **Design Example**

Consider the following design example (Figure 6):  $V_{IN} = 12V$ ,  $I_{MAX} = 5A$ .  $I_{INRUSH} = 750$ mA,  $C_L = 150$ µF,  $V_{UVON} = 9.88V$ ,  $V_{OVOFF} = 15.2V$ ,  $V_{PWRGD} = 10.5V$ . A current limit fault triggers an automatic restart of the power-up sequence.

The inrush current is set to 100mA using CGATE:

$$C_{GATE} = C_L \frac{I_{GATE(UP)}}{I_{INRUSH}} = 150 \mu F \frac{24 \mu A}{750 mA} \approx 4.7 n F$$

Calculate the time it takes to charge C<sub>I</sub>:

$$t_{CHARGEUP} = \frac{C_L \cdot V_{IN}}{I_{INRUSH}} = \frac{150\mu F \cdot 12V}{750mA} = 2.4ms$$

The peak power dissipation of 12V at 750mA (or 9W) is within the SOA of the pass MOSFET for 2.4ms (see MOSFET SOA curve in the Typical Performance Characteristics section).

Next the power dissipated in the MOSFET during overcurrent must be limited. The active current limit uses a timer to prevent excessive energy dissipation in the MOSFET. The worst-case power dissipation occurs when the voltage versus current profile of the foldback current limit is at the maximum. This occurs when the current is 6.1A and the voltage is one half of the 12V or 6V. See the Current Limit Threshold Foldback graph in the Typical Performance Characteristics section to view this profile. In order to survive 36W, the MOSFET SOA dictates a maximum time of 10ms (see SOA graph). Therefore, it is acceptable to set the current limit timeout using  $C_T$  to be 1.2ms:

$$C_T = \frac{1.2ms}{12[ms/\mu F]} = 0.1\mu F$$

After the 1.2ms timeout the FLT pin needs to pull-down on the UV pin to restart the power-up sequence.

The values for overvoltage, undervoltage and power good thresholds using the resistive dividers on the UV, OV and FB pins match the requirements of turn-on at 9.88V and turn-off at 15.2V.

The final schematic in Figure 6 results in very few external components. The pull-up resistor, R1, connects to the PG pin while the 20k (R2) converts the  $I_{MON}$  current to a voltage at a ratio:

$V_{IMON} = 20[\mu A/A] \cdot 20k \cdot I_{OUT} = 0.4[V/A] \cdot I_{OUT}$ In addition there is a 1 $\mu$ F bypass (C1) on the INTV<sub>CC</sub> pin.

#### **Layout Considerations**

In Hot Swap applications where load currents can be 5A, narrow PCB tracks exhibit more resistance than wider tracks and operate at elevated temperatures. The minimum trace width for 1oz copper foil is 0.02" per amp to make sure the trace stays at a reasonable temperature. Using 0.03" per amp or wider is recommended. Note that 1oz copper exhibits a sheet resistance of about  $0.5 m\Omega/square$ . Small resistances add up quickly in high current applications.

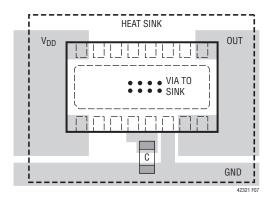

There are two  $V_{DD}$  pins on opposite sides of the package that connect to the sense resistor and MOSFET. The PCB layout should be balanced and symmetrical to each  $V_{DD}$  pin to balance current in the MOSFET bond wires. Figure 7 shows a recommended layout for the LTC4232-1.

Although the MOSFET is self protected from overtemperature, it is recommended to solder the backside of the package to a copper trace to provide a good heat sink. Note that the backside is connected to the SENSE pin and

Figure 7. Recommended Layout

cannot be soldered to the ground plane. During normal loads the power dissipated in the MOSFET is as high as 1.9W. A  $10\text{mm} \times 10\text{mm}$  area of 1oz copper should be sufficient. This area of copper can be divided in many layers.

It is also important to put C1, the bypass capacitor for the  $\mathsf{INTV}_{\mathsf{CC}}$  pin as close as possible between the  $\mathsf{INTV}_{\mathsf{CC}}$  and GND.

#### **Additional Applications**

The LTC4232-1 has a wide operating range from 2.9V to 15V. The UV, OV and PG thresholds are set with few resistors. All other functions are independent of supply voltage.

In addition to Hot Swap applications, the LTC4232-1 also functions as a backplane resident switch for removable load cards (see Figure 8.)

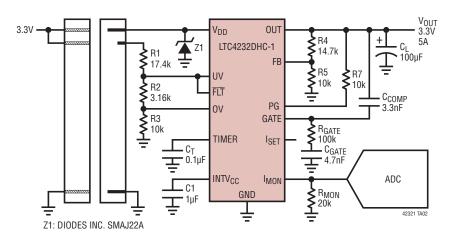

The last page shows a 3.3V application with a UV threshold of 2.87V, an OV threshold of 3.77V and a PG threshold of 3.05V.

Figure 8. 12V, 5A Backplane Resident Application with Insertion Activated Turn-On

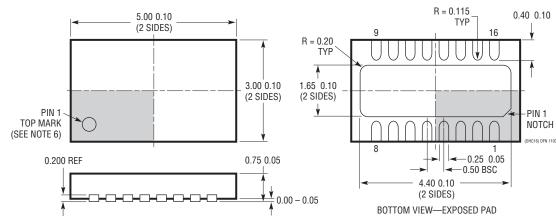

# PACKAGE DESCRIPTION

Please refer to http://www.linear.com/designtools/packaging/ for the most recent package drawings.

#### **DHC Package** 16-Lead Plastic DFN (5mm × 3mm) (Reference LTC DWG # 05-08-1706)

**RECOMMENDED** SOLDER PAD PITCH AND DIMENSIONS

#### NOTE:

- 1. DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WJED-1) IN JEDEC

- DRAWING PROPOSED TO BE MADE VARIATION OF VERSION (WJED-1) IN JEDEC PACKAGE OUTLINE MO-229

DRAWING NOT TO SCALE

ALL DIMENSIONS ARE IN MILLIMETERS

DIMENSIONS OF EXPOSED PAD ON BOTTOM OF PACKAGE DO NOT INCLUDE MOLD FLASH. MOLD FLASH, IF PRESENT, SHALL NOT EXCEED 0.15mm ON ANY SIDE SEXPOSED PAD SHALL BE SOLDER PLATED

SHADED AREA IS ONLY A REFERENCE FOR PIN 1 LOCATION ON THE TOP AND BOTTOM OF PACKAGE

# **REVISION HISTORY**

| REV | DATE  | DESCRIPTION                                              | PAGE NUMBER |

|-----|-------|----------------------------------------------------------|-------------|

| Α   | 08/15 | Raised I <sub>GATE(DN)</sub> maximum from 340μA to 400μA | 3           |

# TYPICAL APPLICATION

#### 3.3V, 5A Card Resident Application with Auto-Retry

# **RELATED PARTS**

| PART NUMBER | DESCRIPTION                                                        | COMMENTS                                                                                                                                          |

|-------------|--------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|

| LTC4210     | Single Channel, Hot Swap Controller                                | Operates from 2.7V to 16.5V, Active Current Limiting, SOT23-6                                                                                     |

| LTC4211     | Single Channel, Hot Swap Controller                                | Operates from 2.5V to 16.5V, Multifunction Current Control, MSOP-8 or MSOP-10                                                                     |

| LTC4212     | Single Channel, Hot Swap Controller                                | Operates from 2.5V to 16.5V, Power-Up Timeout, MSOP-10                                                                                            |

| LTC4214     | Negative Voltage, Hot Swap Controller                              | Operates from 0V to -16V, MSOP-10                                                                                                                 |

| LTC4215     | Hot Swap Controller with I <sup>2</sup> C Compatible Monitoring    | Operates from 2.9V to 15V, 8-Bit ADC Monitors Current and Voltage                                                                                 |

| LTC4217     | 2A Integrated Hot Swap Controller                                  | Operates from 2.9V to 26.5V, Adjustable 5% Accurate Current Limit                                                                                 |

| LTC4218     | Hot Swap Controller with 5% Accurate (15mV)<br>Current Limit       | Operates from 2.9V to 26.5V, Adjustable Current Limit, SSOP-16, DFN-16                                                                            |

| LTC4219     | 5A Integrated Hot Swap Controller                                  | 12V and 5V Preset Versions, 10% Accurate Current Limit                                                                                            |

| LT4220      | Positive and Negative Voltage Dual Channels Hot<br>Swap Controller | Operates from ±2.7V to ±16.5V, SSOP-16                                                                                                            |

| LTC4221     | Dual Hot Swap Controller/Sequencer                                 | Operates from 1V to 13.5V, Multifunction Current Control, SSOP-16                                                                                 |

| LTC4230     | Triple Channels Hot Swap Controller                                | Operates from 1.7V to 16.5V, Multifunction Current Control, SSOP-20                                                                               |

| LTC4227     | Dual Ideal Diode and Single Hot Swap Controller                    | Operates from 2.9V to 18V, PowerPath™ and Inrush Current Control for Redundant Supplies                                                           |

| LTC4228     | Dual Ideal Diode and Hot Swap Controller                           | Operates from 2.9V to 18V, PowerPath and Inrush Current Control for Two Rails, MicroTCA, Redundant Power Supplies, and Supply Holdup Applications |