LMK61E2

SNAS674 - SEPTEMBER 2015

# LMK61E2 Ultra-Low Jitter Programmable Oscillator with Internal EEPROM

### **Features**

- Ultra-low Noise, High Performance

- Jitter: 90 fs RMS typical f<sub>OUT</sub> > 100 MHz

- PSRR: -70 dBc, robust supply noise immunity

- Flexible Output Format; User Selectable

- LVPECL up to 1 GHz

- LVDS up to 900 MHz

- HCSL up to 400 MHz

- Total frequency tolerance of ± 50 ppm

- System Level Features

- Frequency margining: fine and coarse

- Internal EEPROM: user configurable default settings

- Other Features

- Device control: I<sup>2</sup>C

- 3.3 V operating voltage

- Industrial temperature range (-40°C to +85°C)

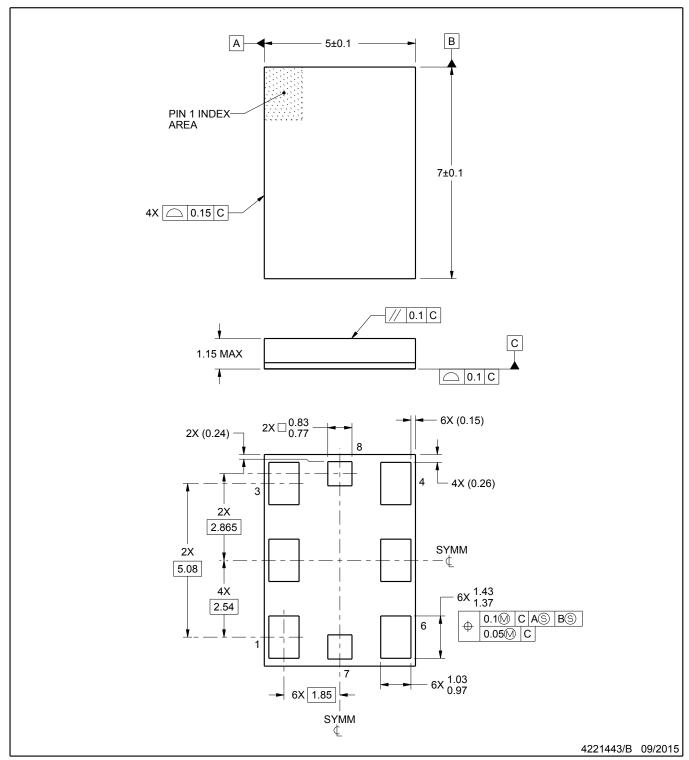

- 7 mm x 5 mm 8-pin package

# 2 Applications

- High-performance replacement for crystal-, SAW-, or silicon-based Oscillators

- Switches, Routers, Network Line Cards, Base Band Units (BBU), Servers, Storage/SAN

- Test and Measurement

- Medical Imaging

- FPGA, Processor Attach

# 3 Description

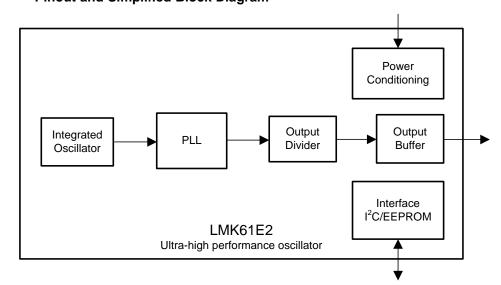

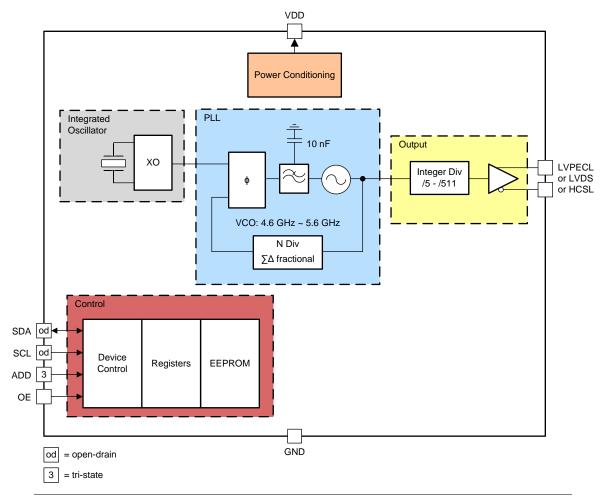

The LMK61E2 is an ultra-low jitter PLLatinum<sup>TM</sup> programmable oscillator with a fractional-N frequency synthesizer with integrated VCO that generates commonly used reference clocks. The outputs can be configured as LVPECL or LVDS or HCSL.

The device features self startup from on-chip EEPROM that is factory programmed to generate 156.25 MHz LVPECL output. The device registers and EEPROM settings are fully programmable insystem via I<sup>2</sup>C serial interface. Internal power conditioning provide excellent power supply ripple rejection (PSRR), reducing the cost and complexity of the power delivery network. The device operates from a single  $3.3 \text{ V} \pm 5\%$  supply.

The device provides fine and coarse frequency margining options via I<sup>2</sup>C serial interface to support system design verification tests (DVT), such as standard compliance and system timing margin testing.

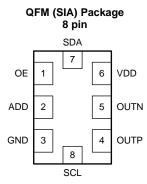

## Device Information<sup>(1)</sup>

| PART NUMBER | PACKAGE         | BODY SIZE (NOM) |

|-------------|-----------------|-----------------|

| LMK61E2     | 8-pin QFM (SIA) | 7.0 mm x 5.0 mm |

(1) For all available packages, see the orderable addendum at the end of the data sheet.

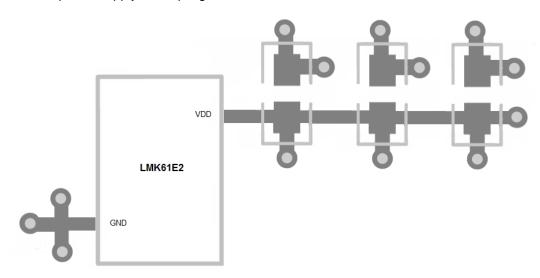

# **Pinout and Simplified Block Diagram**

# **Table of Contents**

| 1 | Features 1                                                       | Characteristics                       |                  |

|---|------------------------------------------------------------------|---------------------------------------|------------------|

| • |                                                                  |                                       | nd Qualification |

| 2 | Applications                                                     | -                                     | Characteristics  |

| 3 | Description 1                                                    | 7 Parameter Measurement               |                  |

| 4 | Revision History2                                                | 7.1 Device Output Configur            |                  |

| 5 | Pin Configuration and Functions 3                                |                                       |                  |

| 6 | Specifications3                                                  | 8 Detailed Description                |                  |

|   | 6.1 Absolute Maximum Ratings3                                    |                                       |                  |

|   | 6.2 ESD Ratings 3                                                |                                       | ım 1             |

|   | 6.3 Recommended Operating Conditions 4                           |                                       | 1                |

|   | 6.4 Thermal Information                                          | 8.4 Device Functional Mode            | es 1             |

|   | 6.5 Electrical Characteristics - Power Supply 4                  | 8.5 Programming                       | 1                |

|   | 6.6 LVPECL Output Characteristics                                | 8.6 Register Map                      | 2                |

|   | 6.7 LVDS Output Characteristics                                  | 8.7 EEPROM Map                        | 3                |

|   | 6.8 HCSL Output Characteristics                                  | 9 Application and Impleme             | entation 3       |

|   | 6.9 OE Input Characteristics                                     | 9.1 Application Information.          | 3                |

|   | 6.10 ADD Input Characteristics                                   | 9.2 Typical Applications              | 3                |

|   | 6.11 Frequency Tolerance Characteristics                         | 10 Power Supply Recomme               |                  |

|   | 6.12 Power-On/Reset Characteristics (VDD)                        | 11 Layout                             |                  |

|   | 6.13 I <sup>2</sup> C-Compatible Interface Characteristics (SDA, | 11.1 Layout Guidelines                |                  |

|   | SCL)                                                             | 12 Device and Documentat              |                  |

|   | 6.14 Spurious and PSRR Characteristics                           |                                       | S 4              |

|   | 6.15 Other Characteristics                                       | •                                     | 4                |

|   | 6.16 PLL Clock Output Jitter Characteristics                     |                                       | e Caution4       |

|   | 6.17 Typical 156.25 MHz Output Phase Noise                       |                                       | 4                |

|   | Characteristics                                                  | •                                     |                  |

|   | 6.18 Typical 161.1328125 MHz Output Phase Noise                  | 13 Mechanical, Packaging, Information |                  |

|   |                                                                  |                                       |                  |

# 4 Revision History

| DATE           | REVISION | NOTES           |

|----------------|----------|-----------------|

| September 2015 | *        | Initial Release |

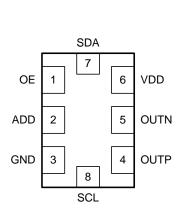

# 5 Pin Configuration and Functions

#### **Pin Functions**

| PI            | IN           | I/O       | DESCRIPTION                                                                                                                                                                                                           |  |  |

|---------------|--------------|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| NAME          | NO.          | 1/0       | DESCRIPTION                                                                                                                                                                                                           |  |  |

| POWER         |              |           |                                                                                                                                                                                                                       |  |  |

| GND           | 3            | Ground    | Device Ground.                                                                                                                                                                                                        |  |  |

| VDD           | 6            | Analog    | 3.3 V Power Supply.                                                                                                                                                                                                   |  |  |

| OUTPUT BLOCK  |              |           |                                                                                                                                                                                                                       |  |  |

| OUTP,<br>OUTN | 4, 5         | Universal | Differential Output Pair (LVPECL, LVDS or HCSL).                                                                                                                                                                      |  |  |

| DIGITAL CON   | TROL / INTER | ACES      |                                                                                                                                                                                                                       |  |  |

| ADD           | 2            | LVCMOS    | When left open, LSB of I <sup>2</sup> C slave address is set to "01". When tied to VDD, LSB of I <sup>2</sup> C slave address is set to "10". When tied to GND, LSB of I <sup>2</sup> C slave address is set to "00". |  |  |

| OE            | 1            | LVCMOS    | Output Enable (internal pullup). When set to low, output pair is disabled and set at high impedance.                                                                                                                  |  |  |

| SCL           | 8            | LVCMOS    | I <sup>2</sup> C Serial Clock (open-drain). Requires an external pull-up resistor to VDD.                                                                                                                             |  |  |

| SDA           | 7            | LVCMOS    | <sup>2</sup> C Serial Data (bi-directional, open-drain). Requires an external pull-up resistor to VDD.                                                                                                                |  |  |

# 6 Specifications

# 6.1 Absolute Maximum Ratings

over operating free-air temperature range (unless otherwise noted) (1)

|                  |                                        | MIN  | MAX       | UNIT |

|------------------|----------------------------------------|------|-----------|------|

| VDD              | Device Supply Voltage                  | -0.3 | 3.6       | V    |

| V <sub>IN</sub>  | Output Voltage Range for Logic Inputs  | -0.3 | VDD + 0.3 | V    |

| V <sub>OUT</sub> | Output Voltage Range for Clock Outputs | -0.3 | VDD + 0.3 | V    |

| T <sub>J</sub>   | Junction Temperature                   |      | 150       | °C   |

| T <sub>STG</sub> | Storage Temperature                    | -40  | 125       | °C   |

<sup>(1)</sup> Stresses beyond those listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only, which do not imply functional operation of the device at these or any other conditions beyond those indicated under Recommended Operating Conditions. Exposure to absolute maximum-rated conditions for extended periods may affect device reliability.

#### 6.2 ESD Ratings

|                    |                         |                                                                     | VALUE | UNIT |

|--------------------|-------------------------|---------------------------------------------------------------------|-------|------|

|                    |                         | Human-body model (HBM), per ANSI/ESDA/JEDEC JS-001 (1)              | ±4000 |      |

| V <sub>(ESD)</sub> | Electrostatic discharge | Charged-device model (CDM), per JEDEC specification JESD22-C101 (2) | ±1500 | V    |

(1) JEDEC document JEP155 states that 500 V HBM allows safe manufacturing with a standard ESD control process.

(2) JEDEC document JEP157 states that 250 V CDM allows safe manufacturing with a standard ESD control process.

SNAS674-SEPTEMBER 2015 www.ti.com

# 6.3 Recommended Operating Conditions

over operating free-air temperature range (unless otherwise noted)

|                   |                        | MIN   | NOM | MAX   | UNIT |

|-------------------|------------------------|-------|-----|-------|------|

| VDD               | Device Supply Voltage  | 3.135 | 3.3 | 3.465 | V    |

| T <sub>A</sub>    | Ambient Temperature    | -40   | 25  | 85    | °C   |

| TJ                | Junction Temperature   |       |     | 125   | °C   |

| t <sub>RAMP</sub> | VDD Power-Up Ramp Time | 0.1   |     | 100   | ms   |

### 6.4 Thermal Information

|                               |                                              |                     | LMK61E2 (2) (3) (4) |      |       |  |

|-------------------------------|----------------------------------------------|---------------------|---------------------|------|-------|--|

| THERMAL METRIC <sup>(1)</sup> |                                              | QFM (SIA)<br>8 PINS |                     |      |       |  |

|                               |                                              |                     |                     |      |       |  |

| $R_{\theta JA}$               | Junction-to-ambient thermal resistance       | 54                  | 44                  | 41.2 |       |  |

| R <sub>0</sub> JC(top)        | Junction-to-case (top) thermal resistance    | 34                  | n/a                 | n/a  |       |  |

| $R_{\theta JB}$               | Junction-to-board thermal resistance         | 36.7                | n/a                 | n/a  | °C/W  |  |

| ΨЈТ                           | Junction-to-top characterization parameter   | 11.2                | 16.9                | 21.9 | 10/00 |  |

| ΨЈВ                           | Junction-to-board characterization parameter | 36.7                | 37.8                | 38.9 |       |  |

| R <sub>0</sub> JC(bot)        | Junction-to-case (bottom) thermal resistance | n/a                 | n/a                 | n/a  |       |  |

For more information about traditional and new thermal metrics, see the Semiconductor and IC Package Thermal Metrics application report, SPRA953.

# 6.5 Electrical Characteristics - Power Supply<sup>(1)</sup>

$VDD = 3.3 V \pm 5\%, T_A = -40C \text{ to } 85^{\circ}C$

|        | PARAMETER                                          | TEST CONDITIONS       | MIN | TYP | MAX | UNIT |

|--------|----------------------------------------------------|-----------------------|-----|-----|-----|------|

| IDD    | Device Current Consumption                         | LVPECL <sup>(2)</sup> |     | 162 | 208 | mA   |

|        |                                                    | LVDS                  |     | 152 | 196 |      |

|        |                                                    | HCSL                  |     | 155 | 196 |      |

| IDD-PD | Device Current Consumption when output is disabled | OE = GND              |     | 136 |     |      |

<sup>(1)</sup> Refer to Parameter Measurement Information for relevant test conditions.

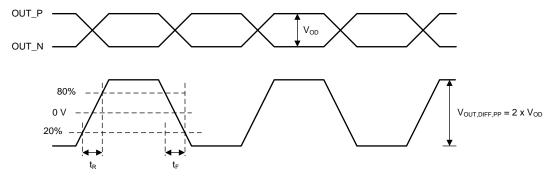

# 6.6 LVPECL Output Characteristics (1)

$VDD = 3.3 V \pm 5\%, T_A = -40C \text{ to } 85^{\circ}C$

|                                 | PARAMETER                                                                | TEST CONDITIONS | MIN | TYP                     | MAX  | UNIT        |

|---------------------------------|--------------------------------------------------------------------------|-----------------|-----|-------------------------|------|-------------|

| f <sub>OUT</sub>                | Output Frequency <sup>(2)</sup>                                          |                 | 10  |                         | 1000 | MHz         |

| V <sub>OD</sub>                 | Output Voltage Swing (V <sub>OH</sub> - V <sub>OL</sub> ) <sup>(2)</sup> |                 | 700 | 800                     | 1200 | mV          |

| V <sub>OUT, DIFF, PP</sub>      | Differential Output Peak-to-<br>Peak Swing                               |                 |     | 2 x<br> V <sub>OD</sub> |      | <b>&gt;</b> |

| V <sub>OS</sub>                 | Output Common Mode<br>Voltage                                            |                 |     | VDD –<br>1.55           |      | <b>&gt;</b> |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time (20% to 80%) (3)                                   |                 |     | 120                     | 200  | ps          |

| PN-Floor                        | Output Phase Noise Floor (f <sub>OFFSET</sub> > 10 MHz)                  | 156.25 MHz      |     | -165                    |      | dBc/Hz      |

Refer to Parameter Measurement Information for relevant test conditions.

Submit Documentation Feedback

Product Folder Links: LMK61E2

STRUMENTS

The package thermal resistance is calculated on a 4 layer JEDEC board.

Connected to GND with 3 thermal vias (0.3-mm diameter).

ψJB (junction to board) is used when the main heat flow is from the junction to the GND pad. Please refer to Thermal Considerations section for more information on ensuring good system reliability and quality.

On-chip power dissipation should exclude 40 mW, dissipated in the 150 ohm termination resistors, from total power dissipation.

An output frequency over f<sub>OUT</sub> max spec is possible, but output swing may be less than V<sub>OD</sub> min spec.

<sup>(3)</sup> Ensured by characterization.

www.ti.com

# LVPECL Output Characteristics<sup>(1)</sup> (continued)

$VDD = 3.3 V \pm 5\%, T_A = -40C \text{ to } 85^{\circ}C$

|     | PARAMETER             | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----|-----------------------|-----------------|-----|-----|-----|------|

| ODC | Output Duty Cycle (3) |                 | 45% |     | 55% |      |

# 6.7 LVDS Output Characteristics(1)

$VDD = 3.3 V \pm 5\%$ .  $T_A = -40^{\circ}C$  to 85°C

|                                 | PARAMETER                                                                | TEST CONDITIONS | MIN | TYP                     | MAX | UNIT   |

|---------------------------------|--------------------------------------------------------------------------|-----------------|-----|-------------------------|-----|--------|

| f <sub>OUT</sub>                | Output Frequency <sup>(1)</sup>                                          |                 | 10  |                         | 900 | MHz    |

| V <sub>OD</sub>                 | Output Voltage Swing (V <sub>OH</sub> - V <sub>OL</sub> ) <sup>(1)</sup> |                 | 300 | 390                     | 480 | mV     |

| $V_{\text{OUT, DIFF, PP}}$      | Differential Output Peak-to-<br>Peak Swing                               |                 |     | 2 x<br> V <sub>OD</sub> |     | V      |

| V <sub>OS</sub>                 | Output Common Mode<br>Voltage                                            |                 |     | 1.2                     |     | V      |

| t <sub>R</sub> / t <sub>F</sub> | Output Rise/Fall Time (20% to 80%) (2)                                   |                 |     | 150                     | 250 | ps     |

| PN-Floor                        | Output Phase Noise Floor (f <sub>OFFSET</sub> > 10 MHz)                  | 156.25 MHz      |     | -162                    |     | dBc/Hz |

| ODC                             | Output Duty Cycle (2)                                                    |                 | 45% |                         | 55% |        |

| R <sub>OUT</sub>                | Differential Output Impedance                                            |                 |     | 125                     |     | Ohm    |

<sup>(1)</sup> An output frequency over f<sub>OUT</sub> max spec is possible, but output swing may be less than V<sub>OD</sub> min spec.

# 6.8 HCSL Output Characteristics(1)

$VDD = 3.3 \text{ V} \pm 5\%, T_{\Delta} = -40^{\circ}\text{C} \text{ to } 85^{\circ}\text{C}$

|                          | PARAMETER                                               | TEST CONDITIONS | MIN  | TYP  | MAX | UNIT   |

|--------------------------|---------------------------------------------------------|-----------------|------|------|-----|--------|

| f <sub>OUT</sub>         | Output Frequency                                        |                 | 10   |      | 400 | MHz    |

| V <sub>OH</sub>          | Output High Voltage                                     |                 | 600  |      | 850 | mV     |

| V <sub>OL</sub>          | Output Low Voltage                                      |                 | -100 |      | 100 | mV     |

| V <sub>CROSS</sub>       | Absolute Crossing Voltage <sup>(2)(3)</sup>             |                 | 250  |      | 475 | mV     |

| V <sub>CROSS-DELTA</sub> | Variation of V <sub>CROSS</sub> (2)(3)                  |                 | 0    |      | 140 | mV     |

| dV/dt                    | Slew Rate <sup>(4)</sup>                                |                 | 0.8  |      | 2   | V/ns   |

| PN-Floor                 | Output Phase Noise Floor (f <sub>OFFSET</sub> > 10 MHz) | 100 MHz         |      | -164 |     | dBc/Hz |

| ODC                      | Output Duty Cycle <sup>(4)</sup>                        |                 | 45%  |      | 55% |        |

<sup>(1)</sup> Refer to Parameter Measurement Information for relevant test conditions.

# 6.9 OE Input Characteristics

$VDD = 3.3 V \pm 5\%, T_A = -40^{\circ}C \text{ to } 85^{\circ}C$

|                 | PARAMETER          | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------------|--------------------|-----------------|-----|-----|-----|------|

| $V_{IH}$        | Input High Voltage |                 | 1.4 |     |     | V    |

| $V_{IL}$        | Input Low Voltage  |                 |     |     | 0.6 | V    |

| I <sub>IH</sub> | Input High Current | $V_{IH} = VDD$  | -40 |     | 40  | uA   |

| I <sub>IL</sub> | Input Low Current  | $V_{IL} = GND$  | -40 |     | 40  | uA   |

| C <sub>IN</sub> | Input Capacitance  |                 |     | 2   |     | pF   |

<sup>(2)</sup> Ensured by characterization.

<sup>(2)</sup> Measured from -150 mV to +150 mV on the differential waveform with the 300 mVpp measurement window centered on the differential zero crossing.

<sup>(3)</sup> Ensured by design.

<sup>(4)</sup> Ensured by characterization.

# TEXAS INSTRUMENTS

# 6.10 ADD Input Characteristics

VDD =  $3.3 \text{ V} \pm 5\%$ ,  $T_A = -40^{\circ}\text{C}$  to  $85^{\circ}\text{C}$

|                 | PARAMETER          | TEST CONDITIONS       | MIN | TYP | MAX | UNIT |

|-----------------|--------------------|-----------------------|-----|-----|-----|------|

| $V_{IH}$        | Input High Voltage |                       | 1.4 |     |     | V    |

| $V_{IL}$        | Input Low Voltage  |                       |     |     | 0.4 | V    |

| I <sub>IH</sub> | Input High Current | V <sub>IH</sub> = VDD | -40 |     | 40  | uA   |

| I <sub>IL</sub> | Input Low Current  | V <sub>IL</sub> = GND | -40 |     | 40  | uA   |

| C <sub>IN</sub> | Input Capacitance  |                       |     | 2   |     | pF   |

# 6.11 Frequency Tolerance Characteristics<sup>(1)</sup>

$VDD = 3.3 V \pm 5\%, T_A = -40^{\circ}C \text{ to } 85^{\circ}C$

| PARAMETER | TEST CONDITIONS                                                                                                                                                                              | MIN | TYP | MAX | UNIT |

|-----------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----|-----|------|

| , ,       | All output formats, frequency bands and device junction temperature up to 125°C; includes initial freq tolerance, temperature & supply voltage variation, solder reflow and aging (10 years) | -50 |     | 50  | ppm  |

<sup>(1)</sup> Ensured by characterization.

# 6.12 Power-On/Reset Characteristics (VDD)

$VDD = 3.3 V \pm 5\%, T_A = -40^{\circ}C \text{ to } 85^{\circ}C$

|                      | PARAMETER                          | TEST CONDITIONS                                            | MIN  | TYP | MAX  | UNIT |

|----------------------|------------------------------------|------------------------------------------------------------|------|-----|------|------|

| $V_{THRESH}$         | Threshold Voltage <sup>(1)</sup>   |                                                            | 2.72 |     | 2.95 | V    |

| $V_{DROOP}$          | Allowable Voltage Droop (2)        |                                                            |      |     | 0.1  | V    |

| t <sub>STARTUP</sub> | Startup Time (1)                   | Time elapsed from VDD at 3.135 V to output enabled         |      |     | 10   | ms   |

| t <sub>OE-EN</sub>   | Output enable time <sup>(2)</sup>  | Time elapsed from OE at V <sub>IH</sub> to output enabled  |      |     | 50   | us   |

| t <sub>OE-DIS</sub>  | Output disable time <sup>(2)</sup> | Time elapsed from OE at V <sub>IL</sub> to output disabled |      |     | 50   | us   |

<sup>(1)</sup> Ensured by characterization.

# 6.13 I<sup>2</sup>C-Compatible Interface Characteristics (SDA, SCL)<sup>(1)(2)</sup>

$VDD = 3.3 V \pm 5\%, T_A = -40$ °C to 85°C

|                                       | PARAMETER                        | TEST CONDITIONS         | MIN | TYP | MAX | UNIT |

|---------------------------------------|----------------------------------|-------------------------|-----|-----|-----|------|

| V <sub>IH</sub>                       | Input High Voltage               |                         | 1.2 |     |     | V    |

| $V_{IL}$                              | Input Low Voltage                |                         |     |     | 0.6 | V    |

| I <sub>IH</sub>                       | Input Leakage                    |                         | -40 |     | 40  | uA   |

| C <sub>IN</sub>                       | Input Capacitance                |                         |     | 2   |     | pF   |

| C <sub>OUT</sub>                      | Input Capacitance                |                         |     |     | 400 | pF   |

| V <sub>OL</sub>                       | Output Low Voltage               | I <sub>OL</sub> = 3 mA  |     |     | 0.6 | V    |

| f <sub>SCL</sub>                      | I <sup>2</sup> C Clock Rate      |                         | 100 |     | 400 | kHz  |

| t <sub>SU_STA</sub>                   | START Condition Setup<br>Time    | SCL high before SDA low | 0.6 |     |     | us   |

| t <sub>H_STA</sub>                    | START Condition Hold Time        | SCL low after SDA low   | 0.6 |     |     | us   |

| t <sub>PH_SCL</sub>                   | SCL Pulse Width High             |                         | 0.6 |     |     | us   |

| t <sub>PL_SCL</sub>                   | SCL Pulse Width Low              |                         | 1.3 |     |     | us   |

| t <sub>H_SDA</sub>                    | SDA Hold Time                    | SDA valid after SCL low | 0   |     | 0.9 | us   |

| t <sub>SU_SDA</sub>                   | SDA Setup Time                   |                         | 115 |     |     | ns   |

| t <sub>R_IN</sub> / t <sub>F_IN</sub> | SCL/SDA Input Rise and Fall Time |                         |     |     | 300 | ns   |

<sup>(1)</sup> Total capacitive load for each bus line ≤ 400 pF.

<sup>(2)</sup> Ensured by design.

<sup>(2)</sup> Ensured by design.

www.ti.com

# I<sup>2</sup>C-Compatible Interface Characteristics (SDA, SCL)<sup>(1)(2)</sup> (continued)

$VDD = 3.3 V \pm 5\%, T_A = -40^{\circ}C \text{ to } 85^{\circ}C$

|                      | PARAMETER                            | TEST CONDITIONS                    | MIN | TYP | MAX | UNIT |

|----------------------|--------------------------------------|------------------------------------|-----|-----|-----|------|

| t <sub>F_OUT</sub>   | SDA Output Fall Time                 | C <sub>BUS</sub> = 10 pF to 400 pF |     |     | 250 | ns   |

| t <sub>SU_STOP</sub> | STOP Condition Setup Time            |                                    | 0.6 |     |     | us   |

| t <sub>BUS</sub>     | Bus Free Time between STOP and START |                                    | 1.3 |     |     | us   |

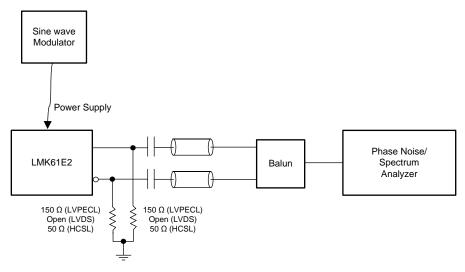

# 6.14 Spurious and PSRR Characteristics (1)

VDD = 3.3 V,  $T_A = 25^{\circ}\text{C}$ , PLL bandwidth = 400 kHz, VCO Frequency = 5 GHz (Integer-N PLL) or 5.15625 GHz (Fractional-N PLL), Output Divider = 32, Output Type = LVPECL/LVDS/HCSL

|      | PARAMETER                                            | TEST CONDITIONS      | MIN | TYP | MAX | UNIT |

|------|------------------------------------------------------|----------------------|-----|-----|-----|------|

| PSRR | Spurs Induced by 50 mV                               | Sine wave at 50 kHz  |     | -70 |     | dBc  |

|      | Power Supply Ripple (2)(3) at 156.25 MHz output, all | Sine wave at 100 kHz |     | -70 |     |      |

|      | output types                                         | Sine wave at 500 kHz |     | -70 |     | -    |

|      |                                                      | Sine wave at 1 MHz   |     | -70 |     |      |

| SPUR | Max spur power at 156.25<br>MHz output               | All output types     |     | -90 |     | dBc  |

|      | Max spur power at<br>161.1328125 MHz output          | All output types     |     | -80 |     |      |

- (1) Refer to Parameter Measurement Information for relevant test conditions.

- (2) Measured max spur level with 50 mVpp sinusoidal signal between 50 kHz and 1 MHz applied on VDD pin

- (3)  $DJ_{SPUR}$  (ps, pk-pk) = [2\*10(SPUR/20) / ( $\pi$ \*fOUT)]\*1e6, where PSRR or SPUR in dBc and fOUT in MHz.

#### 6.15 Other Characteristics

$VDD = 3.3 V \pm 5\%$ ,  $T_A = -40$ °C to 85°C

|           | PARAMETER           | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|-----------|---------------------|-----------------|-----|-----|-----|------|

| $f_{VCO}$ | VCO Frequency Range |                 | 4.6 |     | 5.6 | GHz  |

# 6.16 PLL Clock Output Jitter Characteristics (1)(2)

$VDD = 3.3 V \pm 5\%, T_A = -40^{\circ}C \text{ to } 85^{\circ}C$

|    | PARAMETER                                                               | TEST CONDITIONS                                           | MIN | TYP | MAX | UNIT   |

|----|-------------------------------------------------------------------------|-----------------------------------------------------------|-----|-----|-----|--------|

| RJ | RMS Phase Jitter <sup>(3)</sup><br>(12 kHz – 20 MHz)<br>(1 kHz – 5 MHz) | $f_{OUT} \ge 100$ MHz, Integer-N PLL, All output types    |     | 100 | 200 | fs RMS |

| RJ | RMS Phase Jitter <sup>(3)</sup><br>(12 kHz – 20 MHz)<br>(1 kHz – 5 MHz) | $f_{OUT} \ge 100$ MHz, Fractional-N PLL, All output types |     | 150 | 300 | fs RMS |

- (1) Refer to Parameter Measurement Information for relevant test conditions.

- (2) Phase jitter measured with Agilent E5052 signal source analyzer using a differential-to-single ended converter (balun or buffer).

- (3) Ensured by characterization.

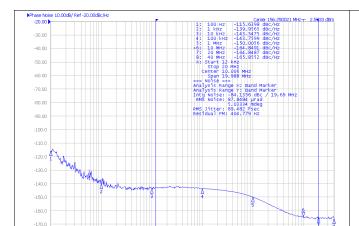

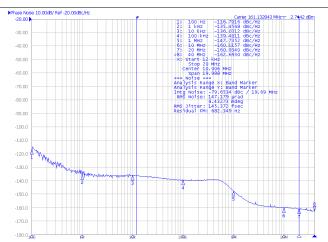

# 6.17 Typical 156.25 MHz Output Phase Noise Characteristics (1)(2)

VDD = 3.3 V,  $T_A = 25^{\circ}\text{C}$ , PLL bandwidth = 400 kHz, VCO Frequency = 5 GHz, Integer-N PLL, Output Divider = 32, Output Type = LVPECL/LVDS/HCSL

| Typo - EVI EGDEVBORTOGE |                               |        |      |       |        |  |  |

|-------------------------|-------------------------------|--------|------|-------|--------|--|--|

| SYMBOL                  | PARAMETER                     |        |      | UNITS |        |  |  |

|                         |                               | LVPECL | LVDS | HCSL  |        |  |  |

| phn <sub>10k</sub>      | Phase noise at 10 kHz offset  | -143   | -143 | -143  | dBc/Hz |  |  |

| Phn <sub>20k</sub>      | Phase noise at 20 kHz offset  | -143   | -143 | -143  | dBc/Hz |  |  |

| phn <sub>100k</sub>     | Phase noise at 100 kHz offset | -144   | -144 | -144  | dBc/Hz |  |  |

| Phn <sub>200k</sub>     | Phase noise at 200 kHz offset | -145   | -145 | -145  | dBc/Hz |  |  |

(1) Refer to Parameter Measurement Information for relevant test conditions.

(2) Phase jitter measured with Agilent E5052 signal source analyzer using a differential-to-single ended converter (balun or buffer).

SNAS674 – SEPTEMBER 2015 www.ti.com

# TEXAS INSTRUMENTS

# Typical 156.25 MHz Output Phase Noise Characteristics<sup>(1)(2)</sup> (continued)

$VDD = 3.3 \text{ V}, T_A = 25^{\circ}\text{C}, PLL \text{ bandwidth} = 400 \text{ kHz}, VCO \text{ Frequency} = 5 \text{ GHz}, Integer-N PLL, Output Divider} = 32, Output Type = LVPECL/LVDS/HCSL$

| SYMBOL             | PARAMETER                    |        |      | UNITS |        |

|--------------------|------------------------------|--------|------|-------|--------|

|                    |                              | LVPECL | LVDS | HCSL  |        |

| phn <sub>1M</sub>  | Phase noise at 1 MHz offset  | -150   | -150 | -150  | dBc/Hz |

| phn <sub>2M</sub>  | Phase noise at 2 MHz offset  | -154   | -154 | -154  | dBc/Hz |

| phn <sub>10M</sub> | Phase noise at 10 MHz offset | -165   | -162 | -164  | dBc/Hz |

| phn <sub>20M</sub> | Phase noise at 20 MHz offset | -165   | -162 | -164  | dBc/Hz |

# 6.18 Typical 161.1328125 MHz Output Phase Noise Characteristics (1)(2)

$\label{eq:VDD} VDD = 3.3 \text{ V}, \text{ $T_A$} = 25 ^{\circ}\text{C}, \text{ PLL bandwidth} = 400 \text{ kHz}, \text{ VCO Frequency} = 5.15625 \text{ GHz}, \text{ Fractional-N PLL, Output Divider} = 32, \\ Output \text{ Type} = \text{LVPECL/LVDS/HCSL}$

| SYMBOL              | PARAMETER                     |        | UNITS |      |        |

|---------------------|-------------------------------|--------|-------|------|--------|

|                     |                               | LVPECL | LVDS  | HCSL |        |

| phn <sub>10k</sub>  | Phase noise at 10 kHz offset  | -136   | -136  | -136 | dBc/Hz |

| phn <sub>20k</sub>  | Phase noise at 20 kHz offset  | -136   | -136  | -136 | dBc/Hz |

| phn <sub>100k</sub> | Phase noise at 100 kHz offset | -140   | -140  | -140 | dBc/Hz |

| phn <sub>200k</sub> | Phase noise at 200 kHz offset | -141   | -141  | -141 | dBc/Hz |

| phn <sub>1M</sub>   | Phase noise at 1 MHz offset   | -148   | -148  | -148 | dBc/Hz |

| phn <sub>2M</sub>   | Phase noise at 2 MHz offset   | -156   | -156  | -156 | dBc/Hz |

| phn <sub>10M</sub>  | Phase noise at 10 MHz offset  | -161   | -159  | -160 | dBc/Hz |

| phn <sub>20M</sub>  | Phase noise at 20 MHz offset  | -162   | -160  | -161 | dBc/Hz |

<sup>(1)</sup> Refer to Parameter Measurement Information for relevant test conditions.

## 6.19 Additional Reliability and Qualification

| PARAMETER                  | CONDITION / TEST METHOD |  |  |

|----------------------------|-------------------------|--|--|

| Mechanical Shock           | MIL-STD-202, Method 213 |  |  |

| Mechanical Vibration       | MIL-STD-202, Method 204 |  |  |

| Moisture Sensitivity Level | J-STD-020, MSL3         |  |  |

<sup>(2)</sup> Phase jitter measured with Agilent E5052 signal source analyzer using a differential-to-single ended converter (balun or buffer).

www.ti.com

# 6.20 Typical Performance Characteristics

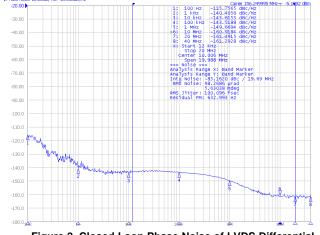

Figure 1. Closed Loop Phase Noise of LVPECL Differential Output at 156.25 MHz with PLL bandwidth at 400 kHz, Integer-N PLL, 5 GHz VCO Frequency, Output Divider = 32

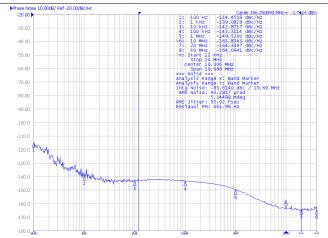

Figure 2. Closed Loop Phase Noise of LVDS Differential Output at 156.25 MHz with PLL bandwidth at 400 kHz, Integer-N PLL, 5 GHz VCO Frequency, Output Divider = 32

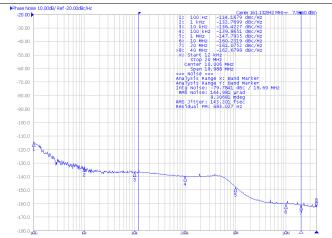

Figure 3. Closed Loop Phase Noise of HCSL Differential Output at 156.25 MHz with PLL bandwidth at 400 kHz, Integer-N PLL, 5 GHz VCO Frequency, Output Divider = 32

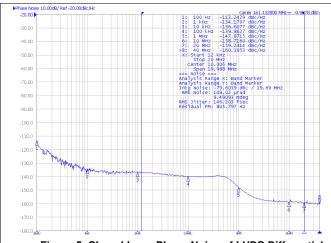

Figure 4. Closed Loop Phase Noise of LVPECL Differential Output at 161.1328125 MHz with PLL Bandwidth at 400 kHz, Fractional-N PLL, 5.15625 GHz VCO Frequency, Output Divider = 32

SNAS674 – SEPTEMBER 2015 www.ti.com

# TEXAS INSTRUMENTS

# **Typical Performance Characteristics (continued)**

Figure 5. Closed Loop Phase Noise of LVDS Differential

Output at 161.1328125 MHz with PLL bandwidth at 400 kHz,

Fractional-N PLL, 5.15625 GHz VCO Frequency, Output

Divider = 32

Figure 6. Closed Loop Phase Noise of HCSL Differential

Output at 161.1328125 MHz with PLL bandwidth at 400 kHz,

Fractional-N PLL, 5.15625 GHz VCO Frequency, Output

Divider = 32

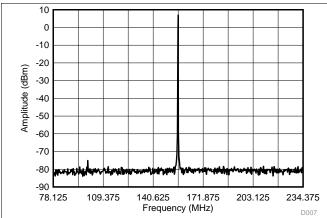

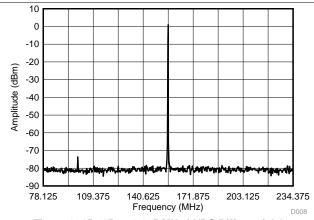

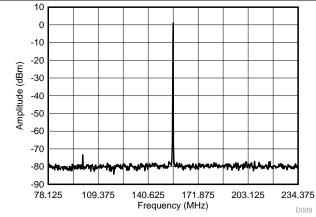

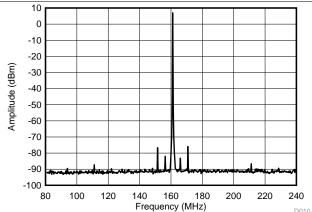

Figure 7. 156.25 ± 78.125 MHz LVPECL Differential Output Spectrum with PLL bandwidth at 400 kHz, Integer-N PLL, 5 GHz VCO Frequency, Output Divider = 32

Figure 8. 156.25 ± 78.125 MHz LVDS Differential Output Spectrum with PLL bandwidth at 400 kHz, Integer-N PLL, 5 GHz VCO Frequency, Output Divider = 32

Figure 9. 156.25 ± 78.125 MHz HCSL Differential Output Spectrum with PLL bandwidth at 400 kHz, Integer-N PLL, 5 GHz VCO Frequency, Output Divider = 32

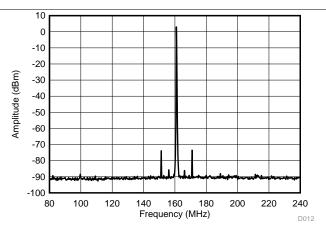

Figure 10. 161.1328125 ± 80.56640625 MHz LVPECL

Differential Output Spectrum with PLL bandwidth at 400 kHz, Fractional-N PLL, 5.15625 GHz VCO Frequency, Output

Divider = 32

Submit Documentation Feedback

Copyright © 2015, Texas Instruments Incorporated

# **Typical Performance Characteristics (continued)**

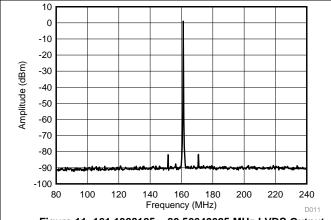

Figure 11. 161.1328125 ± 80.56640625 MHz LVDS Output Spectrum with PLL bandwidth at 400 kHz, Fractional-N PLL, 5.15625 GHz VCO Frequency, Output Divider = 32

Figure 12. 161.1328125 ± 80.56640625 MHz HCSL Output Spectrum with PLL bandwidth at 400 kHz, Fractional-N PLL 5.15625 GHz VCO Frequency, Output Divider = 32

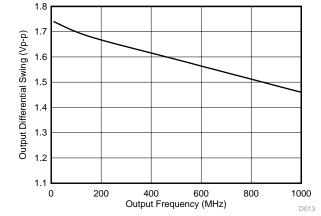

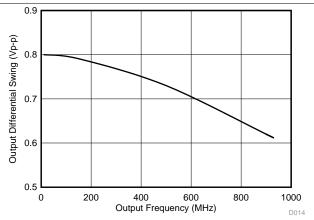

Figure 13. LVPECL Differential Output Swing vs Frequency

Figure 14. LVDS Differential Output Swing vs Frequency

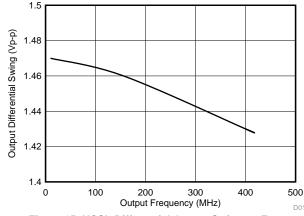

Figure 15. HCSL Differential Output Swing vs Frequency

SNAS674 – SEPTEMBER 2015 www.ti.com

# TEXAS INSTRUMENTS

# 7 Parameter Measurement Information

# 7.1 Device Output Configurations

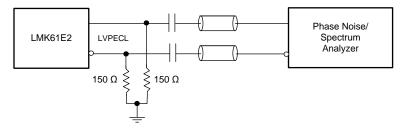

High impedance differential probe

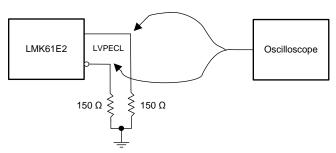

Figure 16. LVPECL Output DC Configuration during Device Test

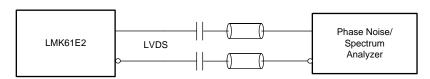

High impedance differential probe

Figure 17. LVDS Output DC Configuration during Device Test

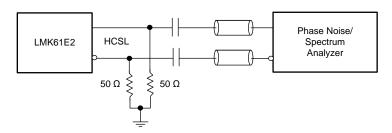

High impedance differential probe

Figure 18. HCSL Output DC Configuration during Device Test

Figure 19. LVPECL Output AC Configuration during Device Test

Figure 20. LVDS Output AC Configuration during Device Test

# **Device Output Configurations (continued)**

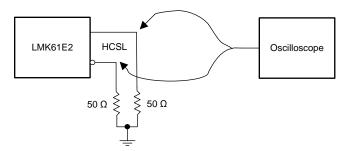

Figure 21. HCSL Output AC Configuration during Device Test

Figure 22. PSRR Test Setup

Figure 23. Differential Output Voltage and Rise/Fall Time

# TEXAS INSTRUMENTS

## 8 Detailed Description

#### 8.1 Overview

The LMK61E2 is a programmable oscillator that generates commonly used reference clocks with less than 200 fs, rms max random jitter in integer PLL mode and less than 300 fs, rms max random jitter in fractional PLL mode.

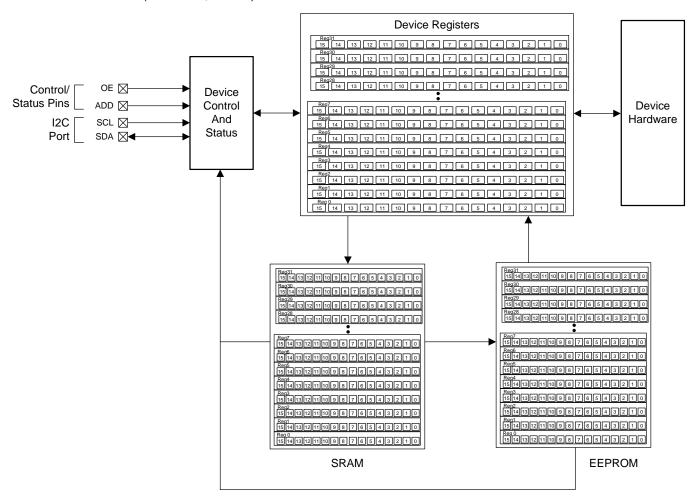

## 8.2 Functional Block Diagram

NOTE

Control blocks are compatible with 1.8/2.5/3.3 V I/O voltage levels.

### 8.3 Feature Description

### 8.3.1 Device Block-Level Description

The LMK61E2 comprises of an integrated oscillator that includes a 50 MHz crystal, a fractional PLL with integrated VCO that supports a frequency range of 4.6 GHz to 5.6 GHz. The PLL block consists of a phase frequency detector (PFD), charge pump, integrated passive loop filter, a feedback divider that can support both integer and fractional values and a delta-sigma engine for noise suppression in fractional PLL mode. Completing the device is the combination of an integer output divider and a universal differential output buffer. The PLL is powered by on-chip low dropout (LDO) linear voltage regulators and the regulated supply network is partitioned

## **Feature Description (continued)**

such that the sensitive analog supplies are running from separate LDOs than the digital supplies which use their own LDO. The LDOs provide isolation to the PLL from any noise in the external power supply rail with a PSRR of better than -70 dBc at 50 kHz to 1 MHz ripple frequencies at 3.3 V device supply. The device supports fine and coarse frequency margining by changing the settings of the integrated oscillator and the output divider respectively.

#### 8.3.2 Device Configuration Control

The LMK61E2 supports I<sup>2</sup>C programming interface where an I<sup>2</sup>C host can update any device configuration after the device enables the host interface and the host writes a sequence that updates the device registers. Once the device configuration is set, the host can also write to the on-chip EEPROM for a new set of powerup defaults based on the configuration pin settings in the soft pin configuration mode.

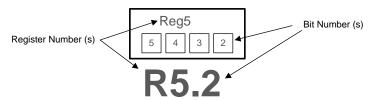

# 8.3.3 Register File Reference Convention

Figure 24 shows the method that this document employs to refer to an individual register bit or a grouping of register bits. If a drawing or text references an individual bit the format is to specify the register number first and the bit number second. The LMK61E2 contains 38 registers that are 8 bits wide. The register addresses and the bit positions both begin with the number zero (0). A period separates the register address and bit address. The first bit in the register file is address 'R0.0' meaning that it is located in Register 0 and is bit position 0. The last bit in the register file is address 'R31.7' referring to the 8th bit of register address 31 (the 32nd register in the device). Figure 24 also lists specific bit positions as a number contained within a box. A box with the register address encloses the group of boxes that represent the bits relevant to the specific device circuitry in context.

Figure 24. LMK61E2 Register Reference Format

## 8.3.4 Configuring the PLL

The PLL in LMK61E2 can be configured to accommodate various output frequencies either through I<sup>2</sup>C programming interface or in the absence of programming, the PLL defaults stored in EEPROM is loaded on powerup. The PLL can be configured by setting the Reference Doubler, Integrated PLL Loop Filter, Feedback Divider, and Output Divider.

For the PLL to operate in closed loop mode, the following condition in Equation 1 has to be met.

$F_{VCO} = F_{REF} \times D \times [(INT + NUM/DEN)]$

#### where

- F<sub>VCO</sub>: PLL/VCO Frequency (4.6 GHz to 5.6 GHz)

- F<sub>REF</sub>: 50 MHz reference input

- D: PLL input frequency doubler, 1=Disabled, 2=Enabled

- INT: PLL feedback divider integer value (12 bits, 1 to 4095)

- NUM: PLL feedback divider fractional numerator value (22 bits, 0 to 4194303)

- DEN: PLL feedback divider fractional denominator value (22 bits, 1 to 4194303)

(1)

The output frequency is related to the VCO frequency as given in Equation 2.

$F_{OUT} = F_{VCO} / OUTDIV$

#### where

OUTDIV: Output divider value (9 bits, 5 to 511)

(2)

# TEXAS INSTRUMENTS

# **Feature Description (continued)**

#### 8.3.5 Integrated Oscillator

The integrated oscillator in LMK61E2 features programmable load capacitances that can be set to either operate at exactly its nominal oscillation frequency or operate at a fixed frequency offset from its nominal oscillation frequency. This is done by programming R16 and R17. More details on frequency margining are provided in Fine Frequency Margining.

#### 8.3.6 Reference Doubler

The reference path has a frequency doubler that can be enabled by programming R34.5 = "1". Enabling the doubler allows a higher comparison frequency for the PLL and would result in a 3 dB reduction in the in-band phase noise at the output of the LMK61E2. Enabling the doubler also results in higher reference and phase detector spurs which will be minimized by enabling the higher order components (R3, C3) of the loop filter and programmed to appropriate values. Disabling the doubler would result in higher in-band phase noise on the device output than when the doubler is enabled but the reference and phase detector spurs would be lower on the device output than when the doubler is enabled.

#### 8.3.7 Phase Frequency Detector

The PFD of the PLL takes inputs from the reference path and the feedback divider output and produces an output that is dependent on the phase and frequency difference between the two inputs. The allowable range of frequencies at the inputs of the PFD is 50 MHz, when reference doubler is disabled, or 100 MHz, when reference doubler is enabled.

### 8.3.8 Feedback Divider (N)

The N divider of the PLL includes fractional compensation and can achieve any fractional denominator (DEN) from 1 to 4,194,303. The integer portion, INT, is the whole part of the N divider value and the fractional portion, NUM / DEN, is the remaining fraction. N, NUM, and DEN are programmed in R25, R26, R27, R28, R29, R30, R31, and R32. The total programmed N divider value, N, is determined by: N = INT + NUM / DEN. The output of the N divider sets the PFD frequency to the PLL and should equal 50 MHz, when reference doubler is disabled, or 100 MHz, when reference doubler is enabled.

#### 8.3.9 Fractional Circuitry

The delta signal modulator is a key component of the fractional circuitry and is involved in noise shaping for better phase noise and spurs in the band of interest. The order of the delta sigma modulator is selectable between integer mode and third order, for fractional PLL mode, and can be programmed in R33[1-0]. The dithering mode is selectable between disabled, for integer PLL mode, and weak, for fractional PLL mode, and can be programmed in R33[3-2].

#### 8.3.10 Charge Pump

The PLL has charge pump slices of 1.6 mA, to be used when PLL is set to fractional mode, or 6.4 mA, to be used when PLL is set to integer mode. These slices can be selected by programming R34[3-0]. When PLL is set to fractional mode, a phase shift needs to be introduced to ensure consistent performance across operating conditions and a value of "010" should be programmed in R35[6-4]. When PLL is set to integer mode, a value of "000" should be programmed in R35[6-4].

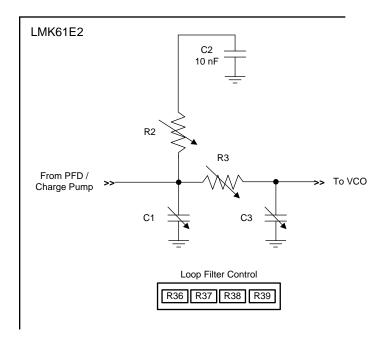

# 8.3.11 Loop Filter

The LMK61E2 features a fully integrated loop filter for the PLL and supports programmable loop bandwidth from 100 kHz to 1 MHz. The loop filter components, R2, C1, R3, C3, can be configured by programming R36, R37, R38 and R39 respectively. The LMK61E2 features a fixed value of C2 of 10 nF. When PLL is configured in the fractional mode, R35.2 should be set to "1". When reference doubler is disabled for integer mode PLL, R35.2 should be set to "0" and R38[6-0] should be set to "0000000". When reference doubler is enabled for integer mode PLL, R35.2 should be set to "1" and R38 and R39 are written with the appropriate values. Figure 25 shows the loop filter structure of the PLL. It is important to set the PLL to best possible bandwidth to minimize output jitter. TI provides the WEBENCH Clock Architect Tool that makes it easy to select the right loop filter components.

#### **Feature Description (continued)**

Figure 25. Loop Filter Structure of PLL

#### 8.3.12 VCO Calibration

The PLL in LMK61E2 is made of LC VCO that is designed using high-Q monolithic inductors to oscillate between 4.6 GHz and 5.6 GHz and has low phase noise characteristics. The VCO must be calibrated to ensure that the clock outputs deliver optimal phase noise performance. Fundamentally, a VCO calibration establishes an optimal operating point within the tuning range of the VCO. Setting R72.1 to "1" causes a VCO recalibration and is necessary after device reconfiguration. VCO calibration automatically occurs on device power up.

#### 8.3.13 High-Speed Output Divider

The high-speed output divider supports divide values of 5 to 511 and are programmed in R22 and R23. The output divider also supports coarse frequency margining that can initiate as low as a 5% change in the output frequency.

#### 8.3.14 High-Speed Clock Output

The clock output can be configured as LVPECL, LVDS, or HCSL by programming R21.1 and R21.0. Interfacing to LVPECL, LVDS, or HCSL receivers are done either with direct coupling or with AC-coupling capacitor as shown in Figure 3 - Figure 8.

The LVDS output structure has integrated 125 ohm termination between each side (P and N) of the differential pair. The HCSL output structure is open drain and can be DC or AC coupled to HCSL receivers with appropriate termination scheme. The LVPECL output structure is an emitter follower requiring external termination.

#### 8.3.15 Device Status

The PLL loss of lock and PLL calibration status can be monitored by reading R66.1 and R66.0. These bits represent a logic-high interrupt output and are self-cleared once the readback is complete.

#### 8.3.15.1 Loss of Lock

The PLL loss of lock detection circuit is a digital circuit that detects any frequency error, even a single cycle slip. Loss of lock may occur when an incorrect PLL configuration is programmed or the VCO has not been recalibrated.

SNAS674 – SEPTEMBER 2015 www.ti.com

# TEXAS INSTRUMENTS

#### 8.4 Device Functional Modes

#### 8.4.1 Interface and Control

The host (DSP, Microcontroller, FPGA, etc) configures and monitors the LMK61E2 via the I<sup>2</sup>C port. The host reads and writes to a collection of control/status bits called the register map. The device blocks can be controlled and monitored via a specific grouping of bits located within the register file. The host controls and monitors certain device Wide critical parameters directly via register control/status bits. In the absence of the host, the LMK61E2 can be configured to operate from its on-chip EEPROM. The EEPROM array is automatically copied to the device registers upon powerup. The user has the flexibility to re Write the contents of EEPROM from the SRAM up to a 100 times.

Within the device registers, there are certain bits that have read/write access. Other bits are read-only (an attempt to write to a read only bit will not change the state of the bit). Certain device registers and bits are reserved meaning that they must not be changed from their default reset state. Figure 28 shows interface and control blocks within LMK61E2 and the arrows refer to read access from and write access to the different embedded memories (EEPROM, SRAM).

Figure 26. LMK61E2 Interface and Control Block

# 8.5 Programming

www.ti.com

#### 8.5.1 I<sup>2</sup>C Serial Interface

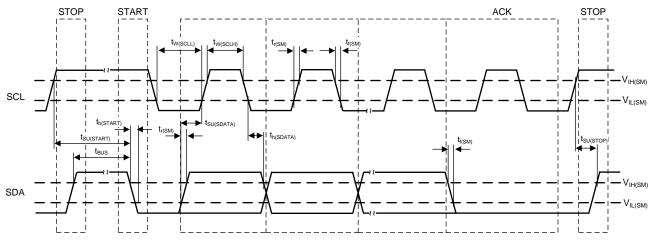

The I<sup>2</sup>C port on the LMK61E2 works as a slave device and supports both the 100 kHz standard mode and 400 kHz fast mode operations. Fast mode imposes a glitch tolerance requirement on the control signals. Therefore, the input receivers ignore pulses of less than 50 ns duration. The I<sup>2</sup>C timing is given in Table 4. The timing diagram is given in Figure 27.

Figure 27. I<sup>2</sup>C Timing Diagram

In an I<sup>2</sup>C bus system, the LMK61E2 acts as a slave device and is connected to the serial bus (data bus SDA and lock bus SCL). These are accessed via a 7-bit slave address transmitted as part of an I<sup>2</sup>C packet. Only the device with a matching slave address responds to subsequent I<sup>2</sup>C commands. In soft pin mode, the LMK61E2 allows up to three unique slave devices to occupy the I<sup>2</sup>C bus based on the pin strapping of ADD (tied to VDD, GND or left open). The device slave address is 10110xx (the two LSBs are determined by the ADD pin).

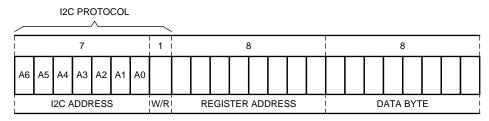

During the data transfer through the I<sup>2</sup>C interface, one clock pulse is generated for each data bit transferred. The data on the SDA line must be stable during the high period of the clock. The high or low state of the data line can change only when the clock signal on the SCL line is low. The start data transfer condition is characterized by a high-to-low transition on the SDA line while SCL is high. The stop data transfer condition is characterized by a low-to-high transition on the SDA line while SCL is high. The start and stop conditions are always initiated by the master. Every byte on the SDA line must be eight bits long. Each byte must be followed by an acknowledge bit and bytes are sent MSB first. The I<sup>2</sup>C register structure of the LMK61E2 is shown in Figure 28.

Figure 28. I<sup>2</sup>C Register Structure

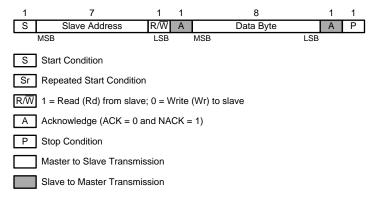

The acknowledge bit (A) or non-acknowledge bit (A') is the 9th bit attached to any 8-bit data byte and is always generated by the receiver to inform the transmitter that the byte has been received (when A = 0) or not (when A' = 0). A = 0 is done by pulling the SDA line low during the 9th clock pulse and A' = 0 is done by leaving the SDA line high during the 9th clock pulse.

# TEXAS INSTRUMENTS

## Programming (continued)

The I<sup>2</sup>C master initiates the data transfer by asserting a start condition which initiates a response from all slave devices connected to the serial bus. Based on the 8-bit address byte sent by the master over the SDA line (consisting of the 7-bit slave address (MSB first) and an R/W' bit), the device whose address corresponds to the transmitted address responds by sending an acknowledge bit. All other devices on the bus remain idle while the selected device waits for data transfer with the master.

After the data transfer has occurred, stop conditions are established. In write mode, the master asserts a stop condition to end data transfer during the 10th clock pulse following the acknowledge bit for the last data byte from the slave. In read mode, the master receives the last data byte from the slave but does not pull SDA low during the 9th clock pulse. This is known as a non-acknowledge bit. By receiving the non-acknowledge bit, the slave knows the data transfer is finished and enters the idle mode. The master then takes the data line low during the low period before the 10th clock pulse, and high during the 10th clock pulse to assert a stop condition. A generic transation is shown in Figure 29.

Figure 29. Generic Programming Sequence

The LMK61E2 I<sup>2</sup>C interface supports "Block Register Write/Read", "Read/Write SRAM", and "Read/Write EEPROM" operations. For "Block Register Write/Read" operations, the I<sup>2</sup>C master can individually access addressed registers that are made of an 8-bit data byte. The offset of the indexed register is encoded in the register address, as described in Table 1 below.

**Table 1. Slave Address Byte**

| DEVICE  | A6 | A5 | A4 | А3 | A2 | ADD          | R/W |

|---------|----|----|----|----|----|--------------|-----|

| LMK61E2 | 1  | 0  | 1  | 1  | 0  | 00, 01 or 10 | 1/0 |

#### 8.5.2 Block Register Write

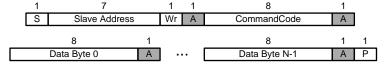

The I<sup>2</sup>C "Block Register Write" transaction is illustrated in Figure 30 and consists of the following sequence.

- 1. Master issues a Start Condition.

- 2. Master writes the 7-bit Slave Address following by a Write bit.

- 3. Master writes the 8-bit Register address as the CommandCode of the programming sequence.

- 4. Master writes one or more data bytes each of which should be acknowledged by the slave. The slave increments the internal register address after each byte.

- 5. Master issues a Stop Condition to terminate the transaction.

Figure 30. "Block Register Write" Programming Sequence

Submit Documentation Feedback

www.ti.com

# 8.5.3 Block Register Read

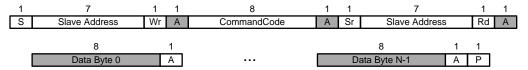

The I<sup>2</sup>C "Block Register Read" transaction is illustrated in Figure 31 and consists of the following sequence.

- 1. Master issues a Start Condition.

- 2. Master writes the 7-bit Slave Address followed by a Write bit.

- 3. Master writes the 8-bit Register address as the CommandCode of the programming sequence.

- 4. Master issues a Repeated Start Condition.

- 5. Master writes the 7-bit Slave Address following by a Read bit.

- 6. Slave returns one or more data bytes as long as the Master continues to acknowledge them. The slave increments the internal register address after each byte.

- 7. Master issues a Stop Condition to terminate the transaction.

Figure 31. "Block Register Read" Programming Sequence

#### 8.5.4 Write SRAM

The on-chip SRAM is a volatile, shadow memory array used to temporarily store register data, and is intended only for programming the non Volatile EEPROM. The SRAM has the identical data format as the EEPROM map. The register configuration data can be transferred to the SRAM array through special memory access registers in the register map. In order to successfully program the SRAM, the complete base array and at least one page should be written. The following details the programming sequence to transfer the device registers into the SRAM.

- 1. Program the device registers to match a desired setting.

- 2. Write a "1" to R49.6. This ensures that the device registers are copied to the SRAM.

The SRAM can also be written with particular values according to the following programming seguence.

- 1. Write the SRAM address in R51.

- 2. Write the desired data byte in R53 in the same I<sup>2</sup>C transaction and this data byte will be written to the address specified in the step above. Any additional access that is part of the same transaction will cause the SRAM address to be incremented and a write will take place to the next SRAM address. Access to SRAM will terminate at the end of current I<sup>2</sup>C transaction.

#### NOTE

It is possible to increment SRAM address incorrectly when 2 successive accesses are made to R51.

#### 8.5.5 Write EEPROM

The on-chip EEPROM is a non Volatile memory array used to permanently store register data for a custom device start-up configuration setting to initialize registers upon power-up or POR. The EEPROM is comprised of bits shown in the EEPROM Map. The transfer must first happen to the SRAM and then to the EEPROM. During "EEPROM write", R49.2 is a "1" and the EEPROM contents cannot be accessed. The following details the programming sequence to transfer the entire contents of SRAM to EEPROM.

- 1. Make sure the "Write SRAM" procedure (Write SRAM) was done to commit the register settings to the SRAM with start-up configurations intended for programming to the EEPROM.

- 2. Write "0xBE" to R56. This provides basic protection from inadvertent programming of EEPROM.

- 3. Write a "1" to R49.0. This programs the entire SRAM contents to EEPROM. Once completed, the contents in R48 will increment by 1. R48 contains the total number of EEPROM programming cycles that are successfully completed.

- 4. Write "0x00" to R56 to protect against inadvertent programming of EEPROM.

#### 8.5.6 Read SRAM

The contents of the SRAM can be read out, one word at a time, starting with that of the requested address. Following details the programming sequence for an SRAM read by address.

- 1. Write the SRAM address in R51.

- 2. The SRAM data located at the address specified in the step above can be obtained by reading R53 in the same I<sup>2</sup>C transaction. Any additional access that is part of the same transaction will cause the SRAM address to be incremented and a read will take place of the next SRAM address. Access to SRAM will terminate at the end of current I<sup>2</sup>C transaction.

#### NOTE

It is possible to increment SRAM address incorrectly when 2 successive accesses are made to R51.

#### 8.5.7 Read EEPROM

The contents of the EEPROM can be read out, one word at a time, starting with that of the requested address. Following details the programming sequence for an EEPROM read by address.

- 1. Write the EEPROM address in R51.

- 2. The EEPROM data located at the address specified in the step above can be obtained by reading R52 in the same I<sup>2</sup>C transaction. Any additional access that is part of the same transaction will cause the EEPROM address to be incremented and a read will take place of the next EEPROM address. Access to EEPROM will terminate at the end of current I<sup>2</sup>C transaction.

#### NOTE

It is possible to increment EEPROM address incorrectly when 2 successive accesses are made to R51.

Product Folder Links: LMK61E2

Submit Documentation Feedback

www.ti.com

# 8.6 Register Map

| Name                | Addr | Reset | Bit7            | Bit6           | Bit5           | Bit4  | Bit3           | Bit2      | Bit1         | Bit0       |

|---------------------|------|-------|-----------------|----------------|----------------|-------|----------------|-----------|--------------|------------|

| VNDRID_BY1          | 0    | 0x10  | VNDRID[15:8]    | ,              |                |       | ·              |           | 1            |            |

| VNDRID_BY0          | 1    | 0x0B  | VNDRID[7:0]     |                |                |       |                |           |              |            |

| PRODID              | 2    | 0x33  | PRODID[7:0]     |                |                |       |                |           |              |            |

| REVID               | 3    | 0x00  | REVID[7:0]      |                |                |       |                |           |              |            |

| SLAVEADR            | 8    | 0xB0  | SLAVEADR[7:1]   |                |                |       |                |           |              | RSRVD      |

| EEREV               | 9    | 0x00  | EEREV[7:0]      |                |                |       |                |           |              |            |

| DEV_CTL             | 10   | 0x01  | RSRVD           | PLL_PDN        | RSRVD          |       |                |           | ENCAL        | AUTOSTRT   |

| XO_CAPCTRL_<br>BY1  | 16   | 0x00  | RSRVD           |                |                |       |                |           | XO_CAPCTRL   | 1:0]       |

| XO_CAPCTRL_<br>BY0  | 17   | 0x00  | XO_CAPCTRL[9:2] |                |                |       |                |           |              |            |

| DIFFCTL             | 21   | 0x01  | DIFF_OUT_PD     | RSRVD          |                |       |                |           | OUT_SEL[1:0] |            |

| OUTDIV_BY1          | 22   | 0x00  | RSRVD           |                |                |       |                |           |              | OUT_DIV[8] |

| OUTDIV_BY0          | 23   | 0x20  | OUT_DIV[7:0]    |                |                |       |                |           |              |            |

| PLL_NDIV_BY1        | 25   | 0x00  | RSRVD           |                |                |       | PLL_NDIV[11:8] |           |              |            |

| PLL_NDIV_BY0        | 26   | 0x64  | PLL_NDIV[7:0]   |                |                |       |                |           |              |            |

| PLL_FRACNUM_<br>BY2 | 27   | 0x00  | RSRVD           |                | PLL_NUM[21:16] |       |                |           |              |            |

| PLL_FRACNUM_<br>BY1 | 28   | 0x00  | PLL_NUM[15:8]   |                |                |       |                |           |              |            |

| PLL_FRACNUM_<br>BY0 | 29   | 0x00  | PLL_NUM[7:0]    |                |                |       |                |           |              |            |

| PLL_FRACDEN_<br>BY2 | 30   | 0x00  | RSRVD           |                | PLL_DEN[21:16] |       |                |           |              |            |

| PLL_FRACDEN_<br>BY1 | 31   | 0x00  | PLL_DEN[15:8]   |                |                |       |                |           |              |            |

| PLL_FRACDEN_<br>BY0 | 32   | 0x00  | PLL_DEN[7:0]    |                |                |       |                |           |              |            |

| PLL_MASHCTRL        | 33   | 0x0C  | RSRVD           |                |                |       | PLL_DTHRMODE   | [1:0]     | PLL_ORDER[1  | :0]        |

| PLL_CTRL0           | 34   | 0x24  | RSRVD           |                | PLL_D          | RSRVD | PLL_CP[3:0]    |           |              |            |

| PLL_CTRL1           | 35   | 0x03  | RSRVD           | PLL_CP_PHASE_  | SHIFT[2:0]     |       | RSRVD          | PLL_DISAE | BLE_4TH[2:0] |            |

| PLL_LF_R2           | 36   | 0x28  | PLL_LF_R2[7:0]  |                |                |       |                |           |              |            |

| PLL_LF_C1           | 37   | 0x00  | RSRVD           |                |                |       |                | PLL_LF_C  | 1[2:0]       |            |

| PLL_LF_R3           | 38   | 0x00  | RSRVD           | PLL_LF_R3[6:0] |                |       |                |           |              |            |

| PLL_LF_C3           | 39   | 0x00  | RSRVD           |                |                |       |                | PLL_LF_C3 | 3[2:0]       |            |

| PLL_CALCTRL         | 40   | 0x00  | RSRVD           |                |                |       | PLL_CLSDWAIT[1 | :0]       | PLL_VCOWAIT  | [1:0]      |

Submit Documentation Feedback

23

24

# TEXAS INSTRUMENTS

# **Register Map (continued)**

| Name     | Addr | Reset | Bit7         | Bit6        | Bit5      | Bit4       | Bit3      | Bit2    | Bit1     | Bit0    |

|----------|------|-------|--------------|-------------|-----------|------------|-----------|---------|----------|---------|

| NVMSCRC  | 47   | 0x00  | NVMSCRC[7:0] |             |           |            |           |         |          |         |

| NVMCNT   | 48   | 0x00  | NVMCNT[7:0]  |             |           |            |           |         |          |         |

| NVMCTL   | 49   | 0x10  | RSRVD        | REGCOMMIT   | NVMCRCERR | NVMAUTOCRC | NVMCOMMIT | NVMBUSY | NVMERASE | NVMPROG |

| NVMLCRC  | 50   | 0x00  | NVMLCRC[7:0] |             |           |            | •         |         |          |         |

| MEMADR   | 51   | 0x00  | RSRVD        | MEMADR[6:0] |           |            |           |         |          |         |

| NVMDAT   | 52   | 0x00  | NVMDAT[7:0]  |             |           |            |           |         |          |         |

| RAMDAT   | 53   | 0x00  | RAMDAT[7:0]  |             |           |            |           |         |          |         |

| NVMUNLK  | 56   | 0x00  | NVMUNLK[7:0] |             |           |            |           |         |          |         |

| INT_LIVE | 66   | 0x00  | RSRVD        |             |           |            |           |         | LOL      | CAL     |

| SWRST    | 72   | 0x00  | RSRVD        |             |           |            |           |         | SWR2PLL  | RSRVD   |

## 8.6.1 Register Descriptions

#### 8.6.1.1 VNDRID\_BY1 Register; R0

VNDRID\_BY1 and VNDRID\_BY0 registers are used to store the unique 16-bit Vendor Identification number assigned to I<sup>2</sup>C vendors.

| Bit # | Field        | Туре | Reset | NVM | Description                          |

|-------|--------------|------|-------|-----|--------------------------------------|

| [7:0] | VNDRID[15:8] | R    | 0x10  | N   | Vendor Identification Number Byte 1. |

## 8.6.1.2 VNDRID\_BY0 Register; R1

VNDRID\_BY1 and VNDRID\_BY0 registers are used to store the unique 16-bit Vendor Identification number assigned to I<sup>2</sup>C vendors.

| Bit # | Field       | Туре | Reset | NVM | Description                          |

|-------|-------------|------|-------|-----|--------------------------------------|

| [7:0] | VNDRID[7:0] | R    | 0xB   | N   | Vendor Identification Number Byte 0. |

#### 8.6.1.3 PRODID Register; R2

The Product Identification Number is a unique 8-bit identification number used to identify the LMK61E2.

| Bit # | Field       | Туре | Reset | NVM | Description                    |

|-------|-------------|------|-------|-----|--------------------------------|

| [7:0] | PRODID[7:0] | R    | 0x33  | N   | Product Identification Number. |

#### 8.6.1.4 REVID Register; R3

The REVID register is used to identify the LMK61E2 mask revision.

| Bit # | Field      | Туре | Reset | NVM | Description                                                                                                                         |

|-------|------------|------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------|

| [7:0] | REVID[7:0] | R    | 0x0   | N   | Device Revision Number. The Device Revision Number is used to identify the LMK61E2 mask-set revision used to fabricate this device. |

#### 8.6.1.5 SLAVEADR Register; R8

The SLAVEADR register reflects the 7-bit I<sup>2</sup>C Slave Address value initialized from from on-chip EEPROM.

| Bit # | Field         | Туре | Reset | NVM | Description                                                                                                                                                                                                                  |   |  |

|-------|---------------|------|-------|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|--|

| [7:1] | SLAVEADR[7:1] | R    | 0x58  | Υ   | I <sup>2</sup> C Slave Address. This field holds the 7-bit Slave Address used to identify this device during I <sup>2</sup> C transactions. The two least significant bits of the addrecan be configured using ADD as shown. |   |  |

|       |               |      |       |     | SLAVEADR[2:1] ADD                                                                                                                                                                                                            |   |  |

|       |               |      |       |     | 00                                                                                                                                                                                                                           | 0 |  |

|       |               |      |       |     | 01 Float                                                                                                                                                                                                                     |   |  |

|       |               |      |       |     | 10                                                                                                                                                                                                                           | 1 |  |

| [0]   | RSRVD         | -    | -     | N   | Reserved.                                                                                                                                                                                                                    |   |  |

#### 8.6.1.6 EEREV Register; R9

The EEREV register provides an EEPROM image revision record. EEPROM Image Revision is automatically retrieved from EEPROM and stored in the EEREV register after a reset or after a NVM commit operation.

| Bit # | Field      | Туре | Reset | NVM | Description              |

|-------|------------|------|-------|-----|--------------------------|

| [7:0] | EEREV[7:0] | R    | 0x0   | Υ   | EEPROM Image Revision ID |

## 8.6.1.7 DEV\_CTL Register; R10

The DEV\_CTL register holds the control functions described in the following table.

| Bit # | Field         | Туре | Reset | NVM | Description                                                                                                                                                                                                                                                                                                                                                                                           | Description  |  |  |

|-------|---------------|------|-------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------|--|--|

| [7]   | RESERVED      | -    | 0     | Υ   | Reserved.                                                                                                                                                                                                                                                                                                                                                                                             |              |  |  |

| [6]   | PLL_PDN       | RW   | 0     | Y   | PLL Powerdown. The PLL_PDN bit determines whether PLL is automatically enabled and calibrated after a hardware reset. If the PLL_PDN bit is set to 1 during normal operation then PLL is disabled and the calibratio circuit is reset. When PLL_PDN is then cleared to 0 PLL re-enabled and the calibration sequence is automatically restarted.                                                      |              |  |  |

|       |               |      |       |     | PLL_PDN                                                                                                                                                                                                                                                                                                                                                                                               | Value        |  |  |

|       |               |      |       |     | 0                                                                                                                                                                                                                                                                                                                                                                                                     | PLL Enabled  |  |  |

|       |               |      |       |     | 1                                                                                                                                                                                                                                                                                                                                                                                                     | PLL Disabled |  |  |

| [5:2] | RESERVED[5:2] | RW   | 0     | Υ   | Reserved.                                                                                                                                                                                                                                                                                                                                                                                             |              |  |  |

| [1]   | ENCAL         | RWSC | 0     | N   | Enable Frequency Calibration. Triggers PLL/VCO calibration on both PLLs in parallel on 0 -> 1 transition of ENCAL. This bit is self-clearing and set to a 0 after PLL/VCO calibration is complete. In powerup or software rest mode, AUTOSTRT takes precedence.                                                                                                                                       |              |  |  |

| [0]   | AUTOSTRT      | RW   | 1     | Y   | Autostart. If AUTOSTRT is set to 1 the device will automatically attempt to achieve lock and enable outputs after a device reset. A device reset can be triggered by the power-on-reset, RESETn pin or by writing to the RESETN_SW bit. If AUTOSTRT is 0 then the device will halt after the configuration phase, a subsequent write to set the AUTOSTRT bit to 1 will trigger the PLL Lock sequence. |              |  |  |

# 8.6.1.8 XO\_CAPCTRL\_BY1 Register; R16

XO Margining Offset Value bits[9:8]

| Bit # | Field            | Туре | Reset | NVM | Description                |

|-------|------------------|------|-------|-----|----------------------------|

| [7:2] | RSRVD[5:0]       | -    | -     | N   | Reserved.                  |

| [1:0] | XO_CAPCTRL [1:0] | RW   | 0x0   | Υ   | XO Offset Value bits [1:0] |

# 8.6.1.9 XO\_CAPCTRL\_BY0 Register; R17

XO margining Offset Value bits[7:0]

| Bit # | Field            | Туре | Reset | NVM | Description               |

|-------|------------------|------|-------|-----|---------------------------|

| [7:0] | XO_CAPCTRL [9:2] | RW   | 0x0   | Υ   | XO Offset Value bits[9:2] |

## 8.6.1.10 DIFFCTL Register; R21

The DIFFCTL register provides control over Output.

| Bit # | Field        | Туре   | Reset | NVM | Description                                                   |                  |

|-------|--------------|--------|-------|-----|---------------------------------------------------------------|------------------|

| [7]   | DIFF_OUT_PD  | RW     | 0     | N   | Power down differential                                       | output buffer.   |

| [6:2] | RESERVED     | -      | -     | N   | Reserved.                                                     |                  |

| [1:0] | OUT_SEL[1:0] | RW 0x1 | 0x1 Y |     | Format Select. The OUT_SEL field atput Driver as shown below. |                  |

|       |              |        |       |     | OUT_SEL                                                       | OUTPUT OPERATION |