### **General Description**

The Himalaya series of voltage regulator ICs and power modules enable cooler, smaller, and simpler power supply solutions. The MAXM17544 is an easy-to-use, step-down power module that combines a switching power supply controller, dual n-channel MOSFET power switches, fully shielded inductor, and the compensation components in a low-profile, thermally-efficient, system-in-package (SiP). The device operates over a wide input voltage range of 4.5V to 42V and delivers up to 3.5A continuous output current with excellent line and load regulation over an output voltage range of 0.9V to 12V. The device only requires five external components to complete the total power solution. The high level of integration significantly reduces design complexity, manufacturing risks, and offers a true plug-and-play power supply solution, reducing time-to-market.

The device can be operated in the pulse-width modulation (PWM), pulse-frequency modulation (PFM), or discontinuous conduction mode (DCM) control schemes.

The MAXM17544 is available in a low-profile, highly thermal-emissive, compact, 29-pin 9mm x 15mm x 2.8mm SiP package that reduces power dissipation in the package and enhances efficiency. The package is easily soldered onto a printed circuit board and suitable for automated circuit board assembly. The device can operate over the industrial temperature range from -40°C to +125°C.

### **Applications**

- Industrial Power Supplies

- Distributed Supply Regulation

- FPGA and DSP Point-of-Load Regulator

- Base Station Point-of-Load Regulator

- HVAC and Building Control

Ordering Information appears at end of data sheet.

#### **Features and Benefits**

- Reduces Design Complexity, Manufacturing Risks, and Time-to-Market

- Integrated Switching Power Supply Controller and Dual-MOSFET Power Switches

- · Integrated Inductor

- Integrated Compensation Components

- · Integrated Thermal-Fault Protection

- Integrated Peak Current Limit

- Saves Board Space in Space-Constrained Applications

- Complete Integrated Step-Down Power Supply in a Single Package

- Small Profile 9mm x 15mm x 2.8mm SiP Package

- Simplified PCB Design with Minimal External BOM Components

- Offers Flexibility for Power-Design Optimization

- Wide Input Voltage Range from 4.5V to 42V

- Output-Voltage Adjustable Range from 0.9V to 12V

- Adjustable Frequency with External Frequency Synchronization (100kHz to 1.8MHz)

- · Soft-Start Programmable

- Autoswitch PWM, PFM, or DCM Current-Mode Control

- Optional Programmable EN/UVLO

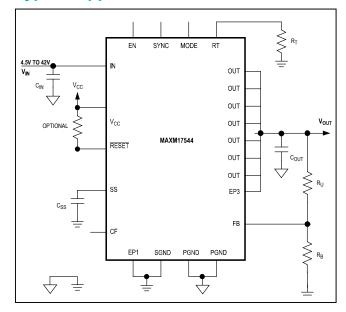

### **Typical Application Circuit**

## 4.5V to 42V, 3.5A High-Efficiency, DC-DC Step-Down Power Module with Integrated Inductor

### **Absolute Maximum Ratings (Notes 1, 2)**

| IN to PGND (Note 2)                 | 0.3V to +48V                        |

|-------------------------------------|-------------------------------------|

| EN to SGND (Note 2)                 | 0.3V to +48V                        |

| V <sub>CC</sub>                     | 0.3V to min $(V_{IN} + 0.3V, 6.5V)$ |

| FB, RESET, SS, CF, MODE,            |                                     |

| SYNC, RT to SGND                    | 0.3V to +6.5V                       |

| OUT to PGND (V <sub>IN</sub> < 25V) | 0.3V to (V <sub>IN</sub> + 0.3V)    |

| OUT to PGND (V <sub>IN</sub> ≥ 25V) | 0.3V to +25V                        |

| LX to PGND                          | 0.3V to (V <sub>IN</sub> + 0.3V)    |

| BST to PGND                        | 0.3V to +53V   |

|------------------------------------|----------------|

| BST to V <sub>CC</sub>             | 0.3V to +48V   |

| BST to LX                          | 0.3V to +6.5V  |

| Operating Temperature Range        | 40°C to +125°C |

| Junction Temperature               | +125°C         |

| Storage Temperature Range          | 65°C to +125°C |

| Lead Temperature (soldering, 10s). | +245°C         |

### **Package Thermal Characteristics (Note 3)**

Junction-to-Top-Case Thermal Resistance ( $\Psi_{JT}$ )..........5.2°C/W Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).........25.2°C/W

- Note 1: SGND and PGND are internally connected.

- Note 2: See Pin Description for the connection of the backside exposed pad.

- Note 3: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### **Electrical Characteristics**

$(V_{IN} = V_{EN} = 24V, R_{RT} = 40.2k\Omega (500kHz) \text{ to SGND}, V_{PGND} = V_{MODE} = V_{SYNC} = V_{SGND} = 0V, V_{CC} = LX = SS = \overline{RESET} = OUT = open, V_{BST} \text{ to } V_{LX} = 5V, V_{FB} = 1V, T_A = T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ . All voltages are referenced to SGND, unless otherwise noted.) (Note 4)

| PARAMETER                            | SYMBOL                          | CONDITIONS                                                | MIN   | TYP   | MAX   | UNITS |

|--------------------------------------|---------------------------------|-----------------------------------------------------------|-------|-------|-------|-------|

| INPUT SUPPLY (V <sub>IN</sub> )      | INPUT SUPPLY (V <sub>IN</sub> ) |                                                           |       |       |       |       |

| IN Input Voltage Range               | V <sub>IN</sub>                 |                                                           | 4.5   |       | 42    | V     |

| Input Shutdown Current               | I <sub>IN_SH</sub>              | V <sub>EN</sub> = 0V                                      |       | 10.5  | 13    | μA    |

|                                      | I <sub>Q_PFM_</sub><br>HIB      | MODE = RT = open                                          |       | 125   |       | μA    |

| Input Quiescent Current              | I <sub>Q_DCM</sub>              | MODE = V <sub>CC</sub>                                    |       | 1.16  | 1.8   | mA    |

|                                      | I <sub>Q_PWM</sub>              | Normal switching mode, no load                            |       | 9.5   |       | mA    |

| LOGIC INPUTS                         |                                 |                                                           |       |       |       |       |

| EN Threshold                         | V <sub>ENR</sub>                | V <sub>EN</sub> rising                                    | 1.192 | 1.215 | 1.26  | V     |

| EN THESHOU                           | V <sub>ENF</sub>                | V <sub>EN</sub> falling                                   | 1.068 | 1.09  | 1.131 | V     |

| Enable Pullup Resistor               | R <sub>ENP</sub>                | Pullup resistor between IN and EN pins                    | 3.15  | 3.3   | 3.45  | МΩ    |

| LDO                                  |                                 |                                                           |       |       |       |       |

| V <sub>CC</sub> Output Voltage Range | V <sub>CC</sub>                 | 6V < V <sub>IN</sub> < 42V, 1mA < I <sub>VCC</sub> < 25mA | 4.75  | 5     | 5.25  | V     |

| V <sub>CC</sub> Current Limit        | I <sub>VCC_MAX</sub>            | V <sub>IN</sub> = 6V, V <sub>CC</sub> = 4.3V              | 26.5  | 60    | 100   | mA    |

| V <sub>CC</sub> Dropout              | V <sub>CC_DO</sub>              | V <sub>IN</sub> = 4.5V, I <sub>VCC</sub> = 20mA           | 4.2   |       |       | V     |

| V INC                                | V <sub>CC_UVR</sub>             | V <sub>CC</sub> rising                                    | 4.05  | 4.2   | 4.3   | V     |

| V <sub>CC</sub> UVLO                 | V <sub>CC_UVF</sub>             | V <sub>CC</sub> falling                                   | 3.65  | 3.8   | 3.9   | V     |

### **Electrical Characteristics (continued)**

$(V_{IN} = V_{EN} = 24V, R_{RT} = 40.2k\Omega (500kHz) \text{ to SGND}, V_{PGND} = V_{MODE} = V_{SYNC} = V_{SGND} = 0V, V_{CC} = LX = SS = \overline{RESET} = OUT = open, V_{BST} \text{ to } V_{LX} = 5V, V_{FB} = 1V, T_A = T_J = -40^{\circ}\text{C} \text{ to } +125^{\circ}\text{C}, \text{ unless otherwise noted.}$  Typical values are at  $T_A = +25^{\circ}\text{C}$ . All voltages are referenced to SGND, unless otherwise noted.) (Note 4)

| PARAMETER                                               | SYMBOL                 | CONDITIONS                                                          | MIN                   | TYP                | MAX             | UNITS  |  |

|---------------------------------------------------------|------------------------|---------------------------------------------------------------------|-----------------------|--------------------|-----------------|--------|--|

| OUTPUT SPECIFICATIONS                                   |                        |                                                                     |                       |                    |                 |        |  |

| Line Regulation Accuracy                                |                        | V <sub>IN</sub> = 6.5V to 42V, V <sub>OUT</sub> = 5V                |                       | 0.1                |                 | mV/V   |  |

| Load Regulation Accuracy                                |                        | Tested with I <sub>OUT</sub> = 0A and 1A                            |                       | 1                  |                 | mV/A   |  |

| ED Dogulation Valtage                                   | V                      | MODE = SGND                                                         | 0.887                 |                    | 0.910           | V      |  |

| FB Regulation Voltage                                   | V <sub>FB_REG</sub>    | MODE = open                                                         | 0.890                 | 0.915              | 0.936           | V      |  |

| FB Input Bias Current                                   | I <sub>FB</sub>        | 0V < V <sub>FB</sub> < 1V, T <sub>A</sub> = +25°C                   | -50                   |                    | +50             | nA     |  |

| FB Undervoltage Trip Level to Cause Hiccup              | V <sub>FB_HICF</sub>   |                                                                     | 0.56                  | 0.58               | 0.65            | V      |  |

| Hiccup Timeout                                          |                        |                                                                     |                       | 32,768             |                 | Cycles |  |

| SOFT-START (SS)                                         |                        |                                                                     |                       |                    |                 |        |  |

| Charging Current                                        | I <sub>SS</sub>        | V <sub>SS</sub> = 0.5V                                              | 4.7                   | 5                  | 5.3             | μA     |  |

| RT AND SYNC                                             |                        |                                                                     |                       |                    |                 |        |  |

|                                                         |                        | $R_{RT} = 210k\Omega$                                               | 90                    | 100                | 110             | kHz    |  |

| Switching Frequency                                     | f <sub>SW</sub>        | $R_{RT} = 9.76k\Omega$                                              |                       | 1800               |                 | kHz    |  |

|                                                         |                        | R <sub>RT</sub> = open                                              | 450                   | 500                | 550             | kHz    |  |

| SYNC Frequency Range                                    |                        |                                                                     | 1.1x                  |                    | 1.4x            | kHz    |  |

|                                                         |                        |                                                                     | f <sub>SW</sub>       |                    | f <sub>SW</sub> | IXI IZ |  |

| SYNC Pulse Width                                        |                        |                                                                     | 50                    |                    |                 | ns     |  |

| SYNC Threshold                                          | V <sub>IH</sub>        |                                                                     | 2.1                   |                    |                 | V      |  |

|                                                         | V <sub>IL</sub>        |                                                                     |                       |                    | 0.8             |        |  |

| MODE                                                    |                        |                                                                     |                       |                    |                 | ı      |  |

|                                                         | V <sub>M_DCM</sub>     | MODE = V <sub>CC</sub> (DCM mode)                                   | V <sub>CC</sub> - 1.6 | <u> </u>           |                 |        |  |

| MODE Threshold                                          | V <sub>M_PFM</sub>     | MODE = open (PFM mode)                                              |                       | V <sub>CC</sub> /2 |                 | V      |  |

|                                                         | V <sub>M_PWM</sub>     | MODE = GND (PWM mode)                                               |                       |                    | 1.4             |        |  |

| CURRENT LIMIT                                           |                        |                                                                     |                       |                    |                 |        |  |

| Average Current-Limit Threshold                         | I <sub>AVG_LIMIT</sub> | V <sub>OUT</sub> = V <sub>FB</sub> = 0.8V, f <sub>SW</sub> = 200kHz |                       | 4.6                |                 | Α      |  |

| RESET                                                   | <u>-</u>               |                                                                     |                       |                    |                 | L      |  |

| RESET Output Level Low                                  |                        | I <sub>RESET</sub> = 10mA                                           |                       |                    | 0.4             | V      |  |

| RESET Output Leakage Current                            |                        | $V_{RESET} = 5.5V, T_A = T_J = +25^{\circ}C$                        | -0.1                  |                    | +0.1            | μA     |  |

| FB Threshold for RESET Assertion                        | V <sub>FB_OKF</sub>    | V <sub>FB</sub> falling                                             | 90.5                  | 92                 | 94.6            | %      |  |

| FB Threshold for RESET Deassertion                      | V <sub>FB_OKR</sub>    | V <sub>FB</sub> rising                                              | 93.8                  | 95                 | 97.8            | %      |  |

| RESET Deassertion Delay After FB Reaches 95% Regulation |                        |                                                                     |                       | 1024               |                 | Cycles |  |

| THERMAL SHUTDOWN                                        |                        |                                                                     |                       |                    |                 |        |  |

| Thermal-Shutdown Threshold                              |                        | Temperature rising                                                  |                       | +165               |                 | °C     |  |

| Thermal-Shutdown Hysteresis                             |                        |                                                                     |                       | 10                 |                 | °C     |  |

Note 4: All limits are 100% tested at  $T_A = +25$ °C. Maximum and minimum limits are guaranteed by design and characterized over temperature.

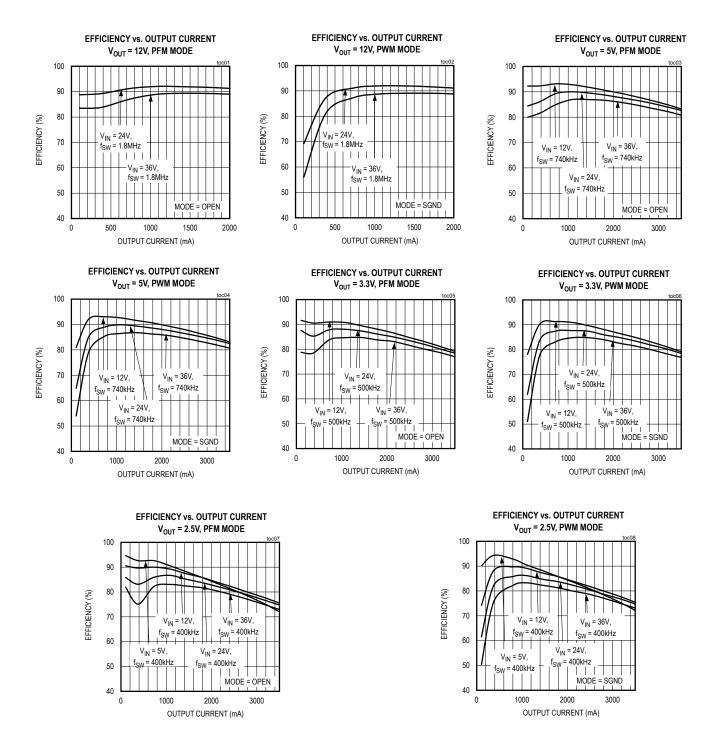

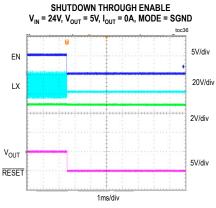

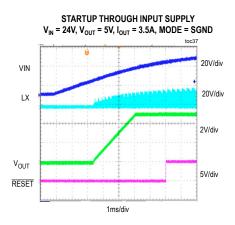

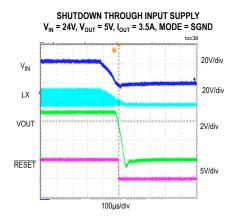

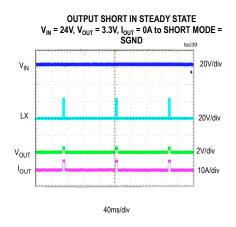

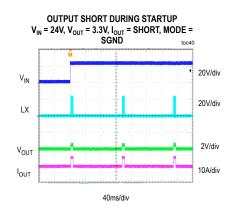

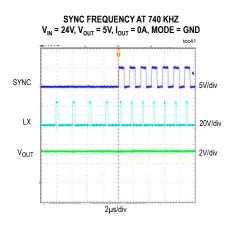

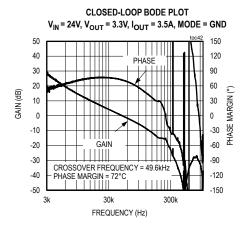

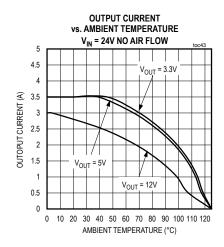

### **Typical Operating Characteristics**

$(V_{IN} = 4.5V \text{ to } 42V, V_{OUT} = 0.9 \text{ to } 12V, I_{OUT} = 0A-3.5A, T_A = +25^{\circ}C, unless otherwise noted.)$

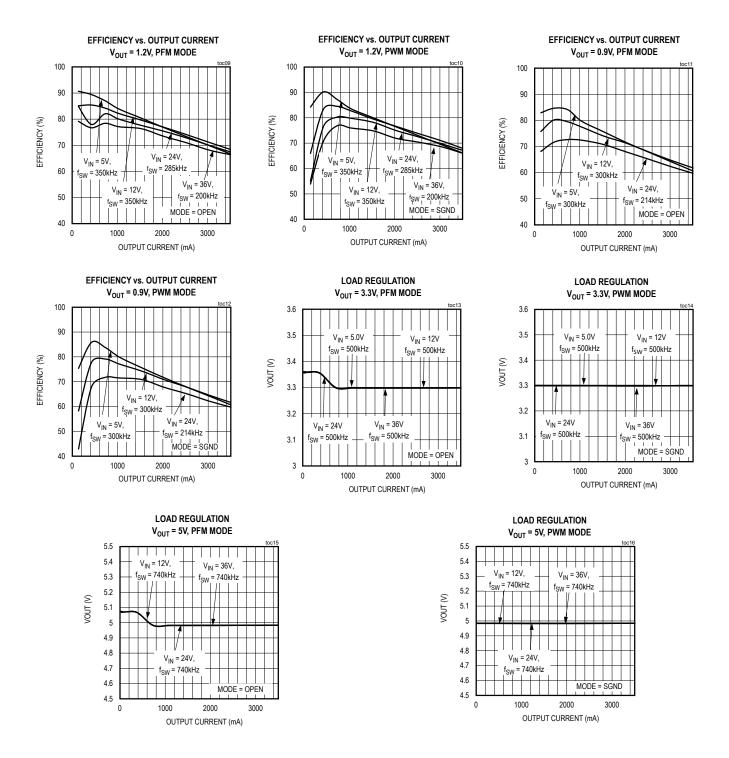

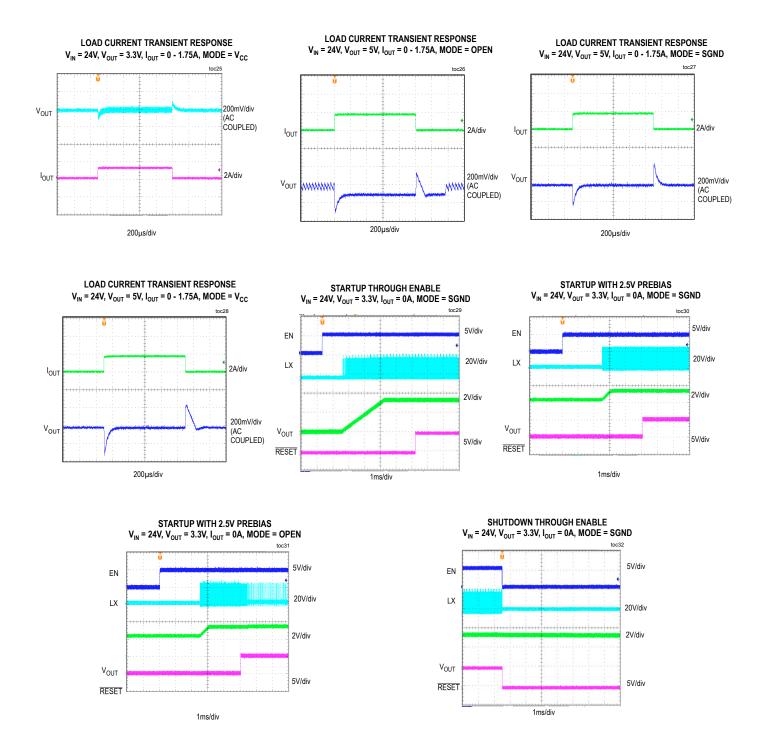

### **Typical Operating Characteristics (continued)**

$(V_{IN} = 4.5V \text{ to } 42V, V_{OUT} = 0.9 \text{ to } 12V, I_{OUT} = 0A-3.5A, T_A = +25^{\circ}C, unless otherwise noted.)$

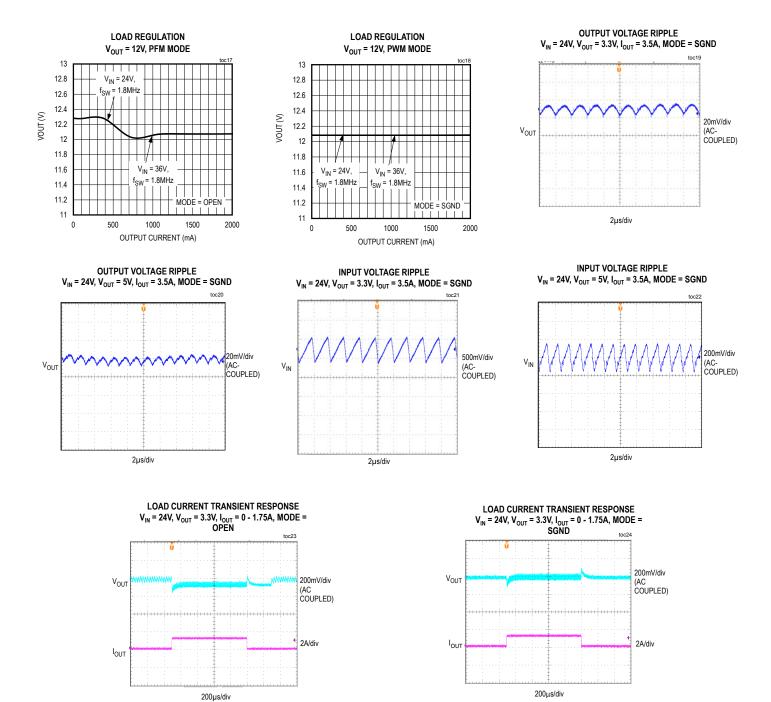

## **Typical Operating Characteristics (continued)**

$(V_{IN} = 4.5V \text{ to } 42V, V_{OUT} = 0.9 \text{ to } 12V, I_{OUT} = 0A-3.5A, T_A = +25^{\circ}C, unless otherwise noted.)$

### **Typical Operating Characteristics (continued)**

$(V_{IN} = 4.5V \text{ to } 42V, V_{OUT} = 0.9 \text{ to } 12V, I_{OUT} = 0A-3.5A, T_A = +25^{\circ}C, unless otherwise noted.)$

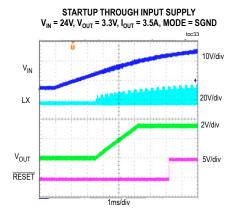

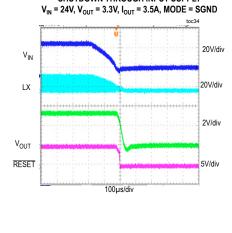

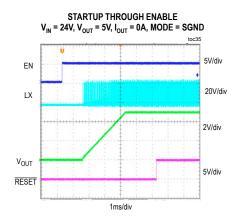

## **Typical Operating Characteristics (continued)**

$(V_{IN} = 4.5V \text{ to } 42V, V_{OUT} = 0.9 \text{ to } 12V, I_{OUT} = 0A-3.5A, T_A = +25^{\circ}C, unless otherwise noted.)$

SHUTDOWN THROUGH INPUT SUPPLY

## **Typical Operating Characteristics (continued)**

$(V_{IN} = 4.5V \text{ to } 42V, V_{OUT} = 0.9 \text{ to } 12V, I_{OUT} = 0A-3.5A, T_A = +25^{\circ}C, unless otherwise noted.)$

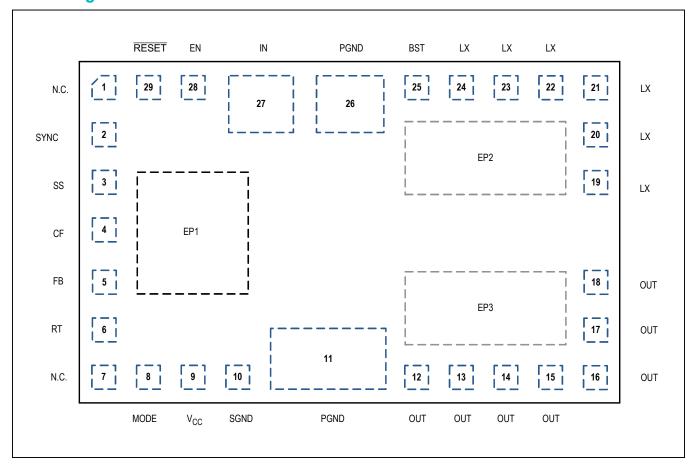

## **Pin Configuration**

# 4.5V to 42V, 3.5A High-Efficiency, DC-DC Step-Down Power Module with Integrated Inductor

# **Pin Description**

| PIN    | NAME            | FUNCTION                                                                                                                                                                                                                                                                                                                                                                               |

|--------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 7   | N.C.            | No Connection                                                                                                                                                                                                                                                                                                                                                                          |

| 2      | SYNC            | Frequency Synchronization. The device can be synchronized to an external clock using this pin. See the <i>External Frequency Synchronization (SYNC)</i> section for more details.                                                                                                                                                                                                      |

| 3      | SS              | Soft-Start Input. Connect a capacitor from SS to SGND to set the soft-start.                                                                                                                                                                                                                                                                                                           |

| 4      | CF              | Compensation Filter. Connect capacitor from CF to FB to correct frequency response in applications using non-ceramic output capacitors with switching frequency below 500kHz. Leave CF open otherwise.                                                                                                                                                                                 |

| 5      | FB              | Feedback Input. Connect FB to the center tap of an external resistor-divider from the OUT to SGND to set the output voltage. See the Setting the Output Voltage section for more details.                                                                                                                                                                                              |

| 6      | RT              | Frequency Set. Connect a resistor from RT to SGND to set the regulator's switching frequency. Leave RT open for the default 500kHz frequency.                                                                                                                                                                                                                                          |

| 8      | MODE            | Light-Load Mode Selection. The MODE pin configures the MAXM17544 to operate in PWM, PFM, or DCM mode of operation. Leave MODE unconnected for PFM operation (pulse-skipping at light-loads). Connect MODE to SGND for constant-frequency PWM operation at all loads. Connect MODE to V <sub>CC</sub> for DCM operation. See the <u>Mode Selection (MODE)</u> section for more details. |

| 9      | V <sub>CC</sub> | 5V LDO Output. No external connection.                                                                                                                                                                                                                                                                                                                                                 |

| 10     | SGND            | Analog Ground. Internally-shorted to PGND. Connect it to PGND through a single point at output capacitor.                                                                                                                                                                                                                                                                              |

| 11, 26 | PGND            | Power Ground. Connect the PGND pins externally to the power ground plane.                                                                                                                                                                                                                                                                                                              |

| 12–18  | OUT             | Regulator Output Pin. Connect a capacitor from OUT to PGND. See <u>PCB Layout Guidelines</u> section for more connection details.                                                                                                                                                                                                                                                      |

| 19–24  | LX              | Internally Connected to EP2. Please do not connect these pins to external components for any reason.                                                                                                                                                                                                                                                                                   |

| 25     | BST             | Boost Flying Cap Node. No external connection.                                                                                                                                                                                                                                                                                                                                         |

| 27     | IN              | Input Supply Connection. Bypass to PGND with a capacitor; place the capacitor close to the IN and PGND pins. See <a href="Table 1">Table 1</a> for more details                                                                                                                                                                                                                        |

| 28     | EN              | Enable/Undervoltage-Lockout Input. Default enable through the pullup $3.3M\Omega$ resistor between EN and IN. Connect a resistor from EN to SGND to set the UVLO threshold.                                                                                                                                                                                                            |

| 29     | RESET           | Open-Drain RESET Output. The RESET output is driven low if FB drops below 92% of its set value. RESET goes high 1024 clock cycles after FB rises above 95% of its set value.                                                                                                                                                                                                           |

| EP1    | SGND            | Analog Ground. Connect this pad to 1in x 1in copper island with a lot of vias for cooling.                                                                                                                                                                                                                                                                                             |

| EP2    | LX              | Switching Node. Connect this pad to a small copper area of 1in x 1in under the device for thermal relief.                                                                                                                                                                                                                                                                              |

| EP3    | OUT             | Connect this pad to the OUT pins and copper area of 1in x 1in.                                                                                                                                                                                                                                                                                                                         |

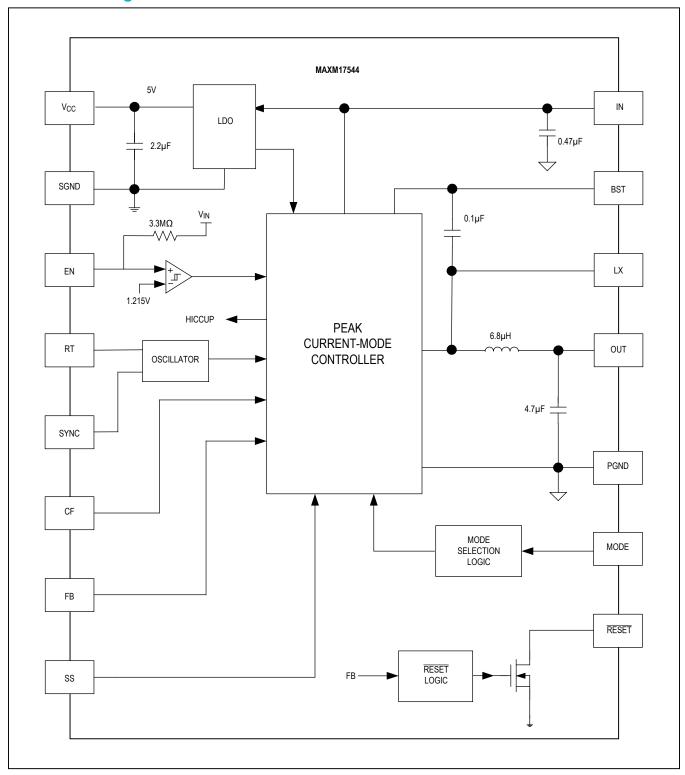

# **Functional Diagram**

### **Design Procedure**

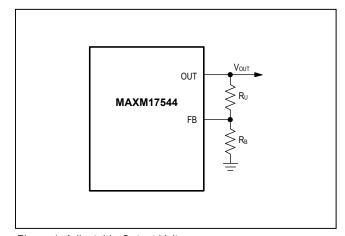

#### **Setting the Output Voltage**

The MAXM17544 supports an adjustable output voltage range of 0.9V to 12V from an input voltage range of 4.5V to 42V by using a resistive feedback divider from OUT to FB. Table 1 provides the feedback dividers for desired input and output voltages. Other adjustable output voltages can be calculated by following the procedure to choose the resistive voltage-divider values.

Calculate resistor R<sub>U</sub> from the output to FB as follows:

$$R_U = \frac{216 \times 1000}{f_C \times C_{OUT}}$$

where  $R_U$  is in  $k\Omega,$  crossover frequency  $f_C$  is in kHz, and output capacitor  $C_{OUT}$  is in  $\mu F.$  Choose  $f_C$  to be 1/9th of the switching frequency ( $f_{SW}$ ) if the switching frequency is less than or equal to 500kHz. If the switching frequency is more than 500kHz, select  $f_C$  to be 55kHz.

$$R_B = \frac{R_U \times 0.9}{V_{OUT} - 0.9} k\Omega \text{, where } R_B \text{ is in } k\Omega.$$

Figure 1. Adjustable Output Voltage

#### **Input Voltage Range**

Due to the limitation of minimum and maximum duty cycle, the maximum value ( $V_{IN\ (MAX)}$ ) and minimum value ( $V_{IN\ (MIN)}$ ) must accommodate the worst-case conditions, accounting for the input voltage rises and drops. To simplify, <u>Table 1</u> provides operating input voltage ranges of different desired output voltages.

#### Input Capacitor Selection

The input capacitor serves to reduce the current peaks drawn from the input power supply and reduces switching noise to the IC. The input capacitor values in <a href="Table 1">Table 1</a> are the minimum recommended values for desired input and output voltages. Applying capacitor values larger than those indicated in <a href="Table 1">Table 1</a> are acceptable to improve the dynamic response. For further operating conditions, the total input capacitance must be greater than or equal to the value given by the following equation in order to keep the input-voltage ripple within specifications and minimize the high-frequency ripple current being fed back to the input source:

$$C_{IN} = \frac{\left(I_{IN}\_AVG\right) \times (1-D)}{\left(\Delta V_{IN}\right) \times f_{SW}}$$

where:

I<sub>IN AVG</sub> is the average input current given by:

$$I_{IN\_AVG} = \frac{P_{OUT}}{\eta \times V_{IN}}$$

D is the operating duty cycle, which is approximately equal to  $V_{\mbox{OUT}}/V_{\mbox{IN}}$ .

$\Delta V_{IN}$  is the required input voltage ripple.

f<sub>SW</sub> is the operating switching frequency.

$P_{OUT}$  is the out power, which is equal to  $V_{OUT} \times I_{OUT}$ .  $\eta$  is the efficiency.

The input capacitor must meet the ripple-current requirement imposed by the switching currents. The RMS input ripple current is given by:

$$I_{RMS} = I_{OUT} \times \sqrt{D \times (1 - D)}$$

The worst-case RMS current requirement occurs when operating with D = 0.5. At this point, the above equation simplifies to  $I_{RMS} = 0.5 \times I_{OUT}$ .

For the MAXM17544 system (IN) supply, ceramic capacitors are preferred due to their resilience to inrush surge currents typical of systems, and due to their low parasitic inductance that helps reduce the high-frequency ringing on the IN supply when the internal MOSFETs are turned off. Choose an input capacitor that exhibits less than +10°C temperature rise at the RMS input current for optimal circuit longevity.

**Table 1. Selection Component Values**

| V <sub>IN</sub> (V) | V <sub>OUT</sub> (V) | C <sub>IN</sub>     | C <sub>OUT</sub>           | R <sub>U</sub> (kΩ) | R <sub>B</sub> (kΩ) | f <sub>SW</sub> (kHz) | R <sub>T</sub> (kΩ) |

|---------------------|----------------------|---------------------|----------------------------|---------------------|---------------------|-----------------------|---------------------|

| 4.5 to 15           | 0.9                  | 3 x 2.2µF 1206 100V | 2 x 100µF 1210 4V          | 35.7                | Open                | 300                   | 68.1                |

| 4.5 to 15           | 1                    | 3 x 2.2µF 1206 100V | 2 x 100µF 1210 4V          | 35.7                | 324                 | 300                   | 68.1                |

| 4.5 to 15           | 1.2                  | 3 x 2.2µF 1206 100V | 1 x 100μF 1 x 47μF 1210 4V | 41.2                | 124                 | 350                   | 57.6                |

| 4.5 to 15           | 1.5                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1 x 47µF 1210 4V | 57.6                | 86.6                | 350                   | 57.6                |

| 4.5 to 15           | 1.8                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1210 4V          | 61.9                | 61.9                | 350                   | 57.6                |

| 4.5 to 15           | 2.5                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1210 4V          | 53.6                | 30.1                | 400                   | 49.9                |

| 4.5 to 15           | 3.3                  | 2 x 2.2µF 1206 100V | 1 x 47µF 1210 10V          | 130                 | 48.7                | 500                   | Open                |

| 6.5 to 15           | 5                    | 2 x 2.2µF 1206 100V | 1 x 22µF 1210 10V          | 191                 | 42.2                | 740                   | 26.7                |

| 11 to 15            | 8                    | 2 x 2.2µF 1206 100V | 1 x 10µF 1210 16V          | 309                 | 39.2                | 1200                  | 15.8                |

| 4.5 to 28           | 0.9                  | 3 x 2.2µF 1206 100V | 3 x 100µF 1210 4V          | 35.7                | Open                | 214                   | 95.3                |

| 4.5 to 28           | 1                    | 3 x 2.2µF 1206 100V | 3 x 100µF 1210 4V          | 35.7                | 324                 | 238                   | 86.6                |

| 4.5 to 28           | 1.2                  | 3 x 2.2µF 1206 100V | 2 x 100µF 1210 4V          | 41.2                | 124                 | 285                   | 71.5                |

| 4.5 to 28           | 1.5                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1 x 47µF 1210 4V | 57.6                | 86.6                | 350                   | 57.6                |

| 4.5 to 28           | 1.8                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1210 4V          | 61.9                | 61.9                | 350                   | 57.6                |

| 4.5 to 28           | 2.5                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1210 4V          | 53.6                | 30.1                | 400                   | 49.9                |

| 4.5 to 28           | 3.3                  | 2 x 2.2µF 1206 100V | 1 x 47µF 1210 10V          | 130                 | 48.7                | 500                   | Open                |

| 6.5 to 28           | 5                    | 2 x 2.2µF 1206 100V | 1 x 22µF 1210 10V          | 191                 | 42.2                | 740                   | 26.7                |

| 11 to 28            | 8                    | 2 x 2.2µF 1206 100V | 1 x 10µF 1210 16V          | 309                 | 39.2                | 1200                  | 15.8                |

| 18.5 to 28          | 12                   | 2 x 2.2µF 1206 100V | 1 x 4.7µF 1210 16V         | 464                 | 37.4                | 1800                  | 10.0                |

| 4.5 to 42           | 1.2                  | 3 x 2.2µF 1206 100V | 2 x 100µF 1 x 47µF 1210 4V | 41.2                | 124                 | 200                   | 100.00              |

| 4.5 to 42           | 1.5                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1 x 47uF 1210 4V | 57.6                | 86.6                | 250                   | 82.5                |

| 4.5 to 42           | 1.8                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1 x 47uF 1210 4V | 61.9                | 61.9                | 300                   | 68.1                |

| 4.5 to 42           | 2.5                  | 3 x 2.2µF 1206 100V | 1 x 100µF 1210 4V          | 53.6                | 30.1                | 400                   | 49.90               |

| 4.5 to 42           | 3.3                  | 2 x 2.2µF 1206 100V | 1 x 47µF 1210 10V          | 130                 | 48.7                | 500                   | Open                |

| 6.5 to 42           | 5                    | 2 x 2.2µF 1206 100V | 1 x 22µF 1210 10V          | 191                 | 42.2                | 740                   | 26.7                |

| 11 to 42            | 8                    | 2 x 2.2µF 1206 100V | 1 x 10µF 1210 16V          | 309                 | 39.2                | 1200                  | 15.8                |

| 18.5 to 42          | 12                   | 2 x 2.2µF 1206 100V | 1 x 4.7μF 1210 16V         | 464                 | 37.4                | 1800                  | 10.00               |

#### **Output Capacitor Selection**

The X7R ceramic output capacitors are preferred due to their stability over temperature in industrial applications. The minimum recommended output capacitor values in <u>Table 1</u> are for desired output voltages to support a dynamic step load of 50% of the maximum output current in the application. For additional adjustable output voltages, the output capacitance value is derived from the following equation:

$$C_{OUT} = \frac{I_{STEP} \times t_{RESPONSE}}{2 \times \Delta V_{OUT}}$$

$$t_{RESPONSE} \approx \frac{0.33}{f_C} + \frac{1}{f_{SW}}$$

where I<sub>STEP</sub> is the step load transient,  $t_{RESPONSE}$  is the response time of the controller,  $\Delta V_{OUT}$  is the allowable output ripple voltage during load transient,  $f_C$  is the target closed-loop crossover frequency, and  $f_{SW}$  is the switching frequency. Select  $f_C$  to be 1/9<sup>th</sup> of  $f_{SW}$  or 55kHz if the  $f_{SW}$  greater than 500kHz.

#### **Loop Compensation**

The MAXM17544 integrates the internal compensation to stabilize the control loop. Only the device requires a combination of output capacitors and feedback resistors to program the closed-loop crossover frequency (f<sub>C</sub>) at 1/9th of switching frequency. Use Table 1 to select component values to compensate with appropriating operating switching frequency. Connect the capacitor from CF to FB to correct frequency response in applications using non-ceramic output capacitors with switching frequency below 500kHz. Place a 2.2pF for switching frequency below 300kHz, and 1.2pF for switching frequency range of 300–400kHz.

### **Setting the Switching Frequency (RT)**

The switching frequency range of 100kHz to 1.8MHz are recommended from <u>Table 1</u> for desired input and output voltages. The switching frequency of MAXM17544 can be programmed by using a single resistor ( $R_{RT}$ ) connected from the RT pin to SGND. The calculation of  $R_{RT}$  resistor is given by the following equation:

$$R_{RT} \approx \frac{21000}{f_{SW}} - 1.7$$

where  $R_{RT}$  is in  $k\Omega$  and  $f_{SW}$  is in kHz. Leaving the RT pin open to operate at the default switching frequency of 500kHz.

#### **Soft-Start Capacitor Selection**

The device implements an adjustable soft-start operation to reduce inrush current during startup. A capacitor ( $C_{SS}$ ) connected from the SS pin to SGND to program the soft-start time. The selected output capacitance ( $C_{SEL}$ ) and the output voltage ( $V_{OUT}$ ) determine the minimum value of  $C_{SS}$ , as shown by the following equation:

$$C_{SS} \ge 28 \text{ x } 10^{-3} \text{ x } C_{SEL} \text{ x } V_{OUT}$$

where  $C_{SS}$  is in nF and  $C_{SEL}$  is in  $\mu$ F.

The value of the soft-start capacitor is calculated from the desired soft-start time as follows:

$$t_{SS} \approx \frac{C_{SS}}{5.55}$$

where  $t_{SS}$  is in ms and  $C_{SS}$  is in nF.

### **Detailed Description**

The MAXM17544 is a complete step-down DC-DC power supply that delivers up to 3.5A output current. The device provides a programmable output voltage to regulate up to 12V through external resistor dividers from an input voltage range of 4.5V to 42V. The recommended input voltage in Table 1 is selected highly enough to support the desired output voltage and load current. The device includes an adjustable frequency feature range from 100kHz to 1.8MHz to reduce sizes of input and output capacitors. The *Functional Diagram* shows a complete internal block diagram of the MAXM17544 power module.

#### Input Undervoltage-Lockout Level

The MAXM17544 contains an internal pullup resistor  $(3.3M\Omega)$  from EN to IN to have a default startup voltage. The device offers an adjustable input undervoltage-lockout level to set the voltage at which the device is turned on by a single resistor connecting from EN/UVLO to SGND as equation:

$$R_{ENU} \approx \frac{3.3 \times 1215}{(V_{INU} - 1.215)}$$

where  $R_{ENU}$  is in  $k\Omega$  and  $V_{INU}$  is the voltage at which the device is required to turn on the device. Ensure that  $V_{INU}$  is high enough to support the  $V_{OUT}$ . See <u>Table 1</u> to set the proper  $V_{INU}$  voltage greater than or equal the minimum input voltage for each desired output voltage.

#### Mode Selection (MODE)

The MAXM17544 features a MODE pin to configure the device operating in PWM, PFM, or DCM control schemes. The device operates in PFM mode at light loads if the MODE pin is open. If the MODE pin connects to ground, the device operates in constant-frequency PWM mode at all loads. The device operates in constant-frequency DCM mode at light loads when the MODE pin connects to  $V_{CC}$ . State changes of the MODE operation are only at power-up and ignore during normal operation.

#### **PWM Mode Operation**

In PWM mode, the step-down controller is switching a constant-frequency at all loads with a minimum sink current limit threshold (-1.8A typ) at light load. The PWM mode of operation gives lower efficiency at light loads compared to PFM and DCM modes of operation. However, the PWM mode of operation is useful in applications sensitive to switching frequency.

#### **PFM Mode Operation**

In PFM mode, the controller forces the peak inductor current in order to feed the light loads and maintain high efficiency. If the load is lighter than the average PFM value, the output voltage will exceed 102.3% of the feedback threshold and the controller enters into a hibernation mode, turning off most of the internal blocks. The device exits hibernation mode and starts switching again once the output voltage is discharged to 101.1% of the feedback threshold. The device then begins the process of delivering pulses of energy to the output repeatedly until it reaches 102.3% of the feedback threshold. In this mode, the behavior resembles PWM operation (with occasional pulse skipping), where the inductor current does not need to reach the light-load level.

PFM mode offers the advantage of increased efficiency at light loads due to a lower quiescent current drawn from the supply. However, the output-voltage ripple is also increased as compared to the PWM or DCM modes of operation, and the switching frequency is not constant at light loads.

#### **DCM Mode Operation**

DCM mode features constant frequency operation down to lighter loads than PFM mode, accomplished by not skipping pulses. DCM efficiency performance lies between the PWM and PFM modes.

### **External Frequency Synchronization (SYNC)**

The device can be synchronized by an external clock signal on the SYNC pin. The external synchronization clock frequency must be between 1.1 x  $f_{SW}$  and 1.4 x  $f_{SW}$ , where  $f_{SW}$  is the frequency programmed by the RT

resistor. The minimum external clock high pulse width and amplitude should be greater than 50ns and 2.1V, respectively. The minimum external clock low pulse width should be greater than 160ns, and the maximum external clock low pulse amplitude should be less than 0.8V. Table 1 provides recommended synchronous frequency ranges for desired output voltages. Connect the SYNC pin to SGND if it is not used.

#### **RESET Output**

The device includes a  $\overline{RESET}$  comparator to monitor the output for undervoltage and overvoltage conditions. The open-drain  $\overline{RESET}$  output requires an external pullup resistor from  $10k\Omega$  to  $100k\Omega$  to  $V_{CC}$  pin or maximum 6V voltage source.  $\overline{RESET}$  goes high impedance after the regulator output increases above 95% of the designed nominal regulated voltage.  $\overline{RESET}$  goes low when the regulator output voltage drops below 92% of the nominal regulated voltage.  $\overline{RESET}$  also goes low during thermal shutdown.

#### **Thermal Fault Protection**

The MAXM17544 features a thermal-fault protection circuit. When the junction temperature rises above +165°C (typ), a thermal sensor activates the fault latch, pulls down the RESET output, and shuts down the regulator. The thermal sensor restarts the controllers after the junction temperature cools by 10°C (typ). The soft-start resets during thermal shutdown.

#### **Power Dissipation and Output-Current Derating**

The MAXM17544 output current needs to be derated if the device needs to be operated in a high ambient-temperature environment. The amount of current-derating depends upon the input voltage, output voltage, and ambient temperature. The derating curves in TOC43 from the *Typical Operating Characteristics* section can be used as guidelines. The curves are based on simulating thermal resistance model ( $\Psi_{JT}$ ), measuring thermal resistance ( $\Psi_{TA}$ ), and measuring power dissipation ( $P_{DMAX}$ ) on the bench.

The maximum allowable power losses can be calculated using the following equation:

$$P_{DMAX} = \frac{T_{JMAX} - T_{A}}{\theta_{JA}}$$

where:

P<sub>DMAX</sub> is the maximum allowed power losses with maximum allowed junction temperature.

T<sub>JMAX</sub> is the maximum allowed junction temperature.

T<sub>A</sub> is operating ambient temperature.

$\theta_{\text{JA}}$  is the junction to ambient thermal resistance.

## 4.5V to 42V, 3.5A High-Efficiency, DC-DC Step-Down Power Module with Integrated Inductor

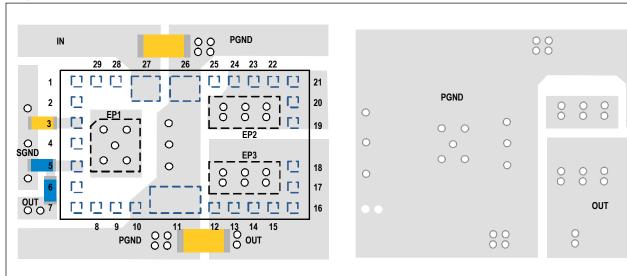

#### **PCB Layout Guidelines**

Careful PCB layout is critical to achieving low switching losses and clean, stable operation.

Use the following guidelines for good PCB layout:

- Keep the input capacitors as close as possible to the IN and PGND pins.

- Keep the output capacitors as close as possible to the OUT and PGND pins.

- Keep the resistive feedback dividers as close as possible to the FB pin.

- Connect all of the PGND connections to as large as copper plane area as possible on the top layer.

- Connect EP1 to PGND and GND planes on bottom layer.

- Use multiple vias to connect internal PGND planes to the top-layer PGND plane.

- Do not keep any solder mask on EP1, EP2, and EP3 on bottom layer. Keeping solder mask on exposed pads decreases the heat-dissipating capability.

- Keep the power traces and load connections short. This practice is essential for high efficiency. Using thick copper PCBs (2oz vs. 1oz) can enhance full-load efficiency. Correctly routing PCB traces is a difficult task that must be approached in terms of fractions of centimeters, where a single  $m\Omega$  of excess trace resistance causes a measurable efficiency penalty.

### **Layout Recommendation**

# 4.5V to 42V, 3.5A High-Efficiency, DC-DC Step-Down Power Module with Integrated Inductor

## **Chip Information**

PROCESS: BICMOS

### **Ordering Information**

| PART           | TEMP RANGE      | PIN-<br>PACKAGE |

|----------------|-----------------|-----------------|

| MAXM17544ALJ+T | -40°C to +125°C | 29 SiP          |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="https://www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE | PACKAGE  | OUTLINE | LAND        |

|---------|----------|---------|-------------|

| TYPE    | CODE     | NO.     | PATTERN NO. |

| 29 SiP  | L32915+1 | 21-0879 | 90-0459     |

T = Tape and reel.

# 4.5V to 42V, 3.5A High-Efficiency, DC-DC Step-Down Power Module with Integrated Inductor

## **Revision History**

| REVISION | REVISION | DESCRIPTION     | PAGES   |

|----------|----------|-----------------|---------|

| NUMBER   | DATE     |                 | CHANGED |

| 0        | 12/14    | Initial release | _       |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.