SLAS356 - DECEMBER 2001

## **PCM CODEC**

#### **FEATURES**

- 2.7-V Operation

- Two Differential Microphone Inputs, One Differential Earphone Output, and One Single-Ended Earphone Output

- Programmable Gain Amplifiers for Transmit, Receive, Sidetone, and Volume Control

- Earphone Mute and Microphone Mute

- On-Chip I<sup>2</sup>C Bus, Which Provides a Simple, Standard, Two-Wire Serial Interface With Digital ICs

- Programmable for 15-Bit Linear Data or 8-Bit Companded (μ-Law or A-Law) Data

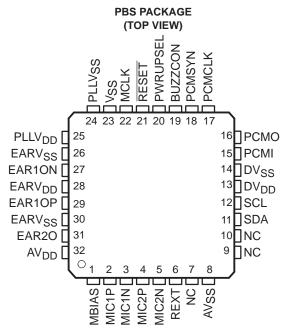

- Available in a 32-Pin Thin Quad Flatpack (TQFP) Package and an 80-Pin GQE MicroStar Junior™ Ball Grid Array (BGA)

- Designed for Analog and Digital Wireless Handsets and Telecommunications Applications

- Dual-Tone Multifrequency (DTMF) and Single Tone Generator

- Pulse Density Modulated (PDM) Buzzer Output

#### **APPLICATIONS**

- Digital Handset

- Digital Headset

- Cordless Phones

- Digital PABX

- Digital Voice Recording

## **DESCRIPTION**

The PCM codec is designed to perform transmit encoding analog/digital (A/D) conversion, receive decoding digital/analog (D/A) conversion, and transmit and receive filtering for voice-band communications systems. The device operates in either the 15-bit linear or 8-bit companded ( $\mu$ -law or A-Law) mode, which is selectable through the I²C interface. The PCM codec generates its own internal clocks from a 2.048-MHz master clock input.

NC - No internal connection

This device contains circuits to protect its inputs and outputs against damage due to high static voltages or electrostatic fields. These circuits have been qualified to protect this device against electrostatic discharges (ESD) of up to 2 kV according to MIL-STD-883C, Method 3015; however, it is advised that precautions be taken to avoid application of any voltage higher than maximum-rated voltages to these high-impedance circuits. During storage or handling, the device leads should be shorted together or the device should be placed in conductive foam. In a circuit, unused inputs should always be connected to an appropriated logic voltage level, preferably either V<sub>CC</sub> or ground. Specific guidelines for handling devices of this type are contained in the publication *Guidelines for Handling Electrostatic-Discharge-Sensitive (ESDS) Devices and Assemblies* available from Texas Instruments.

MicroStar Junior is a trademark of Texas Instruments.

All other trademarks are the property of their respective owners.

# MicroStar Junior™ (GQE) PACKAGE (TOP VIEW)

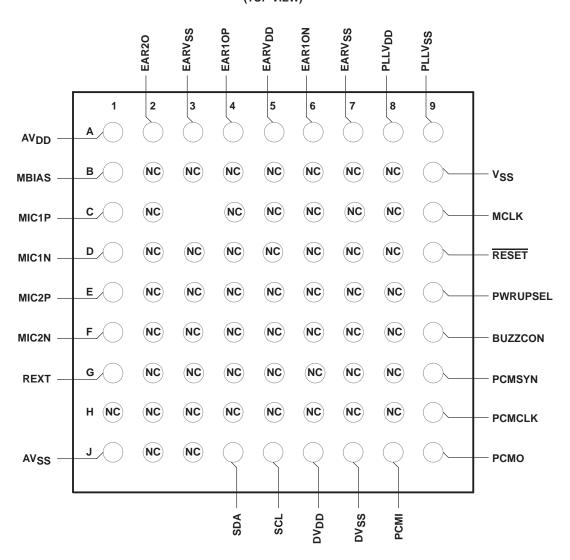

## functional block diagram

SLAS356 - DECEMBER 2001

## functional description

#### power on/reset

The power for the various digital and analog circuits is separated to improve the noise performance of the device. An external reset must be applied to the active low RESET terminal to assure reset upon power on. After the initial power-on sequence the TLV320AlC1103 can be functionally powered up and down by writing to the power control register through the I<sup>2</sup>C interface. There is a hardwired selectable power-up terminal in default mode option. The PWRUPSEL function allows the VBAP to power up in the default mode and allows use without a microcontroller.

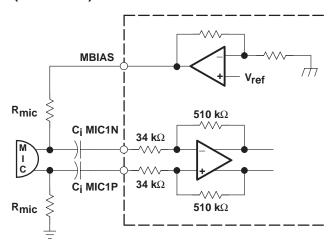

#### reference

A precision band gap reference voltage is generated internally and supplies all required voltage references to operate the transmit and receive channels. The reference system also supplies bias voltage for use with an electret microphone at terminal MBIAS. An external precision resistor is required for reference current setting at terminal REXT.

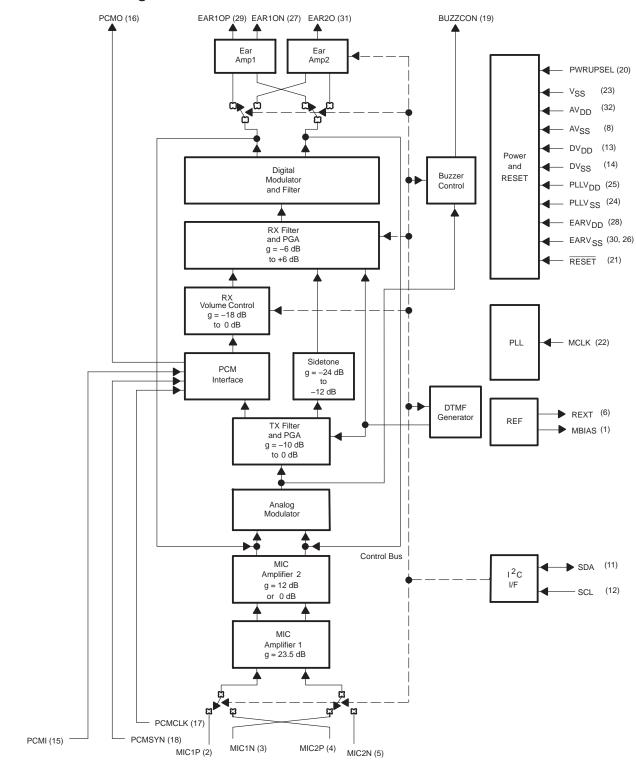

#### control interface

The I<sup>2</sup>C interface is a two-wire bidirectional serial interface that controls the PCM codec by writing data to the six control registers:

- Power control

- Mode control

- Transmit PGA and sidetone control

- Receive PGA gain and volume control

- DTMF high tone

- DTMF low tone

There are two power-up modes which may be selected at the PWRUPSEL terminal:

- The PWRUPSEL state (V<sub>DD</sub> at terminal 20) causes the device to power up in the default mode when power

is applied. In the default mode, the I<sup>2</sup>C interface is not required, and the device may be used without an I<sup>2</sup>C

interface. The programmable functions are fixed in the default modes.

- The PWRUPSEL state (ground at terminal 20) causes the device to go to a power-down state when power is applied. In this mode an I<sup>2</sup>C interface is required to power up the device.

#### phase-locked loop

The internal digital filters and modulators require a 10.24-MHz clock that is generated by phase locking to the 2.048-MHz master clock input.

#### **PCM** interface

The PCM interface transmits and receives data at the PCMO and PCMI terminals respectively. The data is transmitted or received at the PCMCLK speed once every PCMSYN cycle. The PCMCLK can be tied directly to the 2.048-MHz master clock (MCLK). The PCMSYN can be driven by an external source or derived from the master clock and used as an interrupt to the host controller.

## microphone amplifiers

The microphone input is a switchable interface for two differential microphone inputs. The first stage is a lownoise differential amplifier that provides a gain of 23.5 dB. The second stage amplifier has a selectable gain of 0 dB or 12 dB.

## functional description (continued)

#### analog modulator

The transmit channel modulator is a third-order sigma-delta design.

#### transmit filter and PGA

The transmit filter is a digital filter designed to meet CCITT G.714 requirements. The device operates in either the 15-bit linear or 8-bit companded  $\mu$ -law or A-law mode that is selectable through the I<sup>2</sup>C interface. The transmit PGA defaults to 0 dB.

#### sidetone

A portion of the transmitted audio is attenuated and fed back to the receive channel through the sidetone path. The sidetone path defaults to –12 dB. The sidetone path can be enabled by writing to the power control register.

#### receive volume control

The receive volume control block acts as an attenuator with a range of –18 dB to 0 dB in 2 dB steps for control of the receive channel volume. The receive volume control gain defaults to 0 dB.

#### receive filter and PGA

The receive filter is a digital filter that meets CCITT G.714 requirements with a high-pass filter that is selectable through the I<sup>2</sup>C interface. The device operates in either the 15-bit linear or 8-bit  $\mu$ -law or A-law companded mode, which is selectable through the I<sup>2</sup>C interface. The gain defaults to –1 dB representing a 3-dBm0 level for a 32- $\Omega$  load impedance and the corresponding digital full scale PCMI code. The gain may be set to –2 dB for the respective 3-dBm0 level for a 16- $\Omega$  load impedance.

#### digital modulator and filter

The second-order digital modulator and filter convert the received digital PCM data to the analog output required by the earphone interface.

## earphone amplifiers

The analog signal can be routed to either of two earphone amplifiers, one with differential output (EAR1ON and EAR1OP) and one with single-ended output (EAR2O). Clicks and pops are suppressed for EAR1 differential output only.

#### tone generator

The tone generator provides generation of standard DTMF tones and single tone frequencies which are output to the following devices: 1) the buzzer driver, as a pulse density modulation (PDM) signal, and 2) the receive path digital/analog converter (DAC) for outputting through the earphone. There are 255 possible single tones. The tone integer value is determined by the following formula:

Round (Tone Freq (Hz)/7.8135 Hz)

The value is loaded into one of two 8-bit registers, the high-tone register (04), or the low-tone register (05). The tone output is 2 dB higher when applied to the high-tone register (04). When generating DTMF tones, the high DTMF tone must be applied to the high-tone register and the low frequency tone to the low-tone register.

## **Terminal Functions**

| TERMINAL           |              |        |     |                                                                                                                                                                                                                                                                                     |

|--------------------|--------------|--------|-----|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                    | N            | 0.     | 1/0 | DESCRIPTION                                                                                                                                                                                                                                                                         |

| NAME               | μ <b>BGA</b> | PBS    |     |                                                                                                                                                                                                                                                                                     |

| AV <sub>DD</sub>   | A1           | 32     | I   | Analog positive power supply                                                                                                                                                                                                                                                        |

| AVSS               | J1           | 8      | I   | Analog negative power supply                                                                                                                                                                                                                                                        |

| BUZZCON            | F9           | 19     | 0   | Buzzer output, a pulse-density modulated signal to apply to external buzzer driver                                                                                                                                                                                                  |

| $DV_{DD}$          | J6           | 13     | - 1 | Digital positive power supply                                                                                                                                                                                                                                                       |

| DVSS               | J7           | 14     | I   | Digital negative power supply                                                                                                                                                                                                                                                       |

| EAR10N             | A6           | 27     | 0   | Earphone 1 amplifier output (–)                                                                                                                                                                                                                                                     |

| EAR10P             | A4           | 29     | 0   | Earphone 1 amplifier output (+)                                                                                                                                                                                                                                                     |

| EAR2O              | A2           | 31     | 0   | Earphone 2 amplifier output                                                                                                                                                                                                                                                         |

| EARV <sub>DD</sub> | A5           | 28     | - 1 | Analog positive power supply for the earphone amplifiers                                                                                                                                                                                                                            |

| EARVSS             | A3, A7       | 30, 26 | - 1 | Analog negative power supply for the earphone amplifiers                                                                                                                                                                                                                            |

| MBIAS              | B1           | 1      | 0   | Microphone bias supply output, no decoupling capacitors                                                                                                                                                                                                                             |

| MCLK               | C9           | 22     | I   | Master system clock input (2.048 MHz) (digital)                                                                                                                                                                                                                                     |

| MIC1P              | C1           | 2      | - 1 | MIC1 input (+)                                                                                                                                                                                                                                                                      |

| MIC1N              | D1           | 3      | I   | MIC1 input (–)                                                                                                                                                                                                                                                                      |

| MIC2P              | E1           | 4      | I   | MIC2 input (+)                                                                                                                                                                                                                                                                      |

| MIC2N              | F1           | 5      | I   | MIC2 input (–)                                                                                                                                                                                                                                                                      |

| PCMI               | J8           | 15     | - 1 | Receive PCM input                                                                                                                                                                                                                                                                   |

| PCMO               | J9           | 16     | 0   | Transmit PCM output                                                                                                                                                                                                                                                                 |

| PCMSYN             | G9           | 18     | - 1 | PCM frame synchronization                                                                                                                                                                                                                                                           |

| PCMCLK             | H9           | 17     | I   | PCM data clock                                                                                                                                                                                                                                                                      |

| PLLVSS             | A9           | 24     | I   | PLL negative power supply                                                                                                                                                                                                                                                           |

| PLLV <sub>DD</sub> | A8           | 25     | I   | PLL digital power supply                                                                                                                                                                                                                                                            |

| PWRUPSEL           | E9           | 20     | I   | Selects the power-up default mode                                                                                                                                                                                                                                                   |

| REXT               | G1           | 6      | I/O | Internal reference current setting terminal—use precision 100-kΩ resistor and no filtering capacitors                                                                                                                                                                               |

| RESET              | D9           | 21     | I   | Active low reset                                                                                                                                                                                                                                                                    |

| SCL                | J5           | 12     | I   | I <sup>2</sup> C-bus serial clock—this input is used to synchronize the data transfer from and to the PCM codec                                                                                                                                                                     |

| SDA                | J4           | 11     | I/O | $I^2$ C-bus serial address/data input/output—this is a bidirectional terminal used to transfer register control addresses and data into and out of the CODEC. It is an open-drain terminal and therefore requires a pullup resistor to $V_{DD}$ (typical 10 k $\Omega$ for 100 kHz) |

| V <sub>SS</sub>    | В9           | 23     | I   | Ground return for bandgap internal reference                                                                                                                                                                                                                                        |

## absolute maximum ratings over operating free-air temperature range (unless otherwise noted)†

| Supply voltage range, AV <sub>DD</sub> , DV <sub>DD</sub> , PLLV <sub>DD</sub> , EARV <sub>DD</sub> |                 | -0.5 V to 4 | 4 V |

|-----------------------------------------------------------------------------------------------------|-----------------|-------------|-----|

| Output voltage range, VO                                                                            |                 | –0.5 V to 4 | 4 V |

| Input voltage range, V <sub>F</sub>                                                                 |                 | –0.5 V to 4 | 4 V |

| Continuous total power dissipation                                                                  | See Dissipation | Rating Tal  | ble |

| Operating free air temperature range, T <sub>A</sub> (industrial temperature)                       |                 | 40°C to 85  | ί°С |

| Storage temperature range, testing, T <sub>stg</sub>                                                | 6               | 5°C to 150  | )°C |

| Lead temperature 1,6 mm from case for 10 seconds                                                    |                 | 260         | )°C |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

#### **DISSIPATION RATING TABLE**

| PACKAGE | $T_{\mbox{\scriptsize A}} \le 25^{\circ}\mbox{\scriptsize C}$ POWER RATING | DERATING FACTOR<br>ABOVE T <sub>A</sub> = 25°C | T <sub>A</sub> = 85°C<br>POWER RATING |

|---------|----------------------------------------------------------------------------|------------------------------------------------|---------------------------------------|

| PBS     | 680 mW                                                                     | 6.8 mW/°C                                      | 270 mW                                |

## recommended operating conditions (see Notes 1 and 2)

|                                                                                               | MIN                   | NOM | MAX                   | UNIT |

|-----------------------------------------------------------------------------------------------|-----------------------|-----|-----------------------|------|

| Supply voltage, AV <sub>DD</sub> , DV <sub>DD</sub> , PLLV <sub>DD</sub> , EARV <sub>DD</sub> | 2.7                   |     | 3.3                   | V    |

| High-level input voltage, V <sub>IH</sub>                                                     | 0.7 x V <sub>DD</sub> |     |                       | V    |

| Low-level input voltage, (V <sub>IL</sub>                                                     |                       |     | 0.3 x V <sub>DD</sub> | V    |

| Load impedance between EAR1OP and EAR1ON-RL                                                   | 16                    |     | 32                    | Ω    |

| Load impedance for EAR2OP-RL                                                                  |                       | 32  |                       | Ω    |

| Operating free-air temperature, TA                                                            | -40                   |     | 85                    | °C   |

NOTES: 1. To avoid possible damage and resulting reliability problems to these CMOS devices, the *power-on initialization* paragraph should be followed, which is described in the *Principles of Operations*.

<sup>2.</sup> Voltages are with respect to AVSS, DVSS, PLLVSS, and EARVSS.

# electrical characteristics, $V_{DD}$ = 2.7 V, $T_A$ = 25°C (unless otherwise noted)

## supply current

| PARAMETER          |                                            | TEST CONDITIONS                                            | MIN | TYP | MAX | UNIT |

|--------------------|--------------------------------------------|------------------------------------------------------------|-----|-----|-----|------|

|                    |                                            | Operating, EAR1 selected, MicBias disabled                 |     | 6   | 7   | mA   |

|                    | Operating, EAR2 selected, MicBias disabled |                                                            | 5.4 | 6   | mA  |      |

| IDD                | Supply current from V <sub>DD</sub>        | Power down, Reg 2 bit 7 = 1, MCLK not present (see Note 3) |     | 0.5 | 10  | μΑ   |

|                    |                                            | Power down, Reg 2 bit 7 = 0, MCLK not present (see Note 3) |     | 25  | 40  | μΑ   |

| t <sub>on(i)</sub> | Power-up time from power down              |                                                            |     | 5   | 10  | ms   |

NOTE 3: VIH = VDD, VIL = VSS

## digital interface

|                  | PARAMETER                                   | TEST CONE                   | DITIONS               | MIN       | TYP | MAX | UNIT |

|------------------|---------------------------------------------|-----------------------------|-----------------------|-----------|-----|-----|------|

| Vон              | High-level output voltage, PCMO and BUZZCON | $I_{OH} = -3.2 \text{ mA},$ | V <sub>DD</sub> = 3 V | $DV_{DD}$ |     |     | V    |

| VOL              | Low-level output voltage, PCMO and BUZZCON  | I <sub>OL</sub> = 3.2 mA,   | V <sub>DD</sub> = 3 V |           |     | 0   | V    |

| ΙΗ               | High-level input current, any digital input | $V_I = V_{DD}$              |                       |           |     | 10  | μΑ   |

| I <sub>Ι</sub> L | Low-level input current, any digital input  | $V_I = V_{SS}$              |                       |           |     | 10  | μΑ   |

| Cl               | Input capacitance                           |                             |                       |           |     | 10  | pF   |

| Co               | Output capacitance                          |                             |                       |           |     | 20  | pF   |

| RL               | Load impedance (BuzzCon)                    |                             |                       |           |     | 5   | kΩ   |

## microphone interface

|                      | PARAMETER                                                                              | TEST CONDITIONS                                 | MIN  | TYP | MAX  | UNIT              |

|----------------------|----------------------------------------------------------------------------------------|-------------------------------------------------|------|-----|------|-------------------|

| VIO                  | Input offset voltage at MIC1N, MIC2N                                                   | See Note 4                                      | -5   |     | 5    | mV                |

| I <sub>IB</sub>      | Input bias current at MIC1N, MIC2N                                                     |                                                 | -200 |     | 200  | nA                |

| Ci                   | Input capacitance at MIC1N, MIC2N                                                      |                                                 |      | 5   |      | pF                |

| Vn                   | Microphone input referred noise, psophometric weighted (C-message weighted is similar) | Micamp 1 gain = 23.5 dB<br>Micamp 2 gain = 0 dB |      | 3   | 7.7  | μV <sub>rms</sub> |

| I <sub>O</sub> max   | Output source current MBIAS                                                            |                                                 | 1    |     | 1.2  | mA                |

| V <sub>(mbias)</sub> | Microphone bias supply voltage (see Note 5)                                            |                                                 | 2.4  | 2.5 | 2.55 | V                 |

|                      | MICMUTE                                                                                |                                                 | -80  |     |      | dB                |

|                      | Input impedance                                                                        | Fully differential                              | 35   | 60  | 100  | kΩ                |

NOTES: 4. Measured while MIC1P and MIC1N are connected together. Less than 5-mV offset results in 0 value code on PCMOUT.

5. Not a JEDEC symbol.

## speaker interface

|       | PARAMETER                               | TEST CONDITIONS                                                               | MIN | TYP   | MAX   | UNIT |

|-------|-----------------------------------------|-------------------------------------------------------------------------------|-----|-------|-------|------|

|       |                                         | $V_{DD}$ = 2.7 V, fully differential, 16-Ω load, 3-dBm0 output, RGXPA = -2 dB |     | 120.9 | 151.1 | mW   |

|       | Earphone AMP1 output power (See Note 6) | $V_{DD}$ = 2.7 V, fully differential, 32-Ω load, 3-dBm0 output, RGXPA = -1 dB |     | 76.1  | 95.1  | mW   |

|       | Earphone AMP2 output power (See Note 6) | $V_{DD}$ = 2.7 V, single ended, 32-Ω load, 3-dBm0 output                      |     | 10    | 12.5  | mW   |

| Voo   | Output offset voltage at EAR1           | Fully differential                                                            |     | ±5    | ±30   | mV   |

|       |                                         | 3-dBm0 input, 16-Ω load                                                       |     | 86.9  | 108.6 |      |

| Iomax | Maximum output current for EAR1(rms)    | 3-dBm0 input, 32-Ω load                                                       |     | 48.7  | 60.8  | mA   |

|       | Maximum output current for EAR2 (rms)   | 3-dBm0 input                                                                  |     | 17.7  | 22.1  |      |

|       | EARMUTE                                 |                                                                               | -80 |       |       | dB   |

NOTE 6: Maximum power is with a load impedance of approximately 12  $\Omega$ .

## electrical characteristics, V<sub>DD</sub> = 2.7 V, T<sub>A</sub> = 25°C (unless otherwise noted) (continued)

# transmit gain and dynamic range, companded mode (μ-law or A-law) or linear mode selected, transmit slope filter bypassed (see Notes 7 and 8)

| PARAMETER                                                                        | TEST CONDITIONS                                        | MIN  | TYP | MAX | UNIT      |

|----------------------------------------------------------------------------------|--------------------------------------------------------|------|-----|-----|-----------|

| Transmit reference-signal level (0 dB)                                           | Differential                                           |      |     | 175 | $mV_{pp}$ |

| Overload-signal level (3 dBm0)                                                   | Differential, normal mode                              |      |     | 248 | \/        |

|                                                                                  | Differential, extended mode                            |      |     | 63  | $mV_{pp}$ |

| Absolute gain error                                                              | 0-dBm0 input signal, V <sub>DD</sub> = 2.7 V (minimum) | -1   |     | 1   | dB        |

|                                                                                  | MIC1N, MIC1P to PCMO at 3 dBm0 to -30 dBm0             | -0.5 |     | 0.5 |           |

| Gain error with input level relative to gain at<br>-10 dBm0 MIC1N, MIC1P to PCMO | MIC1N, MIC1P to PCMO at -31 dBm0 to -45 dBm0           | -1   |     | 1   | dB        |

| - 10 dBillo lillo 114, lillo 11 to 1 olivo                                       | MIC1N, MIC1P to PCMO at -46 dBm0 to -55 dBm0           | -1.2 |     | 1.2 |           |

NOTES: 7. Unless otherwise noted, the analog input is 0 dB, 1020-Hz sine wave, where 0 dB is defined as the zero-reference point of the channel under test.

8. The reference signal level, which is input to the transmit channel, is defined as a value 3 dB below the full-scale value of 88-mV<sub>rms</sub>.

# transmit gain and dynamic range, companded mode ( $\mu$ -law or A-law) or linear mode selected, transmit slope filter enabled (see Notes 7 and 8)

| PARAMETER                                                                        | TEST CONDITIONS                                        | MIN  | TYP | MAX | UNIT             |

|----------------------------------------------------------------------------------|--------------------------------------------------------|------|-----|-----|------------------|

| Transmit reference-signal level (0dB)                                            | Differential                                           |      |     | 175 | $mV_{pp}$        |

| Overload-signal level (3 dBm0)                                                   | Differential, normal mode                              |      |     | 248 | >/               |

|                                                                                  | Differential, extended mode                            |      |     | 63  | mV <sub>pp</sub> |

| Absolute gain error                                                              | 0-dBm0 input signal, V <sub>DD</sub> = 2.7 V (minimum) | -1   |     | 1   | dB               |

|                                                                                  | MIC1N, MIC1P to PCMO at 3 dBm0 to -30 dBm0             | -0.5 |     | 0.5 |                  |

| Gain error with input level relative to gain at<br>-10-dBm0 MIC1N, MIC1P to PCMO | MIC1N, MIC1P to PCMO at -31 dBm0 to -45 dBm0           | -1   |     | 1   | dB               |

| To abino Mio 114, Mio II to I owo                                                | MIC1N, MIC1P to PCMO at -46 dBm0 to -55 dBm0           | -1.2 |     | 1.2 |                  |

NOTES: 7. Unless otherwise noted, the analog input is 0 dB, 1020-Hz sine wave, where 0 dB is defined as the zero-reference point of the channel under test.

8. The reference signal level, which is input to the transmit channel, is defined as a value 3 dB below the full-scale value of 88-mV<sub>rms</sub>.

# transmit filter transfer, companded mode ( $\mu$ -law or A-law) or linear mode selected, transmit slope filter bypassed, external high pass filter bypassed (MCLK = 2.048 MHz)

| PARAMETER                                                                         | TEST CONDITIONS                                          | MIN  | TYP N | /IAX | UNIT |

|-----------------------------------------------------------------------------------|----------------------------------------------------------|------|-------|------|------|

|                                                                                   | fMIC1 or fMIC2 <100 Hz                                   | -0.5 |       | 0.5  |      |

|                                                                                   | fMIC1 or fMIC2 = 200 Hz                                  | -0.5 |       | 0.5  |      |

|                                                                                   | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 300 Hz to 3 kHz | -0.5 |       | 0.5  |      |

| Gain relative to input signal gain at 1020 Hz, internal high-pass filter disabled | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 3.4 kHz         | -1.5 |       | 0    | dB   |

|                                                                                   | fMIC1 or fMIC2 = 4 kHz                                   |      |       | -14  |      |

|                                                                                   | fMIC1 or fMIC2 = 4.6 kHz                                 |      |       | -35  |      |

|                                                                                   | fMIC1 or fMIC2 = 8 k Hz                                  |      |       | -47  |      |

| Gain relative to input signal gain at 1020 Hz, internal high-pass                 | fMIC1 or fMIC2 <100 Hz                                   |      |       | -15  | ٩D   |

| filter enabled                                                                    | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 200 Hz          |      |       | -5   | dB   |

## electrical characteristics, $V_{DD}$ = 2.7 V, $T_A$ = 25°C (unless otherwise noted) (continued)

transmit filter transfer, companded mode ( $\mu$ -law or A-law) or linear mode selected, transmit slope filter selected (MCLK = 2.048 MHz) (see Note 9)

| PARAMETER                                                                   | TEST CONDITIONS                                  | MIN | TYP   | MAX | UNIT |

|-----------------------------------------------------------------------------|--------------------------------------------------|-----|-------|-----|------|

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> =100 Hz   |     |       | -27 | dB   |

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 200 Hz  |     |       | -8  | dB   |

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 250 Hz  |     |       | -4  | dB   |

|                                                                             | fMIC1 or fMIC2 = 300 Hz                          |     | -1.80 |     | dB   |

|                                                                             | fMIC1 or fMIC2 = 400 Hz                          |     | -1.50 |     | dB   |

|                                                                             | fMIC1 or fMIC2 = 500 Hz                          |     | -1.30 |     | dB   |

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 600 Hz  |     | -1.1  |     | dB   |

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 700 Hz  |     | -0.8  |     | dB   |

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 800 Hz  |     | -0.57 |     | dB   |

|                                                                             | fMIC1 or fMIC2 = 900 Hz                          |     | -0.25 |     | dB   |

| Gain relative to input signal gain at 1000 Hz, with slope filter selected   | fMIC1 or fMIC2 = 1000 Hz                         |     | 0     |     | dB   |

| Gairrielative to iriput signal gairrat 1000 riz, with slope litter selected | fMIC1 or fMIC2 = 1500 Hz                         |     | 1.8   |     | dB   |

|                                                                             | fMIC1 or fMIC2 = 2000 Hz                         |     | 4.0   |     | dB   |

|                                                                             | fMIC1 or fMIC2 = 2500 Hz                         |     | 6.5   |     | dB   |

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 3000 Hz |     | 7.6   |     | dB   |

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 3100 Hz |     | 7.7   |     | dB   |

|                                                                             | fMIC1 or fMIC2 = 3300 Hz                         |     | 8.0   |     | dB   |

|                                                                             | fMIC1 or fMIC2 = 3500 Hz                         |     | 6.48  |     | dB   |

|                                                                             | fMIC1 or fMIC2 = 4000 Hz                         |     |       | -13 | dB   |

|                                                                             | fMIC1 or fMIC2 = 4500 Hz                         |     |       | -35 | dB   |

|                                                                             | fMIC1 or fMIC2 = 5000 Hz                         |     |       | -45 | dB   |

|                                                                             | f <sub>MIC1</sub> or f <sub>MIC2</sub> = 8000 Hz |     |       | -50 | dB   |

NOTE 9: The pass-band tolerance is  $\pm$  0.25 dB from 300 Hz to 3500 Hz.

## transmit idle channel noise and distortion, companded mode (µ-law or A-law) selected, slope filter bypassed

| PARAMETER                                              | TEST CONDITIONS                                                 | MIN | TYP   | MAX | UNIT              |

|--------------------------------------------------------|-----------------------------------------------------------------|-----|-------|-----|-------------------|

| Transmit idle channel noise, psophometrically weighted | TXPGA gain= 0 dB, micamp 1 gain = 23.5 dB, micamp 2 gain = 0 dB |     | -86.6 | -78 | dBm0 <sub>p</sub> |

| Transmit signal-to-distortion ratio with 1020-Hz       | MIC1N, MIC1P to PCMO at 3 dBm0                                  | 27  |       |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at 0 dBm0                                  | 30  |       |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at -5 dBm0                                 | 33  |       |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at -10 dBm0                                | 36  |       |     |                   |

| sine-wave input                                        | MIC1N, MIC1P to PCMO at -20 dBm0                                | 35  |       |     | dB                |

|                                                        | MIC1N, MIC1P to PCMO at – 30 dBm0                               | 26  |       |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at – 40 dBm0                               | 24  |       |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at – 45 dBm0                               | 19  |       |     |                   |

| Intermodulation distortion, 2-tone CCITT method,       | CCITT G.712 (7.1), R2                                           | 49  |       |     | -10               |

| composite power level, -13 dBm0                        | CCITT G.712 (7.2), R2                                           | 51  |       |     | dB                |

## electrical characteristics, $V_{DD}$ = 2.7 V, $T_A$ = 25°C (unless otherwise noted) (continued)

# transmit idle channel noise and distortion, companded mode ( $\mu$ -law or A-law) selected, slope filter enabled

| PARAMETER                                              | TEST CONDITIONS                                                   | MIN | TYP   | MAX | UNIT  |

|--------------------------------------------------------|-------------------------------------------------------------------|-----|-------|-----|-------|

| Transmit idle channel noise, psophometrically weighted | TXPGA gain= 0 dB, micamp 1 gain = 23.5 dB, micamp 2 gain = 0.0 dB |     | -86.6 | -78 | dBm0p |

|                                                        | MIC1N, MIC1P to PCMO at 3 dBm0                                    | 27  |       |     |       |

|                                                        | MIC1N, MIC1P to PCMO at 0 dBm0                                    | 30  |       |     |       |

| Transmit signal-to-total distortion ratio with 1020-Hz | MIC1N, MIC1P to PCMO at -5 dBm0                                   | 33  |       |     |       |

|                                                        | MIC1N, MIC1P to PCMO at -10 dBm0                                  | 36  |       |     | ٩D    |

| sine-wave input                                        | MIC1N, MIC1P to PCMO at -20 dBm0                                  | 35  |       |     | dB    |

|                                                        | MIC1N, MIC1P to PCMO at -30 dBm0                                  | 26  |       |     |       |

|                                                        | MIC1N, MIC1P to PCMO at -40 dBm0                                  | 24  |       |     |       |

|                                                        | MIC1N, MIC1P to PCMO at -45 dBm0                                  | 19  |       |     |       |

| Intermodulation distortion, 2-tone CCITT method,       | CCITT G.712 (7.1), R2                                             | 49  |       |     | 40    |

| composite power level, -13 dBm0                        | CCITT G.712 (7.2), R2                                             | 51  |       |     | dB    |

## transmit idle channel noise and distortion, linear mode selected, slope filter bypassed

| PARAMETER                                              | TEST CONDITIONS                                                  | MIN | TYP   | MAX | UNIT              |

|--------------------------------------------------------|------------------------------------------------------------------|-----|-------|-----|-------------------|

| Transmit idle channel noise                            | TXPGA gain = 0 dB, micamp 1 gain = 23.5 dB, micamp 2 gain = 0 dB |     | -86.6 | -78 | dBm0 <sub>p</sub> |

|                                                        | MIC1N, MIC1P to PCMO at 3 dBm0                                   | 40  | 50    |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at 0 dBm0                                   | 50  | 65    |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at -5 dBm0                                  | 60  | 68    |     |                   |

| Transmit signal-to-total distortion ratio with 1020-Hz | MIC1N, MIC1P to PCMO at -10 dBm0                                 | 55  | 70    |     | .ID               |

| sine-wave input                                        | MIC1N, MIC1P to PCMO at -20 dBm0                                 | 58  | 65    |     | dB                |

|                                                        | MIC1N, MIC1P to PCMO at -30 dBm0                                 | 50  | 60    |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at -40 dBm0                                 | 38  | 50    |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at -45 dBm0                                 | 30  | 45    |     |                   |

## transmit idle channel noise and distortion, linear mode selected, slope filter enabled

| PARAMETER                                              | TEST CONDITIONS                                                  | MIN | TYP   | MAX | UNIT              |

|--------------------------------------------------------|------------------------------------------------------------------|-----|-------|-----|-------------------|

| Transmit idle channel noise                            | TXPGA gain = 0 dB, micamp 1 gain = 23.5 dB, micamp 2 gain = 0 dB |     | -86.6 | -78 | dBm0 <sub>p</sub> |

|                                                        | MIC1N, MIC1P to PCMO at 3 dBm0                                   | 40  | 50    |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at 0 dBm0                                   | 50  | 65    |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at -5 dBm0                                  | 60  | 68    |     |                   |

| Transmit signal-to-total distortion ratio with 1020-Hz | MIC1N, MIC1P to PCMO at -10 dBm0                                 | 55  | 70    |     | .ID               |

| sine-wave input                                        | MIC1N, MIC1P to PCMO at -20 dBm0                                 | 58  | 65    |     | dB                |

|                                                        | MIC1N, MIC1P to PCMO at -30 dBm0                                 | 50  | 60    |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at -40 dBm0                                 | 38  | 50    |     |                   |

|                                                        | MIC1N, MIC1P to PCMO at -45 dBm0                                 | 30  | 45    |     |                   |

SLAS356 - DECEMBER 2001

## electrical characteristics, V<sub>DD</sub> = 2.7 V, T<sub>A</sub> = 25°C (unless otherwise noted) (continued)

# receive gain and dynamic range, EAR1 selected, linear or companded ( $\mu$ -law or A-law) mode selected (see Note 10)

| PARAMETER                                                 | TEST CONDITIONS                                        | MIN  | TYP  | MAX | UNIT     |

|-----------------------------------------------------------|--------------------------------------------------------|------|------|-----|----------|

| Constant size at the set (0.0 dD)                         | 16- $\Omega$ load RXPGA = -2 dB                        |      | 3.93 |     | .,       |

| Overload-signal level (3.0 dB)                            | 32-Ω load RXPGA = $-1$ dB (default gain)               |      | 4.41 |     | $V_{pp}$ |

| Absolute gain error                                       | 0-dBm0 input signal, V <sub>DD</sub> = 2.7 V (minimum) | -1   |      | 1   | dB       |

|                                                           | PCMIN to EAR1ON, EAR1OP at 3 dBm0 to -40 dBm0          | -0.5 |      | 0.5 |          |

| Gain error with output level relative to gain at –10 dBm0 | PCMIN to EAR1ON, EAR1OP at -41 dBm0 to -50 dBm0        | -1   |      | 1   | dB       |

| at = 10 dBmo                                              | PCMIN to EAR1ON, EAR1OP at -51 dBm0 to -55 dBm0        | -1.2 |      | 1.2 |          |

NOTE 10: RXPGA = -1 dB for 32  $\Omega$  default mode or RXPGA = -2 dB for 16  $\Omega$ , RXVOL = 0 dB, 1020 Hz input signal at PCMI, output measured differentially between EAR10N and EAR10P

# receive gain and dynamic range, EAR2 selected, linear or companded ( $\mu$ -law or A-law) mode selected (see Note 11)

| PARAMETER                                        | TEST CONDITIONS                                        | MIN  | TYP | MAX | UNIT            |

|--------------------------------------------------|--------------------------------------------------------|------|-----|-----|-----------------|

| Receive reference-signal level (0 dB)            | 0-dBm0 PCM input signal                                |      | 1.1 |     | V <sub>pp</sub> |

| Overload-signal level (3 dB)                     |                                                        |      | 1.6 |     | V <sub>pp</sub> |

| Absolute gain error                              | 0-dBm0 input signal, V <sub>DD</sub> = 2.7 V (minimum) | -1   |     | 1   | dB              |

| Gain error with output level relative to gain at | PCMIN to EAR2O at 3 dBm0 to -40 dBm0                   | -0.5 |     | 0.5 |                 |

|                                                  | PCMIN to EAR2O at -41 dBm0 to -50 dBm0                 | -1   |     | 1   | dB              |

| -10 dBillo                                       | PCMIN to EAR2O at -51 dBm0 to -55 dBm0                 | -1.2 |     | 1.2 |                 |

NOTE 11: RXPGA = -1 dB, RXVOL = 0 dB

# receive filter transfer, companded mode ( $\mu$ -law or A-law) or linear mode selected (MCLK = 2.048 MHz) (see Note 11)

| PARAMETER                                                                         | TEST CONDITIONS                  | MIN  | TYP | MAX | UNIT |

|-----------------------------------------------------------------------------------|----------------------------------|------|-----|-----|------|

|                                                                                   | fEAR1 or fEAR2 < 100 Hz          | -0.5 |     | 0.5 |      |

|                                                                                   | fEAR1 or fEAR2 = 200 Hz          | -0.5 |     | 0.5 |      |

| Gain relative to input signal gain at 1020 Hz, internal high-pass filter disabled | fEAR1 or fEAR2 = 300 Hz to 3 kHz | -0.5 |     | 0.5 |      |

|                                                                                   | fEAR1 or fEAR2 = 3.4 kHz         | -1.5 |     | 0   | dB   |

| Thigh page liker disabled                                                         | fEAR1 or fEAR2 = 4 kHz           |      |     | -14 |      |

|                                                                                   | fEAR1 or fEAR2 = 4.6 kHz         |      |     | -35 |      |

|                                                                                   | fEAR1 or fEAR2 = 8 kHz           |      |     | -47 |      |

| Gain relative to input signal gain at 1020 Hz, internal                           | fEAR1 or fEAR2 < 100 Hz          |      |     | -15 | .ID  |

|                                                                                   | fEAR1 or fEAR2 = 200 Hz          |      |     | -5  | dB   |

NOTE 11: RXPGA = -1 dB, RXVOL = 0 dB

## electrical characteristics, V<sub>DD</sub> = 2.7 V, T<sub>A</sub> = 25°C (unless otherwise noted) (continued)

# receive idle channel noise and distortion, EAR1 selected, companded mode ( $\mu$ -law or A-law) selected (see Note 12)

| PARAMETER                                       | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT              |

|-------------------------------------------------|-------------------------------------|-----|-----|-----|-------------------|

| Receive noise, psophometrically weighted        | PCMIN = 11010101 (A-law)            |     | -89 | -86 | dBm0 <sub>p</sub> |

| Receive noise, C-message weighted               | PCMIN = 11111111 (μ-law)            |     | 36  | 50  | μV <sub>rms</sub> |

|                                                 | PCMIN to EAR1ON, EAR1OP at 3 dBm0   | 21  |     |     |                   |

|                                                 | PCMIN to EAR1ON, EAR1OP at 0 dBm0   | 25  |     |     |                   |

|                                                 | PCMIN to EAR1ON, EAR1OP at -5 dBm0  | 36  |     |     |                   |

| Receive signal-to-distortion ratio with 1020-Hz | PCMIN to EAR1ON, EAR1OP at -10 dBm0 | 43  |     |     | 15                |

| sine-wave input                                 | PCMIN to EAR1ON, EAR1OP at -20 dBm0 | 40  |     |     | dB                |

|                                                 | PCMIN to EAR1ON, EAR1OP at -30 dBm0 | 38  |     |     |                   |

|                                                 | PCMIN to EAR1ON, EAR1OP at -40 dBm0 | 28  |     |     |                   |

|                                                 | PCMIN to EAR1ON, EAR1OP at -45 dBm0 | 23  |     |     |                   |

NOTE 12: RXPGA = -1 dB for 32- $\Omega$  default mode or RXPGA = -2 dB for 16  $\Omega$ , RXVOL = 0 dB, 1020 Hz input signal at PCMI, output measured differentially between EAR10N and EAR10P.

## receive idle channel noise and distortion, EAR1 selected, linear mode selected (see Note 12)

| PARAMETER                                         | TEST CONDITIONS                     | MIN | TYP | MAX | UNIT |

|---------------------------------------------------|-------------------------------------|-----|-----|-----|------|

| Receive noise, (20-Hz to 20-kHz brickwall window) | PCMIN = 000000000000                |     | -86 | -83 | dBm0 |

|                                                   | PCMIN to EAR1ON, EAR1OP at 3 dBm0   | 65  | 78  |     |      |

|                                                   | PCMIN to EAR1ON, EAR1OP at 0 dBm0   | 73  | 80  |     |      |

|                                                   | PCMIN to EAR1ON, EAR1OP at -5 dBm0  | 72  | 78  |     |      |

|                                                   | PCMIN to EAR1ON, EAR1OP at -10 dBm0 | 70  | 78  |     | -ID  |

| sine-wave input                                   | PCMIN to EAR1ON, EAR1OP at -20 dBm0 | 60  | 76  |     | dB   |

|                                                   | PCMIN to EAR1ON, EAR1OP at -30 dBm0 | 50  | 67  |     |      |

|                                                   | PCMIN to EAR1ON, EAR1OP at -40 dBm0 | 40  | 60  |     |      |

|                                                   | PCMIN to EAR1ON, EAR1OP at -45 dBm0 | 35  | 55  |     |      |

| Intermodulation distortion, 2-tone CCITT method,  | CCITT G.712 (7.1), R2               | 50  |     |     | -ID  |

| composite power level, –13 dBm0                   | CCITT G.712 (7.2), R2               | 54  |     |     | dB   |

NOTE 12: RXPGA = -1 dB for 32- $\Omega$  default mode or RXPGA = -2 dB for 16  $\Omega$ , RXVOL = 0 dB, 1020 Hz input signal at PCMI, output measured differentially between EAR10N and EAR10P.

# receive idle channel noise and distortion, EAR2 selected, companded mode ( $\mu$ -law or A-law) selected (see Note 111)

| PARAMETER                                       | TEST CONDITIONS            | MIN | TYP | MAX | UNIT          |

|-------------------------------------------------|----------------------------|-----|-----|-----|---------------|

| Receive noise, psophometrically weighted        | PCMIN = 11010101 (A-law)   |     | -81 | -78 | dBm0p         |

| Receive noise, C-message weighted               | PCMIN = 11111111 (μ-law)   |     | 36  | 50  | $\mu V_{rms}$ |

|                                                 | PCMIN to EAR2O at 3 dBm0   | 21  |     |     |               |

|                                                 | PCMIN to EAR2O at 0 dBm0   | 25  |     |     |               |

|                                                 | PCMIN to EAR2O at -5 dBm0  | 36  |     |     |               |

| Receive signal-to-distortion ratio with 1020-Hz | PCMIN to EAR2O at -10 dBm0 | 43  |     |     | .ID           |

| sine-wave input                                 | PCMIN to EAR2O at -20 dBm0 | 40  |     |     | dB            |

|                                                 | PCMIN to EAR2O at -30 dBm0 | 38  |     |     |               |

|                                                 | PCMIN to EAR2O at -40 dBm0 | 28  |     |     |               |

|                                                 | PCMIN to EAR2O at -45 dBm0 | 23  |     |     |               |

NOTE 11: RXPGA = -1 dB, RXVOL = 0 dB

## electrical characteristics, $V_{DD}$ = 2.7 V, $T_A$ = 25°C (unless otherwise noted) (continued)

## receive idle channel noise and distortion, EAR2 selected, linear mode selected (see Note 11)

| PARAMETER                                                  | TEST CONDITIONS            | MIN | TYP | MAX | UNIT |

|------------------------------------------------------------|----------------------------|-----|-----|-----|------|

| Receive noise, (20-Hz to 20-kHz brickwall window)          | PCMIN = 0000000000000      |     | -86 | -83 | dBm0 |

|                                                            | PCMIN to EAR2O at 3 dBm0   | 45  | 60  |     |      |

|                                                            | PCMIN to EAR2O at 0 dBm0   | 60  | 65  |     |      |

|                                                            | PCMIN to EAR2O at -5 dBm0  | 58  | 62  |     |      |

|                                                            | PCMIN to EAR2O at -10 dBm0 | 55  | 60  |     |      |

|                                                            | PCMIN to EAR2O at -20 dBm0 | 53  | 60  |     | dB   |

|                                                            | PCMIN to EAR2O at -30 dBm0 | 52  | 58  |     |      |

|                                                            | PCMIN to EAR2O at -40 dBm0 | 50  | 57  |     |      |

|                                                            | PCMIN to EAR2O at -45 dBm0 | 45  | 52  |     |      |

| Intermodulation distortion, 2-tone CCITT method, composite | CCITT G.712 (7.1), R2      | 50  |     |     | j    |

| power level, –13 dBm0                                      | CCITT G.712 (7.2), R2      | 54  |     |     | dB   |

NOTE 11: RXPGA = -1 dB, RXVOL = 0 dB

## power supply rejection and crosstalk attenuation

| PARAMETER                                                               | TEST CONDITIONS                                                                            | MIN | TYP | MAX | UNIT |

|-------------------------------------------------------------------------|--------------------------------------------------------------------------------------------|-----|-----|-----|------|

| Supply voltage rejection, transmit channel                              | MIC1N, MIC1P =0 V,<br>VDD = 2.7 V + 100 mV <sub>peak to peak</sub> , f = 0 to 50 kHz       |     | -80 | -45 | dB   |

| Supply voltage rejection, receive channel, EAR1 selected (differential) | PCM code = positive zero,<br>VDD = 2.7 V + 100 mV <sub>peak</sub> to peak, f = 0 to 50 kHz |     | -90 | -45 | dB   |

| Crosstalk attenuation, transmit-to-receive (differential)               | MIC1N, MIC1P = 0 dB, f = 300 to 3400 Hz measured differentially between EAR10N and EAR10P  | 70  |     |     | dB   |

| Crosstalk attenuation, receive-to-transmit                              | PCMIN = 0 dBm0, f = 300 to 3400 Hz measured at PCMO, EAR1 amplifier                        | 70  |     |     | dB   |

## **DTMF** generator

| 3                                                       |                                                     |       |     |      |      |

|---------------------------------------------------------|-----------------------------------------------------|-------|-----|------|------|

| PARAMETER                                               | TEST CONDITIONS                                     | MIN   | TYP | MAX  | UNIT |

| DTMF high to low tone relative amplitude (pre-emphasis) |                                                     | 1.5   | 2   | 2.5  | dB   |

| Tone frequency accuracy                                 |                                                     | -1.5% |     | 1.5% |      |

| Harmonic distortion                                     | Measured from lower tone group to highest parasitic |       |     | -20  | dB   |

## **MICBIAS**

| PARAMETER      | TEST CONDITIONS | MIN | TYP | MAX | UNIT |

|----------------|-----------------|-----|-----|-----|------|

| Load impedance |                 | 2   |     | 2.5 | kΩ   |

## timing requirements

## clock

|                         |                                                | MIN   | NOM | MAX   | UNIT |

|-------------------------|------------------------------------------------|-------|-----|-------|------|

| t <sub>t</sub>          | Transition time, MCLK                          |       |     | 10    | ns   |

|                         | MCLK frequency                                 | 2.048 |     | 2.048 | MHz  |

|                         | MCLK jitter                                    |       |     | 37%   |      |

|                         | Number of PCMCLK clock cycles per PCMSYN frame | 256   |     | 256   |      |

| t <sub>c</sub> (PCMCLK) | PCMCLK clock period                            | 156   | 488 | 512   | ns   |

|                         | Duty cycle, PCMCLK                             | 45%   | 50% | 68%   | •    |

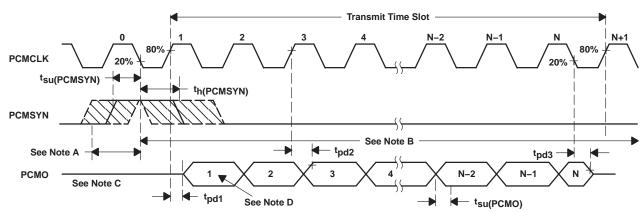

## transmit (see Figure 6)

|                          |                                        | MIN | MAX                        | UNIT |

|--------------------------|----------------------------------------|-----|----------------------------|------|

| t <sub>su</sub> (PCMSYN) | Setup time, PCMSYN high before PCMCLK↓ | 20  | t <sub>C</sub> (PCMCLK)-20 | 20   |

| th(PCMSYN)               | Hold time, PCMSYN high after PCMCLK↓   | 20  | t <sub>c</sub> (PCMCLK)-20 | ns   |

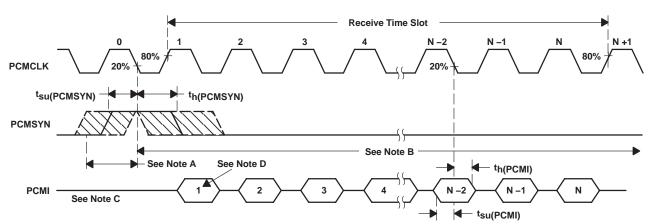

## receive (see Figure 5)

|                         |                                             | MIN | MAX                        | UNIT |

|-------------------------|---------------------------------------------|-----|----------------------------|------|

| t <sub>su</sub> (PCSYN) | Setup time, PCMSYN high before PCMCLK↓      | 20  | t <sub>c</sub> (PCMCLK)-20 | ns   |

| th(PCSYN)               | Hold time, PCMSYN high after PCMCLK↓        | 20  | t <sub>c(PCMCLK)</sub> -20 | ns   |

| t <sub>su(PCMI)</sub>   | Setup time, PCMI high or low before PCMCLK↓ | 20  |                            | ns   |

| th(PCMI)                | Hold time, PCMI high or low after PCMCLK↓   | 20  |                            | ns   |

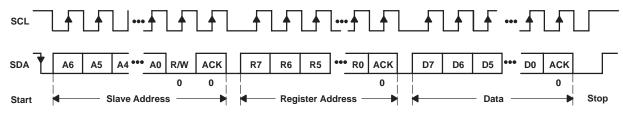

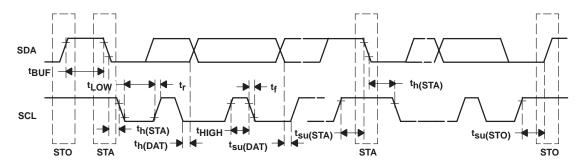

# I<sup>2</sup>C bus (see Figure 6)

|                      |                                                                                             | MIN  | MAX | UNIT |

|----------------------|---------------------------------------------------------------------------------------------|------|-----|------|

| SCL                  | Clock frequency                                                                             |      | 400 | kHz  |

| tHIGH                | Clock high time                                                                             | 600  |     | ns   |

| tLOW                 | Clock low time                                                                              | 1300 |     | ns   |

| t <sub>r</sub>       | SDA and SCL rise time                                                                       |      | 300 | ns   |

| tf                   | SDA and SCL fall time                                                                       |      | 300 | ns   |

| th(STA)              | Hold time (repeated) START condition. After this period the first clock pulse is generated. | 600  |     | ns   |

| t <sub>su(STA)</sub> | Setup time for repeated START condition                                                     | 600  |     | ns   |

| th(DAT)              | Data input hold time                                                                        | 0    |     | ns   |

| t <sub>su(DAT)</sub> | Data input setup time                                                                       | 100  |     | ns   |

| t <sub>su(STO)</sub> | STOP condition setup time                                                                   | 600  | ·   | ns   |

| <sup>t</sup> BUF     | Bus free time                                                                               | 1300 |     | ns   |

# switching characteristics

# propagation delay times, $C_{L(max)} = 10 pF$ (see Figure 5)

|                  |                                             | MIN | MAX | UNIT |

|------------------|---------------------------------------------|-----|-----|------|

| tpd1             | From PCMCLK bit 1 high to PCMO bit 1 valid  |     | 35  | ns   |

| t <sub>pd2</sub> | From PCMCLK high to PCMO valid, bits 2 to n |     | 35  | ns   |

| tpd3             | From PCMCLK bit n low to PCMO bit n Hi-Z    | 30  |     | ns   |

NOTE: SLAVE = Voice Codec

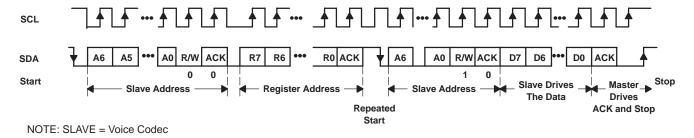

Figure 1. I<sup>2</sup>C Bus Write to Voice Codec

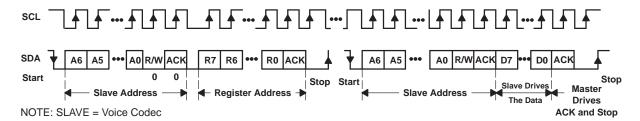

Figure 2. I<sup>2</sup>C Read From Voice Codec: Protocol A

Figure 3. I<sup>2</sup>C Read From Voice Codec: Protocol B

# register map addressing

|               | REG            | 07             | 06             | 05             | 04             | 03             | 02             | 01             | 00             |

|---------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|----------------|

| Power control | 00             | Sidetone<br>En | TXEn           | RXEn           | MICSEL         | BIASEn         | RXEn           | EAROUT<br>Sel  | PWRUP          |

| Mode control  | 01 Comp Sel TM |                | TMEn           | PCMLB Comp En  |                | BUZZEn         | RXFLTR<br>En   | TXFLTR<br>En   | TXSLOPE<br>En  |

| TXPGA         | 02             | PD0            | TP3            | TP2            | TP1            | TP0            | ST2            | ST1            | ST0            |

| RXPGA         | 03             | RP3            | RP2            | RP1            | RP0            | RV3            | RV2            | RV1            | RV0            |

| High DTMF     | 04             | HIFREQ<br>Sel7 | HIFREQ<br>Sel6 | HIFREQ<br>Sel5 | HIFREQ<br>Sel4 | HIFREQ<br>Sel3 | HIFREQ<br>Sel2 | HIFREQ<br>Sel1 | HIFREQ<br>Sel0 |

| Low DTMF      | 05             | LOFREQ<br>Sel7 | LOFREQ<br>Sel6 | LOFREQ<br>Sel5 | LOFREQ<br>Sel4 | LOFREQ<br>Sel3 | LOFREQ<br>Sel2 | LOFREQ<br>Sel1 | LOFREQ<br>Sel0 |

# register power-up defaults

|                | REG | 07 | 06 | 05 | 04 | 03 | 02 | 01 | 00 |

|----------------|-----|----|----|----|----|----|----|----|----|

| Power control† | 00  | 1  | 1  | 1  | 1  | 0  | 1  | 1  | 0  |

| Power control‡ | 00  | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 1  |

| Mode control   | 01  | 0  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| TXPGA          | 02  | 0  | 1  | 0  | 0  | 0  | 0  | 0  | 0  |

| RXPGA          | 03  | 0  | 1  | 1  | 1  | 0  | 0  | 0  | 0  |

| High DTMF      | 04  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| Low DTMF       | 05  | 0  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

<sup>†</sup> Value when PWRUPSEL = 0 ‡ Value when PWRUPSEL = 1

## register map

Table 1. Power Control Register: Address (00) HEX

|   |   | E | BIT NU | MBER |   |   |   | DEFINITIONS                            |  |  |  |

|---|---|---|--------|------|---|---|---|----------------------------------------|--|--|--|

| 7 | 6 | 5 | 4      | 3    | 2 | 1 | 0 | DEFINITIONS                            |  |  |  |

| 1 | 1 | 1 | 1      | 0    | 1 | 1 | 0 | Default setting PWRUPSEL = 0           |  |  |  |

| 1 | 0 | 0 | 1      | 1    | 0 | 1 | 1 | Default setting PWRUPSEL = 1           |  |  |  |

| Х | Χ | Χ | Χ      | Χ    | Χ | Χ | 0 | Reference system, power down           |  |  |  |

| Х | Χ | Χ | Χ      | X    | Χ | Χ | 1 | Reference system, power up             |  |  |  |

| Х | Χ | Χ | Χ      | X    | Χ | 1 | Χ | EAR AMP1 selected, EAR AMP2 power down |  |  |  |

| Х | Χ | Χ | Χ      | X    | Χ | 0 | Χ | EAR AMP2 selected, EAR AMP1 power down |  |  |  |

| Х | Χ | Χ | Χ      | X    | 0 | Χ | Χ | Receive channel enabled                |  |  |  |

| Х | Χ | 0 | Χ      | X    | 1 | Χ | Χ | Receive channel muted                  |  |  |  |

| Х | Χ | 1 | Χ      | Χ    | 1 | Χ | 0 | Receive channel, power down            |  |  |  |

| Х | Χ | Χ | Χ      | 1    | Χ | Χ | Χ | MICBIAS selected                       |  |  |  |

| Х | Χ | Χ | Χ      | 0    | Χ | Χ | Χ | MICBIAS power down                     |  |  |  |

| Х | Χ | Χ | 1      | X    | Χ | Χ | Χ | MIC1 selected                          |  |  |  |

| Х | Χ | Χ | 0      | X    | Χ | Χ | Χ | MIC2 selected                          |  |  |  |

| Х | 0 | Χ | Χ      | Χ    | Χ | Χ | Χ | Transmit channel enabled               |  |  |  |

| Х | 1 | 0 | Χ      | Χ    | Χ | Χ | Χ | Transmit channel muted                 |  |  |  |

| Х | 1 | 1 | Χ      | Χ    | Χ | X | Χ | Transmit channel power down            |  |  |  |

| 0 | Χ | Χ | X      | Χ    | Χ | Χ | Χ | Sidetone enabled                       |  |  |  |

| 1 | Χ | Χ | Χ      | Χ    | Χ | Χ | Χ | Sidetone muted                         |  |  |  |

Table 2. Mode Control Register: Address (01) HEX

|   |   |   | BIT NU | MBER |   |   |   |                                                                |  |  |

|---|---|---|--------|------|---|---|---|----------------------------------------------------------------|--|--|

| 7 | 6 | 5 | 4      | 3    | 2 | 1 | 0 | DEFINITIONS                                                    |  |  |

| 0 | 0 | 0 | 0      | 0    | 0 | 1 | 0 | Default setting                                                |  |  |

| Х | Χ | X | Χ      | X    | X | 0 | 0 | TX channel high-pass filter enabled and slope filter enabled   |  |  |

| Х | Χ | X | Χ      | X    | X | 0 | 1 | TX channel high-pass filter enabled and slope filter disabled  |  |  |

| Х | Χ | Χ | Χ      | Χ    | X | 1 | 0 | TX channel high-pass filter disabled and slope filter enabled  |  |  |

| Х | X | Χ | Χ      | X    | Χ | 1 | 1 | TX channel high-pass filter disabled and slope filter disabled |  |  |

| Х | Χ | Χ | Χ      | Χ    | 0 | Χ | Χ | RX channel high-pass filter disabled (low pass only)           |  |  |

| Х | Χ | X | Χ      | X    | 1 | Χ | Χ | RX channel high-pass filter enabled                            |  |  |

| Х | Χ | Χ | Χ      | 0    | X | Χ | Χ | BUZZCON disabled                                               |  |  |

| Х | Χ | Χ | Χ      | 1    | X | Χ | Χ | BUZZCON enabled                                                |  |  |

| Х | Χ | Χ | 0      | X    | X | Χ | Χ | Linear mode selected                                           |  |  |

| 1 | Χ | Χ | 1      | Χ    | X | Χ | Χ | A-law companding mode selected                                 |  |  |

| 0 | Χ | Χ | 1      | Χ    | X | Χ | Χ | μ-law companding mode selected                                 |  |  |

| Х | Χ | 0 | Χ      | Χ    | X | Χ | Χ | TX and RX channels normal mode                                 |  |  |

| Х | Χ | 1 | Χ      | Χ    | X | Χ | Χ | PCM loopback mode                                              |  |  |

| Х | 0 | Χ | Χ      | X    | Χ | Χ | Χ | Tone mode disabled                                             |  |  |

| Х | 1 | Χ | Χ      | Χ    | X | Χ | Χ | Tone mode enabled                                              |  |  |

Transmit PGA and sidetone control register: Address {02}HEX

#### Bit definitions:

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | DEFINITION              |

|-----|-----|-----|-----|-----|-----|-----|-----|-------------------------|

| PDO | TP3 | TP2 | TP1 | TP0 | ST2 | ST1 | ST0 | See Table 2 and Table 4 |

| 0   | 1   | 0   | 0   | 0   | 0   | 0   | 0   | Default setting         |

Receive volume control register: Address {03}HEX

## Bit definitions:

| 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | DEFINITION              |

|-----|-----|-----|-----|-----|-----|-----|-----|-------------------------|

| RP3 | RP2 | RP1 | RP0 | RV3 | RV2 | RV1 | RV0 | See Table 3 and Table 5 |

| 0   | 1   | 1   | 1   | 0   | 0   | 0   | 0   | Default setting         |

High tone selection control register: Address {04}HEX

#### Bit definitions:

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 | DEFINITION         |

|---|---|---|---|---|---|---|---|--------------------|

| Χ | Х | Х | Х | Х | Х | Х | Х | DTMF (see Table 7) |

| 0 | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Default setting    |

Low tone selection control register: Address {05}HEX

#### Bit definitions:

| 7 | <b>'</b> | 6 | 5 | 4 | 3 | 2 | 1 | 0 | DEFINITION         |

|---|----------|---|---|---|---|---|---|---|--------------------|

| Х | (        | Х | Х | Х | Х | Х | Х | Х | DTMF (see Table 7) |

| 0 | )        | 0 | 0 | 0 | 0 | 0 | 0 | 0 | Default setting    |

NOTES: A. This window is allowed for PCMSYN high.

- B. This window is allowed for PCMSYN low (th(PCMSYN) max determined by data collision considerations).

- C. Transitions are measured at 50%.

- D. Bit 1 = MSB, Bit N = LSB

**Figure 4. Transmit Timing Diagram**

- A. This window is allowed for PCMSYN high.

- B. This window is allowed for PCMSYN low.

- C. Transitions are measured at 50%.

- D. Bit 1 = MSB, Bit N = LSB

Figure 5. Receive Timing Diagram

Figure 6. I<sup>2</sup>C Bus Timing Diagram

## power-on initialization

An external reset with a minimum pulse width of 500 ns must be applied to the active low RESET terminal to assure reset upon power on. All registers are set with default values upon external reset initialization.

The desired selection for all programmable functions can be initialized prior to a power-up command using the I<sup>2</sup>C interface.

Table 3. Power-Up and Power-Down Procedures (V<sub>DD</sub> = 2.7 V, Earphone Amplifier Unloaded)

| DEVICE STATUS | PROCEDURE                                             | MAXIMUM POWER CONSUMPTION |

|---------------|-------------------------------------------------------|---------------------------|

| D             | Set bit 1 = 1 in power control register, EAR1 enabled | 16.2 mW                   |

| Power up      | Set bit 1 = 0 in power control register, EAR2 enabled | 14.6 mW                   |

| Daniel danie  | Set bit 7 = 1 in TXPGA control register and bit 0 = 0 | 1.35 μW                   |

| Power down    | Set bit 7 = 0 in TXPGA control register and bit 0 = 0 | 67.5 μW                   |

In addition to resetting the power-down bit in the power control register, loss of MCLK (no transition detected) automatically enters the device into a power-down state with PCMO in the high impedance state. If during a pulse code modulation (PCM) data transmit cycle an asynchronous power down occurs, the PCM interface remains powered up until the PCM data is completely transferred.

An additional power-down mode overrides the MCLK detection function. This allows the device to enter the power-down state without regard to MCLK. Setting bit 7 of the TX filter and PGA sidetone register to logic high enables this function.

#### conversion laws

The device can be programmed either for a 15-bit linear or 8-bit ( $\mu$ -law or A-law) companding mode. The companding operation approximates the CCITT G.711 recommendation. The linear mode operation uses a 15-bit twos-complement format.

## transmit operation

#### microphone input