# 15 A microBUCK<sup>®</sup> SiC401A/B Integrated Buck Regulator with Programmable LDO

### DESCRIPTION

The Vishay Siliconix SiC401A/B an advanced stand-alone synchronous buck regulator featuring integrated power MOSFETs, bootstrap switch, and a programmable LDO in a space-saving PowerPAK MLP55-32L pin package.

The SiC401A/B is capable of operating with all ceramic solutions and switching frequencies up to 1 MHz. The programmable frequency, synchronous operation and selectable power-save allow operation at high efficiency across the full range of load current. The internal LDO may be used to supply 5 V for the gate drive circuits or it may be bypassed with an external 5 V for optimum efficiency and used to drive external n-channel MOSFETs or other loads. Additional features include cycle-by-cycle current limit, voltage soft-start, under-voltage protection, programmable over-current protection, soft shutdown and selectable power-save. The Vishay Siliconix SiC401A/B also provides an enable input and a power good output.

| PRODUCT SUMMARY           |                                              |  |  |  |  |

|---------------------------|----------------------------------------------|--|--|--|--|

| Input Voltage Range       | 3 V to 17 V                                  |  |  |  |  |

| Output Voltage Range      | 0.6 V to V <sub>IN</sub> x 0.75 <sup>a</sup> |  |  |  |  |

| Operating Frequency       | 200 kHz to 1 MHz                             |  |  |  |  |

| Continuous Output Current | 15 A                                         |  |  |  |  |

| Peak Efficiency           | 93 %                                         |  |  |  |  |

| Package                   | PowerPAK MLP55-32L                           |  |  |  |  |

#### Note

a. See "High Output Voltage Operation" section

### FEATURES

- High efficiency > 93 %

- 15 A continuous output current capability

- Integrated bootstrap switch

- Programmable 200 mA LDO with bypass logic

- Temperature compensated current limit

- All ceramic solution enabled

- Pseudo fixed-frequency adaptive on-time control

- Programmable input UVLO threshold

- Independent enable pin for switcher and LDO

- Selectable ultra-sonic power-save mode (SiC401A)

- Selectable power-save mode (SiC401B)

- Programmable soft-start and soft-shutdown

- 1 % internal reference voltage

- Power good output

- Over-voltage and under-voltage protections

- PowerCAD Simulation software available at <u>www.vishay.com/power-ics/powercad-list/</u>

- Material categorization: for definitions of compliance please see <u>www.vishay.com/doc?99912</u>

### APPLICATIONS

- Notebook, desktop and server computers

- Digital HDTV and digital consumer applications

- Networking and telecommunication equipment

- Printers, DSL, and STB applications

- Embedded applications

- Point of load power supplies

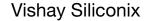

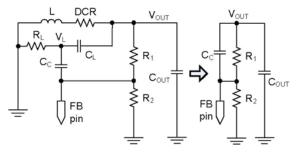

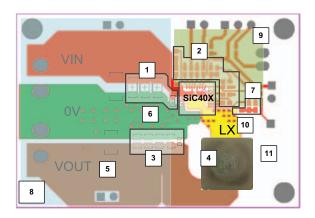

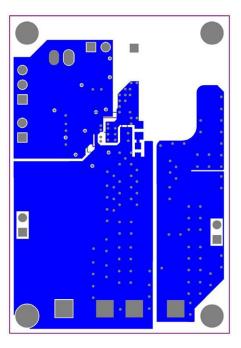

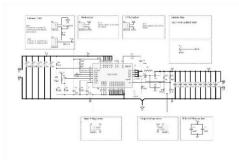

## TYPICAL APPLICATION CIRCUIT AND PACKAGE OPTIONS

Typical Application Circuit for SiC401A/B (PowerPAK MLP5x5-32L)

**Vishay Siliconix**

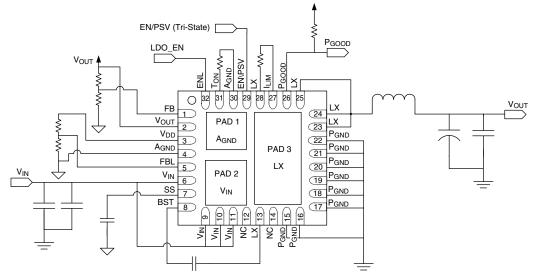

## FUNCTIONAL BLOCK DIAGRAM

SiC401A/B Functional Block Diagram

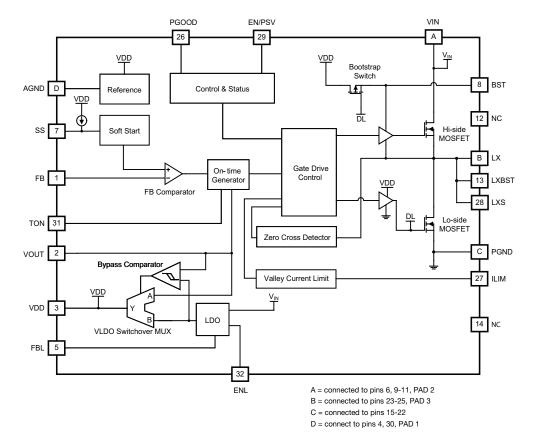

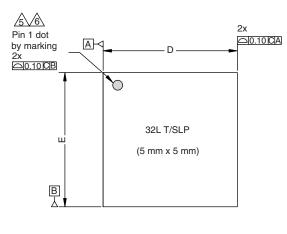

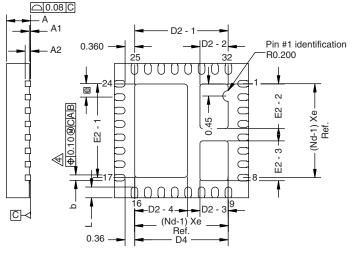

### **PIN CONFIGURATION**

SiC401A/B Pin Configuration (Top View)

www.vishay.com

# Vishay Siliconix

| PIN DESCRIPTI     | ON                |                                                                                                                                                                                                                    |

|-------------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| PIN NUMBER        | SYMBOL            | DESCRIPTION                                                                                                                                                                                                        |

| 1                 | FB                | Feedback input for switching regulator used to program the output voltage - connect to an external resistor divider from $V_{OUT}$ to $A_{GND}$ .                                                                  |

| 2                 | V <sub>OUT</sub>  | Switcher output voltage sense pin - also the input to the internal switch-over between $V_{OUT}$ and $V_{LDO}$ . The voltage at this pin must be less than or equal to the voltage at the $V_{DD}$ pin.            |

| 3                 | V <sub>DD</sub>   | Bias supply for the IC - when using the internal LDO as a bias power supply, $V_{DD}$ is the LDO output. When using an external power supply as the bias for the IC, the LDO output should be disabled.            |

| 4, 30, PAD 1      | A <sub>GND</sub>  | Analog ground                                                                                                                                                                                                      |

| 5                 | FBL               | Feedback input for the internal LDO - used to program the LDO output. Connect to an external resistor divider from $V_{DD}$ to $A_{GND}$ .                                                                         |

| 6, 9 to 11, PAD 2 | V <sub>IN</sub>   | Input supply voltage                                                                                                                                                                                               |

| 7                 | SS                | The soft start ramp will be programmed by an internal current source charging a capacitor on this pin.                                                                                                             |

| 8                 | BST               | Bootstrap pin - connect a capacitor of at least 100 nF from BST to LX to develop the floating supply for the high-side gate drive.                                                                                 |

| 12, 14            | NC                | No connection                                                                                                                                                                                                      |

| 13                | LXBST             | LX Boost - connect to the BST capacitor.                                                                                                                                                                           |

| 23 to 25, PAD3    | LX                | Switching (phase) node                                                                                                                                                                                             |

| 15 to 22          | P <sub>GND</sub>  | Power ground                                                                                                                                                                                                       |

| 26                | P <sub>GOOD</sub> | Open-drain power good indicator - high impedance indicates power is good. An external pull-up resistor is required.                                                                                                |

| 27                | I <sub>LIM</sub>  | Current limit sense pin - used to program the current limit by connecting a resistor from ILIM to LXS.                                                                                                             |

| 28                | LXS               | LX sense - connects to R <sub>ILIM</sub>                                                                                                                                                                           |

| 29                | EN/PSV            | Enable/power save input for the switching regulator - connect to $A_{GND}$ to disable the switching regulator, connect to $V_{DD}$ to operate with power-save mode and float to operate in forced continuous mode. |

| 31                | t <sub>ON</sub>   | On-time programming input - set the on-time by connecting through a resistor to AGND                                                                                                                               |

| 32                | ENL               | Enable input for the LDO - connect ENL to $A_{GND}$ to disable the LDO. Drive with logic signal for logic control, or program the $V_{IN}$ UVLO with a resistor divider between $V_{IN}$ , ENL, and $A_{GND}$ .    |

| ORDERING INFORMATION |                    |                       |

|----------------------|--------------------|-----------------------|

| PART NUMBER          | PACKAGE            | MARKING (LINE 1: P/N) |

| SiC401ACD-T1-GE3     | PowerPAK MLP55-32L | SiC401A               |

| SiC401BCD-T1-GE3     | PowerPAK MLP55-32L | SiC401B               |

| SiC401DB             | Referen            | ce board              |

Format:

Line 1: P/N

Line 2: Siliconix logo + Lot code + ESD symbol

Line 3: Factory code + Year code + Work week code

3

www.vishay.com

Vishay Siliconix

| ABSOLUTE MAXIMUM RATINGS (T <sub>A</sub> = 2                                  | 25 °C, unless otherwise noted) |                                  |      |

|-------------------------------------------------------------------------------|--------------------------------|----------------------------------|------|

| ELECTRICAL PARAMETER                                                          | CONDITIONS                     | LIMITS                           | UNIT |

| V <sub>IN</sub>                                                               | to P <sub>GND</sub>            | -0.3 to +20                      |      |

| V <sub>IN</sub>                                                               | to V <sub>DD</sub>             | -0.4 max.                        |      |

| LX                                                                            | to P <sub>GND</sub>            | -0.3 to +20                      |      |

| LX (Transient < 100 ns)                                                       | to P <sub>GND</sub>            | -2 to +20                        |      |

| V <sub>DD</sub>                                                               | to P <sub>GND</sub>            | -0.3 to +6                       |      |

| EN/PSV, P <sub>GOOD</sub> , I <sub>LIM</sub> , SS, V <sub>OUT</sub> , FB, FBL | Reference to A <sub>GND</sub>  | -0.3 to +(V <sub>DD</sub> + 0.3) | V    |

| t <sub>ON</sub>                                                               | to P <sub>GND</sub>            | -0.3 to +(V <sub>DD</sub> - 1.5) |      |

| BST                                                                           | to LX                          | -0.3 to +6                       |      |

| D31                                                                           | to P <sub>GND</sub>            | -0.3 to +25                      |      |

| ENL                                                                           |                                | -0.3 to V <sub>IN</sub>          |      |

| A <sub>GND</sub> to P <sub>GND</sub>                                          |                                | -0.3 to +0.3                     |      |

| Temperature                                                                   |                                |                                  |      |

| Maximum Junction Temperature                                                  |                                | 150                              | ℃    |

| Storage Temperature                                                           |                                | -65 to 150                       | C    |

| Power Dissipation                                                             |                                |                                  |      |

| Junction to Ambient Thermal Impedance ( $R_{thJA}$ ) <sup>b</sup>             | IC Section                     | 50                               | °C/W |

| Maximum Bawar Dissinction                                                     | Ambient Temperature = 25 °C    | 3.4                              | w    |

| Maximum Power Dissipation                                                     | Ambient Temperature = 100 °C   | 1.3                              | vv   |

| ESD Protection                                                                |                                |                                  | ·    |

|                                                                               | НВМ                            | 2                                | – kV |

|                                                                               | CDM                            | 1                                | ĸv   |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating/conditions for extended periods may affect device reliability.

| <b>RECOMMENDED OPERATING</b>        | <b>CONDITIONS</b> (a | II voltages refer | enced to GNE | 0 = 0 V)               |      |

|-------------------------------------|----------------------|-------------------|--------------|------------------------|------|

| PARAMETER                           | SYMBOL               | MIN.              | TYP.         | MAX.                   | UNIT |

| Input Voltage                       | V <sub>IN</sub>      | 3                 | -            | 17                     |      |

| V <sub>DD</sub> to P <sub>GND</sub> |                      | 3                 | -            | 5.5                    | V    |

| Output Voltage                      | V <sub>OUT</sub>     | 0.6               | -            | V <sub>IN</sub> x 0.75 |      |

| Temperature                         |                      |                   |              |                        |      |

| Ambient Temperature                 |                      | -40 to +          | -85          |                        | °C   |

4

# Vishay Siliconix

| ELECTRICAL SPECIFICATIONS                                              |                              | TEST CONDITIONS UNLESS SPECIFIED                                                                                                                                                                                                                                                                                        |       |         |       |          |

|------------------------------------------------------------------------|------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------|-------|----------|

| PARAMETER                                                              | SYMBOL                       | $      V_{\text{IN}} = 12 \text{ V},  \text{V}_{\text{DD}} = 5 \text{ V},  \text{T}_{\text{A}} = +25 ^{\circ}\text{C} \text{ for typ.}, \\       -40 ^{\circ}\text{C} \text{ to } +85 ^{\circ}\text{C} \text{ for min. and max.}, \\       T_{\text{J}} = < 125 ^{\circ}\text{C}, \text{ typical application circuit} $ | MIN.  | TYP.    | MAX.  | UNIT     |

| Input Power Supplies                                                   |                              |                                                                                                                                                                                                                                                                                                                         |       |         |       |          |

| Input Supply Voltage                                                   | V <sub>IN</sub>              |                                                                                                                                                                                                                                                                                                                         | 3     | -       | 17    |          |

| V <sub>DD</sub>                                                        | V <sub>DD</sub>              |                                                                                                                                                                                                                                                                                                                         | 3     | -       | 5.5   |          |

| V <sub>IN</sub> UVLO Threshold <sup>a</sup>                            | M                            | Sensed at ENL pin, rising                                                                                                                                                                                                                                                                                               | 2.4   | 2.6     | 2.95  | 1        |

| VIN OVEO Threshold "                                                   | V <sub>UVLO</sub>            | Sensed at ENL pin, falling                                                                                                                                                                                                                                                                                              | 2.23  | 2.4     | 2.57  | v        |

| V <sub>IN</sub> UVLO Hysteresis                                        | V <sub>UVLO, HYS</sub>       |                                                                                                                                                                                                                                                                                                                         | -     | 0.25    | -     | v        |

| V <sub>DD</sub> UVLO Threshold                                         | V                            | Measured at V <sub>DD</sub> pin, rising                                                                                                                                                                                                                                                                                 | 2.5   | -       | 3     |          |

| V <sub>DD</sub> OVLO Threshold                                         | V <sub>UVLO</sub>            | Measured at V <sub>DD</sub> pin, falling                                                                                                                                                                                                                                                                                | 2.4   | -       | 2.9   |          |

| V <sub>DD</sub> UVLO Hysteresis                                        | V <sub>UVLO, HYS</sub>       |                                                                                                                                                                                                                                                                                                                         | -     | 0.2     | -     |          |

| V Cumply Current                                                       | 1                            | ENL, EN/PSV = 0 V , V <sub>IN</sub> = 17 V                                                                                                                                                                                                                                                                              | -     | 10      | 20    |          |

| V <sub>IN</sub> Supply Current                                         | I <sub>IN</sub>              | Standby mode; ENL= V <sub>DD</sub> , EN/PSV = 0 V                                                                                                                                                                                                                                                                       | -     | 130     | -     | μA       |

|                                                                        |                              | ENL, EN/PSV = 0 V                                                                                                                                                                                                                                                                                                       | -     | 190     | 300   |          |

|                                                                        |                              | SiC401A, EN/PSV = $V_{DD}$ , no load<br>(f <sub>SW</sub> = 25 kHz), V <sub>FB</sub> > 0.6 V <sup>b</sup>                                                                                                                                                                                                                | -     | 0.3     | -     |          |

| V <sub>DD</sub> Supply Current                                         | I <sub>DD</sub>              | SiC401B, EN/PSV = $V_{DD}$ , no load,<br>$V_{FB} > 0.6 V^{b}$                                                                                                                                                                                                                                                           | -     | 0.7     | -     |          |

|                                                                        |                              | $V_{DD}$ = 5 V, f <sub>SW</sub> = 250 kHz,<br>EN/PSV = floating, no load <sup>b</sup>                                                                                                                                                                                                                                   | -     | 9       | -     | mA       |

|                                                                        |                              | $V_{DD} = 3 \text{ V}, f_{SW} = 250 \text{ kHz},$<br>EN/PSV = floating, no load <sup>b</sup>                                                                                                                                                                                                                            | -     | 5.5     | -     | -        |

| FB On-Time Threshold                                                   |                              | Static V <sub>IN</sub> and load                                                                                                                                                                                                                                                                                         | 0.594 | 0.600   | 0.606 | V        |

| Francisco Dener                                                        | 4                            | Continuous mode operation                                                                                                                                                                                                                                                                                               | -     | -       | 1000  |          |

| Frequency Range                                                        | f <sub>SW</sub>              | Minimum f <sub>SW</sub> , (SiC401A only)                                                                                                                                                                                                                                                                                | -     | 25      | -     | kHz      |

| Bootstrap Switch Resistance                                            |                              |                                                                                                                                                                                                                                                                                                                         | -     | 10      | -     | Ω        |

| Timing                                                                 |                              |                                                                                                                                                                                                                                                                                                                         |       |         |       |          |

| On-Time                                                                | t <sub>ON</sub>              | Continuous mode operation V_{IN} = 12 V, V_{OUT} = 5 V, f_{SW} = 300 kHz, R_{ton} = 133 k\Omega                                                                                                                                                                                                                         | 999   | 1110    | 1220  |          |

| Minimum On-Time <sup>b</sup>                                           | t <sub>ON, min</sub> .       |                                                                                                                                                                                                                                                                                                                         | -     | 80      | -     | ns       |

| Minimum Off-Time <sup>b</sup>                                          | +                            | $V_{DD} = 5 V$                                                                                                                                                                                                                                                                                                          | -     | 250     | -     |          |

| Minimum OII-Time ~                                                     | t <sub>OFF,</sub> min.       | V <sub>DD</sub> = 3 V                                                                                                                                                                                                                                                                                                   | -     | 370     | -     | 1        |

| Soft Start                                                             |                              |                                                                                                                                                                                                                                                                                                                         |       |         |       |          |

| Soft Start Current <sup>b</sup>                                        | I <sub>SS</sub>              |                                                                                                                                                                                                                                                                                                                         | -     | 3       | -     | μA       |

| Soft Start Voltage <sup>b</sup>                                        | V <sub>SS</sub>              | When V <sub>OUT</sub> reaches regulation                                                                                                                                                                                                                                                                                | -     | 1.5     | -     | V        |

| Analog Inputs/Outputs                                                  |                              |                                                                                                                                                                                                                                                                                                                         |       |         |       |          |

| V <sub>OUT</sub> Input Resistance                                      | R <sub>O-IN</sub>            |                                                                                                                                                                                                                                                                                                                         | -     | 500     | -     | kΩ       |

| Current Sense                                                          |                              | · · · · · · · · · · · · · · · · · · ·                                                                                                                                                                                                                                                                                   |       |         |       |          |

| Zero-Crossing Detector Threshold Voltage                               | V <sub>Sense-th</sub>        | LX-P <sub>GND</sub>                                                                                                                                                                                                                                                                                                     | -3    | -       | +3    | mV       |

| Power Good                                                             |                              |                                                                                                                                                                                                                                                                                                                         |       |         |       |          |

| Davier Oa ald Threads ald                                              | PG_V <sub>TH_UPPER</sub>     | Upper limit, V <sub>FB</sub> > internal 600 mV reference                                                                                                                                                                                                                                                                | -     | ± 20    | -     |          |

| Power Good Threshold                                                   | PG_V <sub>TH_LOWER</sub>     | Lower limit, V <sub>FB</sub> < internal 600 mV reference                                                                                                                                                                                                                                                                | -     | -10     | -     | %        |

| Start-Up Delay Time<br>(between PWM enable and P <sub>GOOD</sub> high) | PG_T <sub>d</sub>            | $V_{DD} = 5 \text{ V}, \text{ C}_{SS} = 10 \text{ nF}$<br>$V_{DD} = 3 \text{ V}, \text{ C}_{SS} = 10 \text{ nF}$                                                                                                                                                                                                        | -     | 12<br>7 | -     | ms       |

| Fault (noise-immunity) Delay Time <sup>b</sup>                         | PG_I <sub>CC</sub>           | ייי                                                                                                                                                                                                                                                                                                                     |       | 5       | -     | μs       |

| Leakage Current                                                        | PG_ICC<br>PG_I <sub>LK</sub> |                                                                                                                                                                                                                                                                                                                         | -     | -       | - 1   | μs<br>μA |

| Leanage Ourient                                                        |                              |                                                                                                                                                                                                                                                                                                                         | -     | -       | 1     | μΑ       |

S14-2048-Rev. D, 13-Oct-14

Document Number: 63835

# **Vishay Siliconix**

|                                                                         |                        | TEST CONDITIONS UNLESS SPECIFIED                                                                                                                                                                                                                          |       |      |       |     |

|-------------------------------------------------------------------------|------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|------|-------|-----|

| PARAMETER                                                               | SYMBOL                 | $ \begin{aligned} V_{IN} &= 12 \ V, \ V_{DD} = 5 \ V, \ T_A = +25 \ ^\circ C \ \text{for typ.}, \\ -40 \ ^\circ C \ \text{to} +85 \ ^\circ C \ \text{for min. and max.}, \\ T_J &= < 125 \ ^\circ C, \ \text{typical application circuit} \end{aligned} $ | MIN.  | TYP. | MAX.  | UNI |

| Fault Protection                                                        |                        |                                                                                                                                                                                                                                                           |       |      |       |     |

| Valley Current Limit                                                    | 1                      | $V_{DD} = 5 \text{ V}, \text{ R}_{ILIM} = 3945, \text{ T}_{J} = 0 ^{\circ}\text{C} \text{ to } +125 ^{\circ}\text{C}$                                                                                                                                     | 12.75 | 15   | 17.25 | A   |

|                                                                         | I <sub>LIM</sub>       | V <sub>DD</sub> = 3.3 V, R <sub>ILIM</sub> = 3945                                                                                                                                                                                                         | -     | 13.5 | -     |     |

| I <sub>LIM</sub> Source Current                                         |                        |                                                                                                                                                                                                                                                           | -     | 10   | -     | μA  |

| I <sub>LIM</sub> Comparator Offset Voltage                              | V <sub>ILM-LK</sub>    | With respect to A <sub>GND</sub>                                                                                                                                                                                                                          | -10   | 0    | +10   | m\  |

| Output Under-Voltage Fault                                              | V <sub>OUV_Fault</sub> | V <sub>FB</sub> with respect to Internal 600 mV reference, 8 consecutive clocks                                                                                                                                                                           | -     | -25  | -     |     |

| Smart Power-Save Protection<br>Threshold Voltage <sup>b</sup>           | P <sub>Save_VTH</sub>  | $V_{FB}$ with respect to internal 600 mV                                                                                                                                                                                                                  | -     | +10  | -     | %   |

| Over-Voltage Protection Threshold                                       |                        | V <sub>FB</sub> with respect to internal 600 mV                                                                                                                                                                                                           | -     | +20  | -     | 1   |

| Over-Voltage Fault Delay <sup>b</sup>                                   | t <sub>OV-Delay</sub>  |                                                                                                                                                                                                                                                           | -     | 5    | -     | μs  |

| Over Temperature Shutdown <sup>b</sup>                                  | T <sub>Shut</sub>      | 10 °C hysteresis                                                                                                                                                                                                                                          | -     | 150  | -     | °C  |

| Logic Inputs/Outputs                                                    |                        | ·                                                                                                                                                                                                                                                         |       |      |       |     |

| Logic Input High Voltage                                                | V <sub>IH</sub>        |                                                                                                                                                                                                                                                           | 1     | -    | -     |     |

| Logic Input Low Voltage                                                 | V <sub>IL</sub>        |                                                                                                                                                                                                                                                           | -     | -    | 0.4   |     |

| EN/PSV Input for P-Save Operation <sup>b</sup>                          |                        | $V_{DD} = 5 V$                                                                                                                                                                                                                                            | 2.2   | -    | 5     | ν   |

| EN/PSV Input for Forced Continuous<br>Operation <sup>b</sup>            |                        |                                                                                                                                                                                                                                                           | 1     | -    | 2     |     |

| EN/PSV Input for Disabling Switcher                                     |                        |                                                                                                                                                                                                                                                           | 0     | -    | 0.4   |     |

| EN/PSV Input Bias Current                                               | I <sub>EN</sub>        |                                                                                                                                                                                                                                                           | -10   | -    | +10   |     |

| ENL Input Bias Current                                                  | I <sub>ENL</sub>       |                                                                                                                                                                                                                                                           | -     | 8    | 15    | μA  |

| FBL, FB Input Bias Current                                              | FBL_I <sub>LK</sub>    |                                                                                                                                                                                                                                                           | -1    | -    | +1    |     |

| Linear Dropout Regulator                                                |                        | ·                                                                                                                                                                                                                                                         |       |      |       |     |

| FBL <sup>b</sup>                                                        | V <sub>LDO ACC</sub>   |                                                                                                                                                                                                                                                           | -     | 0.75 | -     | V   |

|                                                                         |                        | Short-circuit protection, $V_{IN} = 12 \text{ V}, V_{DD} < 0.75 \text{ V}$                                                                                                                                                                                | -     | 65   | -     |     |

| LDO Current Limit                                                       | LDO_I <sub>LIM</sub>   | Start-up and foldback, V <sub>IN</sub> = 12 V, 0.75 < V <sub>DD</sub> < 90 % of final V <sub>DD</sub> value                                                                                                                                               | -     | 115  | -     | m/  |

|                                                                         |                        | $\label{eq:operating current limit, V_{IN} = 12 V,} \\ V_{DD} > 90 \ \% \ \text{of final } V_{DD} \ \text{value}$                                                                                                                                         | 135   | 200  | -     |     |

| V <sub>LDO</sub> to V <sub>OUT</sub> Switch-over Threshold <sup>d</sup> | V <sub>LDO-BPS</sub>   |                                                                                                                                                                                                                                                           | -130  | -    | +130  | -   |

| $V_{LDO}$ to $V_{OUT}$ Non-switch-over Threshold <sup>d</sup>           | V <sub>LDO-NBPS</sub>  |                                                                                                                                                                                                                                                           | -500  | -    | +500  | m'  |

| V <sub>LDO</sub> to V <sub>OUT</sub> Switch-over Resistance             | R <sub>LDO</sub>       | V <sub>OUT</sub> = 5 V                                                                                                                                                                                                                                    | -     | 2    | -     | Ω   |

| LDO Drop Out Voltage <sup>e</sup>                                       |                        | From $V_{IN}$ to $V_{DD}$ ,<br>$V_{DD} = +5 V$ , $I_{VLDO} = 100 mA$                                                                                                                                                                                      | _     | 1.2  | -     | v   |

Notes

a. VIN UVLO is programmable using a resistor divider from VIN to ENL to AGND. The ENL voltage is compared to an internal reference.

b. Typical value measured on standard evaluation board.

c. SiC401A/B has first order temperature compensation for over current. Results vary based upon the PCB thermal layout

d. The switch-over threshold is the maximum voltage differential between the  $V_{LDO}$  and  $V_{OUT}$  pins which ensures that  $V_{LDO}$  will internally switch-over to  $V_{OUT}$ . The non-switch-over threshold is the minimum voltage differential between the  $V_{LDO}$  and  $V_{OUT}$  pins which ensures that  $V_{LDO}$  will not switch-over to  $V_{OUT}$ .

e. The LDO drop out voltage is the voltage at which the LDO output drops 2 % below the nominal regulation point.

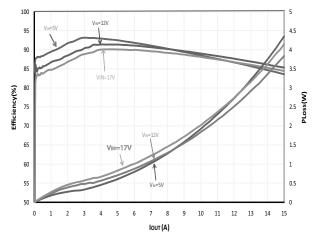

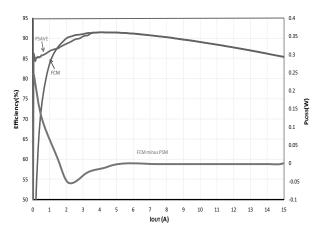

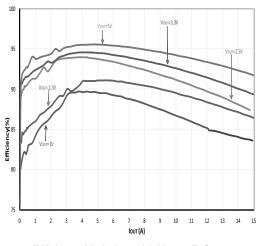

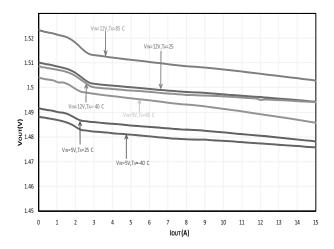

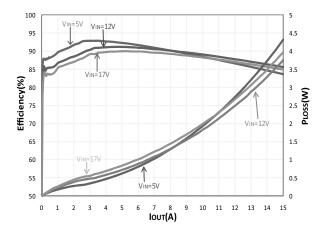

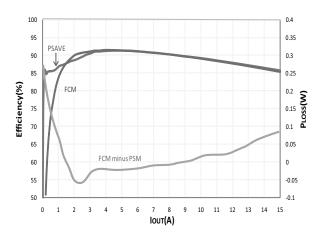

Efficiency/Power Loss vs. Load P-Save (V<sub>DD</sub> = 3.3 V, V<sub>OUT</sub> = 1.5 V, SiC401B)

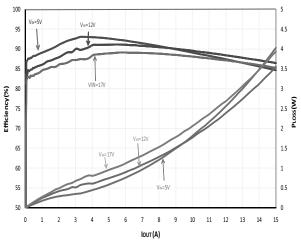

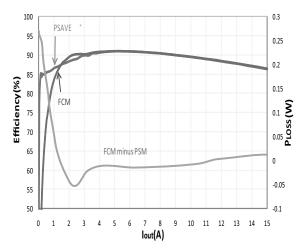

Efficiency/Power Loss-P-Save vs. FCM  $(V_{DD} = 3.3 V, V_{OUT} = 1.5 V, V_{IN} = 12 V, SiC401B)$

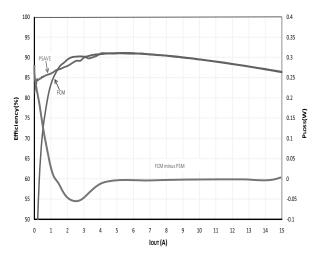

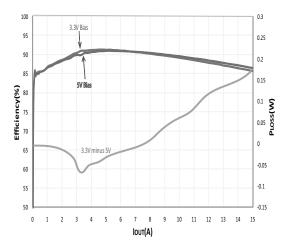

Efficiency/Power Loss-P-Save vs. FCM  $(V_{DD} = 5 V, V_{OUT} = 1.5 V, V_{IN} = 12 V, SiC401B)$

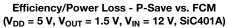

(V<sub>OUT</sub> = 1.5 V, V<sub>IN</sub> = 12 V, SiC401B)

S14-2048-Rev. D, 13-Oct-14

7

Document Number: 63835

SiC401A, SiC401BCD

**Vishay Siliconix**

SiC401A, SiC401BCD Vishay Siliconix

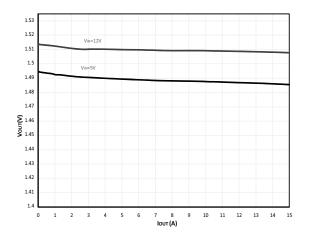

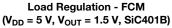

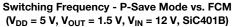

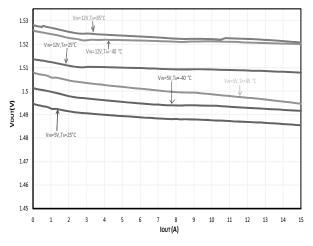

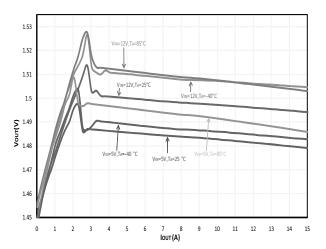

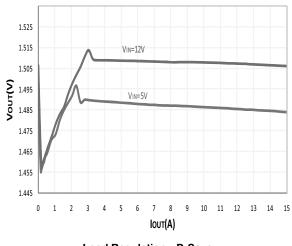

Load Regulation - FCM ( $V_{DD}$  = 3.3 V,  $V_{OUT}$  = 1.5 V, SiC401B)

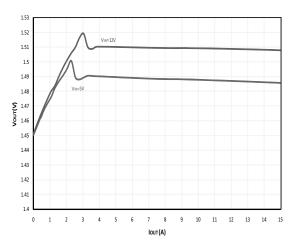

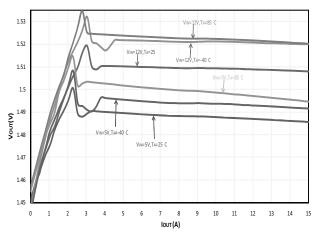

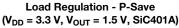

Load Regulation - P-Save  $(V_{DD} = 3.3 \text{ V}, V_{OUT} = 1.5 \text{ V}, \text{SiC401B})$

Document Number: 63835

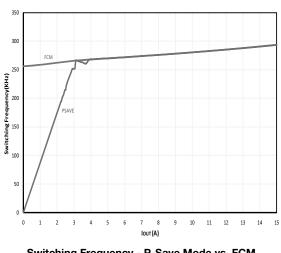

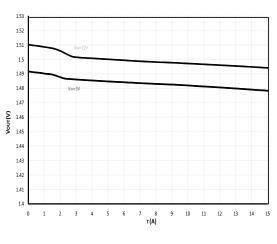

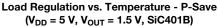

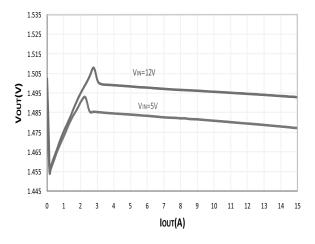

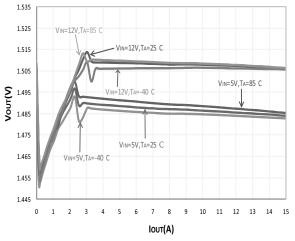

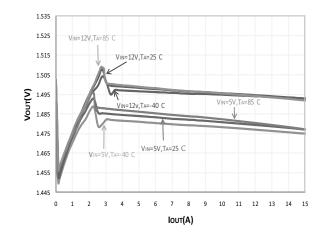

Load Regulation vs. Temperature - FCM ( $V_{DD}$  = 5 V,  $V_{OU}$ T = 1.5 V, SiC401B)

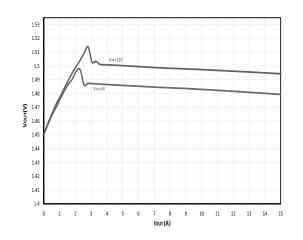

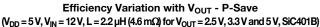

Load Regulation vs. Temperature - P-Save  $(V_{DD} = 3.3 V, V_{OUT} = 1.5 V, SiC401B)$

Load Regulation vs. Temperature - FCM (V<sub>DD</sub> = 3.3 V, V<sub>OUT</sub> = 1.5 V, SiC401B)

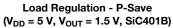

$(V_{OUT} = 1.5 V, V_{IN} = 12 V, SiC401B)$

S14-2048-Rev. D, 13-Oct-14

9 lestions contact: powerictechsuppo Document Number: 63835

SiC401A, SiC401BCD

Vishay Siliconix

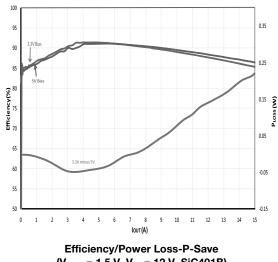

Efficiency/Power Loss vs. Load - P-Save (V<sub>DD</sub> = 3.3 V, V<sub>OUT</sub> = 1.5 V, SiC401A)

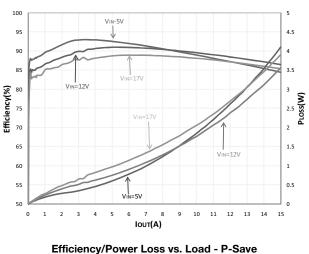

fficiency/Power Loss vs. Load - P-Save (V<sub>DD</sub> = 5 V, V<sub>OUT</sub> = 1.5 V, SiC401A)

Efficiency/Power Loss - P-Save vs. FCM ( $V_{DD}$  = 3.3 V,  $V_{OUT}$  = 1.5 V,  $V_{IN}$  = 12 V, SiC401A)

Efficiency/Power Loss - P-Save (V<sub>OUT</sub> = 1.5 V, V<sub>IN</sub> = 12 V, SiC401A)

Load Regulation - P-Save ( $V_{DD} = 5 V$ ,  $V_{OUT} = 1.5 V$ , SiC401A)

S14-2048-Rev. D, 13-Oct-14

Document Number: 63835

For technical questions, contact: <u>powerictechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

# SiC401A, SiC401BCD

**Vishay Siliconix**

Load Regulation vs. Temperature - P-Save  $(V_{DD} = 5 V, V_{OUT} = 1.5 V, SiC401A)$

S14-2048-Rev. D, 13-Oct-14

11

Document Number: 63835

For technical questions, contact: <u>powerictechsupport@vishay.com</u> THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT <u>www.vishay.com/doc?91000</u>

# SiC401A, SiC401BCD

Vishay Siliconix

**Vishay Siliconix**

## **ELECTRICAL CHARACTERISTICS**

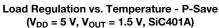

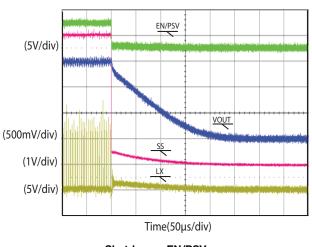

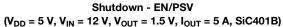

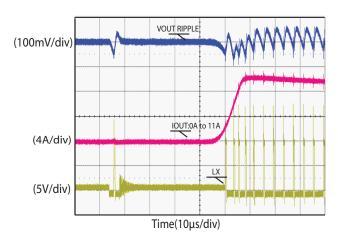

$\label{eq:start-up} \begin{array}{l} \mbox{Start-up (Pre-Bias) - EN/PSV} \\ \mbox{(V_{DD} = 5 V, V_{IN} = 12 V, V_{OUT} = 1.5 V, I_{OUT} = 0 A, SiC401B)} \end{array}$

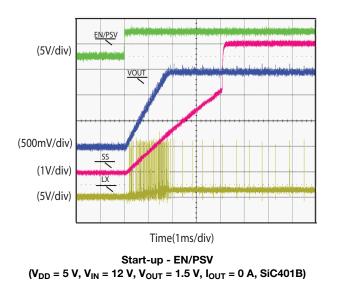

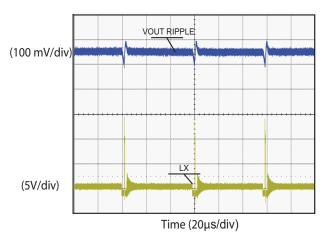

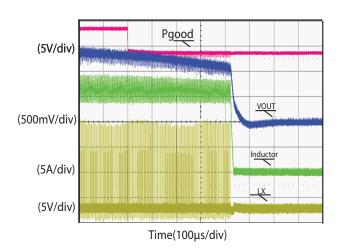

$\label{eq:vdv} \begin{array}{l} Power-Save \mbox{ Mode} \\ (V_{DD}=5 \mbox{ V}, \mbox{ V}_{IN}=12 \mbox{ V}, \mbox{ V}_{OUT}=1.5 \mbox{ V}, \mbox{ I}_{OUT}=0 \mbox{ A}, \mbox{ SiC401A}) \end{array}$

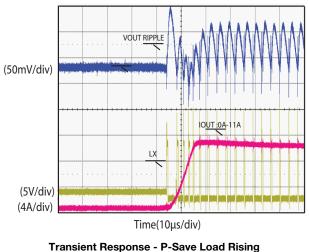

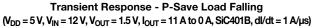

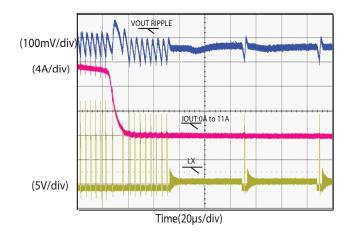

$(V_{DD} = 5 V, V_{IN} = 12 V, V_{OUT} = 1.5 V, I_{OUT} = 0 A to 11 A, SiC401B, dI/dt = 1 A/\mu s)$

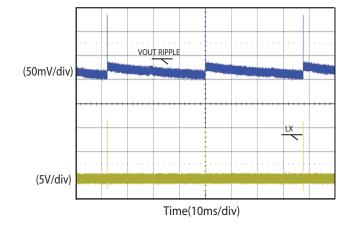

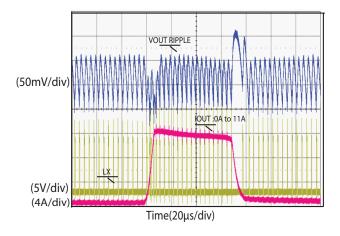

$\label{eq:VDD} \begin{array}{l} Power-Save \mbox{ Mode} \\ (\mbox{V}_{DD}=5\mbox{ V},\mbox{ V}_{IN}=12\mbox{ V},\mbox{ V}_{OUT}=1.5\mbox{ V},\mbox{ I}_{OUT}=0\mbox{ A},\mbox{ SiC401B}) \end{array}$

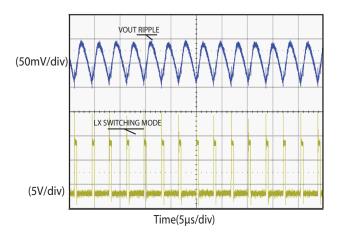

Forced Continuous Mode ( $V_{DD}$  = 5 V,  $V_{IN}$  = 12 V,  $V_{OUT}$  = 1.5 V,  $I_{OUT}$  = 15 A, SiC401B)

S14-2048-Rev. D, 13-Oct-14

12 ns. contact: powerictechs Document Number: 63835

**Vishay Siliconix**

## **ELECTRICAL CHARACTERISTICS**

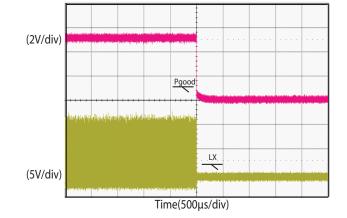

Over Temperature Shutdown at 133.4  $^\circ C$  (V<sub>IN</sub> = 12 V, V<sub>OUT</sub> = 1.5 V, I<sub>OUT</sub> = 0 A, LDO Mode, SiC401B)

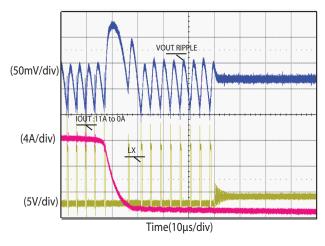

$\label{eq:transient} \begin{array}{l} Transient \ Response \ - \ P-Save \ Load \ Falling \\ (V_{DD}=5 \ V, \ V_{IN}=12 \ V, \ V_{OUT}=1.5 \ V, \ I_{OUT}=11 \ A \ to \ 0 \ A, \ SiC401A, \ dl/dt=1 \ A/\mu s) \end{array}$

$\label{eq:VDD} Transient \ Response \ - \ FCM \\ (V_{DD} = 5 \ V, \ V_{IN} = 12 \ V, \ V_{OUT} = 1.5 \ V, \ I_{OUT} = 0 \ A \ to \ 11 \ A, \ SiC401B, \ dl/dt = 1 \ A/\mu s) \\$

Transient Response - P-Save Load Rising ( $V_{DD}$  = 5 V,  $V_{IN}$  = 12 V,  $V_{OUT}$  = 1.5 V,  $I_{OUT}$  = 0 A to 11 A, SiC401A, dl/dt = 1 A/µs)

Over Current Protection-Under Voltage Prodection ( $V_{DD} = 5 V, V_{IN} = 12 V, V_{OUT} = 1.5 V, SiC401B$ )

S14-2048-Rev. D, 13-Oct-14

13

### **OPERATIONAL DESCRIPTION**

#### **Device Overview**

The SiC401A/B is a step down synchronous DC/DC buck converter with integrated power MOSFETs and a 200 mA capable programmable LDO. The device is capable of 15 A operation at very high efficiency. A space saving 5 mm x 5 mm 32-pin package is used. The programmable operating frequency of up to 1 MHz enables optimizing the configuration for PCB area and efficiency.

The buck controller uses a pseudo-fixed frequency adaptive on-time control. This control method allows fast transient response which permits the use of smaller output capacitors.

#### **Input Voltage Requirements**

The SiC401A/B requires two input supplies for normal operation:  $V_{IN}$  and  $V_{DD}$ .  $V_{IN}$  operates over a wide range from 3 V to 17 V.  $V_{DD}$  requires a 3 V to 5.5 V supply input that can be an external source or the internal LDO configured to supply 3 V to 5.5 V from  $V_{IN}$ .

#### **Power Up Sequence**

When the SiC401A/B uses an external power source at the  $V_{DD}$  pin, the switching regulator initiates the start up when  $V_{IN}$ ,  $V_{DD}$ , and EN/PSV are above their respective thresholds. When EN/PSV is at logic high,  $V_{DD}$  needs to be applied after  $V_{IN}$  rises. It is also recommended to use a 10  $\Omega$  resistor between an external power source and the  $V_{DD}$  pin. To start up by using the EN/PSV pin when both  $V_{DD}$  and  $V_{IN}$  are above their respective thresholds, apply EN/PSV to enable the start-up process. For SiC401A/B in self-biased mode, refer to the LDO section for a full description.

#### Shutdown

The SiC401A/B can be shut-down by pulling either V<sub>DD</sub> or EN/PSV below its threshold. When using an external power source, it is recommended that the V<sub>DD</sub> voltage ramps down before the V<sub>IN</sub> voltage. When V<sub>DD</sub> is active and EN/PSV at logic low, the output voltage discharges into the V<sub>OUT</sub> pin through an internal FET.

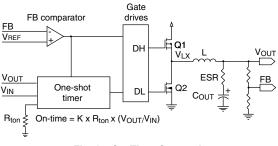

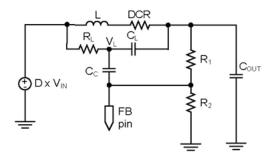

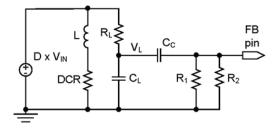

#### **Pseudo-Fixed Frequency Adaptive On-Time Control**

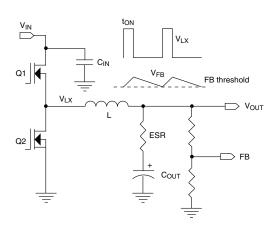

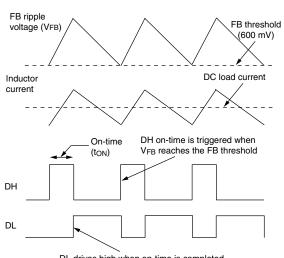

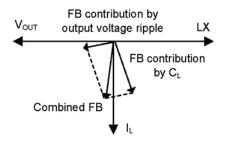

The PWM control method used by the SiC401A/B is pseudo- fixed frequency, adaptive on-time, as shown in figure 1. The ripple voltage generated at the output capacitor ESR is used as a PWM ramp signal. This ripple is used to trigger the on-time of the controller.

#### Fig. 1 - Output Ripple and PWM Control Method

The adaptive on-time is determined by an internal one- shot timer. When the one-shot is triggered by the output ripple, the device sends a single on-time pulse to the high- side MOSFET. The pulse period is determined by  $V_{OUT}$  and  $V_{IN}$ ; the period is proportional to output voltage and inversely proportional to input voltage. With this adaptive on-time arrangement, the device automatically anticipates the on-time needed to regulate  $V_{OUT}$  for the present  $V_{IN}$  condition and at the selected frequency.

The advantages of adaptive on-time control are:

- Predictable operating frequency compared to other variable frequency methods.

- Reduced component count by eliminating the error amplifier and compensation components.

- Reduced component count by removing the need to sense and control inductor current.

- Fast transient response the response time is controlled by a fast comparator instead of a typically slow error amplifier.

- Reduced output capacitance due to fast transient response.

#### **One-Shot Timer and Operating Frequency**

The one-shot timer operates as shown in figure 2. The FB comparator output goes high when  $V_{FB}$  is less than the internal 600 mV reference. This feeds into the gate drive and turns on the high-side MOSFET, and also starts the one-shot timer. The one-shot timer uses an internal comparator and a capacitor. One comparator input is connected to  $V_{OUT}$ , the other input is connected to the capacitor. When the on-time begins, the internal capacitor charges from zero volts through a current which is proportional to  $V_{IN}$ . When the capacitor voltage reaches  $V_{OUT}$ , the on-time is completed and the high-side MOSFET turns off.

14

SiC401A, SiC401BCD

**Vishay Siliconix**

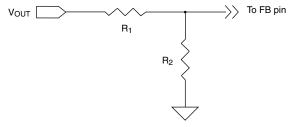

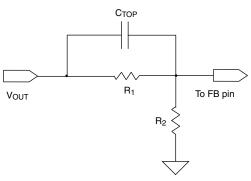

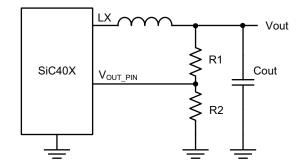

Note that this control method regulates the valley of the output ripple voltage, not the DC value. The DC output

voltage V<sub>OUT</sub> is offset by the output ripple according to the

$V_{OUT} = 0.6 \text{ x} \left( 1 + \frac{R_1}{R_2} \right) + \left( \frac{V_{RIPPLE}}{2} \right)$

When a large capacitor is placed in parallel with R1 (C<sub>TOP</sub>)

$V_{OUT} = 0.6 x \left( 1 + \frac{R_1}{R_2} \right) + \left( \frac{V_{RIPPLE}}{2} \right) x \sqrt{\frac{1 + (R_1 \omega C_{TOP})^2}{1 + \left( \frac{R_2 x R_1}{R_2 + R_1} \omega C_{TOP} \right)^2}}$

The EN/PSV input is used to enable or disable the switching regulator. When EN/PSV is low (grounded), the switching regulator is off and in its lowest power state. When off, the output of the switching regulator soft-discharges the output

into a 15  $\Omega$  internal resistor via the V<sub>OUT</sub> pin. When EN/PSV

is allowed to float, the pin voltage will float to 33 % of the

voltage at V<sub>DD</sub>. The switching regulator turns on with

power-save disabled and all switching is in forced

When EN/PSV is high (above 44 % of the voltage at  $V_{DD}$ ), the switching regulator turns on with power-save enabled. The SiC401A/B P-Save operation reduces the switching frequency according to the load for increased efficiency at

The SiC401A/B operates the switcher in FCM (Forced Continuous Mode) by floating the EN/PSV pin (see figure 4). In this mode one of the power MOSFETs is always on, with

cross-conduction. This feature results in uniform frequency across the full load range with the trade-off being poor efficiency at light loads due to the high-frequency switching of the MOSFETs. DH is gate signal to drive upper MOSFET.

DL is lower gate signal to drive lower MOSFET.

intentional dead time other than to avoid

V<sub>OUT</sub> is shown by the following equation.

Enable and Power-Save Inputs

continuous mode.

light load conditions.

no

**Forced Continuous Mode Operation**

following equation.

## Vishay Siliconix

www.vishay.com

Fig. 2 - On-Time Generation

This method automatically produces an on-time that is proportional to  $V_{OUT}$  and inversely proportional to  $V_{IN}$ . Under steady-state conditions, the switching frequency can be determined from the on-time by the following equation.

$$f_{SW} = \frac{V_{OUT}}{t_{ON} \times V_{IN}}$$

The SiC401A/B uses an external resistor to set the on-time which indirectly sets the frequency. The on-time can be programmed to provide operating frequency up to 1 MHz using a resistor between the  $t_{\rm ON}$  pin and ground. The resistor value is selected by the following equation.

$$R_{ton} = \frac{k}{25 \text{ pF x f}_{SW}}$$

The constant, k, equals 1, when  $V_{DD}$  is greater than 3.6 V. If  $V_{DD}$  is less than 3.6 V and  $V_{IN}$  is greater than ( $V_{DD}$  -1.75) x 10, k is shown by the following equation.

$$k = \frac{(V_{DD} - 1.75) \times 10}{V_{IN}}$$

The maximum  $\mathrm{R}_{\mathrm{tON}}$  value allowed is shown by the following equation.

$$R_{ton\_MAX} = \frac{V_{IN\_MIN}}{15 \ \mu A}$$

#### V<sub>OUT</sub> Voltage Selection

The switcher output voltage is regulated by comparing  $V_{OUT}$  as seen through a resistor divider at the FB pin to the internal 600 mV reference voltage, see figure 3.

Fig. 3 - Output Voltage Selection

S14-2048-Rev. D, 13-Oct-14

15

# **Vishay Siliconix**

www.vishay.com

DL drives high when on-time is completed. DL remains high until  $V_{FB}$  falls to the FB threshold.

#### Fig. 4 - Forced Continuous Mode Operation

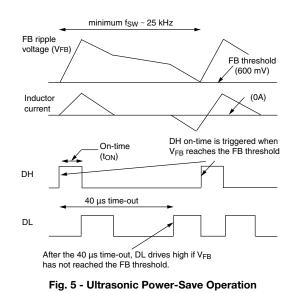

#### Ultrasonic Power-Save Operation (SiC401A)

The SiC401A provides ultrasonic power-save operation at light loads, with the minimum operating frequency fixed at slightly under 25 kHz. This is accomplished by using an internal timer that monitors the time between consecutive high-side gate pulses. If the time exceeds 40  $\mu$ s, DL drives high to turn the low-side MOSFET on. This draws current from V<sub>OUT</sub> through the inductor, forcing both V<sub>OUT</sub> and V<sub>FB</sub> to fall. When V<sub>FB</sub> drops to the 600 mV threshold, the next DH (the drive signal for the high side FET) on-time is triggered. After the on-time is completed, the high-side MOSFET is turned off and the low-side MOSFET turns on. The low-side MOSFET remains on until the inductor current ramps down to zero, at which point the low-side MOSFET is turned off.

Because the on-times are forced to occur at intervals no greater than 40  $\mu$ s, the frequency will not fall far below 25 kHz. Figure 5 shows ultrasonic power-save operation.

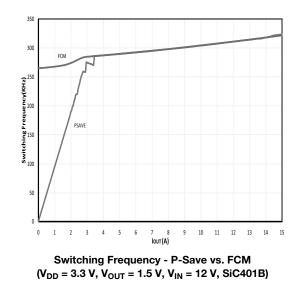

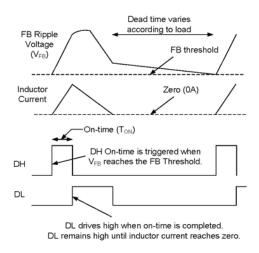

#### Power-Save Operation (SiC401B)

The SiC401B provides power-save operation at light loads with no minimum operating frequency. With power-save enabled, the internal zero crossing comparator monitors the inductor current via the voltage across the low-side MOSFET during the off-time. If the inductor current falls to zero for eight consecutive switching cycles, the controller enters MOSFET on each subsequent cycle provided that the power-save operation. It will turn off the low-side MOSFET on each subsequent cycle provided that the current crosses zero. At this time both MOSFETs remain off until V<sub>FB</sub> drops to the 600 mV threshold. Because the MOSFETs are off, the load is supplied by the output capacitor.

If the inductor current does not reach zero on any switching cycle, the controller immediately exits power-save and returns to forced continuous mode.

Figure 6 shows power-save operation at light loads.

#### Fig. 6 - Power-Save Mode

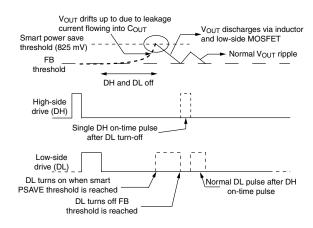

#### **Smart Power-Save Protection**

Active loads may leak current from a higher voltage into the switcher output. Under light load conditions with power-save enabled, this can force V<sub>OUT</sub> to slowly rise and reach the over-voltage threshold, resulting in a hard shut-down. Smart power-save prevents this condition. When the FB voltage exceeds 10 % above nominal, the device immediately disables power-save, and DL drives high to turn on the low-side MOSFET. This draws current from V<sub>OUT</sub> through the inductor and causes V<sub>OUT</sub> to fall. When V<sub>FB</sub> drops back to the 600 mV trip point, a normal t<sub>ON</sub> switching cycle begins. This method prevents a hard OVP shut-down and also cycles energy from V<sub>OUT</sub> back to V<sub>IN</sub>. It also minimizes operating power by avoiding forced conduction mode operation. Figure 7 shows typical waveforms for the Smart Power Save feature.

S14-2048-Rev. D, 13-Oct-14

16

Fig. 7 - Smart Power-Save

#### SmartDrive<sup>™</sup>

For each DH pulse, the DH driver initially turns on the high side MOSFET at a lower speed, allowing a softer, smooth turn-off of the low-side diode. Once the diode is off and the LX voltage has risen 0.5 V above PGND, the SmartDrive circuit automatically drives the high-side MOSFET on at a rapid rate. This technique reduces switching losses while maintaining high efficiency and also avoids the need for snubbers for the power MOSFETs.

#### **Current Limit Protection**

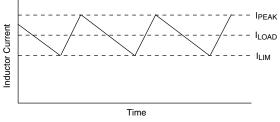

The device features programmable current limiting, which is accomplished by using the R<sub>DS-ON</sub> of the lower MOSFET for current sensing. The current limit is set by RILIM resistor. The  $R_{\text{ILIM}}$  resistor connects from the  $I_{\text{LIM}}$  pin to the LXS pin which is also the drain of the low-side MOSFET. When the low-side MOSFET is on, an internal ~ 10  $\mu$ A current flows from the I<sub>LIM</sub> pin and through the RILIM resistor, creating a voltage drop across the resistor. While the low-side MOSFET is on, the inductor current flows through it and creates a voltage across the R<sub>DS-ON</sub>. The voltage across the MOSFET is negative with respect to ground. If this MOSFET voltage drop exceeds the voltage across  $R_{ILIM}$ , the voltage at the  $I_{LIM}$ pin will be negative and current limit will activate. The current limit then keeps the low-side MOSFET on and will not allow another high-side on-time, until the current in the low-side MOSFET reduces enough to bring the ILIM voltage back up to zero. This method regulates the inductor valley current at the level shown by ILIM in figure 8.

Fig. 8 - Valley Current Limit

# **Vishay Siliconix**

Setting the valley current limit to 15 A results in a peak inductor current of 15 A plus peak ripple current. In this situation, the average (load) current through the inductor is 15 A plus one-half the peak-to-peak ripple current.

The internal 10 uA current source is temperature compensated at 4100 ppm in order to provide tracking with the R<sub>DS-ON</sub>.

The R<sub>ILIM</sub> value is calculated by the following equation.

$R_{ILIM} = 263 \times I_{LIM} \times [0.112 \times (5 \text{ V} - \text{V}_{DD}) + 1]$

When selecting a value for R<sub>IIIM</sub> be sure not to exceed the absolute maximum voltage value for the ILIM pin. Note that because the low-side MOSFET with low R<sub>DS-ON</sub> is used for current sensing, the PCB layout, solder connections, and PCB connection to the LX node must be done carefully to obtain good results. RILIM should be connected directly to LXS (pin 28).

#### Soft-Start of PWM Regulator

SiC401A/B has a programmable soft-start time that is controlled by an external capacitor at the SS pin. After the controller meets both UVLO and EN/PSV thresholds, the controller has an internal current source of 3 µA flowing through the SS pin to charge the capacitor. During the start up process (figure 9), 50 % of the voltage at the SS pin is used as the reference for the FB comparator. The PWM comparator issues an on-time pulse when the voltage at the FB pin is less than 40 % of the SS pin. As a result, the output voltage follows the SS voltage. The output voltage reaches and maintains regulation when the soft start voltage is  $\geq$  1.5 V. The time between the first LX pulse and V<sub>OUT</sub> reaching regulation is the soft-start time (t<sub>SS</sub>). The calculation for the soft-start time is shown by the following equation.

$$t_{SS} = C_{SS} \times \frac{1.5 \text{ V}}{3 \mu \text{A}}$$

The voltage at the SS pin continues to ramp up and eventually equals 64 % of V<sub>DD</sub>. After the soft start completes, the FB pin voltage is compared to an internal reference of 0.6 V. The delay time between the V<sub>OUT</sub> regulation point and P<sub>GOOD</sub> going high is shown by the following equation.

$$t_{PGOOD-DELAY} = \frac{C_{SS} \times (0.64 \times V_{DD} - 1.5 \text{ V})}{3 \,\mu\text{A}}$$

S14-2048-Rev. D, 13-Oct-14

17

Document Number: 63835

Fig. 9 - Soft-Start Timing Diagram

### Pre-Bias Start-Up

The SiC401A/B can start up normally even when there is an existing output voltage present. The soft start time is still the same as normal start up (when the output voltage starts from zero). The output voltage starts to ramp up when 40 % of the voltage at SS pin meets the existing FB voltage level. Pre-bias startup is achieved by turning off the lower gate when the inductor current falls below zero. This method prevents the output voltage from discharging.

### **Power Good Output**

The  $P_{GOOD}$  (power good) output is an open-drain output which requires a pull-up resistor. When the voltage at the FB pin is 10 % below the nominal voltage,  $P_{GOOD}$  is pulled low. It is held low until the output voltage returns above -8 % of nominal.

$\mathsf{P}_{GOOD}$  will transition low if the  $\mathsf{V}_{FB}$  pin exceeds +20 % of nominal, which is also the over-voltage shutdown threshold.  $\mathsf{P}_{GOOD}$  also pulls low if the EN/PSV pin is low when  $\mathsf{V}_{DD}$  is present.

### **Output Over-Voltage Protection**

Over-voltage protection becomes active as soon as the device is enabled. The threshold is set at 600 mV +20 % (720 mV). When V<sub>FB</sub> exceeds the OVP threshold, DL latches high and the low-side MOSFET is turned on. DL remains high and the controller remains off, until the EN/PSV input is toggled or V<sub>DD</sub> is cycled. There is a 5  $\mu$ s delay built into the OVP detector to prevent false transitions. P<sub>GOOD</sub> is also low after an OVP event.

### **Output Under-Voltage Protection**

When  $V_{FB}$  falls 25 % below its nominal voltage (falls to 450 mV) for eight consecutive clock cycles, the switcher is shut off and the DH and DL drives are pulled low to tristate the MOSFETs. The controller stays off until EN/PSV is toggled or  $V_{DD}$  is cycled.

# V<sub>DD</sub> UVLO, and POR

UVLO (Under-Voltage Lock-Out) circuitry inhibits switching and tri-states the DH/DL drivers until V<sub>DD</sub> rises above 3 V. An internal POR (Power-On Reset) occurs when V<sub>DD</sub> exceeds 3 V, which resets the fault latch and a soft-start counter cycle begins which prepares for soft-start. The SiC401A/B then begins a soft-start cycle. The PWM will shut off if V<sub>DD</sub> falls below 2.4 V.

### LDO Regulator

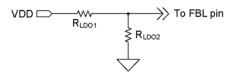

SiC401A/B has an option to bias the switcher by using an internal LDO from V<sub>IN</sub>. The LDO output is connected to V<sub>DD</sub> internally. The output of the LDO is programmable by using external resistors from the V<sub>DD</sub> pin to A<sub>GND</sub> (see figure 10). The feedback pin (FBL) for the LDO is regulated to 750 mV.

Fig. 10 - LDO Output Voltage Selection The LDO output voltage is set by the following equation.

$$V_{LDO} = 750 \text{ mV x} \left(1 + \frac{R_{LDO1}}{R_{LDO2}}\right)$$

A minimum capacitance of 1  $\mu$ F referenced to A<sub>GND</sub> is normally required at the output of the LDO for stability.

Note that if the LDO voltage is set lower than 4.5 V, the minimum output capacitance for the LDO is 10  $\mu F.$

### LDO ENL Functions

The ENL input is used to enable/disable the internal LDO. When ENL is a logic low, the LDO is off. When ENL is above the  $V_{\rm IN}$  UVLO threshold, the LDO is enabled and the switcher is also enabled if the EN/PSV and  $V_{\rm DD}$  are above their threshold. The table below summarizes the function of ENL and EN/PSV pins.

| EN/PSV   | ENL                | LDO | SWITCHER |

|----------|--------------------|-----|----------|

| Disabled | Low, < 0.4 V       | Off | Off      |

| Enabled  | Low, < 0.4 V       | Off | On       |

| Disabled | 1 V < High < 2.6 V | On  | Off      |

| Enabled  | 1 V < High < 2.6 V | On  | Off      |

| Disabled | High, > 2.6 V      | On  | Off      |

| Enabled  | High, > 2.6 V      | On  | On       |

The ENL pin also acts as the switcher under-voltage lockout for the V<sub>IN</sub> supply. When SiC401A/B is self-biased from the LDO and runs from the V<sub>IN</sub> power source only, the V<sub>IN</sub> UVLO feature can be used to prevent false UV faults for the PWM output by programming with a resistor divider at the V<sub>IN</sub>, ENL and A<sub>GND</sub> pins. When SiC401A/B has an external bias voltage at V<sub>DD</sub> and the ENL pin is used to program the V<sub>IN</sub>

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

UVLO feature, the voltage at FBL needs to be higher than 750 mV to force the LDO off.

www.vishay.com

Timing is important when driving ENL with logic and not implementing V<sub>IN</sub> UVLO. The ENL pin must transition from high to low within 2 switching cycles to avoid the PWM output turning off. If ENL goes below the V<sub>IN</sub> UVLO threshold and stays above 1 V, then the switcher will turn off but the LDO will remain on.

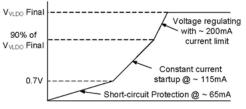

#### LDO Start-Up

Before start-up, the LDO checks the status of the following signals to ensure proper operation can be maintained.

- 1. ENL pin

- 2. V<sub>LDO</sub> output

When the ENL pin is high and  $V_{\mbox{\scriptsize IN}}$  is above the UVLO point, the LDO will begin start-up. During the initial phase, when the V<sub>DD</sub> voltage (which is the LDO output voltage) is less than 0.75 V, the LDO initiates a current-limited start-up (typically 65 mA) to charge the output capacitors while protecting from a short circuit event. When  $V_{DD}$  is greater than 0.75 V but still less than 90 % of its final value (as sensed at the FBL pin), the LDO current limit is increased to ~115 mA. When  $V_{DD}$  has reached 90 % of the final value (as sensed at the FBL pin), the LDO current limit is increased to ~200 mA and the LDO output is quickly driven to the nominal value by the internal LDO regulator. It is recommended that during LDO start-up to hold the PWM switching off until the LDO has reached 90 % of the final value. This prevents overloading the current-limited LDO output during the LDO start-up.

Due to the initial current limitations on the LDO during power up (figure 11), any external load attached to the  $V_{DD}$  pin must be limited to less than the start up current before the LDO has reached 90 % of its final regulation value.

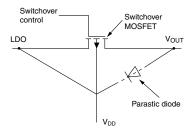

#### LDO Switch-Over Operation

The SiC401A/B includes a switch-over function for the LDO. The switch-over function is designed to increase efficiency by using the more efficient DC/DC converter to power the LDO output, avoiding the less efficient LDO regulator when possible. The switch-over function connects the V<sub>DD</sub> pin directly to the V<sub>OUT</sub> pin using an internal switch. When the switch-over is complete the LDO is turned off, which results in a power savings and maximizes efficiency. If the LDO output is used to bias the SiC401A/B, then after switch-over the device is self-powered from the switching regulator with the LDO turned off.

The switch-over starts 32 switching cycles after P<sub>GOOD</sub>

# Vishay Siliconix

output goes high. The voltages at the V<sub>DD</sub> and V<sub>OUT</sub> pins are then compared; if the two voltages are within  $\pm$  300 mV of each other, the V<sub>DD</sub> pin connects to the V<sub>OUT</sub> pin using an internal switch, and the LDO is turned off. To avoid unwanted switch-over, the minimum difference between the voltages for V<sub>OUT</sub> and V<sub>DD</sub> should be  $\pm$  500 mV.

It is not recommended to use the switch-over feature for an output voltage less than  $V_{\text{DD}}$  UVLO threshold since the SiC401A/B is not operational below that threshold.

#### Switch-Over MOSFET Parasitic Diodes

The switch-over MOSFET contains parasitic diodes that are inherent to its construction, as shown in figure 12. If the voltage at the V<sub>OUT</sub> pin is higher than V<sub>DD</sub>, then the respective diode will turn on and the current will flow through this diode. This has the potential of damaging the device. Therefore, V<sub>OUT</sub> must be less than V<sub>DD</sub> to prevent damaging the device.

Fig. 12 - Switch-Over MOSFET Parasitic Diodes

### **Design Procedure**

When designing a switch mode supply the input voltage range, load current, switching frequency, and inductor ripple current must be specified.

The maximum input voltage (V<sub>IN max</sub>) is the highest specified input voltage. The minimum input voltage (V<sub>IN min</sub>) is determined by the lowest input voltage after evaluating the voltage drops due to connectors, fuses, switches, and PCB traces.

The following parameters define the design:

- Nominal output voltage (V<sub>OUT</sub>)

- Static or DC output tolerance

- Transient response

- Maximum load current (I<sub>OUT</sub>)

There are two values of load current to evaluate - continuous load current and peak load current. Continuous load current relates to thermal stresses which drive the selection of the inductor and input capacitors. Peak load current determines instantaneous component stresses and filtering requirements such as inductor saturation, output capacitors, and design of the current limit circuit.

The following values are used in this design:

- $V_{IN} = 12 V \pm 10 \%$

- $V_{OUT} = 1.5 V \pm 4 \%$

- f<sub>SW</sub> = 300 kHz

- Load = 15 A max.

THIS DOCUMENT IS SUBJECT TO CHANGE WITHOUT NOTICE. THE PRODUCTS DESCRIBED HEREIN AND THIS DOCUMENT ARE SUBJECT TO SPECIFIC DISCLAIMERS, SET FORTH AT www.vishav.com/doc?91000

# **Vishay Siliconix**

#### **Frequency Selection**

Selection of the switching frequency requires making a trade-off between the size and cost of the external filter components (inductor and output capacitor) and the power conversion efficiency.

The desired switching frequency is 300 kHz which results from using component selected for optimum size and cost.

A resistor ( $R_{tON}$ ) is used to program the on-time (indirectly setting the frequency) using the following equation.

$$R_{ton} = \frac{k}{25 \text{ pF x f}_{SW}}$$

To select  $R_{tON},$  use the maximum value for  $V_{IN},$  and for  $t_{ON}$  use the value associated with maximum  $V_{IN}.$

$$t_{ON} = \frac{V_{OUT}}{V_{INmax.} x f_{SW}}$$

Substituting for  $R_{tON}$  results in the following solution.

$R_{tON} = 133.3 \text{ kW}$ , use  $R_{tON} = 130 \text{ kW}$ .

#### Inductor Selection

In order to determine the inductance, the ripple current must first be defined. Low inductor values result in smaller size but create higher ripple current which can reduce efficiency. Higher inductor values will reduce the ripple current/voltage and for a given DC resistance are more efficient. However, larger inductance translates directly into larger packages and higher cost. Cost, size, output ripple, and efficiency are all used in the selection process.

The ripple current will also set the boundary for  $\mathsf{P}_{Save}$  operation. The switching will typically enter  $\mathsf{P}_{Save}$  mode when the load current decreases to 1/2 of the ripple current. For example, if ripple current is 4 A then  $\mathsf{P}_{Save}$  operation will typically start for loads less than 2 A. If ripple current is set at 40 % of maximum load current, then  $\mathsf{P}_{Save}$  will start for loads less than 20 % of maximum current.

The inductor value is typically selected to provide a ripple current that is between 25 % to 50 % of the maximum load current. This provides an optimal trade-off between cost, efficiency, and transient performance.

During the on-time, voltage across the inductor is (V\_{IN} - V\_{OUT}). The equation for determining inductance is shown next.

$$L = \frac{(V_{IN} - V_{OUT}) \times t_{ON}}{I_{RIPPLE}}$$

#### Example

In this example, the inductor ripple current is set equal to 30 % of the maximum load current. Thus ripple current will be 30 % x 15 A or 4.5 A. To find the minimum inductance needed, use the  $V_{\rm IN}$  and  $t_{\rm ON}$  values that correspond to  $V_{\rm INmax}.$

$$L = \frac{(13.2 - 1.5) \text{ x } 379 \text{ ns}}{4.5 \text{ A}} = 0.99 \text{ } \mu\text{H}$$

A slightly larger value of 1  $\mu H$  is selected. This will decrease the maximum  $I_{\text{RIPPLE}}$  to 4.43 A.

Note that the inductor must be rated for the maximum DC load current plus 1/2 of the ripple current.

The ripple current under minimum  $V_{\text{IN}}$  conditions is also checked using the following equations.

$$t_{ON\_VINmin.} = \frac{25 \text{ pF x R}_{tON x V_{OUT}}}{V_{INmin.}} = 451 \text{ ns}$$

$$I_{RIPPLE} = \frac{(V_{IN} - V_{OUT}) \times t_{ON}}{L}$$