Midas Components Limited Electra House 32 Southtown Road Great Yarmouth Norfolk NR31 0DU England Telephone Fax Email Website +44 (0)1493 602602 +44 (0)1493 665111 sales@midasdisplays.com www.midasdisplays.com

## **Contents**

- 1. Module Classification Information

- 2. Precautions in use of LCD Modules

- 3. General Specification

- 4. Absolute Maximum Ratings

- 5. Electrical Characteristics

- 6. Optical Characteristics

- 7. Interface Pin Function

- 8. Power Supply

- 9. Contour Drawing & Block Diagram

- 10. Function Description

- 11. Character Generator ROM Pattern

- 12. Instruction Table

- 13. Interface with MPU

- 14. Initializing of LCM

- 15. Quality Assurance

- 16. Reliability

### **Midas LCD Part Number System**

```

COG

132033

S

Α

6

Т

L

2

3

4

5

6

7

8

9

10

11

12

13

1

14

15

16

=

MC: Midas Components

Blank: COB (chip on board) COG: chip on glass

No of dots

(e.g. 240064 = 240 \times 64 \text{ dots})

(e.g. 21605 = 2 \times 165 mm C.H.)

3

=

=

Series

4

=

Series Variant:

A to Z - see addendum

9: 9 o'clock

12: 12 o'clock

=

3: 3 o'clock

6: 6 o'clock

6

S: Normal (0 to + 50 deg C) W: Wide temp. (-20 to + 70 deg C) X: Extended temp (-30 + 80 Deg C)

7

=

8

Character Set

Blank: Standard (English/Japanese)

C: Chinese Simplified (Graphic Displays only)

CB: Chinese Big 5 (Graphic Displays only)

H: Hebrew

K: European (std) (English/German/French/Greek)

L: English/Japanese (special)

M: European (English/Scandinavian)

R: Cyrillic

W: European (English/Greek)

U: European (English/Scandinavian/Icelandic)

=

Bezel Height (where applicable /available)

LED Connection

Top of Bezel to Top

Array or

Common (via pins 1

of PCB

Edge Lit

and 2)

9.5mm / not

Blank

via pins 15+ 16-

Array

applicable

2

8.9 \; \mathrm{mm}

Common

Array

3

7.8 \; \mathrm{mm}

Separate

Array

4

7.8 \text{ mm}

Common

Array

5

9.5 \text{ mm}

Separate

Array

6

7~\mathrm{mm}

Common

Array

7

7~\mathrm{mm}

Separate

Array

8

Common

6.4 \text{ mm}

Edge

6.4 \text{ mm}

Separate

Edge

5.5 \text{ mm}

Common

Edge

A

В

5.5 \text{ mm}

Separate

Edge

D

6.0mm

Separate

Edge

E

5.0mm

Separate

Edge

\mathbf{F}

4.7mm

Common

Edge

\mathbf{G}

3.7mm

Separate

\mathbf{EL}

7 \text{ mm}

Separate

Edge

T: TN S: STN B: STN Blue G: STN Grey F: FSTN F2: FFSTN V: VA (Vertically Aligned)

10

11

=

P: Positive N: Negative

12

R: Reflective M: Transmissive T: Transflective

=

Backlight: Blank: Reflective L: LED

13

=

Backlight Colour: Y: Yellow-Green W: White B: Blue R: Red A: Amber O: Orange G: Green RGB: R.G.B.

14

Driver Chip:

Blank: Standard I: I<sup>2</sup>C S: SPI T: Toshiba T6963C A: Avant SAP1024B

R: Raio RA6963

15

=

Voltage Variant: e.g. 3 = 3v

16

=

```

## 2. Precautions in use of LCD Modules

- (1) Avoid applying excessive shocks to the module or making any alterations or modifications to it.

- (2) Don't make extra holes on the printed circuit board, modify its shape or change the components of LCD module.

- (3) Don't disassemble the LCM.

- (4) Don't operate it above the absolute maximum rating.

- (5) Don't drop, bend or twist LCM.

- (6) Soldering: only to the I/O terminals.

- (7) Storage: please storage in anti-static electricity container and clean environment.

# 3. General Specification

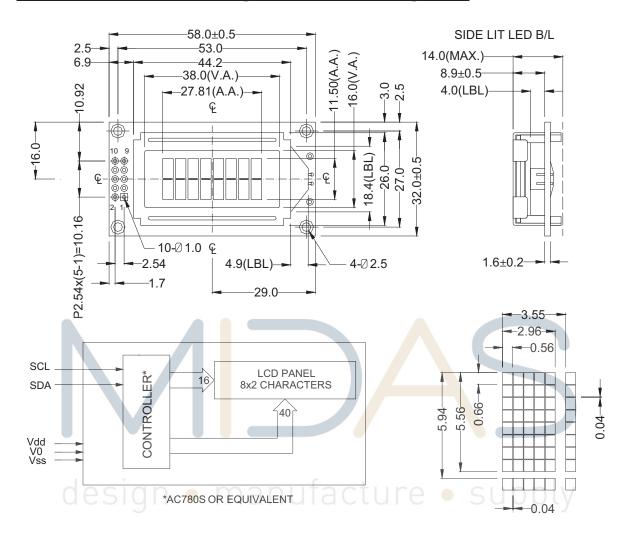

| Item                                  | Dimension                 | Unit      |  |  |  |

|---------------------------------------|---------------------------|-----------|--|--|--|

| Number of Characters                  | 8 characters x 2 Lines    |           |  |  |  |

| Module dimension (With LED Backlight) | 58.0 x 32.0 x 14.0 (MAX)  | mm        |  |  |  |

| View area                             | 38.0 x 16.0               | mm        |  |  |  |

| Active area                           | 27.81 x 11.50             | mm        |  |  |  |

| Dot size man                          | 0.56 x 0.66               | mm        |  |  |  |

| Dot pitch                             | 0.60 x 0.70               | mm        |  |  |  |

| Character size                        | 2.96 x 5.56               | mm        |  |  |  |

| Character pitch                       | 3.55 x 5.94               | mm        |  |  |  |

| LCD type                              | STN, Blue, Negative, Tran | nsmissive |  |  |  |

| Duty                                  | 1/16                      |           |  |  |  |

| View direction                        | 6 o'clock                 |           |  |  |  |

| Backlight Type                        | White LED backlig         | ht        |  |  |  |

# **4. Absolute Maximum Ratings**

| Ite                              | em            | Symbol              | Min     | Max     | Unit |

|----------------------------------|---------------|---------------------|---------|---------|------|

| Input V                          | Voltage       | V <sub>I</sub>      | -0.3    | VDD+0.3 | V    |

| Supply Volta                     | ge For Logic  | VDD-V <sub>SS</sub> | -0.3    | 5.5     | V    |

| Supply Volta                     | ige For LCD   | $V_{DD}$ - $V_0$    | Vdd-7.0 | Vdd+0.3 | V    |

| Wide Temperature Operating Temp. |               | Тор                 | -20     | 70      | °C   |

| LCM                              | Storage Temp. | Tstr                | -30     | 80      | °C   |

# **5. Electrical Characteristics**

| Item                     | Symbol              | Condition                      | Min                   | Тур | Max                   | Unit |

|--------------------------|---------------------|--------------------------------|-----------------------|-----|-----------------------|------|

| Supply Voltage For Logic | $V_{DD}$ - $V_{SS}$ |                                | 4.5                   | 5.0 | 5.5                   | V    |

| Supply Voltage For LCD   | $V_{DD}$ - $V_0$    | Ta=25°C                        | 4.1                   | 4.5 | 5.0                   | V    |

| Input High Volt.         | $V_{ m IH}$         |                                | $0.7~\mathrm{V_{DD}}$ |     | $V_{DD}$              | V    |

| Input Low Volt.          | $V_{IL}$            |                                | $V_{SS}$              | 7   | $0.3~\mathrm{V_{DD}}$ | V    |

| Supply Current           | $I_{DD}$            | V <sub>DD</sub> =5V            | 0.5                   | 1.0 | 1.5                   | mA   |

| Supply Voltage of White  | manu                | Forward current =15 mA         | re                    | SU  | ppl                   | У    |

| LED backlight            | $ m V_{LED}$        | Number of<br>LED die<br>1x1= 1 | 2.9                   | 3.1 | 3.3                   | V    |

## **6. Optical Characteristics**

| Item           | Symbol | Condition     | Min | Тур | Max | Unit |

|----------------|--------|---------------|-----|-----|-----|------|

| View Angle     | (V)θ   | CR <b>≧</b> 2 | -20 | _   | 35  | deg  |

| View Migie     | (Н)ф   | CR <b>≧</b> 2 | -30 | _   | 30  | deg  |

| Contrast Ratio | CR     | _             | _   | 3   | _   | _    |

| Response Time  | T rise | _             | _   | _   | 250 | ms   |

| response Time  | T fall | _             | _   | _   | 250 | ms   |

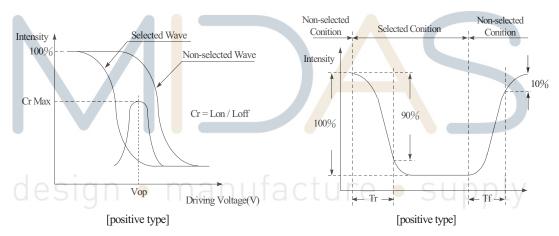

**Definition of Operation Voltage (Vop)**

Definition of Response Time (Tr, Tf)

**Conditions:**

Viewing Angle  $(\theta, \phi): 0^{\circ}, 0^{\circ}$ Operating Voltage: Vop

Frame Frequency: 64 HZ Driving Waveform: 1/N duty, 1/a bias

Definition of viewing angle (CR≧2)

# 7. Interface Pin Function

| Pin No. | Symbol   | Level      | Description               |

|---------|----------|------------|---------------------------|

| 1       | LED (+)  |            | Anode of LED Backlight    |

| 2       | LED (-)  |            | Cathode of LED Backlight  |

| 3       | $V_{SS}$ | 0V         | Ground                    |

| 4       | $V_{DD}$ | 5.0V       | Supply Voltage for logic  |

| 5       | SDA      | H/L        | Serial Data               |

| 6       | SCL      | H/L        | Serial Clock              |

| 7       | V0       | (Variable) | Operating voltage for LCD |

| 8       | NC       |            | No Connection             |

| 9       | NC       |            | No Connection             |

| 10      | NC       |            | No Connection             |

## 8. Power Supply

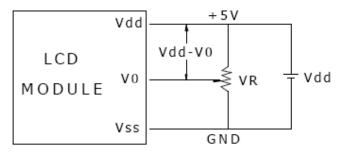

## SINGLE SUPPLY VOLTAGE TYPE

Vdd-V0: LCD Driving Voltage

VR: 10K - 20K

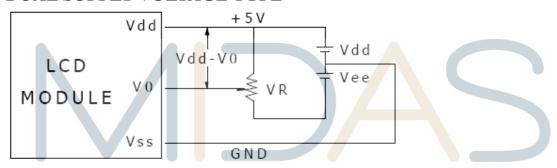

## **DUAL SUPPLY VOLTAGE TYPE**

Vdd-V0: LCD Driving Voltage

vr: 10K - 20K esign • manufacture • supply

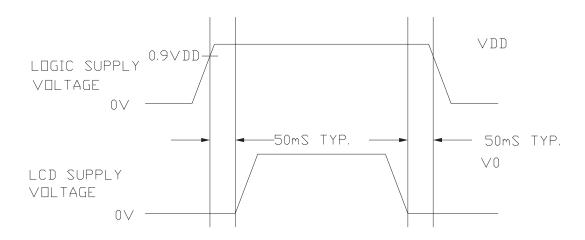

## Timing Diagram of VDD Against V0.

Power on sequence shall meet the requirement of Figure 4, the timing diagram of VDD against V0.

## 9. Contour Drawing & Block Diagram

Link to **Initialization Code**

Link to **Controller**

## **10. Function Description**

The LCD display Module is built in a LSI controller, the controller has two 8-bit registers, an instruction register (IR) and a data register (DR).

The IR stores instruction codes, such as display clear and cursor shift, and address information for display data RAM (DDRAM) and character generator (CGRAM). The IR can only be written from the MPU. The DR temporarily stores data to be written or read from DDRAM or CGRAM. When address information is written into the IR, then data is stored into the DR from DDRAM or CGRAM.

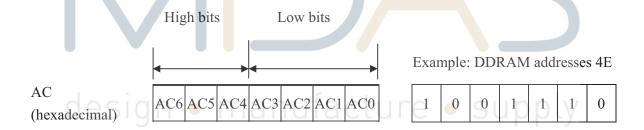

### Address Counter (AC)

The address counter (AC) assigns addresses to both DDRAM and CGRAM

### **Display Data RAM (DDRAM)**

This DDRAM is used to store the display data represented in 8-bit character codes. Its extended capacity is 80×8 bits or 80 characters. Below figure is the relationships between DDRAM addresses and positions on the liquid crystal display.

Display position DDRAM address

5

6

2

1

3

| 00 | 01 | 02 | 03 | 04 | 05 | 06 | 07 |

|----|----|----|----|----|----|----|----|

| 40 | 41 | 42 | 43 | 44 | 45 | 46 | 47 |

2-Line by 8 -Character Display

### **Character Generator ROM (CGROM)**

The CGROM generate 5×8 dot or 5×10 dot character patterns from 8-bit character codes. See Table 2.

### **Character Generator RAM (CGRAM)**

In CGRAM, the user can rewrite character by program. For  $5\times8$  dots, eight character patterns can be written, and for  $5\times10$  dots, four character patterns can be written.

Write into DDRAM the character code at the addresses shown as the left column of table 1. To show the character patterns stored in CGRAM.

# Relationship between CGRAM Addresses, Character Codes (DDRAM) and Character patterns Table 1

| Character Codes (DDRAM data)    | CGRAM Address Character Patterns (CGRAM data)          |

|---------------------------------|--------------------------------------------------------|

| 7 6 5 4 3 2 1 0                 | 5 4 3 2 1 0 7 6 5 4 3 2 1 0                            |

| High Low                        | High Low High Low                                      |

| 0 0 0 0 * 0 0 0                 | 0 0 0 0   * * * *   0 0 0 0 0 0 0 0 0 0                |

| 0 0 0 0 * 0 0 1                 | 0 0 1 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0                |

|                                 | 0 0 0   * * * *                                        |

| * 10 dot character patte        | 1 1 1 1 0 0 1 1 1 1 0 1 1 1 1 1 1 1 1 1                |

| Character Codes<br>(DDRAM data) | C G R A M Address C haracter Patterns (C G R A M data) |

| 7 6 5 4 3 2 1 0                 | 5 4 3 2 1 0 7 6 5 4 3 2 1 0                            |

| High Low                        | High Low Low                                           |

| 0 0 0 0 * 0 0 0                 | 0 0 0 0 0                                              |

|                                 | 1 0 0 1                                                |

|                                 |                                                        |

|                                 | 1 1 1 1   * * * * * * *                                |

# 11. Character Generator ROM Pattern

| <u>b7∾4</u><br>b3∾0 | 0000              | 0001 | 0010 | 0011 | 0100 | 0101 | 0110 | 0111 | 1000 | 1001 | 1010 | 1011 | 1100 | 1101 | 1110 | 1111 |

|---------------------|-------------------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|------|

| 0000                | [00]              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0001                | CG<br>RAM<br>[01] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0010                | [02]              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0011                | CG<br>RAM<br>[03] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0100                | [04]              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0101                | CG<br>RAM<br>[05] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 0110                | 06<br>RAM<br>[06] |      |      |      |      | W    |      |      |      |      |      |      |      |      |      |      |

| 0111                | CG<br>RAM<br>[07] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1000                | C6<br>RAM<br>[08] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1001                | CG<br>RAM<br>[01] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1010                | CG<br>RAM<br>[02] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1011                | [03]              |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1100                | CG<br>RAM<br>[04] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1101                | CG<br>RAM<br>[05] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1110                | CG<br>RAM<br>[06] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

| 1111                | CG<br>RAM<br>[07] |      |      |      |      |      |      |      |      |      |      |      |      |      |      |      |

# **12. Instruction Table**

| Instruction                | Instruction Code |     |     |     |     |     |     |     |     | Description | Execution time                                                                                                                     |               |

|----------------------------|------------------|-----|-----|-----|-----|-----|-----|-----|-----|-------------|------------------------------------------------------------------------------------------------------------------------------------|---------------|

| Instruction                | RS               | R/W | DB7 | DB6 | DB5 | DB4 | DB3 | DB2 | DB1 | DB0         | Description                                                                                                                        | (fosc=210Khz) |

| Clear Display              | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1           | Write "20H" to DDRAM and set<br>DDRAM address to "00H" from AC                                                                     | 1.98ms        |

| Return Home                | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 0   | 1   | _           | Set DDRAM address to "00H" from AC and return cursor to its original position if shifted. The contents of DDRAM are not changed.   | 1.98ms        |

| Entry Mode<br>Set          | 0                | 0   | 0   | 0   | 0   | 0   | 0   | 1   | I/D | SH          | Assign cursor moving direction and enable the shift of entire display.                                                             | 48μs          |

| Display<br>ON/OFF          | 0                | 0   | 0   | 0   | 0   | 0   | 1   | D   | С   | В           | Set display (D), cursor (C), and blinking of cursor (B) on/off control bit.                                                        | 48μs          |

| Cursor or<br>Display Shift | 0                | 0   | 0   | 0   | 0   | 1   | S/C | R/L | _   | _           | Set cursor moving and display shift<br>control bit, and the direction, without<br>changing of DDRAM data.                          | 48μs          |

| Function Set               | 0                | 0   | 0   | 0   | 1   | DL  | N   | F   |     | _           | Set interface data length (DL:8-bit/4-bit), numbers of display line (N:2-line/1-line)and, display font type (F:5×11 dots/5×8 dots) | 48μs          |

| Set CGRAM<br>Address       | 0                | 0   | 0   | 1   | AC5 | AC4 | AC3 | AC2 | AC1 | AC0         | Set CGRAM address in address counter.                                                                                              | 48μs          |

| Set DDRAM<br>Address       | 0                | 0   | 1   | AC6 | AC5 | AC4 | AC3 | AC2 | AC1 | AC0         | Set DDRAM address in address counter.                                                                                              | 48μs          |

| Write Data to<br>RAM       | 1                | 0   | D7  | D6  | D5  | D4  | D3  | D2  | D1  | D0          | Write data into internal RAM (DDRAM/CGRAM).                                                                                        | 48μs          |

## 13. Interface with MPU

# For serial interface data, bus lines (DB5(CSB) \( \) DB6(SDA) and DB7(SCL)) are used. IIC interface

The IIC interface receives and executes the commands sent via the IIC Interface. It also receives RAM data and sends it to the RAM.

The IIC Interface is for bi-directional, two-line communication between different ICs or modules. Serial data line SDA (DB6) and a Serial clock line SCL (DB7) must be connected to a positive supply via a pull-up resistor. Data transfer may be initiated only when the bus is not busy.

\*The CSB (DB5) Pin must be setting to "VSS".

\* When IIC interface is selected, the DL register must be set to "1".

### **BIT TRANSFER**

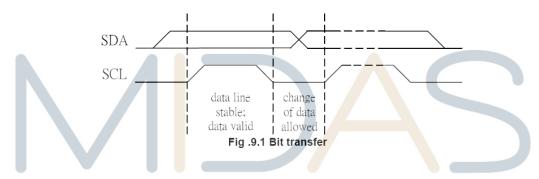

One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the HIGH period of the clock pulse because changes in the data line at this time will be interpreted as a control signal. Bit transfer is illustrated in Fig.9.1

### START AND STOP CONDITIONS

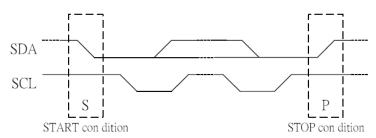

Both data and clock lines remain HIGH when the bus is not busy. A HIGH-to-LOW transition of the data line, while the clock is HIGH is defined as the START condition (S). A LOW-to-HIGH transition of the data line while the clock is HIGH is defined as the STOP condition (P). The START and STOP conditions are illustrated in Fig.9.2

Fig .9.2 Definition of START and STOP conditions

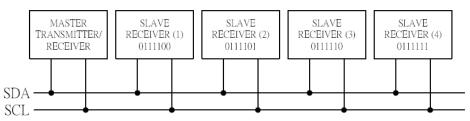

### SYSTEM CONFIGURATION

The system configuration is illustrated in Fig.9.3

- · Transmitter: the device, which sends the data to the bus

- · Receiver: the device, which receives the data from the bus

- · Master: the device, which initiates a transfer, generates clock signals and terminates a transfer

- · Slave: the device addressed by a master

- · Multi-Master: more than one master can attempt to control the bus at the same time without corrupting the message

- · Arbitration: procedure to ensure that, if more than one master simultaneously tries to control the bus, only one is allowed to do so and the message is not corrupted

- · Synchronization: procedure to synchronize the clock signals of two or more devices.

Fig .9.3 System configuration

### ➤ ACKNOWLEDGE

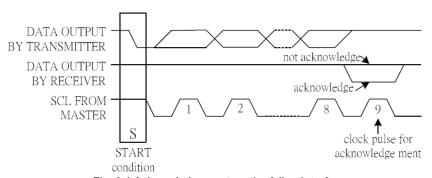

Each byte of eight bits is followed by an acknowledge bit. The acknowledge bit is a HIGH signal put on the bus by the transmitter during which time the master generates an extra acknowledge related clock pulse. A slave receiver which is addressed must generate an Acknowledge after the reception of each byte. A master receiver must also generate an Acknowledge after the reception of each byte that has been clocked out of the slave transmitter. The device that acknowledges must pull-down the SDA line during the acknowledge clock pulse, so that the SDA line is stable LOW during the HIGH period of the Acknowledge related clock pulse (set-up and hold times must be taken into consideration). A master receiver must signal an end-of-data to the transmitter by not generating an Acknowledge on the last byte that has been clocked out of the slave. In this event the transmitter must leave the data line HIGH to enable the master to generate a STOP condition. Acknowledgement on the IIC Interface is illustrated in Fig.9.4

Fig .9.4 Acknowledgement on the 2-line Interface

### > IIC Interface protocol

The RW1063 supports command, data write addressed slaves on the bus.

Before any data is transmitted on the IIC Interface, the device, which should respond, is addressed first. Four 7-bit slave addresses (0111100, 0111101, 0111110 and 0111111) are reserved for the RW1063. The least significant bit of the slave address is set by connecting the input SA0 (DB0) and SA1 (DB1) to either logic 0 (VSS) or logic 1 (VDD).

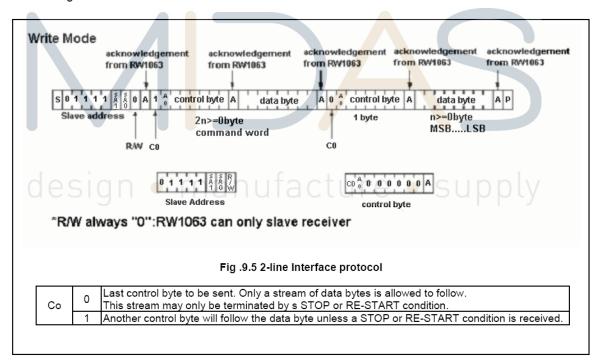

The IIC Interface protocol is illustrated in Figure.9.5

The sequence is initiated with a START condition (S) from the IIC Interface master, which is followed by the slave address. All slaves with the corresponding address acknowledge in parallel, all the others will ignore the IIC Interface transfer. After acknowledgement, one or more command words follow which define the status of the addressed slaves.

A command word consists of a control byte, which defines Co and A0, plus a data byte.

The last control byte is tagged with a cleared most significant bit (i.e. the continuation bit Co). After a control byte with a cleared Co bit, only data bytes will follow. The state of the A0 bit defines whether the data byte is interpreted as a command or as RAM data. All addressed slaves on the bus also acknowledge the control and data bytes. After the last control byte, depending on the A0 bit setting; either a series of display data bytes or command data bytes may follow. If the A0 bit is set to logic 1, these display bytes are stored in the display RAM at the address specified by the data pointer. The data pointer is automatically updated and the data is directed to the intended RW 1063 device. If the A0 bit of the last control byte is set to logic 0, these command bytes will be decoded and the setting of the device will be changed according to the received commands. Only the addressed slave makes the acknowledgement after each byte. At the end of the transmission the IIC interface-bus master issues a STOP condition (P). If no acknowledge is generated by the master after a byte, the driver stops transferring data to the master.

### **Slave Address Option:**

J8,J10 short,J7,J9open, SA1=0,SA0=0(default setting); J8,J9 short,J7,J10open, SA1=0,SA0=1; J7,J10 short,J8,J9open, SA1=1,SA0=0; J7,J9 short,J8,J10open, SA1=1,SA0=1;

DB5(CSB)is connected to Vss by short J6.

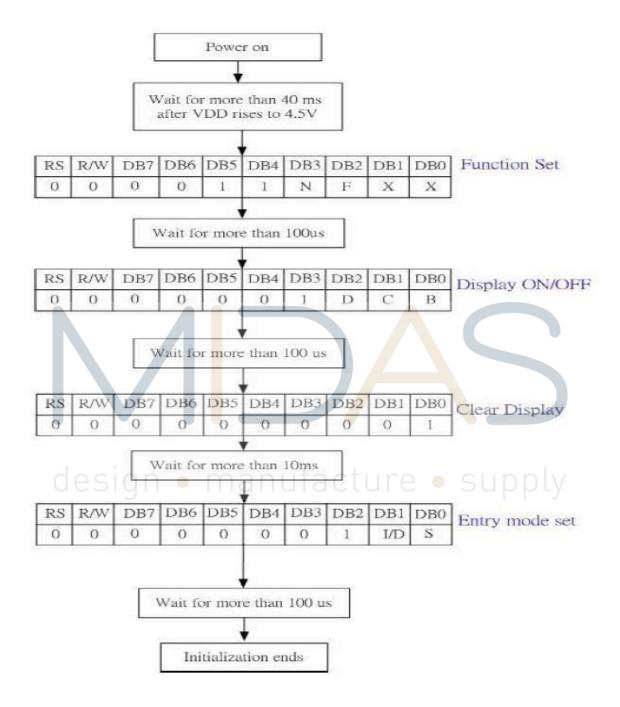

## 14. Initializing of LCM

```

Initial Code:

void WriteData(BYTE byData)

I2C_Start();

I2C_Send(0x78);

I2C_Ack();

I2C Send(0x40);

I2C Ack();

I2C Send(byData);

I2C_Ack();

I2C_Stop();

void WriteInst(BYTE byInst)

I2C Start();

I2C_Send(0x78);

I2C_Ack();

I2C Send(0x00);

I2C Ack();

I2C Send(byInst);

I2C_Ack();

I2C Stop();

void InitRW1063(void)

WriteInst (0x38); //DL=1: 8 bits; N=1: 2 line; F=0: 5 x 8dots

WriteInst (0x0c); // D=1, display on; C=B=0; cursor off; blinking off;

WriteInst (0x06); // I/D=1: Increment by 1; S=0: No shift

```

}

# **15. Quality Assurance**

### **Screen Cosmetic Criteria**

| Defect               | Judgment Criterion                                                                                                                                                                                                                                                                                                                                  | Partition                                                                                                                                                                                                                                                                                                                                                                            |

|----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Spots                | A) Clear  Size: d mm $d \le 0.1$ $0.1 < d \le 0.2$ $0.3 < d \le 0.3$ Note: Including pin holes and defective dots which must be within one pixel size.  B) Unclear  Size: d mm $d \le 0.2$ Acceptable Qty in active area  Disregard  Acceptable Qty in active area  Disregard $d \le 0.2$ Disregard $d \le 0.2 < d \le 0.5$ $d \le 0.5 < d \le 0.7$ | Minor                                                                                                                                                                                                                                                                                                                                                                                |

| Bubbles in Polarizer | Size: d mm d $\leq 0.3$                                                                                                                                                                                                                                                                                                                             | Minor                                                                                                                                                                                                                                                                                                                                                                                |

| Scratch              | In accordance with spots cosmetic criteria. When the light reflects on the panel surface, the scratches are not to be remarkable.                                                                                                                                                                                                                   | Minor                                                                                                                                                                                                                                                                                                                                                                                |

| Allowable Density    | Above defects should be separated more than 30mm each other.                                                                                                                                                                                                                                                                                        | Minor                                                                                                                                                                                                                                                                                                                                                                                |

| Coloration           | Not to be noticeable coloration in the viewing area of the LCD panels.  Back-light type should be judged with back-light on state only.                                                                                                                                                                                                             | Minor                                                                                                                                                                                                                                                                                                                                                                                |

|                      | Spots  Bubbles in Polarizer  Scratch  Allowable Density                                                                                                                                                                                                                                                                                             | A) Clear  Size: d mm d ≤0.1 Disregard 0.1 <d≤0.2 0.2<d≤0.3="" 0.2<d≤0.5="" 0.3<d="" 0.3<d≤1.0="" 0.5<d≤0.7="" 0.7<d="" acceptable="" active="" and="" area="" b)="" be="" d="" defective="" disregard="" dots="" d≤0.7="" holes="" in="" including="" mm="" must="" one="" onote:="" onote<="" pin="" pixel="" qty="" size.="" size:="" td="" unclear="" which="" within=""></d≤0.2> |

# 16. Reliability

## **Content of Reliability Test**

|                                      | <b>Environmental T</b>                                                                                                            | est                                                            |                        |

|--------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------|------------------------|

| Test Item                            | Content of Test                                                                                                                   | <b>Test Condition</b>                                          | Applicable<br>Standard |

| High<br>Temperature<br>storage       | Endurance test applying the high storage temperature for a long time.                                                             | 80°C<br>96hrs                                                  |                        |

| Low<br>Temperature<br>storage        | Endurance test applying the high storage temperature for a long time.                                                             | -30°C<br>96hrs                                                 |                        |

| High<br>Temperature<br>Operation     | Endurance test applying the electric stress (Voltage & Current) and the thermal stress to the element for a long time.            | 70°C<br>96hrs                                                  |                        |

| Low<br>Temperature<br>Operation      | Endurance test applying the electric stress under low temperature for a long time.                                                | -20°C<br>96hrs                                                 |                        |

| High Temperature/ Humidity Storage   | Endurance test applying the high temperature and high humidity storage for a long time.                                           | 80°C, 90%RH<br>96hrs                                           |                        |

| High Temperature/ Humidity Operation | Endurance test applying the electric stress (Voltage & Current) and temperature / humidity stress to the element for a long time. | 70°C, 90%RH<br>96hrs                                           |                        |

| Temperature<br>Cycle                 | Endurance test applying the low and high temperature cycle.  -30°C 25°C 80°C  30min 5min 30min 1 cycle                            | -30°C→80°C<br>10 cycles                                        | supply                 |

|                                      | Mechanical Tes                                                                                                                    | t                                                              |                        |

| Vibration test                       | Endurance test applying the vibration during transportation and using.                                                            | 10~22Hz→1.5mmp-p<br>22~500Hz→1.5G<br>Total 0.5hrs              |                        |

| Shock test                           | Constructional and mechanical endurance test applying the shock during transportation.                                            | 50G Half sign<br>wave 11 msedc<br>3 times of each<br>direction |                        |

<sup>\*\*\*</sup>Supply voltage for logic system=5V. Supply voltage for LCD system= Operating voltage at 25°C