# General-Purpose, $-55^{\circ}$ C to $+125^{\circ}$ C, Wide Bandwidth, DC-Coupled VGA

**Data Sheet**

# AD8336

#### **FEATURES**

Low noise Voltage noise: 3 nV/√Hz Current noise: 3 pA/√Hz Small-signal BW: 115 MHz Large-signal BW: 2 V p-p = 80 MHz Slew rate: 550 V/µs, 2 V p-p Gain ranges (specified) -14 dB to +46 dB 0 dB to 60 dB Gain scaling: 50 dB/V **DC-coupled** Single-ended input and output Supplies: ±3 V to ±12 V Temperature range: -55°C to +125°C Power 150 mW at ±3 V, -55°C < T < +125°C 84 mW at ±3 V, PWRA = 3 V

#### APPLICATIONS

Industrial process controls High performance AGC systems I/Q signal processing Video Industrial and medical ultrasound Radar receivers

#### **GENERAL DESCRIPTION**

The AD8336 is a low noise, single-ended, linear in dB, generalpurpose variable gain amplifier, usable over a large range of supply voltages. It features an uncommitted preamplifier with a usable gain range of 6 dB to 26 dB. The VGA gain range is 0 dB to 60 dB, with absolute gain limits of -26 dB to +34 dB. When the preamplifier gain is adjusted for 12 dB, the combined 3 dB bandwidth of the preamplifier and VGA is 100 MHz, and the amplifier is fully usable to 80 MHz. With  $\pm 5$  V supplies, the maximum output swing is 7 V p-p.

Because of the X-AMP<sup>\*</sup> architecture, frequency response is maintained across the entire gain range of the VGA. The differential gain control interface provides precise linear in dB gain scaling of 50 dB/V over the temperature span of -55°C to +125°C and is simple to interface with a variety of external sources.

The large supply voltage range makes the AD8336 suited for industrial medical applications and video circuits. Dual-supply operation enables bipolar input signals, such as those generated by photodiodes or photomultiplier tubes.

The fully independent voltage feedback preamplifier allows both inverting and noninverting gain topologies. The AD8336 can be used within the specified gain range of -14 dB to +60 dB by selecting a preamplifier gain between 6 dB and 26 dB and choosing appropriate feedback resistors. For the nominal preamplifier gain of 4×, the overall gain range is -14 dB to +46 dB.

If required, quiescent power is limited to a safe level by asserting the PWRA pin.

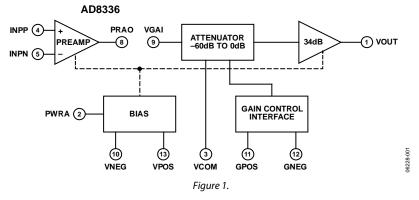

#### FUNCTIONAL BLOCK DIAGRAM

Rev. D Document Feedback Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties that may result from its use. Specifications subject to change without notice. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices. Trademarks and registered trademarks are the property of their respective owners.

One Technology Way, P.O. Box 9106, Norwood, MA 02062-9106, U.S.A. Tel: 781.329.4700 ©2006-2016 Analog Devices, Inc. All rights reserved. Technical Support www.analog.com

# AD8336\* Product Page Quick Links

Last Content Update: 08/30/2016

## Comparable Parts

View a parametric search of comparable parts

## Evaluation Kits

AD8336 Evaluation Board

## Documentation 🖵

## **Application Notes**

• AN-934: 60 dB Wide Dynamic Range, Low Frequency AGC Circuit Using a Single VGA

## **Data Sheet**

• AD8336: General-Purpose, -55°C to +125°C, Wide Bandwidth, DC-Coupled VGA Data Sheet

## Tools and Simulations

## AD8336 SPICE Macro Model

## Reference Materials

## **Product Selection Guide**

• Variable Gain Amplifier Selection Table

## Design Resources

- AD8336 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

## Discussions 🖵

View all AD8336 EngineerZone Discussions

## Sample and Buy

Visit the product page to see pricing options

## Technical Support

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# TABLE OF CONTENTS

| Features                                    | 1   |

|---------------------------------------------|-----|

| Applications                                | 1   |

| General Description                         | 1   |

| Functional Block Diagram                    | 1   |

| Revision History                            | . 2 |

| Specifications                              | . 3 |

| Absolute Maximum Ratings                    | 5   |

| ESD Caution                                 | . 5 |

| Pin Configuration and Function Descriptions | . 6 |

| Typical Performance Characteristics         | . 7 |

| Test Circuits 1                             | 16  |

| Theory of Operation2                        | 20  |

| Overview2                                   | 20  |

| Preamplifier2                               | 20  |

| VGA                                         | 20  |

## **REVISION HISTORY**

#### 5/2016-Rev. C to Rev. D

| Changes to General Description Section and Figure 1. | 1 |

|------------------------------------------------------|---|

| Changes to Figure 2 and Table 3                      | 6 |

| Change to Overview Section                           |   |

| Updated Outline Dimensions                           |   |

| Changes to Ordering Guide                            |   |

## 5/2011—Rev. B to Rev. C

| Change to Figure 2 and Table 3 6 |  |

|----------------------------------|--|

| Changes to OG26                  |  |

## 4/2011-Rev. A to Rev. B

| Change to Table 2                                         | 5  |

|-----------------------------------------------------------|----|

| Changes to Figure 77 and Preamplifier Section             | 20 |

| Changes to Evaluation Board Section, Optional Circuitry   |    |

| Section, and Board Layout Considerations Section          | 24 |

| Added Table 6                                             | 24 |

| Deleted Figure 83; Renumbered Figures Sequentially        | 24 |

| Changes to Figure 82, Figure 83, and Figure 84            | 24 |

| Changes to Figure 85, Figure 86, Figure 87, and Figure 88 | 25 |

| Deleted Table 6                                           | 26 |

|                                                           |    |

| . 21 |

|------|

| . 21 |

| . 21 |

| . 22 |

| . 22 |

| . 22 |

| . 23 |

| . 23 |

| . 24 |

| . 24 |

| . 24 |

| . 27 |

| . 27 |

|      |

#### 9/2008—Rev. 0 to Rev. A

| Change to General Description Section            | 1    |

|--------------------------------------------------|------|

| Deleted Input Capacitance Parameter, Table 1     | 3    |

| Added Exposed Pad Notation to Figure 2           | 6    |

| Changes to Figure 11                             | 8    |

| Changes to Figure 55                             | . 15 |

| Change to Preamplifier Section                   | . 20 |

| Changes to Noise Section                         | . 21 |

| Change to Circuit Configuration for Noninverting |      |

| Gain Section                                     | . 22 |

| Changes to Table 5                               | . 22 |

| Changes to Figure 89 and Table 6                 | . 26 |

| Updated Outline Dimensions                       | . 27 |

| Changes to Ordering Guide                        | . 27 |

#### 10/2006—Revision 0: Initial Version

# **SPECIFICATIONS**

$V_S = \pm 5 V$ ,  $T = 25^{\circ}C$ , gain range = -14 dB to +46 dB, preamplifier gain = 4×, f = 1 MHz,  $C_L = 5 pF$ ,  $R_L = 500 \Omega$ , PWRA = GND, unless otherwise specified.

| Table 1. Parameter                          | Test Conditions/Comments                                                        | Min | True | Max | Unit <sup>1</sup> |

|---------------------------------------------|---------------------------------------------------------------------------------|-----|------|-----|-------------------|

|                                             | lest Conditions/Comments                                                        | Min | Тур  | Max | Unit              |

| PREAMPLIFIER                                |                                                                                 |     | 150  |     |                   |

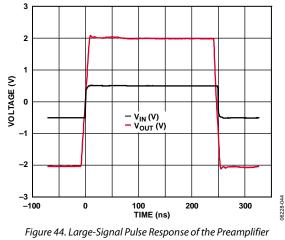

| –3 dB Small-Signal Bandwidth                | $V_{OUT} = 10 \text{ mV p-p}$                                                   |     | 150  |     | MHz               |

| –3 dB Large-Signal Bandwidth                | V <sub>OUT</sub> = 2 V p-p                                                      |     | 85   |     | MHz               |

| Bias Current, Either Input                  |                                                                                 |     | 725  |     | nA                |

| Differential Offset Voltage                 |                                                                                 |     | ±600 |     | μV                |

| Input Resistance                            |                                                                                 |     | 900  |     | kΩ                |

|                                             |                                                                                 | -   | 3    |     | pF                |

| PREAMPLIFIER + VGA                          |                                                                                 |     | 115  |     | N411-             |

| –3 dB Small-Signal Bandwidth                | $V_{OUT} = 10 \text{ mV p-p}$                                                   |     | 115  |     | MHz               |

|                                             | V <sub>OUT</sub> = 10 mV p-p, PWRA = 5 V                                        |     | 40   |     | MHz               |

|                                             | $V_{OUT} = 10 \text{ mV p-p}$ , preamplifier gain = $20 \times$                 |     | 20   |     | MHz               |

|                                             | $V_{OUT} = 10 \text{ mV p-p}$ , preamplifier gain = $-3 \times$                 |     | 125  |     | MHz               |

| –3 dB Large-Signal Bandwidth                | V <sub>OUT</sub> = 2 V p-p                                                      |     | 80   |     | MHz               |

|                                             | V <sub>OUT</sub> = 2 V p-p, PWRA = 5 V                                          |     | 30   |     | MHz               |

|                                             | $V_{OUT} = 2 V p-p$ , preamplifier gain = $20 \times$                           |     | 20   |     | MHz               |

|                                             | $V_{OUT} = 2 V p-p$ , preamplifier gain = $-3 \times$                           |     | 100  |     | MHz               |

| Slew Rate                                   | $V_{OUT} = 2 V p - p$                                                           |     | 550  |     | V/µs              |

| Short-Circuit Preamplifier Input<br>Voltage | $\pm 3 V \le V_S \le \pm 12 V$                                                  |     | 3.0  |     | nV/√Hz            |

| Noise Spectral Density                      |                                                                                 |     | 2.0  |     |                   |

| Input Current Noise Spectral Density        |                                                                                 |     | 3.0  |     | pA/√Hz            |

| Output-Referred Noise                       | $V_{GAIN} = 0.7 V$ , preamplifier gain = 4×                                     |     | 600  |     | nV/√Hz            |

|                                             | $V_{GAIN} = -0.7 V$ , preamplifier gain = 4×                                    |     | 190  |     | nV/√Hz            |

|                                             | $V_{GAIN} = 0.7 V$ , preamplifier gain = 20×                                    |     | 2500 |     | nV/√Hz            |

|                                             | $V_{GAIN} = -0.7 V$ , preamplifier gain = $20 \times$                           |     | 200  |     | nV/√Hz            |

|                                             | $V_{GAIN} = 0.7 V, -55^{\circ}C \le T \le +125^{\circ}C$                        |     | 700  |     | nV/√Hz            |

|                                             | $V_{GAIN} = -0.7 \text{ V}, -55^{\circ}\text{C} \le T \le +125^{\circ}\text{C}$ |     | 250  |     | nV/√Hz            |

| DYNAMIC PERFORMANCE                         |                                                                                 |     |      |     |                   |

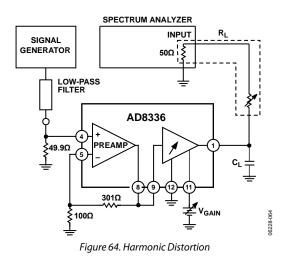

| Harmonic Distortion                         | $V_{GAIN} = 0 V, V_{OUT} = 1 V p - p$                                           |     | 50   |     | 10                |

| HD2                                         | f = 1 MHz                                                                       |     | -58  |     | dBc               |

| HD3                                         | f = 1 MHz                                                                       |     | -68  |     | dBc               |

| HD2                                         | f = 10 MHz                                                                      |     | -60  |     | dBc               |

| HD3                                         | f = 10  MHz                                                                     |     | -60  |     | dBc               |

| Input 1 dB Compression Point                | $V_{GAIN} = -0.7 V$                                                             |     | 11   |     | dBm               |

|                                             | $V_{GAIN} = +0.7 V$                                                             |     | -23  |     | dBm               |

| Two-Tone Intermodulation                    | $V_{GAIN} = 0 V, V_{OUT} = 1 V p-p, f_1 = 0.95 MHz, f_2 = 1.05 MHz$             |     | -71  |     | dBc               |

| Distortion (IMD3)                           | $V_{GAIN} = 0 V, V_{OUT} = 1 V p-p, f_1 = 9.95 MHz, f_2 = 10.05 MHz$            |     | -69  |     | dBc               |

|                                             | $V_{GAIN} = 0 V, V_{OUT} = 2 V p-p, f_1 = 0.95 MHz, f_2 = 1.05 MHz$             |     | -60  |     | dBc               |

|                                             | $V_{GAIN} = 0 V, V_{OUT} = 2 V p-p, f_1 = 9.95 MHz, f_2 = 10.05 MHz$            |     | -58  |     | dBc               |

| Output Third-Order Intercept                | $V_{GAIN} = 0 V, V_{OUT} = 1 V p-p, f = 1 MHz$                                  |     | 34   |     | dBm               |

|                                             | $V_{GAIN} = 0 V, V_{OUT} = 1 V p-p, f = 10 MHz$                                 |     | 32   |     | dBm               |

|                                             | $V_{GAIN} = 0 V, V_{OUT} = 2 V p-p, f = 1 MHz$                                  |     | 34   |     | dBm               |

|                                             | $V_{GAIN} = 0 V, V_{OUT} = 2 V p-p, f = 10 MHz$                                 |     | 33   |     | dBm               |

| Overdrive Recovery                          | $V_{GAIN} = 0.7 V, V_{IN} = 100 mV p-p to 5 mV p-p$                             |     | 50   |     | ns                |

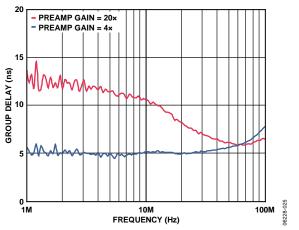

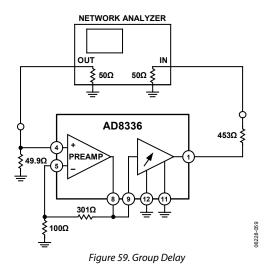

| Group Delay Variation                       | 1 MHz < f < 10 MHz, full gain range                                             |     | ±1   |     | ns                |

| Preamplifier Gain = $20 \times$             | 1 MHz < f < 10 MHz, full gain range                                             |     | ±3   |     | ns                |

| Parameter                                | Test Conditions/Comments                                                                                       | Min      | Тур          | Max   | Unit <sup>1</sup> |

|------------------------------------------|----------------------------------------------------------------------------------------------------------------|----------|--------------|-------|-------------------|

| ABSOLUTE GAIN ERROR <sup>2</sup>         | $-0.7 V < V_{GAIN} < -0.6 V$                                                                                   | 0        | 1 to 5       | 6     | dB                |

|                                          | $-0.6 V < V_{GAIN} < -0.5 V$                                                                                   | 0        | 0.5 to 1.5   | 3     | dB                |

|                                          | $-0.5 V < V_{GAIN} < +0.5 V$                                                                                   | -1.25    | ±0.2         | +1.25 | dB                |

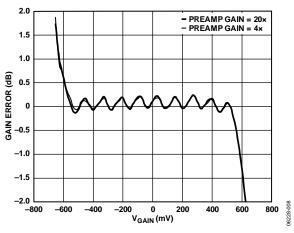

|                                          | $-0.5 \text{ V} < V_{GAIN} < +0.5 \text{ V}, \pm 3 \text{ V} \le V_S \le \pm 12 \text{ V}$                     |          | ±0.5         | +1.25 | dB                |

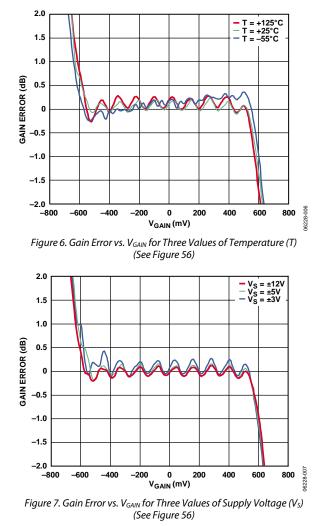

|                                          | $-0.5 \text{ V} < \text{V}_{GAIN} < +0.5 \text{ V}, -55^{\circ}\text{C} \le \text{T} \le +125^{\circ}\text{C}$ |          | ±0.5         |       | dB                |

|                                          | $-0.5 \text{ V} < \text{V}_{GAIN} < +0.5 \text{ V}$ , preamplifier gain = $-3 \times$                          |          | ±0.5         |       | dB                |

|                                          | $0.5 \text{ V} < \text{V}_{GAIN} < +0.6 \text{ V}$                                                             | -4.0     | –1.5 to –3.0 | 0     | dB                |

|                                          | $0.6 \text{ V} < \text{V}_{GAIN} < +0.7 \text{ V}$                                                             | -9.0     | -1 to -5     | 0     | dB                |

| GAIN CONTROL INTERFACE                   |                                                                                                                | 5.0      | 110 5        | 0     | ab                |

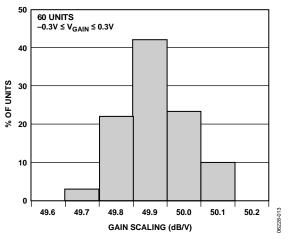

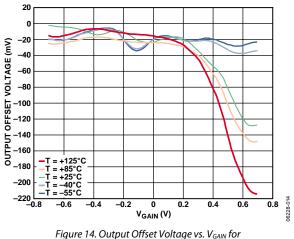

| Gain Scaling Factor                      |                                                                                                                | 48       | 49.9         | 52    | dB/V              |

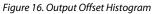

| Intercept                                | Preamplifier + VGA                                                                                             | -10      | 16.4         | 52    | dB                |

| intercept                                | VGA only                                                                                                       |          | 4.5          |       | dB                |

| Coin Dongo                               | VGA ONLY                                                                                                       | 58       | 4.5<br>60    | (2    | dB                |

| Gain Range                               | No folderen                                                                                                    |          | 60           | 62    | ав<br>V           |

| Input Voltage (V <sub>GAIN</sub> ) Range | No foldover                                                                                                    | -Vs      |              | +Vs   | -                 |

| Input Current                            |                                                                                                                |          | 1            |       | μA                |

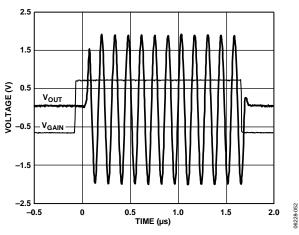

| Response Time                            | 60 dB gain change                                                                                              |          | 300          |       | ns                |

| OUTPUT PERFORMANCE                       |                                                                                                                |          |              |       |                   |

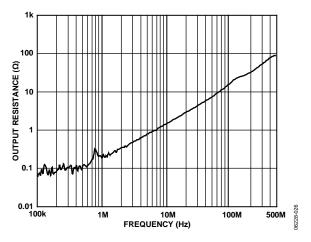

| Output Impedance, DC to 10 MHz           | $\pm 3 V \le V_S \le \pm 12 V$                                                                                 |          | 2.5          |       | Ω                 |

| Output Signal Swing                      | $R_L \geq 500 \; \Omega$ (for $\left  V_S \right  \leq \pm 5 \; V$ ); $R_L \geq 1 \; k \Omega$ above that      |          | Vs  – 1.5    |       | V                 |

|                                          | $R_L \ge 1 \ k\Omega \ (for \  V_S  = \pm 12 \ V)$                                                             |          | Vs  – 2.25   |       | V                 |

| Output Current                           | Linear operation – minimum discernable distortion                                                              |          | 20           |       | mA                |

| Short-Circuit Current                    | $V_s = \pm 3 V$                                                                                                |          | +123/-72     |       | mA                |

|                                          | $V_{S} = \pm 5 V$                                                                                              |          | +123/-72     |       | mA                |

|                                          | $V_S = \pm 12 V$                                                                                               |          | +72/-73      |       | mA                |

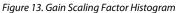

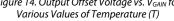

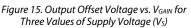

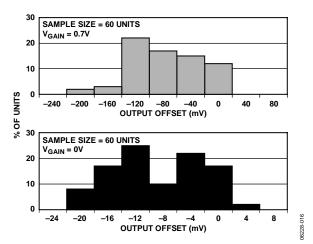

| Output Offset Voltage                    | $V_{GAIN} = 0.7 V$ , gain = 200×                                                                               | -250     | -125         | +150  | mV                |

|                                          | $\pm 3 V \leq V_S \leq \pm 12 V$                                                                               |          | -200         |       | mV                |

|                                          | –55°C ≤ T ≤ +125°C                                                                                             |          | -200         |       | mV                |

| PWRA PIN                                 |                                                                                                                |          |              |       |                   |

| Normal Power (Logic Low)                 | $V_{s} = \pm 3 V$                                                                                              |          |              | 0.7   | V                 |

| Low Power (Logic High)                   | $V_s = \pm 3 V$                                                                                                | 1.5      |              |       | V                 |

| Normal Power (Logic Low)                 | $V_s = \pm 5 V$                                                                                                |          |              | 1.2   | V                 |

| Low Power (Logic High)                   | $V_s = \pm 5 V$                                                                                                | 2.0      |              |       | v                 |

| Normal Power (Logic Low)                 | $V_s = \pm 12 V$                                                                                               |          |              | 3.2   | V                 |

| Low Power (Logic High)                   | $V_s = \pm 12 V$                                                                                               | 4.0      |              | 0.2   | v                 |

| POWER SUPPLY                             |                                                                                                                |          |              |       | •                 |

| Supply Voltage Operating Range           |                                                                                                                | ±3       |              | ±12   | v                 |

| Quiescent Current                        |                                                                                                                | <u> </u> |              | ±12   | v                 |

| $V_s = \pm 3 V$                          |                                                                                                                | 22       | 25           | 30    |                   |

| VS - T2 V                                | –55°C ≤T ≤ +125°C                                                                                              | 22       |              | 20    | m۸                |

|                                          |                                                                                                                | 10       | 23 to 31     | 10    | mA                |

|                                          | PWRA = 3 V                                                                                                     | 10       | 14<br>26     | 18    |                   |

| $V_S = \pm 5 V$                          | 559C                                                                                                           | 22       | 26           | 30    |                   |

|                                          | -55°C ≤ T ≤ +125°C                                                                                             |          | 23 to 31     |       | mA                |

|                                          | PWRA = 5 V                                                                                                     | 10       | 14           | 18    |                   |

| $V_s = \pm 12 V$                         |                                                                                                                | 23       | 28           | 31    |                   |

|                                          | –55°C ≤ T ≤ +125°C                                                                                             |          | 24 to 33     |       | mA                |

|                                          | PWRA = 5 V                                                                                                     |          | 16           |       |                   |

| Power Dissipation                        | $V_S = \pm 3 V$                                                                                                |          | 150          |       | mW                |

|                                          | $V_s = \pm 5 V$                                                                                                |          | 260          |       | mW                |

|                                          | $V_{S} = \pm 12 V$                                                                                             |          | 672          |       | mW                |

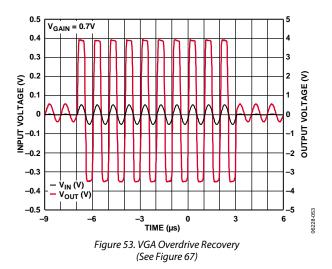

| Power Supply Rejection Ratio (PSRR)      | $V_{GAIN} = 0.7 V, f = 1 MHz$                                                                                  |          | -40          |       | dB                |

$^1$  All dBm values are calculated with 50  $\Omega$  reference, unless otherwise noted.  $^2$  Conformance to theoretical gain expression (see the Setting the Gain section).

## **ABSOLUTE MAXIMUM RATINGS**

#### Table 2.

| 1 4010 2.                           |                            |

|-------------------------------------|----------------------------|

| Parameter                           | Rating                     |

| Supply Voltage (VPOS, VNEG)         | ±15 V                      |

| Input Voltage (INPP, INPN)          | VPOS, VNEG                 |

| Gain Voltage (GPOS, GNEG)           | VPOS, VNEG                 |

| PWRA                                | 5 V, GND                   |

| VGAI                                | VPOS + 0.6 V, VNEG - 0.6 V |

| Power Dissipation                   |                            |

| $V_{S} \le \pm 5 V$                 | 0.43 W                     |

| $\pm 5 V < V_S \leq \pm 12 V$       | 1.12 W                     |

| Operating Temperature Range         |                            |

| $\pm 3 V < V_S \leq \pm 10 V$       | –55°C to +125°C            |

| $\pm 10V < V_S \leq \pm 12V$        | –55°C to +85°C             |

| Storage Temperature Range           | –65°C to +150°C            |

| Lead Temperature (Soldering 60 sec) | 300°C                      |

| Thermal Data <sup>1</sup>           |                            |

| θ」Α                                 | 58.2°C/W                   |

| θ <sub>JB</sub>                     | 35.9°C/W                   |

| θ」                                  | 9.2°C/W                    |

| Ψπ                                  | 1.1°C/W                    |

| Ψ <sub>JB</sub>                     | 34.5°C/W                   |

<sup>1</sup> 4-layer JEDEC board, no airflow, exposed pad soldered to printed circuit board.

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

## **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

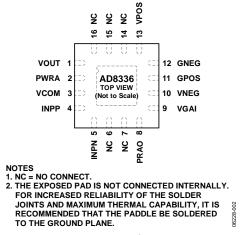

# **PIN CONFIGURATION AND FUNCTION DESCRIPTIONS**

#### Table 3. Pin Function Descriptions

| Pin No.        | Mnemonic | Description                                                                                                                                                                                    |

|----------------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1              | VOUT     | Output Voltage.                                                                                                                                                                                |

| 2              | PWRA     | Power Control. Normal power when grounded; power reduced by half if PWRA is pulled high.                                                                                                       |

| 3              | VCOM     | Common-Mode Voltage. Normally GND when using a dual supply.                                                                                                                                    |

| 4              | INPP     | Positive Input to Preamplifier.                                                                                                                                                                |

| 5              | INPN     | Negative Input to Preamplifier.                                                                                                                                                                |

| 6              | NC       | No Connect.                                                                                                                                                                                    |

| 7              | NC       | No Connect.                                                                                                                                                                                    |

| 8              | PRAO     | Preamplifier Output.                                                                                                                                                                           |

| 9              | VGAI     | VGA Input.                                                                                                                                                                                     |

| 10             | VNEG     | Negative Supply.                                                                                                                                                                               |

| 11             | GPOS     | Positive Gain Control Input.                                                                                                                                                                   |

| 12             | GNEG     | Negative Gain Control Input.                                                                                                                                                                   |

| 13             | VPOS     | Positive Supply.                                                                                                                                                                               |

| 14             | NC       | No Connect.                                                                                                                                                                                    |

| 15             | NC       | No Connect.                                                                                                                                                                                    |

| 16             | NC       | No Connect.                                                                                                                                                                                    |

| Not applicable | EPAD     | The Exposed Pad is Not Connected Internally. For increased reliability of the solder joints and maximum thermal capability, it is recommended that the paddle be soldered to the ground plane. |

# **TYPICAL PERFORMANCE CHARACTERISTICS**

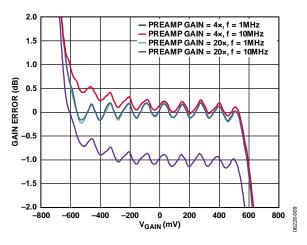

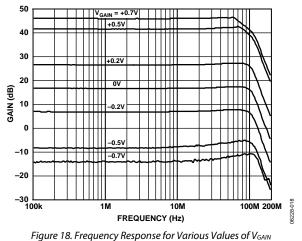

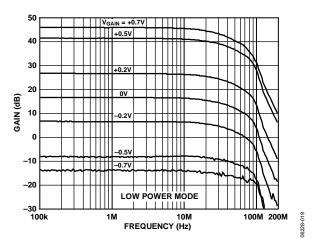

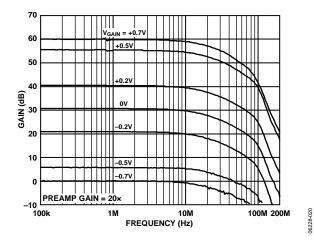

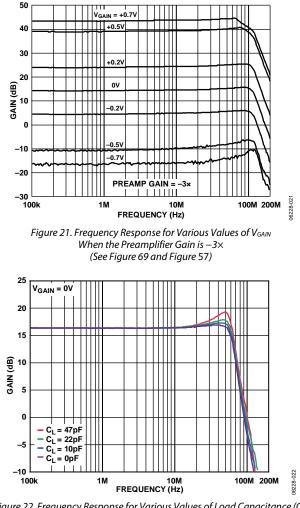

$V_s = \pm 5 V$ ,  $T = 25^{\circ}C$ , gain range = -14 dB to +46 dB, preamplifier gain = 4×, f = 1 MHz,  $C_L = 5 pF$ ,  $R_L = 500 \Omega$ , PWRA = GND, unless otherwise specified.

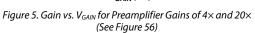

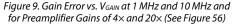

Figure 8. Gain Error vs.  $V_{\text{GAIN}}$  for Preamplifier Gains of 4× and 20× (See Figure 56)

Figure 10. Gain Error vs.  $V_{GAIN}$  at 1 MHz and 10 MHz and for Inverting Preamplifier Gains of  $-3 \times$  and  $-19 \times$  (See Figure 56)

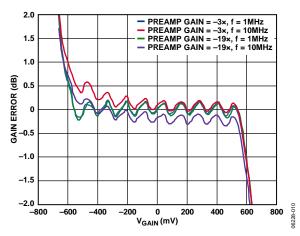

Figure 11. Gain vs. Common-Mode Voltage at VGAIN

## **Data Sheet**

#### 20 ( -20 -40 -60 -60 -80 -10 -120 -120 -140 -160 -160 $V_S = \pm 12V$ -180 = ±5V ٧ \_200 └\_\_\_ \_\_0.8 $V_{S} = \pm 3V$ -0.6 -0.4 0.6 0.8 0 0.2 0.4 06228-015 -0.2 V<sub>GAIN</sub> (V)

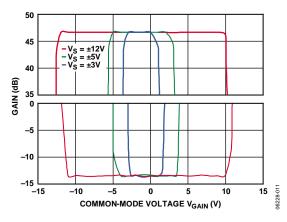

Figure 17. Intercept Histogram

(See Figure 57)

Figure 19. Frequency Response for Various Values of V<sub>GAIN</sub>, Low Power Mode (See Figure 57)

Figure 20. Frequency Response for Various Values of V<sub>GAIN</sub> When the Preamplifier Gain is 20× (See Figure 57)

Figure 22. Frequency Response for Various Values of Load Capacitance (C<sub>L</sub>) (See Figure 57)

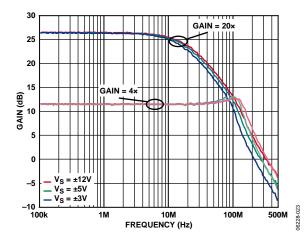

Figure 23. Preamplifier Frequency Response for Three Values of Supply Voltage (Vs) When the Preamplifier Gain is 4× or 20× (See Figure 58)

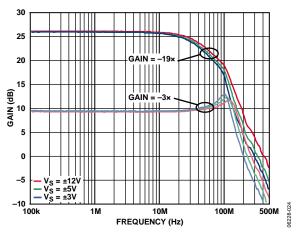

Figure 24. Preamplifier Frequency Response for Three Values of Supply Voltage (V<sub>s</sub>) When the Inverting Gain Value is  $-3 \times$  or  $-19 \times$  (See Figure 69)

Figure 25. Group Delay vs. Frequency for Preamplifier Gains of 4× and 20× (See Figure 59)

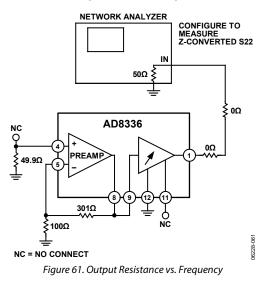

Figure 26. Output Resistance vs. Frequency of the Preamplifier (See Figure 61)

## **Data Sheet**

# $(\mathbf{U})_{\mathbf{U}} = (\mathbf{U})_{\mathbf{U}} = (\mathbf{U})_{\mathbf{U}$

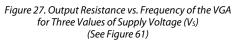

Figure 28. Output-Referred Noise vs. V<sub>GAIN</sub> at Various Temperatures (T) (See Figure 62)

Figure 29. Output-Referred Noise vs. V<sub>GAIN</sub> at Various Temperatures (T) When the Preamplifier Gain is 20× (See Figure 62)

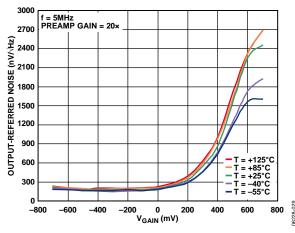

Figure 30. Input-Referred Noise vs.  $V_{GAIN}$  for Preamplifier Gains of 4× and 20× (See Figure 62)

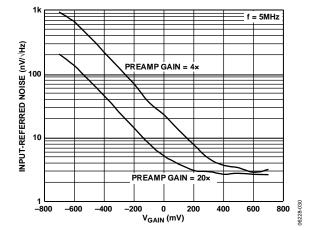

Figure 31. Short-Circuit Input-Referred Noise vs. Frequency at Maximum Gain for Three Values of Supply Voltage (V<sub>5</sub>) (See Figure 62)

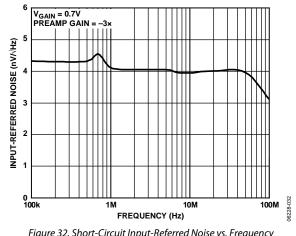

Figure 32. Short-Circuit Input-Referred Noise vs. Frequency at Maximum Inverting Gain (See Figure 73)

## **Data Sheet**

# AD8336

(See Figure 65)

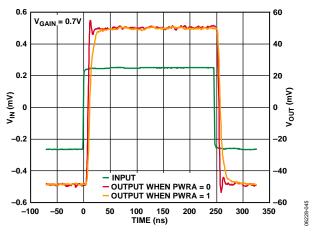

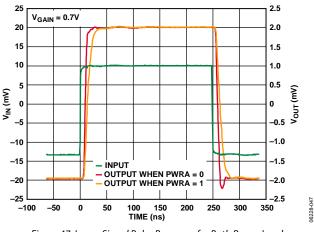

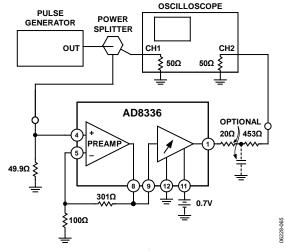

Figure 45. Noninverting Small-Signal Pulse Response for Both Power Levels (See Figure 65)

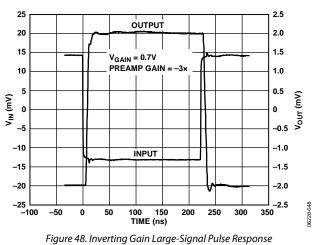

(See Figure 70)

Figure 47. Large-Signal Pulse Response for Both Power Levels (See Figure 65)

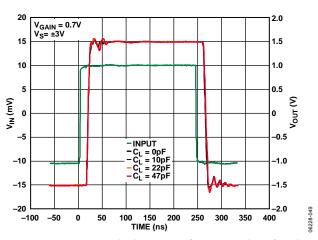

Figure 50. Large-Signal Pulse Response for Various Values of Load Capacitance Using ±5 V Power Supplies (See Figure 65)

## **Data Sheet**

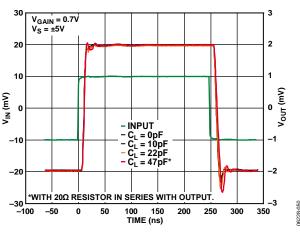

#### 30 V<sub>GAIN</sub> = 0.7V V<sub>S</sub> = ±12V 20 2 10 Vour (mV) V<sub>IN</sub> (mV) 0 INPUT - C<sub>L</sub> = 0pF - C<sub>L</sub> = 10pF\* - C<sub>L</sub> = 22pF\* - C<sub>L</sub> = 47pF\* -10 -1 -2 -20 \*WITH 20Ω RESISTOR IN SERIES WITH OUTPUT -30 6228-051 100 150 TIME (ns) -50 0 50 150 200 250 300 350

Figure 51. Large-Signal Pulse Response for Various Values of Load Capacitance Using ±12 V Power Supplies (See Figure 65)

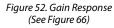

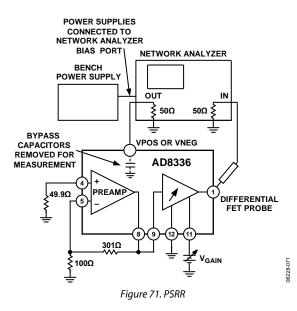

Figure 54. PSRR vs. Frequency for Three Values of V<sub>GAIN</sub> (See Figure 71)

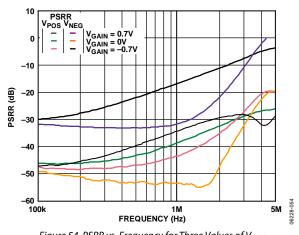

Figure 55. I<sub>Q</sub> vs. Temperature for Three Values of Supply Voltage and High and Low Power (See Figure 68)

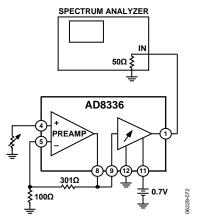

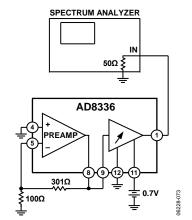

## **TEST CIRCUITS**

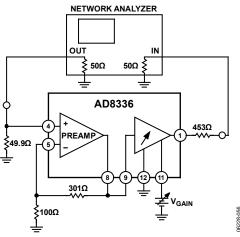

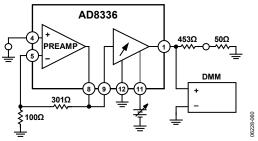

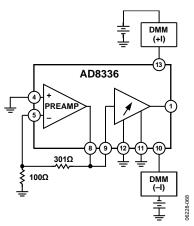

Figure 56. Gain vs. V<sub>GAIN</sub> and Gain Error vs. V<sub>GAIN</sub>

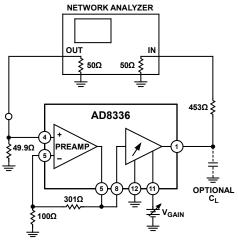

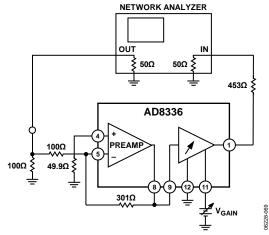

Figure 57. Frequency Response

06228-057

06.22.8-058

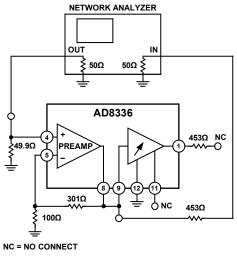

Figure 58. Frequency Response of the Preamplifier

Figure 60. Offset Voltage

## **Data Sheet**

# AD8336

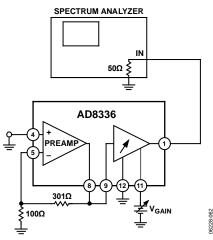

Figure 62. Input-Referred Noise and Output-Referred Noise

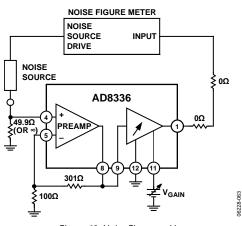

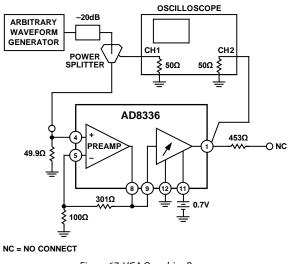

Figure 63. Noise Figure vs. VGAIN

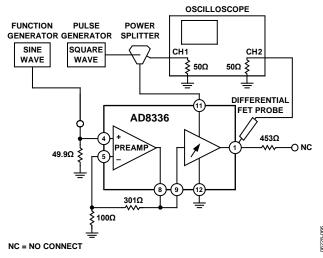

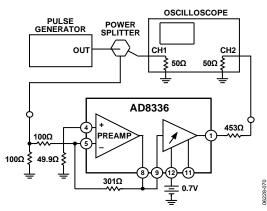

Figure 65. Pulse Response

Figure 66. Gain Response

Figure 67. VGA Overdrive Recovery

Figure 68. Supply Current

Figure 69. Frequency Response, Inverting Gain

Figure 70. Pulse Response, Inverting Gain

Figure 72. Input-Referred Noise vs. Source Resistance

Figure 73. Short-Circuit Input-Referred Noise vs. Frequency

## THEORY OF OPERATION OVERVIEW

The AD8336 is the first VGA designed for operation over exceptionally broad ranges of temperature and supply voltage. The performance has been characterized from temperatures extending from  $-55^{\circ}$ C to  $+125^{\circ}$ C, and supply voltages from  $\pm 3$  V to  $\pm 12$  V. It is ideal for applications requiring dc coupling, large output voltage swings, very large gain ranges, extreme temperature variations, or a combination thereof.

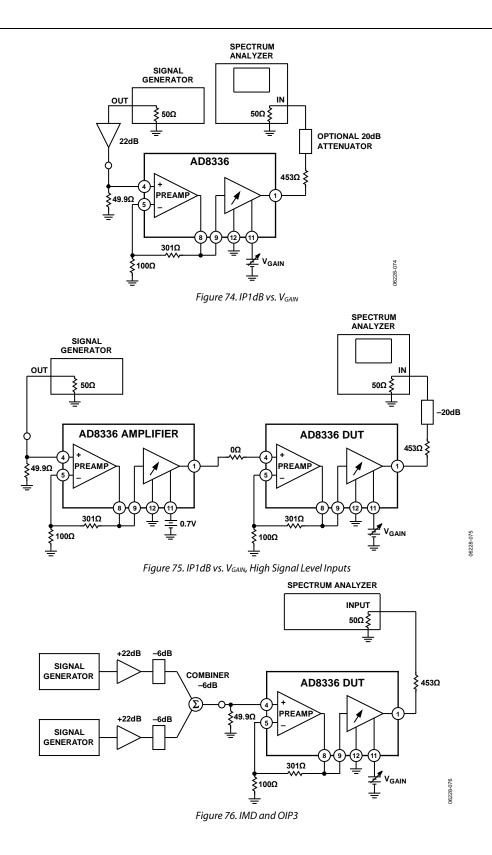

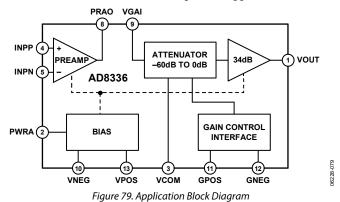

The simplified block diagram is shown in Figure 77. The AD8336 includes a voltage feedback preamplifier, an amplifier with a fixed gain of 34 dB, a 60 dB attenuator, and various bias and interface circuitry. The independent voltage feedback operational amplifier can be used in noninverting and inverting configurations and functions as a preamplifier to the variable gain amplifier (VGA). If desired, the preamplifier output (PRAO) and VGA input (VGAI) pins provide for connection of an interstage filter to eliminate noise and offset. The bandwidth of the AD8336 is dc to 100 MHz with a gain range of 60 dB (-14 dB to +46 dB).

For applications that require large supply voltages, a reduction in power is advantageous. The power reduction pin (PWRA) permits the power and bandwidth to be reduced by about half in such applications.

Figure 77. Simplified Block Diagram

To maintain low noise, the output stages of both the preamplifier and the VGA are capable of driving relatively small load resistances. However, at the largest supply voltages, the signal current can exceed safe operating limits for the amplifiers and, therefore, the load current must not exceed 50 mA. With a  $\pm 12$  V supply and  $\pm 10$  V output voltage at the preamplifier or VGA output, load resistances as low as 200  $\Omega$  are acceptable.

For power supply voltages  $\geq \pm 10$  V, the maximum operating temperature range is derated to +85°C because the power can exceed safe limits (see the Absolute Maximum Ratings section).

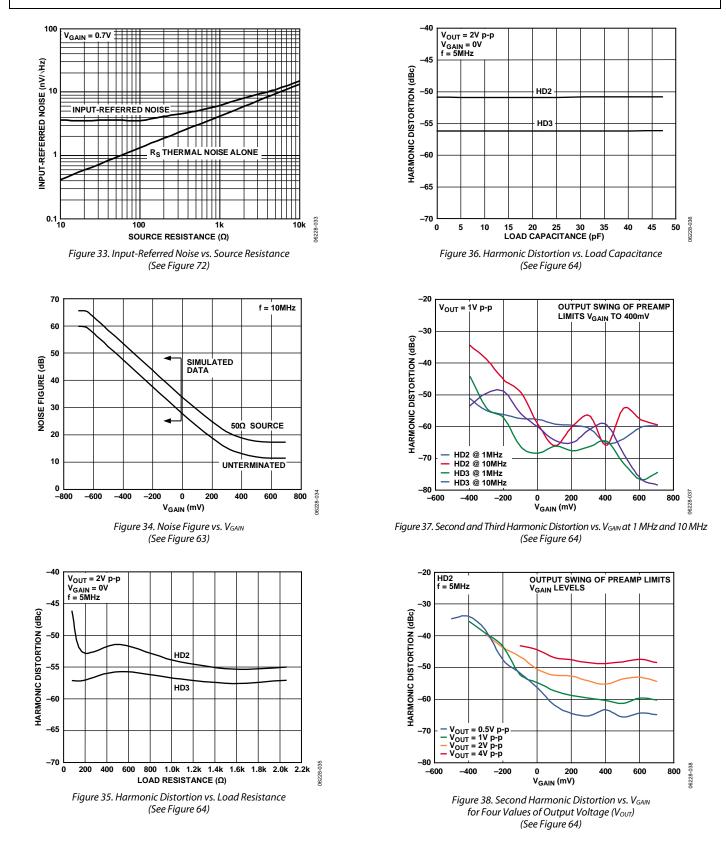

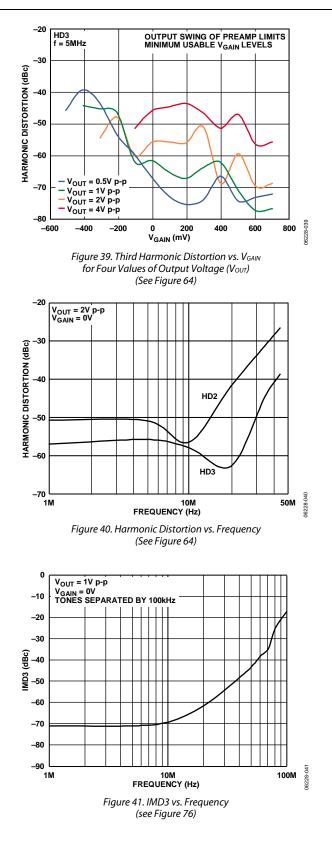

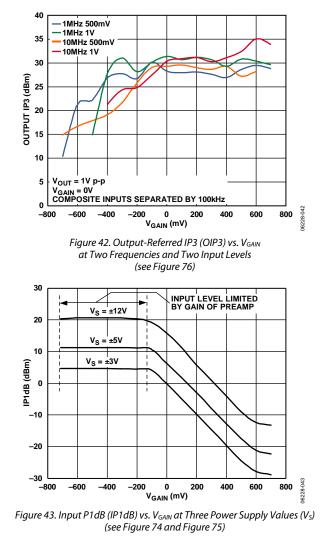

Because harmonic distortion products can increase for various combinations of low impedance loads and high output voltage swings, it is recommended that the user determine load and drive conditions empirically.

## PREAMPLIFIER

The gain of the uncommitted voltage feedback preamplifier is set with external resistors. The combined preamplifier and VGA gain is specified in two ranges: -14 dB to +46 dB and 0 dB to 60 dB. Since the VGA gain is fixed at 34 dB (50×), the preamplifier gain is adjusted for gains of 12 dB (4×) and 26 dB (200×).

With low preamplifier gains between  $2\times$  and  $4\times$ , it can be desirable to reduce the high frequency gain with a shunt capacitor across  $R_{FB2}$  to ameliorate peaking in the frequency domain (see Figure 77). To maintain stability, the gain of the preamplifier must be 6 dB ( $2\times$ ) or greater.

Typical of voltage feedback amplifier configurations, the gainbandwidth product of the AD8336 is fixed (at 600); therefore, the bandwidth decreases as the gain is increased beyond the nominal gain value of 4×. For example, if the preamplifier gain is increased to 20×, the bandwidth reduces by a factor of 5 to about 20 MHz. The -3 dB bandwidth of the preamplifier with a gain of 4× is about 150 MHz, and for the 20× gain is about 30 MHz.

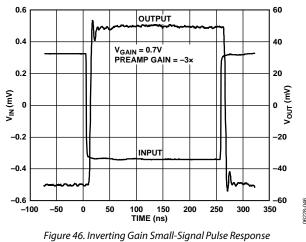

The preamplifier gain diminishes for an amplifier configured for inverting gain, using the same value of feedback resistors as for a noninverting amplifier, but the bandwidth remains unchanged. For example, if the noninverting gain is  $4\times$ , the inverting gain is  $-3\times$ , but the bandwidth stays the same as in the noninverting gain of  $4\times$ . However, because the output-referred noise of the preamplifier is the same in both cases, the input-referred noise increases as the ratio of the two gain values increases. For the previous example, the input-referred noise increases by a factor of 4/3.

The output swing of the preamplifier is the same as for the VGA.

## VGA

The architecture of the variable gain amplifier (VGA) section of the AD8336 is based on the Analog Devices, Inc., X-AMP (exponential amplifier), found in a wide variety of Analog Devices variable gain amplifiers. This type of VGA combines a ladder attenuator and interpolator, followed by a fixed-gain amplifier.

The gain control interface is fully differential, permitting positive or negative gain slopes. Note that the common-mode voltage of the gain control inputs increases with increasing supply.

The gain slope is 50 dB/V and the intercept is 16.4 dB when the nominal preamplifier gain is  $4 \times (12 \text{ dB})$ . The intercept changes with the preamplifier gain; for example, when the preamplifier gain is set to  $20 \times (26 \text{ dB})$ , the intercept becomes 30.4 dB.

Pin VGAI is connected to the input of the ladder attenuator. The ladder ratio is R/2R and the nominal resistance is 320  $\Omega$ . To reduce preamplifier loading and large-signal dissipation, the input resistance at Pin VGAI is 1.28 k $\Omega$ . Safe current density and power dissipation levels are maintained even when large dc signals are applied to the ladder. The tap resistance of the resistors within the R/2R ladder is 640  $\Omega$ /3, or 213.3  $\Omega$ , and is the Johnson noise source of the attenuator.

#### **SETTING THE GAIN**

The overall gain of the AD8336 is the sum (in decibels) or the product (magnitude) of the preamplifier gain and the VGA gain. The preamplifier gain is calculated as with any operational amplifier, as seen in the Applications Information section. It is most convenient to think of the device gain in exponential terms (that is, in decibels) since the VGA responds linearly in decibels with changes in control voltage V<sub>GAIN</sub> at the gain pins.

The gain equation for the VGA is

$$VGA \ Gain \ (dB) = \left[ V_{GAIN}(V) \times \frac{50 \ dB}{V} \right] + 4.4 \ dB$$

where  $V_{GAIN} = V_{GPOS} - V_{GNEG}$ .

The gain and gain range of the VGA are both fixed at 34 dB and 60 dB, respectively; thus, the composite device gain is changed by adjusting the preamplifier gain. For a preamplifier gain of 12 dB (4×), the composite gain is -14 dB to +46 dB. Therefore, the calculation for the composite gain (in decibels) is

Composite Gain =  $G_{PRA}$  + [ $V_{GAIN}$  (V) × 49.9 dB/V] + 4.4 dB

For example, the midpoint gain when the preamplifier gain is 12 dB is

$12 \text{ dB} + [0 \text{ V} \times 49.9 \text{ dB/V}] + 4.4 \text{ dB} = 16.4 \text{ dB}$

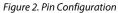

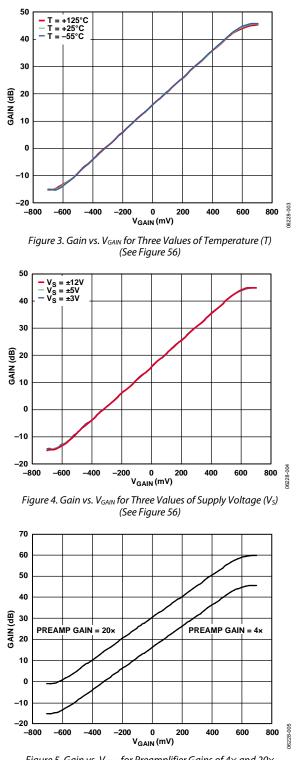

Figure 3 is a plot of gain in decibels vs.  $V_{GAIN}$  in millivolts, when the preamplifier gain is 12 dB (4×). Note that the computed result closely matches the plot of actual gain.

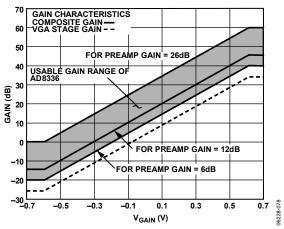

In Figure 3, the gain slope flattens at the limits of the  $V_{GAIN}$  input. The gain response is linear in dB over the center 80% of the control range of the device. Figure 78 shows the ideal gain characteristics for the VGA stage gain, the composite gain, and the preamplifier gain.

Figure 78. Ideal Gain Characteristics of the AD8336

#### NOISE

The noise of the AD8336 is dependent on the value of the VGA gain. At maximum  $V_{GAIN}$ , the dominant noise source is the preamplifier, but it shifts to the VGA as  $V_{GAIN}$  diminishes.

The input-referred noise at the highest VGA gain and a preamplifier gain of 4×, with  $R_{FB1} = 100 \Omega$  and  $R_{FB2} = 301 \Omega$ , is 3 nV/ $\sqrt{Hz}$  and is determined by the preamplifier and the gain setting resistors. See Table 4 for the noise components for the preamplifier.

| Table | e 4. AD833 | <mark>86</mark> Noi | se Components for Preamplifier Gain = 4 | 4× |

|-------|------------|---------------------|-----------------------------------------|----|

|       | -          |                     |                                         |    |

| Noise Component             | Noise Voltage (nV/√Hz) |

|-----------------------------|------------------------|

| Op Amp (Gain = $4 \times$ ) | 2.6                    |

| $R_{FB1} = 100 \ \Omega$    | 0.96                   |

| $R_{FB2} = 301 \Omega$      | 0.55                   |

| VGA                         | 0.77                   |

Using the values listed in Table 4, the total noise of the AD8336 is slightly less than 3 nV/ $\sqrt{\text{Hz}}$ , referred to the input. Although the input noise referred to the VGA is 3.1 nV/ $\sqrt{\text{Hz}}$ , the input-referred noise at the preamplifier is 0.77 nV/ $\sqrt{\text{Hz}}$  when divided by the preamplifier gain of 4×.

At other than maximum gain, the noise of the VGA is determined from the output noise. The noise in the center of the gain range is about 150 nV/ $\sqrt{Hz}$ . Because the gain of the fixed-gain amplifier that is part of the VGA is 50×, the VGA input-referred noise is approximately 3 nV/ $\sqrt{Hz}$ , the same value as the preamplifier and VGA combined. This is expected since the input-referred noise is the same at the input of the attenuator at maximum gain. However, the noise referred to the VGAI pin (the preamplifier output) increases by the amount of attenuation through the ladder network. The noise at any point along the ladder network is primarily composed of the ladder resistance noise, the noise of the input devices, and the feedback resistor network noise. The ladder network and the input devices are the largest noise sources.

At minimum gain, the output noise increases slightly to about 180 nV/ $\sqrt{\text{Hz}}$  because of the finite structure of the X-AMP.

#### **OFFSET VOLTAGE**

Extensive cancellation circuitry included in the variable gain amplifier section minimizes locally generated offset voltages. However, when operated at very large values of gain, dc voltage errors at the output can still result from small dc input voltages. When configured for the nominal gain range of -14 dB to +46 dB, the maximum gain is 200× and an offset of only 100  $\mu$ V at the input generates 20 mV at the output.

The primary source for dc offset errors is the preamplifier; ac coupling between the PRAO and VGAI pins is the simplest solution. In applications where dc coupling is essential, a compensating current can be injected at the INPN input (Pin 5) to cancel preamplifier offset. The direction of the compensating current depends on the polarity of the offset voltage.

## APPLICATIONS INFORMATION AMPLIFIER CONFIGURATION

The AD8336 amplifiers can be configured in various options. In addition to the 60 dB gain range variable gain stage, an uncommitted voltage gain amplifier is available to the user as a preamplifier. The preamplifier connections are separate to enable noninverting or inverting gain configurations or the use of interstage filtering. The AD8336 can be used as a cascade connected VGA with preamp input, as a standalone VGA, or as a standalone preamplifier. This section describes some of the possible applications.

#### PREAMPLIFIER

While observing just a few constraints, the uncommitted voltage feedback preamplifier of the AD8336 can be connected in a variety of standard high frequency operational amplifier configurations. The amplifier is optimized for a gain of  $4 \times (12 \text{ dB})$  and has a gain bandwidth product of 600 MHz. At a gain of  $4 \times$ , the bandwidth is 150 MHz. The preamplifier gain can be adjusted to a minimum gain of  $2 \times$ ; however, there will be a small peak in the response at high frequencies. At higher preamplifier gains, the bandwidth diminishes proportionally in conformance to the classical voltage gain amplifier GBW relationship.

While setting the overall gain of the AD8336, the user must consider the input-referred offset voltage of the preamplifier. Although the offset of the attenuator and postamplifier are almost negligible, the preamplifier offset voltage, if uncorrected, is increased by the combined gain of the preamplifier and post-amplifier. Therefore, for a maximum gain of 60 dB, an input offset voltage of only 200  $\mu$ V results in an error of 200 mV at the output.

## **Circuit Configuration for Noninverting Gain**

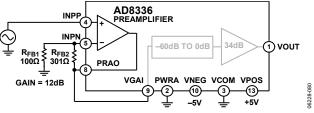

The noninverting configuration is shown in Figure 80. The preamplifier gain is described by the classical operational amplifier gain equation:

$$Gain = \frac{R_{FB2}}{R_{FB1}} + 1$$

The practical gain limits for this amplifier are 6 dB to 26 dB. The gain bandwidth product is about 600 MHz, so at 150 MHz, the maximum achievable gain is 12 dB (4×). The minimum gain is established internally by fixed loop compensation and is 6 dB (2×). This amplifier is not designed for unity-gain operation. Table 5 shows the gain and bandwidth for the noninverting gain configuration.

Figure 80. Circuit Configuration for Noninverting Gain

The preamplifier output reliably sources and sinks currents up to 50 mA. When using  $\pm 5$  V power supplies, the suggested sum of the output resistor values is 400  $\Omega$  total for the optimal tradeoff between distortion and noise. Much of the low gain value device characterization was performed with resistor values of 301  $\Omega$  and 100  $\Omega$ , resulting in a preamplifier gain of 12 dB (4×). With supply voltages between  $\pm 5$  V and  $\pm 12$  V, the sum of the output resistance must be increased accordingly; a total resistance of 1 k $\Omega$  is recommended. Larger resistance values, subject to a trade-off in higher noise performance, can be used if circuit power and load driving is an issue. When considering the total power dissipation, remember that the input ladder resistance of the VGA is part of the preamplifier load.

Table 5. Gain and Bandwidth for Noninverting PreamplifierConfiguration

| Preamplifier Gain |    | Preamplifier | Composite  |  |

|-------------------|----|--------------|------------|--|

| Numerical         | dB | BW (MHz)     | Gain (dB)  |  |

| 4×                | 12 | 150          | -14 to +46 |  |

| 8×                | 18 | 60           | -8 to +52  |  |

| 16×               | 24 | 30           | -2 to +58  |  |

| 20×               | 26 | 25           | 0 to +60   |  |

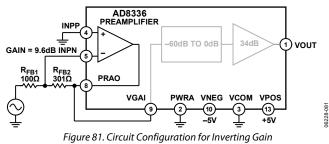

## **Circuit Configuration for Inverting Gain**

The preamplifier can also be used in an inverting configuration, as shown in Figure 81.

The considerations regarding total resistance vs. distortion, noise, and power that were noted in the noninverting case also apply in the inverting case, except that the amplifier can be operated at unity inverting gain. The signal gain is reduced while the noise gain is the same as for the noninverting configuration:

Signal Gain =

$$\frac{R_{FB2}}{R_{FB1}}$$

and

Noise Gain =

$$\frac{R_{FB2}}{R_{FB1}} + 1$$

## **USING THE POWER ADJUST FEATURE**

The AD8336 has the provision to operate at lower power with a trade-off in bandwidth. The power reduction applies to the preamplifier and the VGA sections, and the bandwidth is reduced equally between them. Reducing the power is particularly useful when operating with higher supply voltages and lower values of output loading that otherwise stresses the output amplifiers. When Pin PWRA is grounded, the amplifiers operate in their default mode, and the combined 3 dB bandwidth is 80 MHz with the preamplifier gain adjusted to 4×. When the voltage on Pin PWRA is between 1.2 V and 5 V, the power is reduced by approximately half and the 3 dB bandwidth reduces to approximately 35 MHz. The voltage at Pin PWRA must not exceed 5 V.

## **DRIVING CAPACITIVE LOADS**

The output stages of the AD8336 are stable with capacitive loads up to 47 pF for a supply voltage of  $\pm 3$  V and with capacitive loads up to 10 pF for supply voltages up to  $\pm 8$  V. For larger combined values of load capacitance and/or supply voltage, a 20  $\Omega$  series resistor is recommended for stability.

The influence of capacitance and supply voltage are shown in Figure 50 and Figure 51, where representative combinations of load capacitance and supply voltage requiring a 20  $\Omega$  resistor are marked with an asterisk. No resistor is required for the ±3 V plots in Figure 49, but a resistor is required for most of the ±12 V plots in Figure 51.

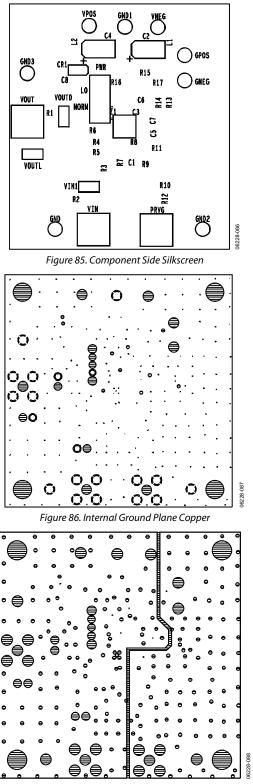

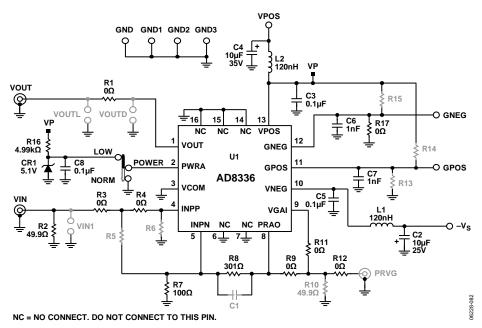

## **EVALUATION BOARD**

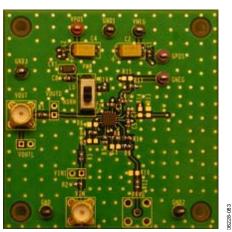

An evaluation board, AD8336-EVALZ, is available online for the AD8336. Figure 82 is a photo of the board.

The board is shipped from the factory configured for a noninverting preamplifier gain of  $4\times$ . To change the value of the gain of the preamplifier or to change the gain polarity to inverting, alter the component values or install components in the alternate locations provided. All components are standard 0603 size, and the board is compliant with RoHS requirements. Table 6 shows the components to be removed and added to change the amplifier configuration to inverting gain.

#### Table 6. Component Changes for Inverting Configuration

| Remove | Install |

|--------|---------|

| R4, R7 | R5, R6  |

## **OPTIONAL CIRCUITRY**

The AD8336 features differential inputs for the gain control, permitting nonzero or floating gain control inputs. To avoid any delay in making the board operational, the gain input circuit is shipped with Pin GNEG connected to ground via a 0  $\Omega$  resistor in the R17 location. The user can adjust the gain of the device by driving the GPOS test loop with a power supply or voltage reference. Optional resistor networks R15/R17 and R13/R14 provide fixed-gain bias voltages at Pin GNEG and Pin GPOS for non-zero common-mode voltages. The gain control can also be driven with an active input such as a ramp. Provision is made for an optional SMA connector at PRVG for monitoring the preamplifier output or for driving the VGA from an external source. Remove the 0  $\Omega$  resistor at R9 to isolate the preamplifier from an external generator. The capacitor at Location C1 limits the bandwidth of the preamplifier.

## **BOARD LAYOUT CONSIDERATIONS**

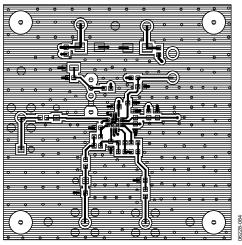

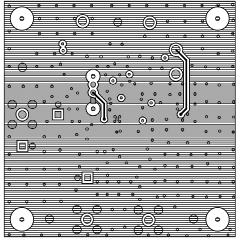

The evaluation board uses four layers, with power and ground planes located between two conductor layers. This arrangement is highly recommended for customers, and several views of the board are provided as reference for board layout details. When laying out a printed circuit board for the AD8336, remember to provide a pad beneath the device to solder the exposed pad of the matching device. The pad in the board must have at least five vias to provide a thermal path for the chip scale package. Unlike leaded devices, the thermal pad is the primary means to remove heat dissipated within the device.

Figure 82. AD8336 Evaluation Board

Figure 83. Component Side Copper

Figure 84. Secondary Side Copper

Figure 87. Internal Power Plane Copper

Figure 88. AD8336-EVALZ Schematic Shown as Shipped, Configured for a Noninverting Gain of  $4 \times$

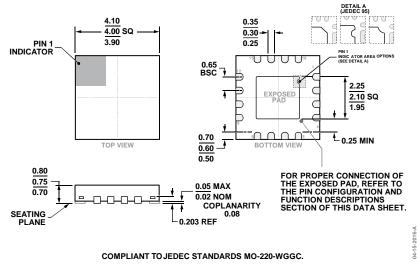

# **OUTLINE DIMENSIONS**

Figure 89. 16-Lead Lead Frame Chip Scale Package [LFCSP] 4 mm × 4 mm Body and 0.75 mm Package Height (CP-16-23) Dimensions shown in millimeters

## **ORDERING GUIDE**

| Model <sup>1</sup> | Temperature Range | Package Description                           | Package Option |

|--------------------|-------------------|-----------------------------------------------|----------------|

| AD8336ACPZ-R7      | -40°C to +85°C    | 16-Lead Lead Frame Chip Scale Package [LFCSP] | CP-16-23       |

| AD8336ACPZ-RL      | -40°C to +85°C    | 16-Lead Lead Frame Chip Scale Package [LFCSP] | CP-16-23       |

| AD8336ACPZ-WP      | -40°C to +85°C    | 16-Lead Lead Frame Chip Scale Package [LFCSP] | CP-16-23       |

| AD8336-EVALZ       |                   | Evaluation Board                              |                |

$^{1}$  Z = RoHS Compliant Part.

# NOTES

www.analog.com

©2006–2016 Analog Devices, Inc. All rights reserved. Trademarks and registered trademarks are the property of their respective owners. D06228-0-5/16(D)