# 16-Bit, 8-Channel Simultaneous Sampling Data Acquisition System

Data Sheet ADAS3023

#### **FEATURES**

Ease-of-use, 16-bit complete data acquisition system Simultaneous sampling selection of 2, 4, 6, and 8 channels Differential input voltage range:  $\pm 20.48$  V maximum High impedance 8-channel input: >500 M $\Omega$  High input common-mode rejection: 95.0 dB User-programmable input ranges On-chip 4.096 V reference and buffer No latency/pipeline delay (SAR architecture) Serial 4-wire 1.8 V to 5 V SPI-/SPORT-compatible interface 40-lead LFCSP package (6 mm  $\times$  6 mm)  $-40^{\circ}$ C to  $+85^{\circ}$ C industrial temperature range

#### **APPLICATIONS**

Multichannel data acquisition and system monitoring

Process control

Power line monitoring

Automated test equipment

Patient monitoring

Spectrum analysis

Instrumentation

#### **GENERAL DESCRIPTION**

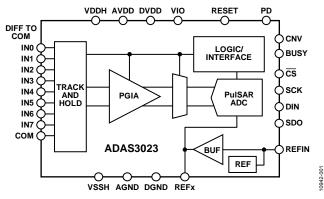

The ADAS3023 is a complete 16-bit successive approximation-based analog-to-digital data acquisition system. This device is capable of simultaneously sampling up to 500 kSPS for two channels, 250 kSPS for four channels, 167 kSPS for six channels, and 125 kSPS for eight channels manufactured on the Analog Devices, Inc., proprietary *i*CMOS\* high voltage industrial process technology.

The ADAS3023 integrates eight channels of low leakage track and hold, a programmable gain instrumentation amplifier (PGIA) stage with a high common-mode rejection offering four differential input ranges, a precision low drift 4.096 V reference and buffer, and a 16-bit charge redistribution successive approximation register (SAR) analog-to-digital converter (ADC). The ADAS3023 can resolve differential input ranges of up to  $\pm 20.48~\rm V$  when using  $\pm 15~\rm V$  supplies.

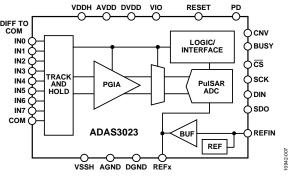

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

The ADAS3023 simplifies design challenges by eliminating signal buffering, level shifting, amplification and attenuation, common-mode rejection, settling time, or any of the other analog signal conditioning challenges, yet allows for smaller form factor, faster time to market, and lower costs.

The ADAS3023 is factory calibrated and its operation is specified from -40°C to +85°C.

**Table 1. Typical Input Range Selection**

| Single-Ended Signals <sup>1</sup> | Input Range, V <sub>IN</sub> |

|-----------------------------------|------------------------------|

| 0 V to 1 V                        | ±1.28 V                      |

| 0 V to 2.5 V                      | ±2.56 V                      |

| 0 V to 5 V                        | ±5.12 V                      |

| 0 V to 10 V                       | ±10.24 V                     |

<sup>&</sup>lt;sup>1</sup> See Figure 39 and Figure 40 in the Analog Inputs section for more information.

### **ADAS3023\* Product Page Quick Links**

Last Content Update: 08/30/2016

### Comparable Parts

View a parametric search of comparable parts

### Evaluation Kits <a> □</a>

· ADAS3023 Evaluation Kit

### Documentation <a>□</a>

#### **Data Sheet**

ADAS3023: 16-Bit, 8-Channel Simultaneous Sampling Data Acquisition System Data Sheet

#### **User Guides**

UG-515: Evaluation Board for the ADAS3023 16-Bit, 8-Channel, Simultaneous Sampling Data Acquisition System

### Tools and Simulations

- ADAS3023 FPGA Reference Design

- ADAS3022/ADAS3023 IBIS Model

### Reference Designs

• CN0201

### Reference Materials -

#### **Technical Articles**

- Exploring Different SAR ADC Analog Input Architectures

- Let's Compare SAR & Δ-Σ Converters for a Mux'd DAS (Planet Analog, 12/2013)

### Design Resources -

- · ADAS3023 Material Declaration

- PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### Discussions <a>□</a>

View all ADAS3023 EngineerZone Discussions

### Sample and Buy -

Visit the product page to see pricing options

### Technical Support -

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

### **TABLE OF CONTENTS**

| Features                                      |

|-----------------------------------------------|

| Applications                                  |

| Functional Block Diagram                      |

| General Description                           |

| Revision History                              |

| Specifications                                |

| Timing Specifications                         |

| Absolute Maximum Ratings                      |

| ESD Caution                                   |

| Pin Configuration and Function Descriptions10 |

| Typical Performance Characteristics           |

| Terminology1                                  |

| Theory of Operation                           |

| Overview19                                    |

| Operation19                                   |

| Transfer Functions                            |

|                                               |

| REVISION HISTORY                              |

| 2/14—Rev. 0 to Rev. A                         |

| Typical Application Connection Diagram | 21 |

|----------------------------------------|----|

| Analog Inputs                          | 21 |

| Voltage Reference Input/Output         | 22 |

| Power Supply                           | 24 |

| Power Dissipation Modes                | 24 |

| Conversion Modes                       | 25 |

| Digital Interface                      | 26 |

| Conversion Control                     | 26 |

| RESET and Power-Down (PD) Inputs       | 26 |

| Serial Data Interface                  | 27 |

| General Timing                         | 28 |

| Configuration Register                 | 29 |

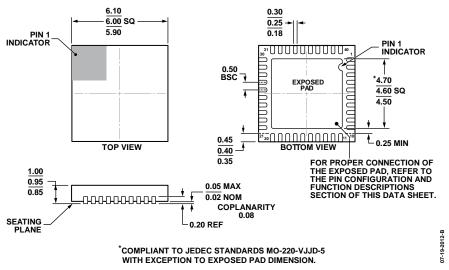

| Packaging and Ordering Information     | 30 |

| Outline Dimensions                     | 30 |

| Ordering Guide                         | 30 |

| Changes to Table 2   | . 5 |

|----------------------|-----|

| Changes to Figure 38 | 21  |

#### 5/13—Revision 0: Initial Version

### **SPECIFICATIONS**

$VDDH = 15\ V \pm 5\%, VSSH = -15\ V \pm 5\%, AVDD = DVDD = 5\ V \pm 5\%; VIO = 1.8\ V \ to \ AVDD, Internal\ Reference\ V_{REF} = 4.096\ V,\ f_S = 500\ kSPS, all\ specifications\ T_{MIN}\ to\ T_{MAX}, unless\ otherwise\ noted.$

Table 2.

| Parameter                                          | Test Conditions/Comments                               | Min                    | Тур  | Max             | Unit <sup>1</sup> |

|----------------------------------------------------|--------------------------------------------------------|------------------------|------|-----------------|-------------------|

| RESOLUTION                                         |                                                        | 16                     |      |                 | Bits              |

| ANALOG INPUT (IN0 to IN7, COM)                     |                                                        |                        |      |                 |                   |

| Input Impedance                                    | Z <sub>IN</sub>                                        | 500                    |      |                 | ΜΩ                |

| Operating Input Voltage Range <sup>2</sup>         | V <sub>IN</sub> , on any single pin                    | VSSH + 2.5             |      | VDDH – 2.5      | V                 |

| Differential Input Voltage Ranges, $V_{\text{IN}}$ | V <sub>INX</sub> – COM                                 |                        |      |                 |                   |

|                                                    | PGIA gain = 0.2, V <sub>IN</sub> = 40.96 V p-p         | -5V <sub>REF</sub>     |      | $+5V_{REF}$     | V                 |

|                                                    | PGIA gain = 0.4, V <sub>IN</sub> = 20.48 V p-p         | -2.5V <sub>REF</sub>   |      | $+2.5V_{REF}$   | V                 |

|                                                    | PGIA gain = $0.8$ , $V_{IN} = 10.24 \text{ V p-p}$     | -1.25V <sub>REF</sub>  |      | $+1.25V_{REF}$  | V                 |

|                                                    | PGIA gain = 1.6, V <sub>IN</sub> = 5.12 V p-p          | -0.625V <sub>REF</sub> |      | $+0.625V_{REF}$ | V                 |

| THROUGHPUT                                         |                                                        |                        |      |                 |                   |

| Conversion Rate                                    | Two channels                                           | 0                      |      | 500             | kSPS              |

|                                                    | Four channels                                          | 0                      |      | 250             | kSPS              |

|                                                    | Six channels                                           | 0                      |      | 167             | kSPS              |

|                                                    | Eight channels                                         | 0                      |      | 125             | kSPS              |

| Transient Response <sup>3</sup>                    | Full-scale step                                        |                        |      | 820             | ns                |

| DC ACCURACY                                        |                                                        |                        |      |                 |                   |

| No Missing Codes                                   |                                                        | 16                     |      |                 | Bits              |

| Integral Linearity Error                           | PGIA gain = 0.2, 0.4, or 0.8, COM = 0 V                | -2.5                   | ±1   | +2.5            | LSB               |

|                                                    | PGIA gain = 1.6, COM = 0 V                             | -3                     | ±1   | +3              |                   |

| Differential Linearity Error                       | All PGIA gains, $COM = 0 V$                            | -0.95                  | ±0.5 | +1.25           | LSB               |

| Transition Noise                                   | PGIA gain = 0.2 or 0.4                                 |                        | 6    |                 | LSB               |

|                                                    | PGIA gain = 0.8                                        |                        | 7    |                 | LSB               |

|                                                    | PGIA gain = 1.6                                        |                        | 10   |                 | LSB               |

| Gain Error <sup>4</sup>                            | External reference, all PGIA gains                     | -0.075                 |      | +0.075          | %FS               |

| Gain Error Match, Delta Mean                       | External reference, all PGIA gains                     | -0.05                  |      | +0.05           | %FS               |

| Gain Error Temperature Drift                       | External reference, PGIA gain = 0.2, 0.4, or 0.8       |                        |      | 1               | ppm/°C            |

|                                                    | External reference, PGIA gain = 1.6                    |                        |      | 2               | ppm/°C            |

| Offset Error <sup>4</sup>                          | External reference, PGIA gain = 0.2                    | -65                    | -35  | +12             | LSB               |

|                                                    | External reference, PGIA gain = 0.4                    | -85                    | -45  | +12             | LSB               |

|                                                    | External reference, PGIA gain = 0.8                    | -10                    | 0    | +10             | LSB               |

|                                                    | External reference, PGIA gain = 1.6                    | 0                      | 130  | 250             | LSB               |

| Offset Error Match, Delta Mean                     | External reference, PGIA gain = 0.2, 0.4, 0.8, or 1.6  | -15                    | ±1   | +15             | LSB               |

| Offset Error Temperature Drift                     | External reference, PGIA gain = 0.2 or 0.4, IN0 to IN7 | 0                      | 0.5  | 2               | ppm/°C            |

|                                                    | External reference, PGIA gain = 0.8, IN0 to IN7        | 0                      | 1.5  | 3               | ppm/°C            |

|                                                    | External reference, PGIA gain = 1.6, IN0 to IN7        | 0                      | 2.5  | 5               | ppm/°C            |

| AC ACCURACY⁵                                       | Internal reference                                     |                        |      |                 |                   |

| Signal-to-Noise Ratio                              | $f_{IN} = 1 \text{ kHz, COM} = 0 \text{ V}$            |                        |      |                 |                   |

|                                                    | PGIA gain = 0.2                                        | 90.0                   | 91.5 |                 | dB                |

|                                                    | PGIA gain = 0.4                                        | 89.5                   | 91.0 |                 | dB                |

|                                                    | PGIA gain = 0.8                                        | 87.5                   | 89.0 |                 | dB                |

|                                                    | PGIA gain = 1.6                                        | 85.0                   | 86.5 |                 | dB                |

| Signal-to-Noise + Distortion (SINAD)               | $f_{IN} = 1$ kHz, two, four, six, and eight channels   |                        |      |                 |                   |

|                                                    | PGIA gain = 0.2                                        | 89.5                   | 91.0 |                 | dB                |

|                                                    | PGIA gain = 0.4                                        | 89.0                   | 90.5 |                 | dB                |

|                                                    | PGIA gain = 0.8                                        | 87.0                   | 88.5 |                 | dB                |

|                                                    | PGIA gain = 1.6                                        | 84.0                   | 86.0 |                 | dB                |

| Parameter                             | Test Conditions/Comments                                      | Min       | Тур        | Max           | Unit <sup>1</sup> |

|---------------------------------------|---------------------------------------------------------------|-----------|------------|---------------|-------------------|

| Dynamic Range                         | $f_{IN} = 1 \text{ kHz}, -60 \text{ dB input}$                |           |            |               |                   |

|                                       | PGIA gain = 0.2                                               | 91.0      | 92         |               | dB                |

|                                       | PGIA gain = 0.4                                               | 90.5      | 91.5       |               | dB                |

|                                       | PGIA gain = 0.8                                               | 88.0      | 89.5       |               | dB                |

|                                       | PGIA gain = 1.6                                               | 86.0      | 87.0       |               | dB                |

| Total Harmonic Distortion             | f <sub>IN</sub> = 1 kHz, all PGIA gains                       |           | -100       |               | dB                |

| Spurious-Free Dynamic Range           | f <sub>IN</sub> = 1 kHz, all PGIA gains                       |           | 105        |               | dB                |

| Channel-to-Channel Crosstalk          | $f_{IN} = 1$ kHz, all channels inactive                       |           | 95         |               | dB                |

| DC Common-Mode Rejection Ratio (CMRR) | All channels                                                  |           |            |               |                   |

|                                       | PGIA gain = 0.2                                               |           | 95.0       |               | dB                |

|                                       | PGIA gain = 0.4                                               |           | 95.0       |               | dB                |

|                                       | PGIA gain = 0.8                                               |           | 95.0       |               | dB                |

|                                       | PGIA gain = 1.6                                               |           | 95.0       |               | dB                |

| –3 dB Input Bandwidth                 | -40 dBFS                                                      |           | 8          |               | MHz               |

| INTERNAL REFERENCE                    |                                                               |           |            |               |                   |

| REFx Pins                             |                                                               |           |            |               |                   |

| Output Voltage                        | T <sub>A</sub> = 25°C                                         | 4.088     | 4.096      | 4.104         | V                 |

| Output Current                        | T <sub>A</sub> = 25°C                                         |           | 250        |               | μΑ                |

| Temperature Drift                     | REFEN bit = 1                                                 |           | ±5         |               | ppm/°C            |

| ·                                     | REFEN bit = 0, REFIN pin = 2.5V                               |           | ±1         |               | ppm/°C            |

| Line Regulation                       | ·                                                             |           |            |               | ' '               |

| Internal Reference                    | $AVDD = 5 V \pm 5\%$                                          |           | 20         |               | μV/V              |

| Buffer Only                           | $AVDD = 5 V \pm 5\%$                                          |           | 4          |               | ppm               |

| REFIN Output Voltage <sup>6</sup>     | T <sub>A</sub> = 25°C                                         | 2.495     | 2.5        | 2.505         | V                 |

| Turn-On Settling Time                 | $C_{REFIN}$ , $C_{REF1}$ , $C_{REF2} = 10 \mu F    0.1 \mu F$ |           | 100        |               | ms                |

| EXTERNAL REFERENCE                    | REFEN bit = 0                                                 |           |            |               |                   |

| Voltage Range                         | REFx input, REFIN = 0 V                                       | 4.000     | 4.096      | 4.104         | V                 |

| <b>.</b>                              | REFIN input (buffered)                                        |           | 2.5        | 2.505         | V                 |

| Current Drain                         | $f_S = 500 \text{ kSPS}$                                      |           | 100        |               | μΑ                |

| DIGITAL INPUTS                        | 13 221 1121 2                                                 |           |            |               | F** 1             |

| Logic Levels                          |                                                               |           |            |               |                   |

| V <sub>IL</sub>                       | VIO > 3 V                                                     | -0.3      |            | +0.3 × VIO    | V                 |

| VIH                                   | VIO > 3 V                                                     | 0.7 × VIO |            | VIO + 0.3     | V                 |

| V <sub>IL</sub>                       | VIO ≤ 3 V                                                     | -0.3      |            | +0.1 × VIO    | V                 |

| ViH                                   | VIO ≤ 3 V                                                     | 0.9 × VIO |            | VIO + 0.3     | v                 |

| I <sub>IL</sub>                       | VIO 2 3 V                                                     | -1        |            | +1            | μΑ                |

| I <sub>IH</sub>                       |                                                               | -1        |            | +1            | μΑ                |

| DIGITAL OUTPUTS <sup>7</sup>          |                                                               | <u>'</u>  |            |               | Pr' (             |

| Data Format                           |                                                               | Two       | s comple   | ment          |                   |

| Vol                                   | $I_{SINK} = +500 \mu\text{A}$                                 |           | os compici | 0.4           | V                 |

| V <sub>OH</sub>                       | $I_{\text{SOURCE}} = -500 \mu\text{A}$                        | VIO – 0.3 |            | 0.1           | V                 |

| POWER SUPPLIES                        | 1300NCE - 300 MT                                              | VIO 0.3   |            |               |                   |

| VIO                                   |                                                               | 1.8       |            | AVDD + 0.3    | V                 |

| AVDD                                  |                                                               | 4.75      | 5          | 5.25          | V                 |

| DVDD                                  |                                                               | 4.75      | 5          | 5.25          | V                 |

| VDDH                                  | VDDH > input voltage + 2.5 V                                  | 14.25     | 5<br>15    | 5.25<br>15.75 | V                 |

| VSSH                                  | VSSH < input voltage + 2.5 V                                  | -15.75    | –15        |               | V                 |

| νυΠ                                   | v 3317 < IIIput voitage – 2.3 v                               | -15./5    | -13        | -14.25        | V                 |

| Parameter                | Test Conditions/Comments                                       | Min   | Тур  | Max  | Unit <sup>1</sup> |

|--------------------------|----------------------------------------------------------------|-------|------|------|-------------------|

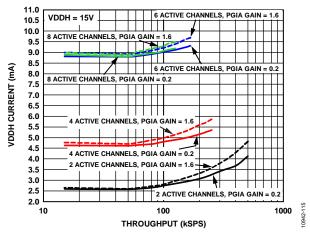

| Іуррн                    | Two channels                                                   |       | 5.0  | 5.5  | mA                |

|                          | Four channels                                                  |       | 6.0  | 7.0  | mA                |

|                          | Six channels                                                   |       | 9.5  | 10.5 | mA                |

|                          | Eight channels                                                 |       | 9.5  | 10.5 | mA                |

|                          | PD = 1                                                         |       | 10.0 |      | μΑ                |

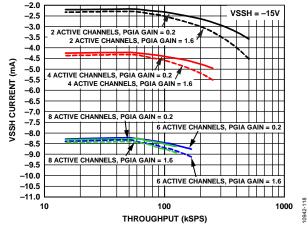

| lvssh                    | Two channels                                                   | -5.5  | -5.0 |      | mA                |

|                          | Four channels                                                  | -6.5  | -5.5 |      | mA                |

|                          | Six channels                                                   | -10.0 | -8.5 |      | mA                |

|                          | Eight channels                                                 | -10.0 | -8.5 |      | mA                |

|                          | All PGIA gains, PD = 1                                         |       | 10.0 |      | μΑ                |

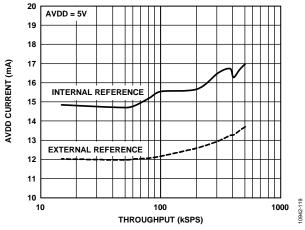

| I <sub>AVDD</sub>        | All PGIA gains, PD = $0$ , reference buffer enabled            |       | 16.0 | 17.0 | mA                |

|                          | All PGIA gains, $PD = 0$ , reference buffer disabled           |       |      | 15.5 | mA                |

|                          | All PGIA gains, PD = 1                                         |       | 100  |      | μΑ                |

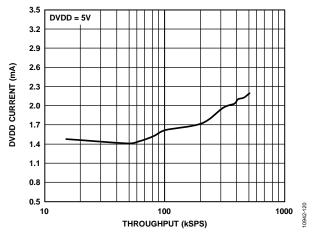

| I <sub>DVDD</sub>        | All PGIA gains, $PD = 0$                                       |       | 2.5  | 3    | mA                |

|                          | All PGIA gains, PD = 1                                         |       | 100  |      | μΑ                |

| Ivio                     | All PGIA gains, PD = $0$ , VIO = $3.3 \text{ V}$               |       |      | 1.0  | mA                |

|                          | All PGIA gains, PD = 1                                         |       | 10.0 |      | μΑ                |

| Power Supply Sensitivity | External reference, T <sub>A</sub> = 25°C                      |       |      |      |                   |

|                          | PGIA gain = 0.2 or 0.4, VDDH/VSSH = $\pm 15 \text{ V} \pm 5\%$ |       | ±0.1 |      | LSB               |

|                          | PGIA gain = 0.8, VDDH/VSSH = $\pm 15 \text{ V} \pm 5\%$        |       | ±0.2 |      | LSB               |

|                          | PGIA gain = 1.6, VDDH/VSSH = $\pm 15 \text{ V} \pm 5\%$        |       | ±0.4 |      | LSB               |

|                          | PGIA gain = 0.2 or 0.4, AVDD, DVDD = $\pm 5 \text{ V} \pm 5\%$ |       | ±1.0 |      | LSB               |

|                          | PGIA gain = 0.8, AVDD, DVDD = $\pm 5 \text{ V} \pm 5\%$        |       | ±1.5 |      | LSB               |

|                          | PGIA gain = 1.6, AVDD, DVDD = $\pm 5 \text{ V} \pm 5\%$        |       | ±2.5 |      | LSB               |

| TEMPERATURE RANGE        |                                                                |       |      |      |                   |

| Specified Performance    | T <sub>MIN</sub> to T <sub>MAX</sub>                           | -40   |      | +85  | °C                |

<sup>&</sup>lt;sup>1</sup> The LSB unit means least significant bit. The weight of the LSB, referred to input, changes depending on the input voltage range. See the Programmable Gain section for the LSB size.

$<sup>^2</sup>$  Full-scale differential input ranges of  $\pm 2.56$  V,  $\pm 5.12$  V,  $\pm 10.24$  V, and  $\pm 20.48$  V are set by the configuration register.

<sup>&</sup>lt;sup>3</sup> If using the external multiplexer in front of the ADAS3023, it must be switched at least 820 ns prior to the rising edge of CNV.

<sup>&</sup>lt;sup>4</sup> See the Terminology section. These parameters are specified at ambient temperature with an external reference. All other influences of temperature and supply are measured and specified separately.

<sup>&</sup>lt;sup>5</sup> All ac specifications expressed in decibels are referenced to the full-scale input range (FSR) and are tested with an input signal at 0.5 dB below full scale, unless otherwise specified.

$<sup>^{\</sup>rm 6}$  This is the output from the internal band gap reference.

<sup>&</sup>lt;sup>7</sup> There is no pipeline delay. Conversion results are available immediately after a conversion is completed.

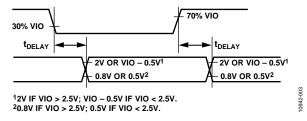

#### **TIMING SPECIFICATIONS**

$VDDH = 15~V \pm 5\%, VSSH = -15~V \pm 5\%, AVDD = DVDD = 5~V \pm 5\%, VIO = 1.8~V~to~AVDD, Internal~Reference~V_{REF} = 4.096~V,~f_S = 500~kSPS, all~specifications~T_{MIN}~to~T_{MAX}, unless otherwise noted. \\^{1}$

Table 3.

| Parameter                                          | Symbol                   | Min                   | Тур   | Max      | Unit |

|----------------------------------------------------|--------------------------|-----------------------|-------|----------|------|

| TIME BETWEEN CONVERSIONS                           | t <sub>CYC</sub>         |                       | ·     |          |      |

| $Warp^2 Mode, CMS = 0$                             |                          |                       |       |          |      |

| Two Channels                                       |                          | 2.0                   |       | 1000     | μs   |

| Four Channels                                      |                          | 4.0                   |       | 1000     | μs   |

| Six Channels                                       |                          | 6.0                   |       | 1000     | μs   |

| Eight Channels                                     |                          | 8.0                   |       | 1000     | μs   |

| Normal Mode (Default), CMS = 1                     |                          | 0.0                   |       |          |      |

| Two Channels                                       |                          | 2.1                   |       | 1000     | μs   |

| Four Channels                                      |                          | 4.1                   |       | 1000     | μs   |

| Six Channels                                       |                          | 6.1                   |       | 1000     | μs   |

| Eight Channels                                     |                          | 8.1                   |       | 1000     | μs   |

| CONVERSION TIME: CNV RISING EDGE TO DATA AVAILABLE | t <sub>CONV</sub>        | 0.1                   |       | 1000     | μ3   |

| Warp Mode, CMS = 0                                 | CONV                     |                       |       |          |      |

| Two Channels                                       |                          |                       | 1 405 | 1620     |      |

|                                                    |                          |                       | 1485  | 1630     | ns   |

| Four Channels                                      |                          |                       | 2850  | 3340     | ns   |

| Six Channels                                       |                          |                       | 4215  | 5000     | ns   |

| Eight Channels                                     |                          |                       | 5580  | 6700     | ns   |

| Normal Mode (Default), CMS = 1                     |                          |                       |       |          |      |

| Two Channels                                       |                          |                       | 1575  | 1720     | ns   |

| Four Channels                                      |                          |                       | 2940  | 3430     | ns   |

| Six Channels                                       |                          |                       | 4305  | 5090     | ns   |

| Eight Channels                                     |                          |                       | 5670  | 6790     | ns   |

| CNV                                                |                          |                       |       |          |      |

| Pulse Width                                        | <b>t</b> <sub>CNVH</sub> | 10                    |       |          | ns   |

| CNV High to Hold Time (Aperture Delay)             | t <sub>AD</sub>          |                       | 2     |          | ns   |

| CNV High to BUSY/SDO2 Delay                        | <b>t</b> <sub>CBD</sub>  |                       |       | 520      | ns   |

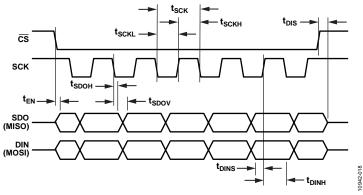

| SCK                                                |                          |                       |       |          |      |

| Period                                             | <b>t</b> <sub>SCK</sub>  | t <sub>SDOV</sub> + 3 | }     |          | ns   |

| Low Time                                           | <b>t</b> sckl            | 5                     |       |          | ns   |

| High Time                                          | tsckh                    | 5                     |       |          | ns   |

| SCK Falling Edge to Data Remains Valid             | t <sub>SDOH</sub>        | 4                     |       |          | ns   |

| SCK Falling Edge to Data Valid Delay               | t <sub>spov</sub>        | '                     |       |          | 1.15 |

| VIO > 4.5 V                                        | 4350V                    |                       |       | 12       | ns   |

| VIO > 3 V                                          |                          |                       |       | 18       | ns   |

| VIO > 2.7 V                                        |                          |                       |       | 24       | ns   |

| VIO > 2.3 V                                        |                          |                       |       |          |      |

| VIO > 1.8 V                                        |                          |                       |       | 25<br>37 | ns   |

| CS/RESET/PD                                        |                          |                       |       | ٥/       | ns   |

|                                                    |                          |                       |       |          |      |

| CS/RESET/PD Low to SDO D15 MSB Valid               | t <sub>EN</sub>          |                       |       |          |      |

| VIO > 4.5 V                                        |                          |                       |       | 7        | ns   |

| VIO > 3 V                                          |                          |                       |       | 8        | ns   |

| VIO > 2.7 V                                        |                          |                       |       | 10       | ns   |

| VIO > 2.3 V                                        |                          |                       |       | 15       | ns   |

| VIO > 1.8 V                                        |                          |                       |       | 20       | ns   |

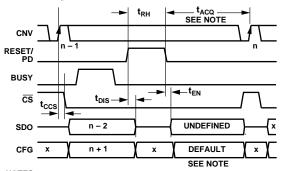

| CS/RESET/PD High to SDO High Impedance             | t <sub>DIS</sub>         |                       |       | 25       | ns   |

| CNV Rising to CS                                   | tccs                     | 5                     |       |          | ns   |

| Parameter                                  | Symbol            | Min | Тур | Max | Unit |

|--------------------------------------------|-------------------|-----|-----|-----|------|

| DIN                                        |                   |     |     |     |      |

| DIN Valid Setup Time from SCK Falling Edge | t <sub>DINS</sub> | 4   |     |     | ns   |

| DIN Valid Hold Time from SCK Falling Edge  | t <sub>DINH</sub> | 4   |     |     | ns   |

| RESET/PD HIGH PULSE                        | t <sub>RH</sub>   | 5   |     |     | ns   |

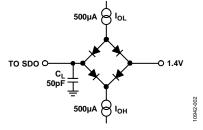

<sup>&</sup>lt;sup>1</sup> See Figure 2 and Figure 3 for load conditions.

#### **Circuit and Voltage Diagrams**

Figure 2. Load Circuit for Digital Interface Timing

Figure 3. Voltage Levels for Timing

<sup>&</sup>lt;sup>2</sup> Exceeding the maximum time has an effect on the accuracy of the conversion (see the Conversion Modes section).

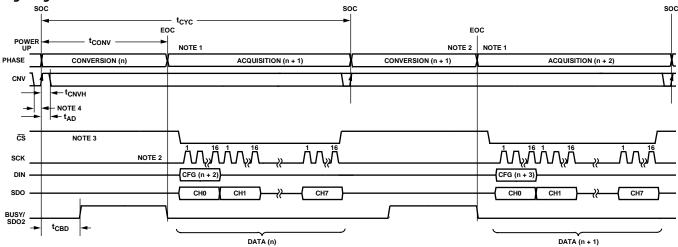

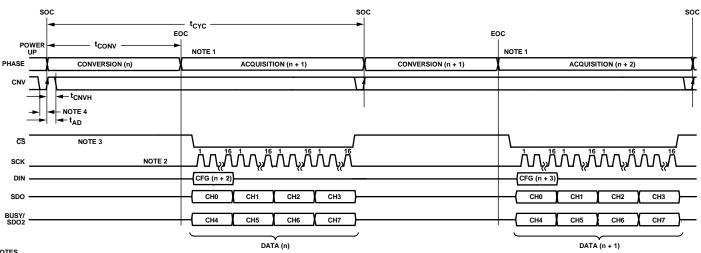

#### **Timing Diagrams**

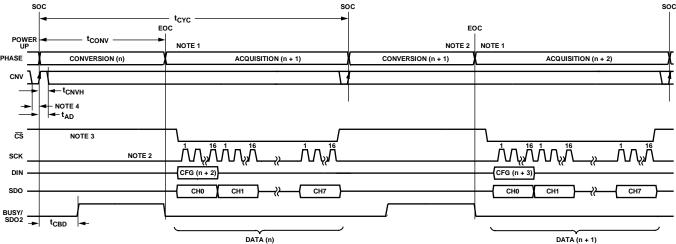

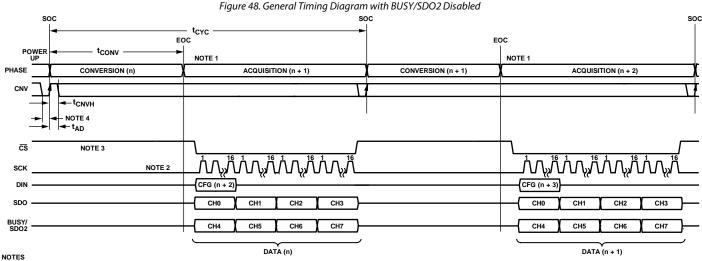

- NOTES

1. DATA ACCESS CAN ONLY OCCUR AFTER CONVERSION. BOTH CONVERSION RESULT AND THE CFG REGISTER ARE UPDATED AT THE END OF THE CONVERSION (EOC).

2. A TOTAL OF 16 SCK FALLING EDGES ARE REQUIRED FOR CONVERSION RESULT. AN ADDITIONAL 16 EDGES AFTER THE LAST CONVERSION RESULT ON BUSY READS BACK THE CFG ASSOCIATED WITH CONVERSION.

3. CS CAN BE HELD LOW OR CONNECTED TO CNV. CS IS SHOWN WITH FULL INDEPENDENT CONTROL.

4. FOR OPTIMAL PERFORMANCE, DATA ACCESS SHOULD NOT OCCUR DURING THE SAMPLING INSTANT. A MINIMUM TIME OF AT LEAST THE APERATURE DELAY, tad, should lapse prior to Data ACCESS.

Figure 4. General Timing Diagram with BUSY/SDO2 Disabled

- NOTES

1. DATA (n)

DATA (n + 1)

1. DATA ACCESS CAN ONLY OCCUR AFTER CONVERSION. BOTH CONVERSION RESULT AND THE CFG REGISTER ARE UPDATED AT THE END OF THE CONVERSION (EOC).

2. A TOTAL OF 16 SCK FALLING EDGES ARE REQUIRED FOR CONVERSION RESULT. AN ADDITIONAL 16 EDGES AFTER THE LAST CONVERSION RESULT ON BUSY READS BACK THE CFG ASSOCIATED WITH CONVERSION.

3. CS CAN BE HELD LOW OR CONNECTED TO CNV. CS IS SHOWN WITH FULL INDEPENDENT CONTROL.

4. FOR OPTIMAL PERFORMANCE, DATA ACCESS SHOULD NOT OCCUR DURING THE SAMPLING INSTANT. A MINIMUM TIME OF AT LEAST THE APERATURE DELAY, tAD, SHOULD LAPSE PRIOR TO DATA ACCESS.

Figure 5. General Timing Diagram with BUSY/SDO2 Enabled

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| 1 abit 4.                                 |                              |

|-------------------------------------------|------------------------------|

| Parameter                                 | Rating                       |

| Analog Inputs/Outputs                     |                              |

| INx, COM to AGND                          | VSSH - 0.3 V to VDDH + 0.3 V |

| REFx to AGND                              | AGND – 0.3 V to AVDD + 0.3 V |

| REFIN to AGND                             | AGND – 0.3 V to +2.7 V       |

| REFN to AGND                              | ±0.3 V                       |

| Ground Voltage Differences                |                              |

| AGND, RGND, DGND                          | ±0.3 V                       |

| Supply Voltages                           |                              |

| VDDH to AGND                              | −0.3 V to +16.5 V            |

| VSSH to AGND                              | +0.3 V to -16.5 V            |

| AVDD, DVDD, VIO to AGND                   | −0.3 V to +7 V               |

| ACAP, DCAP, RCAP to AGND                  | −0.3 V to +2.7 V             |

| Digital Inputs/Outputs                    |                              |

| CNV, DIN, SCK, RESET, PD, $\overline{CS}$ | −0.3 V to VIO + 0.3 V        |

| to DGND                                   |                              |

| SDO, BUSY/SDO2 to DGND                    | −0.3 V to VIO + 0.3 V        |

| Internal Power Dissipation                | 2 W                          |

| Junction Temperature                      | 125°C                        |

| Storage Temperature Range                 | −65°C to +125°C              |

| Thermal Impedance                         |                              |

| $\theta_{JA}$ (LFCSP)                     | 44.1°C/W                     |

| θ <sub>JC</sub> (LFCSP)                   | 0.28°C/W                     |

|                                           |                              |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD (electrostatic discharge) sensitive device.**Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

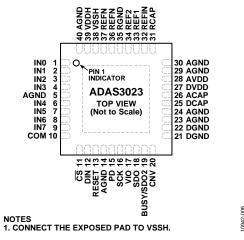

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 6. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No.               | Mnemonic   | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

|-----------------------|------------|-------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1 to 4                | IN0 to IN3 | Al                | Input Channel 0 to Input Channel 3.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 6 to 9                | IN4 to IN7 | Al                | Input Channel 4 to Input Channel 7.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 5, 14, 23,<br>24, 29, | AGND       | Р                 | Analog Ground. Connect AGND to the system analog ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 24, 29,<br>30, 40     |            |                   |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 10                    | СОМ        | Al                | IN0 to IN7 Common Channel Input. Input Channel IN0 to Input Channel IN7 are referenced to a common point. The maximum voltage on this pin is $\pm 10.24$ V for all PGIA gains.                                                                                                                                                                                                                                                                                                                                          |

| 11                    | <u>cs</u>  |                   | Chip Select. Active low signal. Enables the digital interface for writing and reading data. Use the $\overline{\text{CS}}$ pin when sharing the serial bus. For a dedicated and simplified ADAS3023 serial interface, tie $\overline{\text{CS}}$ to DGND or CNV.                                                                                                                                                                                                                                                        |

| 12                    | DIN        | DI                | Data Input. DIN is the serial data input for writing the 16-bit configuration (CFG) word that is clocked into the device on the SCK rising edges. The CFG is an internal register that is updated on the rising edge of the next end of a conversion pulse, which coincides with the falling edge of BUSY/SDO2. The CFG register is written into the device on the first 16 clocks after conversion. To avoid corrupting a conversion due to digital activity on the serial bus, do not write data during a conversion. |

| 13                    | RESET      | DI                | Asynchronous Reset. A low-to-high transition resets the ADAS3023. The current conversion, if active, is aborted and the CFG register is reset to the default state.                                                                                                                                                                                                                                                                                                                                                     |

| 15                    | PD         | DI                | Power-Down. A low-to-high transition powers down the ADAS3023, minimizing the device operating current. Note that PD must be held high until the user is ready to power on the device. After powering on the device, the user must wait 100 ms until the reference is enabled and then wait for the completion of one dummy conversion before the device is ready to convert. Note that the RESET pin remains low for 100 ns after the release of PD. See the Power-Down Mode section for more information.             |

| 16                    | SCK        | DI                | Serial Clock Input. The DIN and SDO data sent to and from the ADAS3023 are synchronized with SCK.                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 17                    | VIO        | Р                 | Digital Interface Supply. Nominally, it is recommended that VIO be at the same voltage as the supply of the host interface: 1.8 V, 2.5 V, 3.3 V, or 5 V.                                                                                                                                                                                                                                                                                                                                                                |

| 18                    | SDO        | DO                | Serial Data Output. The conversion result is output on this pin and synchronized to the SCK falling edges. The conversion results are presented on this pin in twos complement format.                                                                                                                                                                                                                                                                                                                                  |

| 19                    | BUSY/SDO2  | DO                | Busy/Serial Data Output 2. The converter busy signal is always output on the BUSY/SDO2 pin when $\overline{CS}$ is logic high. If SDO2 is enabled when $\overline{CS}$ is brought low after the EOC, the SDO outputs the data. The conversion result is output on this pin and synchronized to the SCK falling edges. The conversion results are presented on this pin in twos complement format.                                                                                                                       |

| 20                    | CNV        | DI                | Convert Input. A conversion is initiated on the rising edge of the CNV pin.                                                                                                                                                                                                                                                                                                                                                                                                                                             |

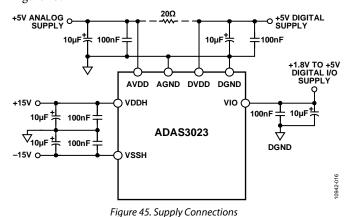

| 21, 22                | DGND       | Р                 | Digital Ground. Connect DGND to the system digital ground plane.                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 25                    | DCAP       | Р                 | Internal 2.5 V Digital Regulator Output. Decouple DCAP, an internally regulated output, using a 10 $\mu$ F and a 0.1 $\mu$ F local capacitor.                                                                                                                                                                                                                                                                                                                                                                           |

| 26                    | ACAP       | Р                 | Internal 2.5 V Analog Regulator Output. This regulator supplies power to the internal ADC core and to all of the supporting analog circuits, except for the internal reference. Decouple this internally regulated output (ACAP) using a 10 $\mu$ F capacitor and a 0.1 $\mu$ F local capacitor.                                                                                                                                                                                                                        |

| Pin No. | Mnemonic   | Type <sup>1</sup> | Description                                                                                                                                                                                                                                                                    |

|---------|------------|-------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 27      | DVDD       | Р                 | Digital 5 V Supply. Decouple the DVDD supply to DGND using a 10 μF capacitor and 0.1 μF local capacitor.                                                                                                                                                                       |

| 28      | AVDD       | Р                 | Analog 5 V Supply. Decouple the AVDD supply to AGND using a 10 $\mu$ F capacitor and 0.1 $\mu$ F local capacitor.                                                                                                                                                              |

| 31      | RCAP       | Р                 | Internal 2.5 V Analog Regulator Output. RCAP supplies power to the internal reference. Decouple this internally regulated output (RCAP) using a 10 µF capacitor and a 0.1 µF local capacitor.                                                                                  |

| 32      | REFIN      |                   | Internal 2.5 V Band Gap Reference Output, Reference Buffer Input, or Reference Power-Down Input. REF1 and REF2 must be tied together externally. See the Voltage Reference Input/Output section for more information.                                                          |

| 33, 34  | REF1, REF2 | AI/O              | Reference Input/Output. Regardless of the reference method, REF1 and REF2 need individual decoupling using external 10 $\mu$ F ceramic capacitors connected as close to REF1, REF2, and REFN as possible. See the Voltage Reference Input/Output section for more information. |

| 35      | RGND       | Р                 | Reference Supply Ground. Connect RGND to the system analog ground plane.                                                                                                                                                                                                       |

| 36, 37  | REFN       | Р                 | Reference Input/Output Ground. Connect the 10 µF capacitors that are on REF1 and REF2 to the REFN pins, then connect the REFN pins to the system analog ground plane.                                                                                                          |

| 38      | VSSH       | Р                 | High Voltage Analog Negative Supply. Nominally, the supply of VSSH is –15 V. Decouple VSSH using a 10 µF capacitor and a 0.1 µF local capacitor. Connect the exposed pad to VSSH.                                                                                              |

| 39      | VDDH       | Р                 | High Voltage Analog Positive Supply. Nominally, the supply of VDDH is 15 V. Decouple VDDH using a 10 µF capacitor and a 0.1 µF local capacitor.                                                                                                                                |

|         | EP         | N/A               | Exposed Pad. Connect the exposed pad to VSSH.                                                                                                                                                                                                                                  |

$<sup>^{1}</sup>$ Al = analog input, Al/O = analog input/output, DI = digital input, DO = digital output, P = power, and N/A means not applicable.

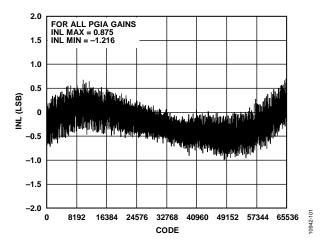

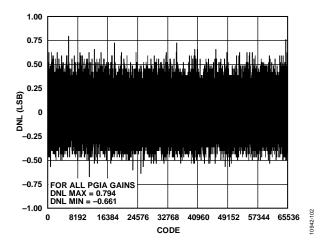

### TYPICAL PERFORMANCE CHARACTERISTICS

VDDH = 15 V, VSSH = -15 V, AVDD = DVDD = 5 V, VIO = 1.8 V to AVDD, unless otherwise noted.

Figure 7. Integral Nonlinearity (INL) vs. Code for All PGIA Gains

Figure 8. Differential Nonlinearity (DNL) vs. Code for All PGIA Gains

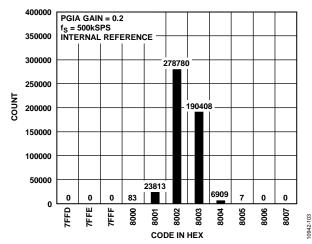

Figure 9. Histogram of a DC Input at Code Center, PGIA Gain = 0.2

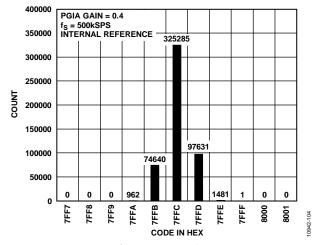

Figure 10. Histogram of a DC Input at Code Center, PGIA Gain = 0.4

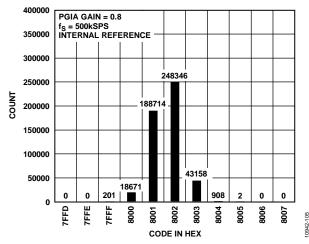

Figure 11. Histogram of a DC Input at Code Center, PGIA Gain = 0.8

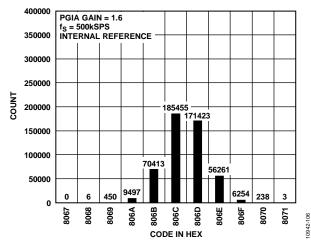

Figure 12. Histogram of a DC Input at Code Center, PGIA Gain = 1.6

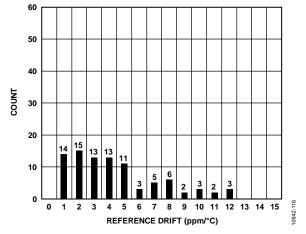

Figure 13. Reference Drift, Internal Reference

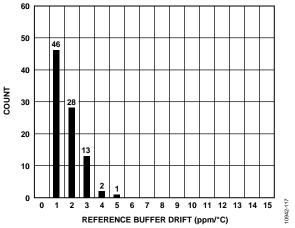

Figure 14. Reference Buffer Drift, Internal Reference

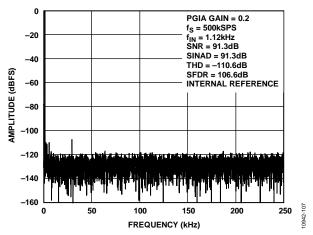

Figure 15. 1 kHz FFT, PGIA Gain = 0.2

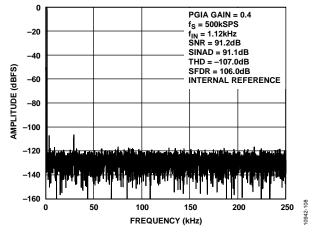

Figure 16. 1 kHz FFT, PGIA Gain = 0.4

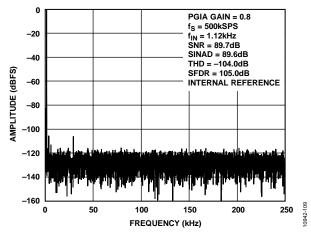

Figure 17. 1 kHz FFT, PGIA Gain = 0.8

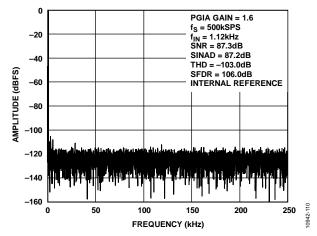

Figure 18. 1 kHz FFT, PGIA Gain = 1.6

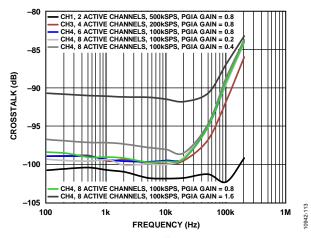

Figure 19. Crosstalk vs. Frequency

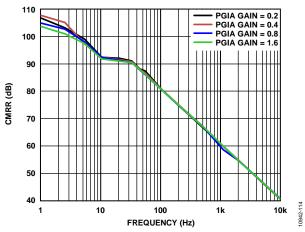

Figure 20. CMRR vs. Frequency

Figure 21. VDDH Current vs. Throughput

Figure 22. VSSH Current vs. Throughput

Figure 23. AVDD Current vs. Throughput

Figure 24. DVDD Current vs. Throughput

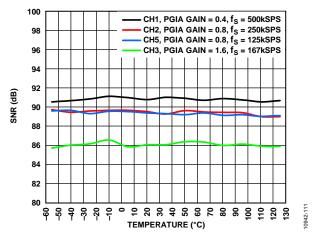

Figure 25. SNR vs. Temperature

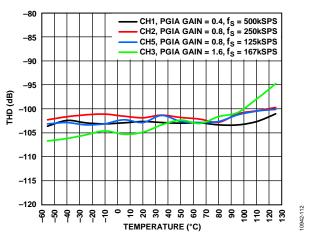

Figure 26. THD vs. Temperature

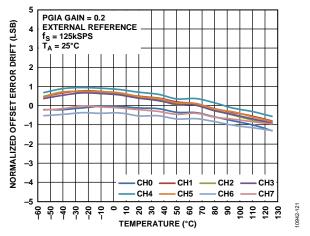

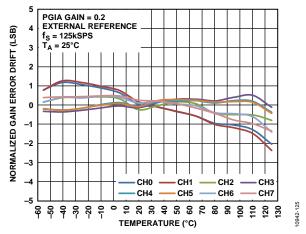

Figure 27. Normalized Offset Error Drift, PGIA GAin = 0.2

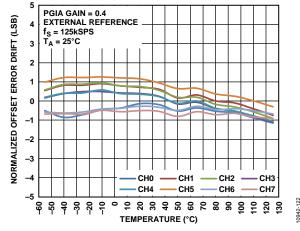

Figure 28. Normalized Offset Error Drift, PGIA Gain = 0.4

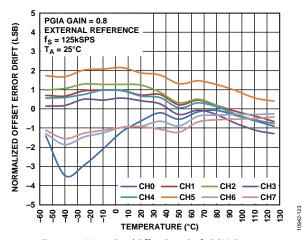

Figure 29. Normalized Offset Error Drift, PGIA Gain = 0.8

Figure 30. Normalized Offset Error Drift, PGIA Gain = 1.6

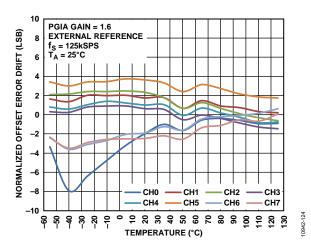

Figure 31. Normalized Gain Error Drift Error, PGIA Gain = 0.2

Figure 32. Normalized Gain Error Drift Error, PGIA Gain = 0.4

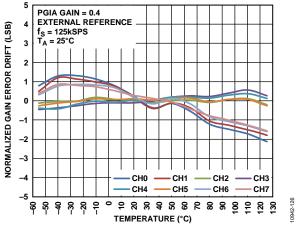

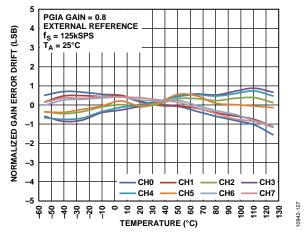

Figure 33. Normalized Gain Error Drift Error, PGIA Gain = 0.8

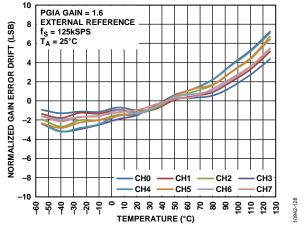

Figure 34. Normalized Gain Error Drift Error, PGIA Gain = 1.6

### **TERMINOLOGY**

#### **Operating Input Voltage Range**

Operating input voltage range is the maximum input voltage range, including common-mode, which can be applied to the input channels, IN0 to IN7, and COM.

#### Differential Input Voltage Range

Differential input voltage range is the maximum differential full-scale input range. The value changes according to the selected programmable gain setting.

#### **Channel Off Leakage**

Channel off leakage is the leakage current with the channel turned off.

#### Channel On Leakage

Channel on leakage is the leakage current with the channel turned on.

#### Common-Mode Rejection Ratio (CMRR)

CMRR is computed as the ratio of the signal magnitude of the converted result, referred to input, in the converted result to the amplitude of the common modulation signal applied to an input pair, expressed in decibels. CMRR is a measure of the ability of the ADAS3023 to reject signals, such as power line noise, that are common to the inputs. This specification is tested and specified for all input channels, IN0 to IN7, with respect to COM.

#### **Transient Response**

Transient response is a measure of the time required for the ADAS3023 to properly acquire the input after a full-scale step function is applied to the system.

#### Least Significant Bit (LSB)

The LSB is the smallest increment that can be represented by a converter. For a fully differential input ADC with N bits of resolution, the LSB expressed in volts is

$$LSB(V) = \frac{2V_{REF}}{2^N}$$

#### **Integral Nonlinearity Error (INL)**

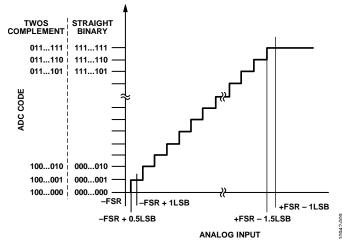

INL refers to the deviation of each individual code from a line drawn from negative full scale through positive full scale. The point used as negative full scale occurs ½ LSB before the first code transition. Positive full scale is defined as a level 1½ LSB beyond the last code transition. The deviation is measured from the middle of each code to the true straight line (see Figure 37).

#### Differential Nonlinearity Error (DNL)

In an ideal ADC, code transitions are 1 LSB apart. DNL is the maximum deviation from this ideal value. DNL is often specified in terms of resolution for which no missing codes are guaranteed.

#### **Offset Error**

Ideally, the MSB transition occurs at an input level that is ½ LSB above analog ground. The offset error is the deviation of the actual transition from that point.

#### **Gain Error**

Ideally, the last transition (from  $011\dots 10$  to  $011\dots 11$ ) occurs for an analog voltage  $1\frac{1}{2}$  LSB below the nominal full scale. The gain error is the deviation in LSB (or percentage of full-scale range) of the actual level of the last transition from the ideal level after the offset error is removed. Closely related is the full-scale error (also in LSB or percentage of full-scale range), which includes the effects of the offset error.

#### **Aperture Delay**

Aperture delay is the measure of the acquisition performance. It is the time between the rising edge of the CNV input and the point at which the input signal is held for a conversion.

#### **Dynamic Range**

Dynamic range is the ratio of the rms value of the full scale to the total rms noise measured with a -60 dBFS input signal applied to the inputs. The value for dynamic range is expressed in decibels.

#### Signal-to-Noise Ratio (SNR)

SNR is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, excluding harmonics and dc. The value for SNR is expressed in decibels.

#### Signal-to-(Noise + Distortion) Ratio (SINAD)

SINAD is the ratio of the rms value of the actual input signal to the rms sum of all other spectral components below the Nyquist frequency, including harmonics but excluding dc. The value for SINAD is expressed in decibels.

#### **Total Harmonic Distortion (THD)**

THD is the ratio of the rms sum of the first five harmonic components to the rms value of a full-scale input signal expressed in decibels.

#### Spurious-Free Dynamic Range (SFDR)

SFDR is the difference, in decibels, between the rms amplitude of the input signal and the peak spurious signal.

#### **Channel-to-Channel Crosstalk**

Channel-to-channel crosstalk is a measure of the level of crosstalk between any channel and all other channels. The crosstalk is measured by applying a dc input to the channel under test and applying a full-scale, 10 kHz sine wave signal to all other channels. The crosstalk is the amount of signal that leaks into the test channel expressed in decibels.

#### Reference Voltage Temperature Coefficient

The reference voltage temperature coefficient is derived from the typical shift of output voltage at 25°C on a sample of devices at the maximum and minimum reference output voltage ( $V_{REF}$ ) measured at  $T_{MIN}$ ,  $T_A$  (25°C), and  $T_{MAX}$  expressed in ppm/°C.

$$TCV_{REF} (\text{ppm/°C}) = \frac{V_{REF} (Max) - V_{REF} (Min)}{V_{REF} (25^{\circ}C) \times (T_{MAX} - T_{MIN})} \times 10^{6}$$

where:

$V_{REF}$  (Max) is the maximum  $V_{REF}$  at  $T_{MIN}$ ,  $T_{A}$  (25°C), or  $T_{MAX}$ .  $V_{REF}$  (Min) is the minimum  $V_{REF}$  at  $T_{MIN}$ ,  $T_{A}$  (25°C), or  $T_{MAX}$ .  $V_{REF}$  (25°C) =  $V_{REF}$  at 25°C.

$T_{MAX} = +85$ °C.

$T_{MIN} = -40$ °C.

# THEORY OF OPERATION OVERVIEW

The ADAS3023 is a 16-bit, 8-channel simultaneous system on a single chip that integrates the typical components used in a data acquisition system in one easy to use, programmable device. It is capable of converting two channels simultaneously up to 500,000 samples per second (500 kSPS) throughput. The ADAS3023 features

- High impedance inputs

- High common-mode rejection

- An 8-channel, low leakage track and hold

- A programmable gain instrumentation amplifier (PGIA) with four selectable differential input ranges from ±2.56 V to ±20.48 V

- A 16-bit PulSAR\* ADC with no missing codes

- An internal, precision, low drift 4.096 V reference and buffer

The ADAS3023 uses the Analog Devices patented high voltage iCMOS process allowing up to a  $\pm 20.48$  V differential input voltage range when using  $\pm 15$  V supplies, which makes the device suitable for industrial applications.

The device is housed in a small 6 mm  $\times$  6 mm, 40-lead LFCSP package and can operate over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C. A typical discrete multichannel data acquisition system containing similar circuitry requires more space on the circuit board than the ADAS3023. Therefore, advantages of the ADAS3023 solution include a reduced footprint and less complex design requirements, leading to faster time to market and lower costs.

#### **OPERATION**

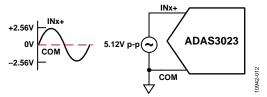

The analog circuitry of the ADAS3023 consists of a high impedance, low leakage, track-and-hold PGIA with a high common-mode rejection that can accept the full-scale differential voltages of  $\pm 2.56$  V,  $\pm 5.12$  V,  $\pm 10.24$  V, and  $\pm 20.48$  V (see Figure 15). The ADAS3023 can be configured to sample two, four, six, or eight channels simultaneously.

The ADAS3023 offers true high impedance inputs in a differential structure and rejects common-mode signals present on the inputs. This architecture does not require additional input buffers (op amps) that are usually required for signal buffering, level shifting, amplification, attenuation, and kickback reduction when using switched capacitor-based SAR ADCs.

Digital control of the programmable gain setting of each channel input is set via the configuration (CFG) register.

The conversion results are output in twos complement format on the serial data output (SDO) and through an optional secondary serial data output on the BUSY/SDO2 pin. The digital interface uses a dedicated chip select  $(\overline{CS})$  to control data access to and from the ADAS3023 together with a BUSY/SDO2 output, asynchronous reset (RESET), and power-down (PD) inputs.

The internal reference of the ADAS3023 uses an internal temperature compensated 2.5 V output band gap reference, followed by a precision buffer amplifier to provide the 4.096 V high precision system reference.

All of these components are configured through a serial (SPI-compatible), 16-bit CFG register. Configuration and conversion results are read after the conversions are completed.

The ADAS3023 requires a minimum of three power supplies +15 V, -15 V, and +5 V. Internal low dropout regulators provide the necessary 2.5 V system voltages that must be decoupled externally via dedicated pins (ACAP, DCAP, and RCAP). The ADAS3023 can be interfaced to any 1.8 V to 5 V digital logic family using the dedicated VIO logic level voltage supply (see Table 9).

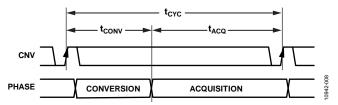

A rising edge on the CNV pin initiates a conversion and changes the ADAS3023 from track to hold. In this state, the ADAS3023 performs the analog signal conditioning and conversion. When the signal conditioning is completed, the ADAS3023 returns to the track state while, at the same time, quantizes the sample. This two-tiered process satisfies the necessary settling time requirement and achieves a fast throughput rate of up to 500 kSPS with 16-bit accuracy.

Figure 35. Simplified Block Diagram

Figure 36. System Timing

Regardless of the type of signal, (single-ended symmetric or asymmetric), the ADAS3023 converts all signals present on the enabled inputs and COM pin in a differential fashion identical to an industry-standard difference or instrumentation amplifier.

The conversion results are available after the conversion is complete and can be read back at any time before the end of the next conversion. Avoid reading back data during the quiet period, indicated by BUSY/SDO2 being active high. Because the ADAS3023 has an on-board conversion clock, the serial clock (SCK) is not required for the conversion process; it is only required to present results to the user.

#### TRANSFER FUNCTIONS

The ideal transfer characteristic for the ADAS3023 is shown in Figure 37. The inputs are configured for differential input ranges and the data outputs are in twos complement format, as listed in Table 6.

Figure 37. ADC Ideal Transfer Function

Table 6. Output Codes and Ideal Input Voltages

| Description      | Differential Analog Inputs, V <sub>REF</sub> = 4.096 V | Digital Output Code<br>(Twos Complement Hex) |

|------------------|--------------------------------------------------------|----------------------------------------------|

| FSR – 1 LSB      | (32,767 × V <sub>REF</sub> )/(32,768 × PGIA gain)      | 0x7FFF                                       |

| Midscale + 1 LSB | (V <sub>REF</sub> /(32,768 × PGIA gain))               | 0x0001                                       |

| Midscale         | 0                                                      | 0x0000                                       |

| Midscale – 1 LSB | -(V <sub>REF</sub> /(32,768 × PGIA gain))              | 0xFFFF                                       |

| −FSR + 1 LSB     | $-(32,767 \times V_{REF})/(32,768 \times PGIA gain)$   | 0x8001                                       |

| –FSR             | −V <sub>REF</sub> × PGIA gain                          | 0x8000                                       |

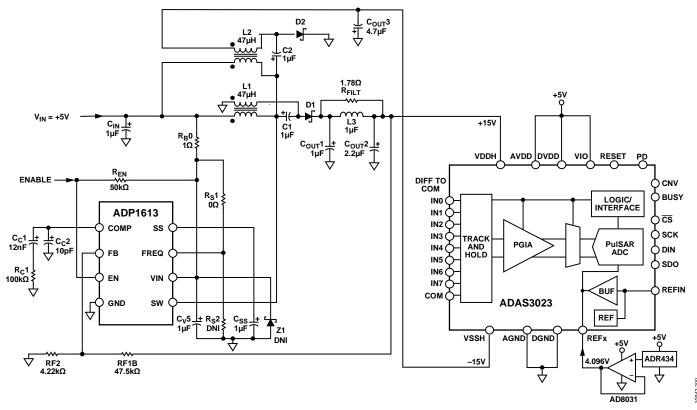

Figure 38. Complete 5 V, Single-Supply, 8-Channel Data Acquisition System with PGIA

#### TYPICAL APPLICATION CONNECTION DIAGRAM

As shown in Figure 38, the ADP1613 is used in an inexpensive SEPIC-Ćuk topology, which is an ideal candidate for providing the ADAS3023 with the necessary high voltage ±15 V robust supplies (at 20 mA) and low output ripple (3 mV maximum) from an external 5 V supply. The ADP1613 satisfies the specification requirements of the ADAS3023 using minimal external components yet achieves greater than 86% efficiency. See the CN-0201 circuit note for complete information about this test setup.

#### **ANALOG INPUTS**

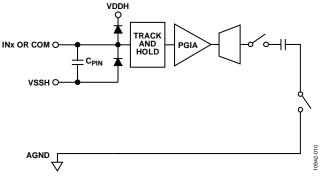

#### **Input Structure**

The ADAS3023 uses a differential input structure between each of the channel inputs, IN0 to IN7, and a common reference (COM), all of which sample simultaneously.

Figure 39 shows an equivalent circuit of the inputs. The diodes provide ESD protection for the analog inputs (IN0 to IN7) and COM from the high voltage supplies (VDDH and VSSH). Ensure that the analog input signal does not exceed the supply rails by more than 0.3 V because this can cause the diodes to become forward-biased and to start conducting current. The voltages beyond the absolute maximum ratings may cause permanent damage to the ADAS3023 (see Table 4).

Figure 39. Equivalent Analog Input Circuit

#### **Programmable Gain**

The ADAS3023 incorporates a programmable gain instrumentation amplifier (PGIA) with four selectable ranges. The PGIA settings are specified in terms of the maximum absolute differential input voltage across an input pin and the COM pin, for example INx to COM. The power on and default conditions are preset to the  $\pm 20.48$  V (PGIA = 11) input range.

Note that because the ADAS3023 can use any input type, such as bipolar single-ended and pseudo bipolar, setting the PGIA is important to make full use of the allowable input span.

Table 7 describes each differential input range and the corresponding LSB size, PGIA bit settings, and PGIA gain.

Table 7. Differential Input Ranges, LSB Size, and PGIA Settings

| Differential Input Ranges,<br>INx – COM (V) | LSB (μV) | PGIA<br>CFG | PGIA<br>Gain<br>(V/V) |

|---------------------------------------------|----------|-------------|-----------------------|

| ±20.48                                      | 625      | 11          | 0.2                   |

| ±10.24                                      | 312.5    | 00          | 0.4                   |

| ±5.12                                       | 156.3    | 01          | 0.8                   |

| ±2.56                                       | 78.13    | 10          | 1.6                   |

#### **Common-Mode Operating Range**

The differential input common-mode range changes according to the input range selected for a given channel and the high voltage power supplies. Note that the operating input voltage of any input pin, as defined in the Specifications section, requires a minimum of 2.5 V of headroom from the VDDH/VSSH supplies or

$$(VSSH + 2.5 \text{ V}) \leq INx/COM \leq (VDDH - 2.5 \text{ V})$$

The following sections offer some examples of setting the PGIA for various input signals. Note that the ADAS3023 always takes the difference between the INx and COM signals.

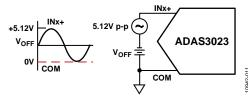

# Single-Ended Signals with a Nonzero DC Offset (Asymmetrical)

When a 5.12~V p-p signal with a 2.56~V dc offset is connected to one of the inputs (INx+) and the dc ground sense of the signal is connected to COM, the PGIA gain configuration is set to 01 for the  $\pm 5.12~V$  range because the maximum differential voltage across the inputs is  $\pm 5.12~V$ . This scenario uses only half the codes available for the transfer function.

Figure 40. Typical Single-Ended Unipolar Input Using Only Half of the Codes

#### Single-Ended Signals with a 0 V DC Offset (Symmetrical)

Compared with the example in the Single-Ended Signals with a Nonzero DC Offset (Asymmetrical) section, a better solution for single-ended signals, when possible, is to remove as much differential dc offset between INx and COM such that the average voltage is 0 V (symmetrical around the ground sense). The differential voltage across the inputs is never greater than  $\pm 2.56$  V, and the PGIA gain configuration is set for a  $\pm 2.56$  V range (10). This scenario uses all of the codes available for the transfer function, making full use of the allowable differential input range.

Figure 41. Optimal Single-Ended Configuration Using All Codes

Notice that the voltages in the examples are not integer values due to the 4.096 V reference and the scaling ratios of the PGIA. The maximum allowed dc offset voltage on the COM input pin for various PGIA gains in this case is shown in Table 8.

Table 8. DC Offset Voltage on COM Input and PGIA Settings<sup>1</sup>

| PGIA Gain (V/V) | DC Offset Voltage on COM (V) |

|-----------------|------------------------------|

| 0.2             | 0                            |

| 0.4             | 0                            |

| 0.8             | ±5.12                        |

| 1.6             | ±7.68                        |

| 1.6             | ±7.68                        |

<sup>&</sup>lt;sup>1</sup> Full-scale signal on INx.

#### **VOLTAGE REFERENCE INPUT/OUTPUT**

The ADAS3023 allows the choice of an internal reference, an external reference using an internal buffer, or an external reference.

The internal reference of the ADAS3023 provides excellent performance and can be used in nearly any application. Setting the reference selection mode uses the internal reference enable bit, REFEN, and the REFIN pin as described in the following sections (Internal Reference, External Reference and Internal Buffer, External Reference, and Reference Decoupling).

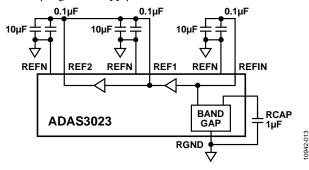

#### Internal Reference

The precision internal reference is factory trimmed and is suitable for most applications.

Setting the REFEN bit in the CFG register to 1 (default) enables the internal reference and produces 4.096 V on the REF1 and REF2 pins; this 4.096 V output serves as the main system reference. The unbuffered 2.5 V (typical) band gap reference voltage is output on the REF1N pin, which requires an external parallel combination of 10  $\mu F$  and 0.1  $\mu F$  capacitors to reduce the noise on the output. Because the current output of REF1N is limited, it can be used as a source when followed by a suitable buffer, such as the AD8031. Note that excessive loading of the REF1N output lowers the 4.096 V system reference because the internal amplifier uses a fixed gain.

The internal reference output is trimmed to the targeted value of 4.096 V with an initial accuracy of  $\pm 8$  mV. The reference is also temperature compensated to provide a typical drift of  $\pm 5$  ppm/°C.

When the internal reference is used, decouple the ADAS3023, as shown in Figure 42. Note that both the REF1 and REF2 connections are shorted together and externally decoupled with

suitable decoupling on the REFIN output and the RCAP internally regulated supply.

Figure 42. 4.096V Internal Reference Connection

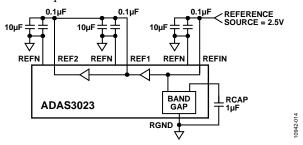

#### **External Reference and Internal Buffer**

The external reference and internal buffer are useful where a common system reference is used or when improved drift performance is required.

Setting Bit REFEN to 0 disables the internal band gap reference, allowing the user to provide an external voltage reference (2.5 V typical) to the REFIN pin. The internal buffer remains enabled, thus reducing the need for an external buffer amplifier to generate the main system reference. Where REFIN = 2.5 V and REF1 and REF2 output 4.096 V, this serves as the main system reference.

For this configuration, connect the external source, as shown in Figure 43. Any type of 2.5 V reference can be used in this configuration (low power, low drift, small package, and so forth) because the internal buffer handles the dynamics of the ADAS3023 reference requirements.

Figure 43. External Reference Using Internal Buffer

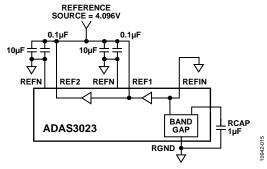

#### **External Reference**

For applications that require a precise, low drift, 4.096 V reference, an external reference can be used. Note that in this mode, disabling the internal buffer requires setting REFEN to 0, and driving or connecting REFIN to AGND; thus, both hardware and software control are necessary. Attempting to drive the REF1 and REF2 pins alone prior to disabling the internal buffer can cause source/sink contention in the outputs of the driving amplifiers.

Connect the precision 4.096 V reference directly to REF1 and REF2, which are the main system reference (see Figure 44); two recommended references are the ADR434 or ADR444.

If an op amp is used as an external reference source, take note of the concerns regarding driving capacitive loads. Capacitive loading for op amps usually refers to the ability of the amplifier to remain marginally stable in ac applications but can also play a role in dc applications, such as a reference source.