# Octal LNA/VGA/AAF/ADC and Crosspoint Switch

AD9273

#### **FEATURES**

8 channels of LNA, VGA, AAF, and ADC

Low noise preamplifier (LNA)

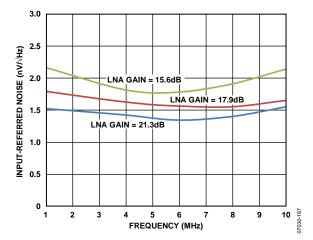

Input-referred noise voltage = 1.26 nV/√Hz

(gain = 21.3 dB) @ 5 MHz typical

SPI-programmable gain = 15.6 dB/17.9 dB/21.3 dB

Single-ended input; V<sub>IN</sub> maximum = 733 mV p-p/

550 mV p-p/367 mV p-p

Dual-mode active input impedance matching

Bandwidth (BW) > 100 MHz

Full-scale (FS) output = 4.4 V p-p differential

Variable gain amplifier (VGA)

Attenuator range = −42 dB to 0 dB

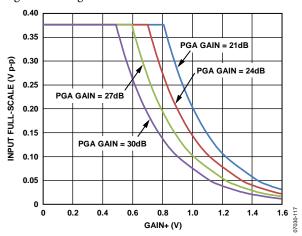

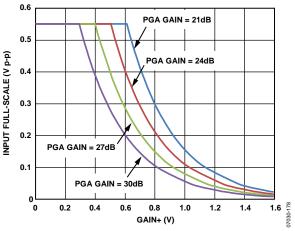

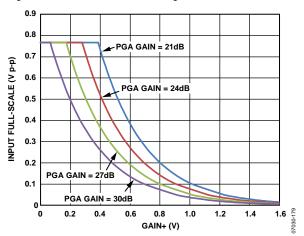

SPI-programmable PGA gain = 21 dB/24 dB/27 dB/30 dB

Antialiasing filter (AAF)

Programmable 2nd-order low-pass filter (LPF) from

8 MHz to 18 MHz Programmable high-pass filter (HPF)

Analog-to-digital converter (ADC)

12 bits at 10 MSPS to 50 MSPS

CND 70-ID

Linear-in-dB gain control

SNR = 70 dB SFDR = 75 dB

Serial LVDS (ANSI-644, IEEE 1596.3 reduced range link)

Data and frame clock outputs

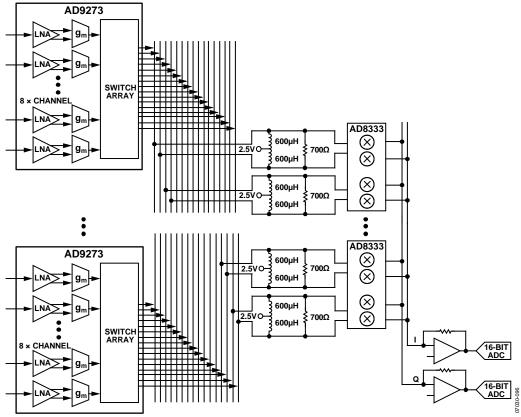

Includes an 8  $\times$  8 differential crosspoint switch to support continuous wave (CW) Doppler

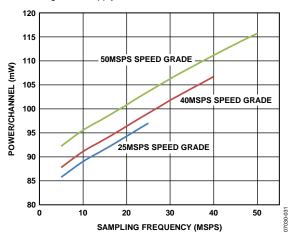

Low power, 109 mW per channel at 12 bits/40 MSPS (TGC)

70 mW per channel in CW Doppler

Flexible power-down modes

Overload recovery in <10 ns

Fast recovery from low power standby mode, <2  $\mu s$

100-lead TQFP and 144-ball BGA

#### **APPLICATIONS**

Medical imaging/ultrasound Automotive radar

### **GENERAL DESCRIPTION**

The AD9273 is designed for low cost, low power, small size, and ease of use. It contains eight channels of a low noise preamplifier (LNA) with a variable gain amplifier (VGA); an antialiasing filter (AAF); and a 12-bit, 10 MSPS to 50 MSPS analog-to-digital converter (ADC).

Each channel features a variable gain range of 42 dB, a fully differential signal path, an active input preamplifier termination, a maximum gain of up to 52 dB, and an ADC with a conversion rate of up to 50 MSPS. The channel is optimized for dynamic performance and low power in applications where a small package size is critical.

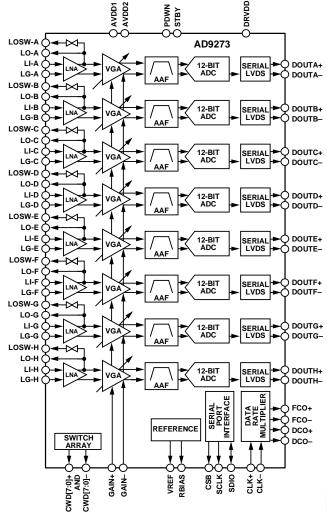

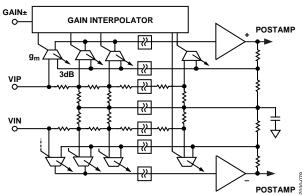

#### FUNCTIONAL BLOCK DIAGRAM

Figure 1.

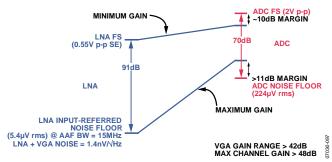

The LNA has a single-ended-to-differential gain that is selectable through the SPI. The LNA input-referred noise voltage is typically 1.26 nV/ $\sqrt{\rm Hz}$  at a gain of 21.3 dB, and the combined input-referred noise voltage of the entire channel is 1.42 nV/ $\sqrt{\rm Hz}$  at typical gain. Assuming a 15 MHz noise bandwidth (NBW) and a 21.3 dB LNA gain, the input SNR is about 91 dB. In CW Doppler mode, the LNA output drives a transconductance amp that is switched through an 8  $\times$  8 differential crosspoint switch. The switch is programmable through the SPI.

# **AD9273\* Product Page Quick Links**

Last Content Update: 08/30/2016

### Comparable Parts

View a parametric search of comparable parts

### Evaluation Kits <a> □</a>

· AD9273 Evaluation Board

### Documentation <a>□</a>

### **Application Notes**

- AN-1142: Techniques for High Speed ADC PCB Layout

- AN-586: LVDS Outputs for High Speed A/D Converters

- AN-737: How ADIsimADC Models an ADC

- AN-812: MicroController-Based Serial Port Interface (SPI) Boot Circuit

- AN-835: Understanding High Speed ADC Testing and Evaluation

- AN-877: Interfacing to High Speed ADCs via SPI

- AN-878: High Speed ADC SPI Control Software

- AN-905: Visual Analog Converter Evaluation Tool Version 1 0 User Manual

- AN-935: Designing an ADC Transformer-Coupled Front End

#### **Data Sheet**

AD9273: Octal LNA/VGA/AAF/ADC and Crosspoint Switch Data Sheet

### Software and Systems Requirements <a> □</a>

• UG-001: Evaluation Board User Guide

### Tools and Simulations

- Visual Analog

- AD9273 IBIS Models

### Reference Materials

#### **Press**

- Industry's First Octal Ultrasound Receiver with Digital I/Q Demodulator and Decimation Filter Reduces Processor Overhead in Ultrasound Systems

- Low Cost, Octal Ultrasound Receiver with On-Chip RF Decimator and JESD204B Serial Interface

### **Technical Articles**

- MS-2210: Designing Power Supplies for High Speed ADC

- New Components Offer Fexibility in Ultrasound System Design

- · Processors for Ultrasound Improve Image Quality

### Design Resources <a> □</a>

- · AD9273 Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### Discussions <a>□</a>

View all AD9273 EngineerZone Discussions

## Sample and Buy

Visit the product page to see pricing options

### Technical Support <a> </a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

| TABLE OF CONTENTS                                        |                                                           |    |

|----------------------------------------------------------|-----------------------------------------------------------|----|

| Features                                                 | Theory of Operation                                       | 21 |

| Applications1                                            | Ultrasound                                                | 21 |

| General Description                                      | Channel Overview                                          | 22 |

| Functional Block Diagram 1                               | Input Overdrive                                           | 25 |

| Revision History                                         | CW Doppler Operation                                      | 25 |

| Product Highlights                                       | TGC Operation                                             | 27 |

| Specifications                                           | ADC                                                       | 3  |

| AC Specifications4                                       | Clock Input Considerations                                | 31 |

| Digital Specifications8                                  | Serial Port Interface (SPI)                               | 38 |

| Switching Specifications9                                | Hardware Interface                                        | 38 |

| ADC Timing Diagrams                                      | Memory Map                                                | 40 |

| Absolute Maximum Ratings11                               | Reading the Memory Map Table                              | 40 |

| Thermal Impedance11                                      | Reserved Locations                                        | 40 |

| ESD Caution11                                            | Default Values                                            | 40 |

| Pin Configuration and Function Descriptions              | Logic Levels                                              | 40 |

| Typical Performance Characteristics                      | Outline Dimensions                                        |    |

| Equivalent Circuits                                      | Ordering Guide                                            | 45 |

| REVISION HISTORY                                         |                                                           |    |

| 7/09—Rev. A to Rev. B                                    | Changes to Ultrasound Section                             | 21 |

| Added BGA PackageUniversal                               | Changes to Low Noise Amplifier (LNA) Section              | 22 |

| Changes to Features and General Description Sections     | Changes to Active Impedance Matching Section and          | 2  |

| Changes to Product Highlights Section                    | Figure 40 Changes to LNA Noise Section                    |    |

| Changes to Full-Channel (TGC) Characteristics Parameter, | Changes to Input Overload Protection Section and Figure 4 |    |

| Table 1                                                  | Changes to Figure 48                                      |    |

| Changes to Gain Control Interface Parameter and to CW    | Changes to Figure 49 and Figure 50                        |    |

| Doppler Mode Parameter, Table 1                          | Changes to Clock Input Considerations Section and to      |    |

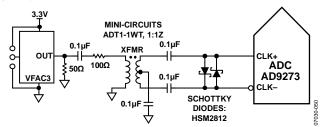

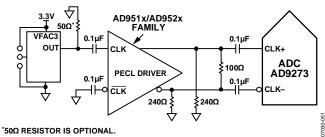

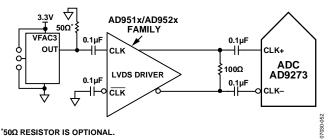

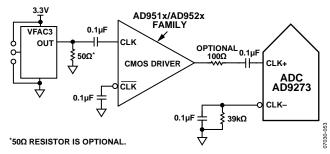

| Parameter                                                | Figure 56 to Figure 59                                    | 31 |

| Changes to Figure 2 and Figure 3                         | Changes to Digital Outputs and Timing Section             |    |

| Changes to Table 4                                       | Changes to CSB Pin Section                                |    |

| Addded Figure 5; Renumbered Sequentially                 | Changes to Reading the Memory Map Table Section           |    |

| Changes to Table 6                                       | Updated Outline Dimensions                                |    |

| Changes to Figure 34 and Figure 35                       | Changes to Ordering Guide                                 |    |

| Changes to rigure 34 and rigure 33                       | 4/09—Revision A: Initial Version                          |    |

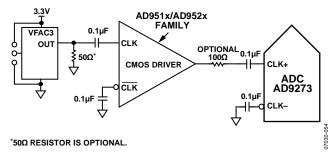

The AD9273 requires a LVPECL-/CMOS-/LVDS-compatible sample rate clock for full performance operation. No external reference or driver components are required for many applications.

The ADC automatically multiplies the sample rate clock for the appropriate LVDS serial data rate. A data clock (DCO±) for capturing data on the output and a frame clock (FCO±) trigger for signaling a new output byte are provided.

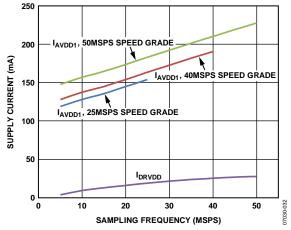

Powering down individual channels is supported to increase battery life for portable applications. There is also a standby mode option that allows quick power-up for power cycling. In CW Doppler operation, the VGA, AAF, and ADC are powered down. The power of the time gain control (TGC) path scales with selectable speed grades.

The ADC contains several features designed to maximize flexibility and minimize system cost, such as a programmable clock, data alignment, and programmable digital test pattern generation. The digital test patterns include built-in fixed patterns, built-in pseudorandom patterns, and custom user-defined test patterns entered via the serial port interface.

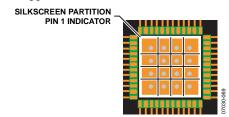

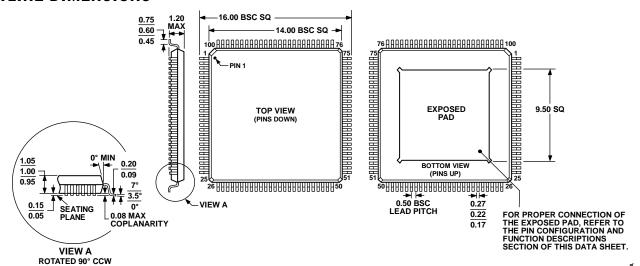

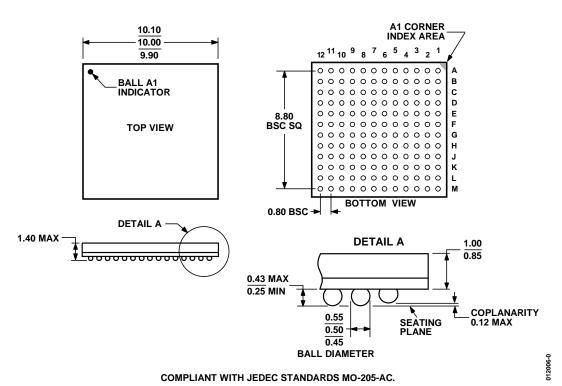

Fabricated in an advanced CMOS process, the AD9273 is available in a 16 mm  $\times$  16 mm, RoHS compliant, 100-lead TQFP or a 144-ball BGA. It is specified over the industrial temperature range of  $-40^{\circ}$ C to  $+85^{\circ}$ C.

### **PRODUCT HIGHLIGHTS**

- 1. Small Footprint. Eight channels are contained in a small, space-saving package. A full TGC path, ADC, and crosspoint switch contained within a 100-lead,  $16 \text{ mm} \times 16 \text{ mm}$  TQFP or a 144-ball BGA.

- 2. Low Power of 109 mW per Channel at 40 MSPS.

- Integrated Crosspoint Switch. This switch allows numerous multichannel configuration options to enable the CW Doppler mode.

- 4. Ease of Use. A data clock output (DCO±) operates up to 300 MHz and supports double data rate (DDR) operation.

- 5. User Flexibility. Serial port interface (SPI) control offers a wide range of flexible features to meet specific system requirements.

- 6. Integrated Second-Order Antialiasing Filter. This filter is placed between the VGA and the ADC and is programmable from 8 MHz to 18 MHz.

# **SPECIFICATIONS**

### **AC SPECIFICATIONS**

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference,  $f_{IN}$  = 5 MHz,  $R_S$  = 50  $\Omega$ , LNA gain = 21.3 dB, LNA bias =mid-high (default), PGA gain = 24 dB, GAIN- = 0.8 V, AAF LPF cutoff =  $f_{SAMPLE}/3$  (default), HPF = LPF cutoff/20.7 (default), full temperature, ANSI-644 LVDS mode, unless otherwise noted.

Table 1.

|                                       |                                                                                                                   | AD9273-25 |                  |     | AD9273-40 |                  |     | AD9273-50 |                  |     |                           |

|---------------------------------------|-------------------------------------------------------------------------------------------------------------------|-----------|------------------|-----|-----------|------------------|-----|-----------|------------------|-----|---------------------------|

| Parameter <sup>1</sup>                | Conditions                                                                                                        | Min       | Тур              | Max | Min       | Тур              | Max | Min       | Тур              | Max | Unit                      |

| LNA CHARACTERISTICS                   |                                                                                                                   |           |                  |     |           |                  |     |           |                  |     |                           |

| Gain                                  | Single-ended<br>input to<br>differential<br>output                                                                |           | 15.6/17.9/21.3   |     |           | 15.6/17.9/21.3   |     |           | 15.6/17.9/21.3   |     | dB                        |

|                                       | Single-ended<br>input to<br>single-ended<br>output                                                                |           | 9.6/11.9/15.3    |     |           | 9.6/11.9/15.3    |     |           | 9.6/11.9/15.3    |     | dB                        |

| Input Voltage Range                   | LNA gain =<br>15.6 dB/<br>17.9 dB/<br>21.3 dB,<br>LNA output<br>limited to<br>4.4 V p-p<br>differential<br>output |           | 733/550/367      |     |           | 733/550/367      |     |           | 733/550/367      |     | mV p-p<br>SE <sup>2</sup> |

| Input Common<br>Mode                  |                                                                                                                   |           | 0.9              |     |           | 0.9              |     |           | 0.9              |     | V                         |

| Input Resistance                      | $R_{FB} = 250 \Omega$                                                                                             |           | 50               |     |           | 50               |     |           | 50               |     | Ω                         |

|                                       | $R_{FB} = 500 \Omega$                                                                                             |           | 100              |     |           | 100              |     |           | 100              |     | Ω                         |

|                                       | $R_{FB} = \infty$                                                                                                 |           | 15               |     |           | 15               |     |           | 15               |     | kΩ                        |

| Input Capacitance                     | LI-x                                                                                                              |           | 22               |     |           | 22               |     |           | 22               |     | pF                        |

| -3 dB Bandwidth                       |                                                                                                                   |           | 70               |     |           | 70               |     |           | 70               |     | MHz                       |

| Input-Referred<br>Noise Voltage       | LNA gain = 15.6 dB/<br>17.9 dB/<br>21.3 dB,<br>$R_S = 0 \Omega$ ,<br>$R_{FB} = \infty$                            |           | 1.6/1.42/1.26    |     |           | 1.6/1.42/1.26    |     |           | 1.6/1.42/1.26    |     | nV/√Hz                    |

| Input Noise Current                   | R <sub>FB</sub> = ∞                                                                                               |           | 1                |     |           | 1                |     |           | 1                |     | pA/√Hz                    |

| 1 dB Input Com-<br>pression Point     | LNA gain =<br>15.6 dB/<br>17.9 dB/<br>21.3 dB,<br>GAIN+ = 0 V                                                     |           | 1.0/0.8/0.5      |     |           | 1.0/0.8/0.5      |     |           | 1.0/0.8/0.5      |     | mV p-p                    |

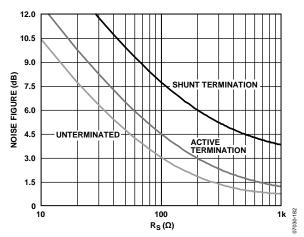

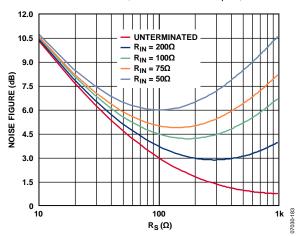

| Noise Figure                          | LNA gain =<br>15.6 dB/<br>17.9 dB/<br>21.3 dB                                                                     |           |                  |     |           |                  |     |           |                  |     |                           |

| Active Termina-<br>tion Matched       | $R_S = 50 \Omega$ ,<br>$R_{FB} = 200 \Omega$ /<br>$250 \Omega/350 \Omega$                                         |           | 5.8/5.1/4.3      |     |           | 5.8/5.1/4.3      |     |           | 5.8/5.1/4.3      |     | dB                        |

| Unterminated                          | $R_{FB} = \infty$                                                                                                 |           | 6.3/5.3/4.4      |     |           | 6.3/5.3/4.4      |     |           | 6.3/5.3/4.4      |     | dB                        |

| FULL-CHANNEL (TGC)<br>CHARACTERISTICS |                                                                                                                   |           |                  |     |           |                  |     |           |                  |     |                           |

| AAF Low-Pass Filter<br>Cutoff         | In range, –3 dB,<br>programmable                                                                                  |           | 8 to 18          |     |           | 8 to 18          |     |           | 8 to 18          |     | MHz                       |

|                                       | Out of range, <sup>3</sup> -3 dB, pro- grammable, >>AAF band- width tolerance                                     |           | 5 to 8, 18 to 35 |     |           | 5 to 8, 18 to 35 |     |           | 5 to 8, 18 to 35 |     | MHz                       |

|                                              |                                                                                                                                                             |     | AD9273-25       |     |     | AD9273-40      |     |     | AD9273-50      |     |         |

|----------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|-----------------|-----|-----|----------------|-----|-----|----------------|-----|---------|

| Parameter <sup>1</sup>                       | Conditions                                                                                                                                                  | Min | Тур             | Max | Min | Тур            | Max | Min | Тур            | Max | Unit    |

| AAF Bandwidth<br>Tolerance                   | In range                                                                                                                                                    |     | ±10             |     |     | ±10            |     |     | ±10            |     | %       |

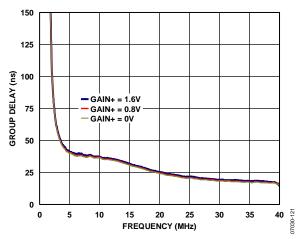

| Group Delay<br>Variation                     | f = 1 MHz to<br>18 MHz,<br>GAIN+ = 0 V to<br>1.6 V                                                                                                          |     | ±2              |     |     | ±2             |     |     | ±2             |     | ns      |

| Input-Referred<br>Noise Voltage              | LNA gain =<br>15.6 dB/<br>17.9 dB/<br>21.3 dB,<br>R <sub>FB</sub> = ∞                                                                                       |     | 1.94/1.64/1.38  |     |     | 1.94/1.64/1.38 |     |     | 1.94/1.64/1.38 |     | nV/√Hz  |

| Noise Figure                                 | LNA gain =<br>15.6 dB/<br>17.9 dB/<br>21.3 dB                                                                                                               |     |                 |     |     |                |     |     |                |     |         |

| Active Termina-<br>tion Matched              | $\begin{aligned} R_S &= 50 \ \Omega, \\ R_{FB} &= 200 \ \Omega/ \\ 250 \ \Omega/350 \ \Omega \end{aligned}$                                                 |     | 10.3/8.7/6.8    |     |     | 10.3/8.6/6.7   |     |     | 10.3/8.6/6.7   |     | dB      |

| Unterminated                                 | R <sub>FB</sub> = ∞                                                                                                                                         |     | 7.1/6.0/4.8     |     |     | 7.1/5.9/4.8    |     |     | 7.1/5.9/4.8    |     | dB      |

| Correlated Noise<br>Ratio                    | No signal,<br>correlated/<br>uncorrelated                                                                                                                   |     | -30             |     |     | -30            |     |     | -30            |     | dB      |

| Output Offset                                |                                                                                                                                                             | -35 |                 | +35 | -35 |                | +35 | -35 |                | +35 | LSB     |

| Signal-to-Noise<br>Ratio (SNR)               | $f_{IN} = 5 \text{ MHz at}$<br>-10 dBFS,<br>GAIN+ = 0 V                                                                                                     |     | 65.5            |     |     | 64             |     |     | 63.5           |     | dBFS    |

|                                              | $f_{IN} = 5 \text{ MHz at}$<br>-1 dBFS,<br>GAIN+ = 1.6 V                                                                                                    |     | 58.5            |     |     | 57             |     |     | 56.5           |     | dBFS    |

| Harmonic Distortion                          |                                                                                                                                                             |     |                 |     |     |                |     |     |                |     |         |

| Second<br>Harmonic                           | f <sub>IN</sub> = 5 MHz at<br>-10 dBFS,<br>GAIN+ = 0 V                                                                                                      |     | <b>–</b> 55     |     |     | <b>-52</b>     |     |     | <b>-52</b>     |     | dBc     |

|                                              | $f_{IN} = 5 \text{ MHz at}$<br>-1 dBFS,<br>GAIN+ = 1.6 V                                                                                                    |     | -67             |     |     | -62            |     |     | -58            |     | dBc     |

| Third Harmonic                               | $f_{IN} = 5 \text{ MHz at}$<br>-10 dBFS,<br>GAIN+ = 0 V                                                                                                     |     | -56             |     |     | -50            |     |     | <b>-47</b>     |     | dBc     |

|                                              | f <sub>IN</sub> = 5 MHz at<br>-1 dBFS,<br>GAIN+ = 1.6 V                                                                                                     |     | -61             |     |     | <b>–</b> 56    |     |     | <b>-55</b>     |     | dBc     |

| Two-Tone IMD3<br>(2 × F1 – F2)<br>Distortion | $f_{\text{IN1}} = 5.0  \text{MHz}$ at $-1  \text{dBFS}$ , $f_{\text{IN2}} = 5.01  \text{MHz}$ at $-21  \text{dBFS}$ , $GAIN+ = 1.6  V$ , LNA gain = 21.3 dB |     | <b>-75</b>      |     |     | <b>−75</b>     |     |     | <b>−75</b>     |     | dBc     |

| Channel-to-Channel<br>Crosstalk              | $f_{IN1} = 5.0 \text{ MHz at}$<br>-1 dBFS                                                                                                                   |     | -70             |     |     | -70            |     |     | -70            |     | dB      |

|                                              | Overrange condition <sup>4</sup>                                                                                                                            |     | <del>-</del> 65 |     |     | -65            |     |     | -65            |     | dB      |

| Channel-to-Channel<br>Delay Variation        | Full TGC path,<br>$f_{IN} = 5 \text{ MHz}$ ,<br>GAIN+ = 0  V to<br>1.6 V                                                                                    |     | 0.3             |     |     | 0.3            |     |     | 0.3            |     | Degrees |

| PGA GAIN                                     | Differential input to differential output                                                                                                                   |     | 21/24/27/30     |     |     | 21/24/27/30    |     |     | 21/24/27/30    |     | dB      |

|                                              |                                                                                                                                                                            |      | AD9273-25    |      |      | AD9273-40    |      |      | AD9273-50    |      |          |

|----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|--------------|------|------|--------------|------|------|--------------|------|----------|

| Parameter <sup>1</sup>                       | Conditions                                                                                                                                                                 | Min  | Тур          | Max  | Min  | Тур          | Max  | Min  | Тур          | Max  | Unit     |

| GAIN ACCURACY                                | 25°C                                                                                                                                                                       |      |              |      |      |              |      |      |              |      |          |

| Gain Law Confor-<br>mance Error              | 0 V < GAIN+<br>< 0.16 V                                                                                                                                                    |      | 1.5          |      |      | 1.5          |      |      | 1.5          |      | dB       |

| mance error                                  | 0.16 V < GAIN+<br>< 1.44 V                                                                                                                                                 | -1.6 |              | +1.6 | -1.6 |              | +1.6 | -1.7 |              | +1.7 | dB       |

|                                              | 1.44 V < GAIN+<br>< 1.6 V                                                                                                                                                  |      | -2.5         |      |      | -2.5         |      |      | -2.5         |      | dB       |

| Linear Gain Error                            | GAIN+ = 0.8 V,<br>normalized for<br>ideal AAF loss                                                                                                                         | -1.6 |              | +1.6 | -1.6 |              | +1.6 | -1.7 |              | +1.7 | dB       |

| Channel-to-Channel<br>Matching               | 0.16 V < GAIN+<br>< 1.44 V                                                                                                                                                 |      | 0.1          |      |      | 0.1          |      |      | 0.1          |      | dB       |

| GAIN CONTROL<br>INTERFACE                    |                                                                                                                                                                            |      |              |      |      |              |      |      |              |      |          |

| Normal Operating<br>Range                    |                                                                                                                                                                            | 0    |              | 1.6  | 0    |              | 1.6  | 0    |              | 1.6  | V        |

| Gain Range                                   | GAIN+ =<br>0 V to 1.6 V                                                                                                                                                    |      | 42           |      |      | 42           |      |      | 42           |      | dB       |

| Scale Factor                                 | 42 -15 -1                                                                                                                                                                  |      | 28           |      |      | 28           |      |      | 28           |      | dB/V     |

| Response Time                                | 42 dB change                                                                                                                                                               |      | 750          |      |      | 750<br>10    |      |      | 750          |      | ns       |

| Gain+ Impedance                              | Single ended<br>Single ended                                                                                                                                               |      | 10<br>70     |      |      | 10           |      |      | 10<br>70     |      | MΩ<br>kΩ |

| Gain-Impedance                               | Single ended                                                                                                                                                               |      | 70           |      |      | 70           |      |      | 70           |      | KL2      |

| CW DOPPLER MODE<br>Transconductance          | Differential,<br>LNA gain =<br>15.6 dB/<br>17.9 dB/                                                                                                                        |      | 5.4/7.3/10.9 |      |      | 5.4/7.3/10.9 |      |      | 5.4/7.3/10.9 |      | mA/V     |

|                                              | 21.3 dB                                                                                                                                                                    |      |              |      |      |              |      |      |              |      |          |

| Output Level Range                           | Differential,<br>CW Doppler<br>output pins                                                                                                                                 | 1.5  |              | 3.6  | 1.5  |              | 3.6  | 1.5  |              | 3.6  | V        |

| Input-Referred<br>Noise Voltage              | LNA gain =<br>15.6 dB/<br>17.9 dB/<br>21.3 dB,<br>$R_S = 0 \Omega$ ,<br>$R_{FB} = \infty$ ,<br>$R_L = 675 \Omega$                                                          |      | 2.6/2.1/1.6  |      |      | 2.6/2.1/1.6  |      |      | 2.6/2.1/1.6  |      | nV/√Hz   |

| Input-Referred<br>Dynamic Range              | LNA gain = 15.6 dB/<br>17.9 dB/<br>21.3 dB,<br>$R_S = 0 \Omega$ ,<br>$R_{FB} = \infty$                                                                                     |      | 160/159/158  |      |      | 160/159/158  |      |      | 160/159/158  |      | dBFS/√H  |

| Two-Tone IMD3<br>(2 × F1 – F2)<br>Distortion | $f_{\text{IN1}} = 5.0 \text{ MHz at}$<br>$-1 \text{ dBFS (FS at LNA input), } f_{\text{IN2}} = 5.01 \text{ MHz at}$<br>-21  dBFS (FS at LNA input), LNA<br>gain = 21.3  dB |      | -70          |      |      | -70          |      |      | -70          |      | dBc      |

| Output DC Bias                               | Single ended,<br>per channel                                                                                                                                               |      | 2.4          |      |      | 2.4          |      |      | 2.4          |      | mA       |

| Maximum Output<br>Swing                      | Single ended,<br>per channel                                                                                                                                               |      | ±2           |      |      | ±2           |      |      | ±2           |      | mA p-p   |

| POWER SUPPLY                                 |                                                                                                                                                                            |      |              |      |      |              |      |      |              | -    |          |

| AVDD1                                        |                                                                                                                                                                            | 1.7  | 1.8          | 1.9  | 1.7  | 1.8          | 1.9  | 1.7  | 1.8          | 1.9  | V        |

| AVDD2                                        |                                                                                                                                                                            | 2.7  | 3.0          | 3.6  | 2.7  | 3.0          | 3.6  | 2.7  | 3.0          | 3.6  | V        |

| DRVDD<br>I <sub>AVDD1</sub>                  | Full-channel                                                                                                                                                               | 1.7  | 1.8<br>158   | 1.9  | 1.7  | 1.8<br>186   | 1.9  | 1.7  | 1.8<br>223   | 1.9  | V<br>mA  |

|                                              | mode                                                                                                                                                                       |      |              |      |      |              |      | 1    |              |      | l        |

Rev. B | Page 6 of 48

| •                                         |                                                                 | AD9273-25 |     |     |     | AD9273-40 |     |     | AD9273-50 | •    |      |

|-------------------------------------------|-----------------------------------------------------------------|-----------|-----|-----|-----|-----------|-----|-----|-----------|------|------|

| Parameter <sup>1</sup>                    | Conditions                                                      | Min       | Тур | Max | Min | Тур       | Max | Min | Тур       | Max  | Unit |

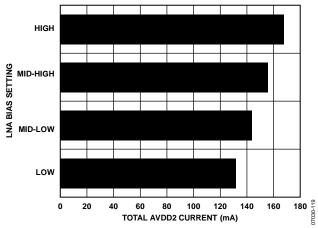

| I <sub>AVDD2</sub>                        | Full-channel<br>mode                                            |           | 150 |     |     | 150       |     |     | 150       |      | mA   |

|                                           | CW Doppler<br>mode with four<br>channels<br>enabled             |           | 70  |     |     | 70        |     |     | 70        |      | mA   |

| I <sub>DRVDD</sub>                        |                                                                 |           | 47  |     |     | 49        |     |     | 50        |      | mA   |

| Total Power<br>Dissipation                | Includes output<br>drivers, full-<br>channel mode,<br>no signal |           | 819 | 940 |     | 873       | 996 |     | 943       | 1072 | mW   |

|                                           | CW Doppler<br>mode with four<br>channels<br>enabled             |           | 275 |     |     | 275       |     |     | 275       |      | mW   |

| Power-Down<br>Dissipation                 |                                                                 |           |     | 5   |     |           | 5   |     |           | 5    | mW   |

| Standby Power Dissipation                 |                                                                 |           |     | 148 |     |           | 158 |     |           | 170  | mW   |

| Power Supply<br>Rejection Ratio<br>(PSRR) |                                                                 |           | 1.6 |     |     | 1.6       |     |     | 1.6       |      | mV/V |

| ADC RESOLUTION                            |                                                                 |           | 12  |     |     | 12        |     |     | 12        |      | Bits |

| ADC REFERENCE                             |                                                                 |           |     |     |     |           |     |     |           |      |      |

| Output Voltage Error                      | VREF = 1 V                                                      |           |     | ±20 |     |           | ±20 |     |           | ±20  | mV   |

| Load Regulation                           | At 1.0 mA,<br>VREF = 1 V                                        |           | 2   |     |     | 2         |     |     | 2         |      | mV   |

| Input Resistance                          |                                                                 |           | 6   |     |     | 6         |     |     | 6         |      | kΩ   |

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and how these tests were completed.

SE = single ended.

AAF settings < 5 MHz are out of range and are not supported.</li>

The overrange condition is specified as being 6 dB more than the full-scale input range.

### **DIGITAL SPECIFICATIONS**

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference,  $f_{IN} = 5 \text{ MHz}$ , full temperature, unless otherwise noted.

| Parameter <sup>1</sup>                                                              | Temperature | Min   | Тур         | Max         | Unit   |

|-------------------------------------------------------------------------------------|-------------|-------|-------------|-------------|--------|

| CLOCK INPUTS (CLK+, CLK-)                                                           |             |       | •           |             |        |

| Logic Compliance                                                                    |             |       | CMOS/LVDS/L | _VPECL      |        |

| Differential Input Voltage <sup>2</sup>                                             | Full        | 250   |             |             | mV p-p |

| Input Common-Mode Voltage                                                           | Full        |       | 1.2         |             | V      |

| Input Resistance (Differential)                                                     | 25°C        |       | 20          |             | kΩ     |

| Input Capacitance                                                                   | 25°C        |       | 1.5         |             | рF     |

| LOGIC INPUTS (PDWN, STBY, SCLK)                                                     |             |       |             |             |        |

| Logic 1 Voltage                                                                     | Full        | 1.2   |             | 3.6         | V      |

| Logic 0 Voltage                                                                     | Full        |       |             | 0.3         | V      |

| Input Resistance                                                                    | 25°C        |       | 30          |             | kΩ     |

| Input Capacitance                                                                   | 25°C        |       | 0.5         |             | рF     |

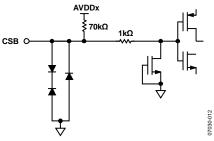

| LOGIC INPUT (CSB)                                                                   |             |       |             |             |        |

| Logic 1 Voltage                                                                     | Full        | 1.2   |             | 3.6         | V      |

| Logic 0 Voltage                                                                     | Full        |       |             | 0.3         | V      |

| Input Resistance                                                                    | 25°C        |       | 70          |             | kΩ     |

| Input Capacitance                                                                   | 25°C        |       | 0.5         |             | рF     |

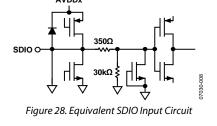

| LOGIC INPUT (SDIO)                                                                  |             |       |             |             |        |

| Logic 1 Voltage                                                                     | Full        | 1.2   |             | DRVDD + 0.3 | V      |

| Logic 0 Voltage                                                                     | Full        | 0     |             | 0.3         | V      |

| Input Resistance                                                                    | 25°C        |       | 30          |             | kΩ     |

| Input Capacitance                                                                   | 25°C        |       | 2           |             | рF     |

| LOGIC OUTPUT (SDIO) <sup>3</sup>                                                    |             |       |             |             |        |

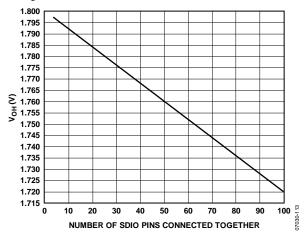

| Logic 1 Voltage (I <sub>OH</sub> = 800 μA)                                          | Full        |       | 1.79        |             | V      |

| Logic 0 Voltage ( $I_{OL} = 50 \mu A$ )                                             | Full        |       |             | 0.05        | V      |

| DIGITAL OUTPUTS (DOUTx+, DOUTx-) IN ANSI-644 MODE <sup>1</sup>                      |             |       |             |             |        |

| Logic Compliance                                                                    |             |       | LVDS        |             |        |

| Differential Output Voltage (VoD)                                                   | Full        | 247   |             | 454         | mV     |

| Output Offset Voltage (Vos)                                                         | Full        | 1.125 |             | 1.375       | V      |

| Output Coding (Default)                                                             |             |       | Offset bin  | ary         |        |

| DIGITAL OUTPUTS (DOUTx+, DOUTx–) WITH LOW POWER, REDUCED-SIGNAL OPTION <sup>1</sup> |             |       |             |             |        |

| Logic Compliance                                                                    |             |       | LVDS        |             |        |

| Differential Output Voltage (V <sub>OD</sub> )                                      | Full        | 150   |             | 250         | mV     |

| Output Offset Voltage (Vos)                                                         | Full        | 1.10  |             | 1.30        | V      |

| Output Coding (Default)                                                             |             |       | Offset bin  | ary         |        |

<sup>&</sup>lt;sup>1</sup> See the AN-835 Application Note, *Understanding High Speed ADC Testing and Evaluation*, for a complete set of definitions and how these tests were completed. <sup>2</sup> Specified for LVDS and LVPECL only. <sup>3</sup> Specified for 13 SDIO pins sharing the same connection.

### **SWITCHING SPECIFICATIONS**

AVDD1 = 1.8 V, AVDD2 = 3.0 V, DRVDD = 1.8 V, 1.0 V internal ADC reference,  $f_{IN} = 5 \text{ MHz}$ , full temperature, unless otherwise noted.

Table 3.

| Parameter <sup>1</sup>                                                | Temp | Min                     | Тур                         | Max                     | Unit         |

|-----------------------------------------------------------------------|------|-------------------------|-----------------------------|-------------------------|--------------|

| CLOCK <sup>2</sup>                                                    |      |                         |                             |                         |              |

| Clock Rate                                                            | Full | 10                      |                             | 50                      | MSPS         |

| Clock Pulse Width High (teh)                                          | Full |                         | 10                          |                         | ns           |

| Clock Pulse Width Low (tel)                                           | Full |                         | 10                          |                         | ns           |

| OUTPUT PARAMETERS <sup>2, 3</sup>                                     |      |                         |                             |                         |              |

| Propagation Delay (tpd)                                               | Full | $(t_{SAMPLE}/2) + 1.5$  | $(t_{SAMPLE}/2) + 2.3$      | $(t_{SAMPLE}/2) + 3.1$  | ns           |

| Rise Time (t <sub>R</sub> ) (20% to 80%)                              | Full |                         | 300                         |                         | ps           |

| Fall Time (t <sub>F</sub> ) (20% to 80%)                              | Full |                         | 300                         |                         | ps           |

| FCO± Propagation Delay (t <sub>FCO</sub> )                            | Full | $(t_{SAMPLE}/2) + 1.5$  | $(t_{SAMPLE}/2) + 2.3$      | $(t_{SAMPLE}/2) + 3.1$  | ns           |

| DCO± Propagation Delay (tcpd) <sup>4</sup>                            | Full |                         | $t_{FCO} + (t_{SAMPLE}/24)$ |                         | ns           |

| DCO± to Data Delay (t <sub>DATA</sub> ) <sup>4</sup>                  | Full | $(t_{SAMPLE}/24) - 300$ | $(t_{SAMPLE}/24)$           | $(t_{SAMPLE}/24) + 300$ | ps           |

| DCO± to FCO± Delay (t <sub>FRAME</sub> ) <sup>4</sup>                 | Full | $(t_{SAMPLE}/24) - 300$ | $(t_{SAMPLE}/24)$           | $(t_{SAMPLE}/24) + 300$ | ps           |

| Data-to-Data Skew<br>(t <sub>DATA-MAX</sub> — t <sub>DATA-MIN</sub> ) | Full |                         | ±100                        | ±350                    | ps           |

| Wake-Up Time (Standby), $GAIN+ = 0.8 V$                               | 25°C |                         | <2                          |                         | μs           |

| Wake-Up Time (Power-Down)                                             | 25°C |                         | 1                           |                         | ms           |

| Pipeline Latency                                                      | Full |                         | 8                           |                         | Clock cycles |

| APERTURE                                                              |      |                         |                             |                         |              |

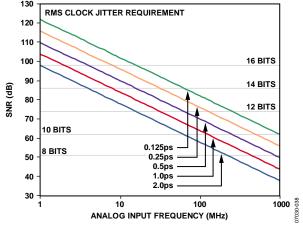

| Aperture Uncertainty (Jitter)                                         | 25°C |                         | <1                          |                         | ps rms       |

See the AN-835 Application Note, Understanding High Speed ADC Testing and Evaluation, for a complete set of definitions and how these tests were completed.

<sup>&</sup>lt;sup>2</sup> Can be adjusted via the SPI.

$<sup>^3</sup>$  Measurements were made using a part soldered to FR-4 material.  $^4$  ts\_AMPLE/24 is based on the number of bits divided by 2 because the delays are based on half duty cycles.

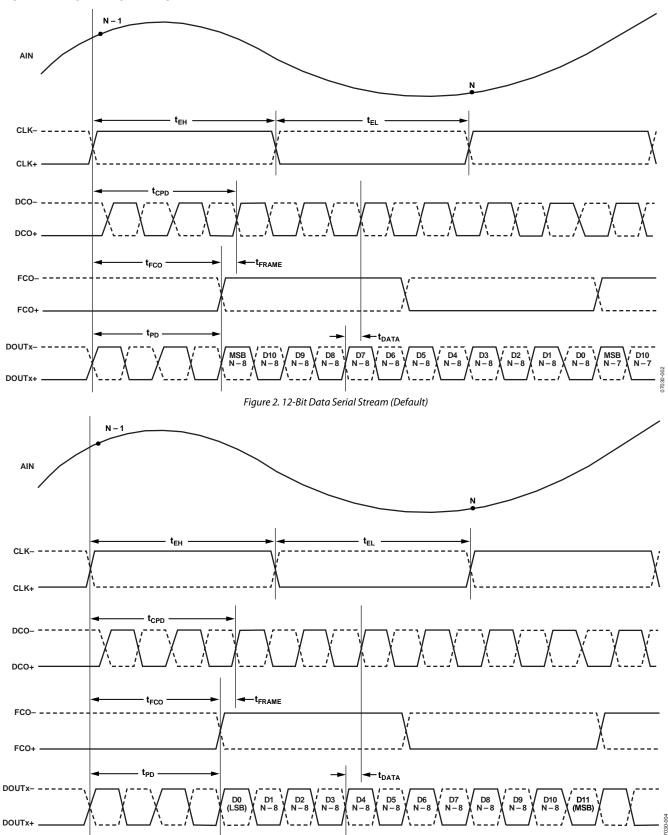

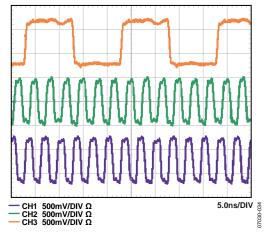

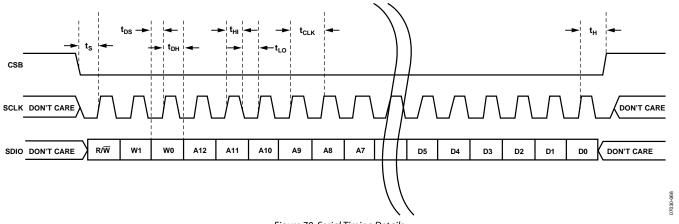

# **ADC TIMING DIAGRAMS**

Figure 3. 12-Bit Data Serial Stream, LSB First

### **ABSOLUTE MAXIMUM RATINGS**

Table 4.

| 14010 11                    |            | 1                |

|-----------------------------|------------|------------------|

|                             | With       |                  |

| Parameter                   | Respect To | Rating           |

| Electrical                  |            |                  |

| AVDD1                       | GND        | -0.3 V to +2.0 V |

| AVDD2                       | GND        | -0.3 V to +3.9 V |

| DRVDD                       | GND        | -0.3 V to +2.0 V |

| GND                         | GND        | -0.3 V to +0.3 V |

| AVDD2                       | AVDD1      | -2.0 V to +3.9 V |

| AVDD2                       | DRVDD      | -2.0 V to +3.9 V |

| AVDD1                       | DRVDD      | -2.0 V to +2.0 V |

| Digital Outputs             | GND        | -0.3 V to +2.0 V |

| (DOUTx+, DOUTx–,            |            |                  |

| DCO+, DCO-,                 |            |                  |

| FCO+, FCO-)                 | GND        | -0.3 V to +3.9 V |

| CLK+, CLK–, GAIN+,<br>GAIN– | GND        | -0.3 V to +3.9 V |

| LI-x, LO-x, LOSW-x          | LG-x       | -0.3 V to +2.0 V |

| CWDx-, CWDx+                | GND        | -0.3 V to +3.9 V |

| PDWN, STBY, SCLK, CSB       | GND        | -0.3 V to +3.9 V |

| RBIAS, VREF, SDIO           | GND        | -0.3 V to +2.0 V |

| Environmental               | GILE       | 0.5 7 10 12.0 7  |

| Operating Temperature       |            | −40°C to +85°C   |

| Range (Ambient)             |            | 10 2 10 103 2    |

| Storage Temperature         |            | −65°C to +150°C  |

| Range (Ambient)             |            |                  |

| Maximum Junction            |            | 150°C            |

| Temperature                 |            |                  |

| Lead Temperature            |            | 300°C            |

| (Soldering, 10 sec)         |            |                  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### THERMAL IMPEDANCE

Table 5.

| Airflow Velocity (m/sec) | $\theta_{JA}^{1}$ | θ <sub>ЈВ</sub> | θις | Unit |

|--------------------------|-------------------|-----------------|-----|------|

| 0.0                      | 20.3              | N/A             | N/A | °C/W |

| 1.0                      | 14.4              | 7.6             | 4.7 | °C/W |

| 2.5                      | 12.9              | N/A             | N/A | °C/W |

$<sup>^1</sup>$   $\theta_{JA}$  is for a 4-layer PCB with a solid ground plane (simulated). The exposed pad is soldered to the PCB.

### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

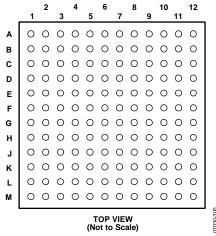

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES 1. THE EXPOSED PAD SHOULD BE TIED TO A QUIET ANALOG GROUND.

Figure 4. TQFP Pin Configuration

Figure 5. BGA Pin Configuration

**Table 6. Pin Function Descriptions**

| Pir                                         | n No.                                                                                                                                          |                  |                                                                     |

|---------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------|---------------------------------------------------------------------|

| TQFP                                        | BGA                                                                                                                                            | Name             | Description                                                         |

| 0                                           | N/A                                                                                                                                            | GND              | Ground (the exposed paddle should be tied to a quiet analog ground) |

| N/A                                         | B5, B6, B8, C5,<br>C6, C7, C8, D5,<br>D6, D7, D8, E1,<br>E5, E6, E7, E8,<br>E12, F2, F4, F6,<br>F7, F9, F11, G1,                               | GND              | Ground                                                              |

| 4, 10, 16, 22,<br>25, 50, 54, 60,<br>66, 72 | G3, G5, G6, G7,<br>G8, G10, G12,<br>H2, H3, H4, H5,<br>H6, H7, H8, H9,<br>H10, H11, J2,<br>K1, K2, M1, M12<br>F1, F3, F5, F8,<br>F10, F12, G2, | AVDD1            | 1.8 V Analog Supply                                                 |

| 3, 9, 15, 21, 55,<br>61, 67, 73, 86         | G4, G9, G11<br>B7, E2, E3, E4,<br>E9, E10, E11                                                                                                 | AVDD2            | 3.0 V Analog Supply                                                 |

| 26, 47                                      | L1, L12                                                                                                                                        | DRVDD            | 1.8 V Digital Output Driver Supply                                  |

| 1                                           | A1                                                                                                                                             | LI-E             | LNA Analog Input for Channel E                                      |

| 2                                           | B1                                                                                                                                             | LG-E             | LNA Ground for Channel E                                            |

| 5                                           | C2                                                                                                                                             | LO-F             | LNA Analog Inverted Output for Channel F                            |

| 6                                           | D2                                                                                                                                             | LOSW-F           | LNA Analog Switched Output for Channel F                            |

| 7                                           | A2                                                                                                                                             | LI-F             | LNA Analog Input for Channel F                                      |

| 8                                           | B2                                                                                                                                             | LG-F             | LNA Ground for Channel F                                            |

| 11                                          | C3                                                                                                                                             | LO-G             | LNA Analog Inverted Output for Channel G                            |

| 12                                          | D3                                                                                                                                             | LOSW-G           | LNA Analog Switched Output for Channel G                            |

| 13                                          | A3                                                                                                                                             | LI-G             | LNA Analog Input for Channel G                                      |

| 14                                          | В3                                                                                                                                             | LG-G             | LNA Ground for Channel G                                            |

| 17                                          | C4                                                                                                                                             | LO-H             | LNA Analog Inverted Output for Channel H                            |

| 18                                          | D4                                                                                                                                             | LOSW-H           | LNA Analog Switched Output for Channel H                            |

| 19                                          | A4                                                                                                                                             | LI-H             | LNA Analog Input for Channel H                                      |

| 20                                          | B4                                                                                                                                             | LG-H             | LNA Ground for Channel H                                            |

| 23                                          | H1                                                                                                                                             | CLK-             | Clock Input Complement                                              |

| 24                                          | J1                                                                                                                                             | CLK+             | Clock Input True                                                    |

| 27                                          | M2                                                                                                                                             | DOUTH-           | ADC H Digital Output Complement                                     |

| 28                                          | L2                                                                                                                                             | DOUTH+           | ADC H Digital Output True                                           |

| 29                                          | M3                                                                                                                                             | DOUTG-           | ADC G Digital Output Complement                                     |

| 30                                          | L3                                                                                                                                             | DOUTG+           | ADC G Digital Output True                                           |

| 31                                          | M4                                                                                                                                             | DOUTF-           | ADC F Digital Output Complement                                     |

| 32                                          | L4                                                                                                                                             | DOUTF+           | ADC F Digital Output True                                           |

| 33                                          | M5                                                                                                                                             | DOUTE-           | ADC E Digital Output Complement                                     |

| 34                                          | L5                                                                                                                                             | DOUTE+           | ADC E Digital Output True                                           |

| 35                                          | M6                                                                                                                                             | DCO-             | Digital Clock Output Complement                                     |

| 36<br>37                                    | L6                                                                                                                                             | DCO+             | Digital Clock Output True                                           |

| 37                                          | M7                                                                                                                                             | FCO-             | Frame Clock Digital Output Complement                               |

| 38                                          | L7                                                                                                                                             | FCO+             | Frame Clock Digital Output True                                     |

| 39<br>40                                    | M8                                                                                                                                             | DOUTD-           | ADC D Digital Output True                                           |

| 40<br>41                                    | L8<br>M9                                                                                                                                       | DOUTD+<br>DOUTC- | ADC D Digital Output True ADC C Digital Output Complement           |

|                                             | L9                                                                                                                                             | DOUTC+           | ADC C Digital Output Complement ADC C Digital Output True           |

| 42<br>43                                    | M10                                                                                                                                            | DOUTE+           | ADC & Digital Output True  ADC B Digital Output Complement          |

| 44                                          | L10                                                                                                                                            | DOUTB+           | ADC B Digital Output True                                           |

| Pin No. |     |        |                                                             |

|---------|-----|--------|-------------------------------------------------------------|

| TQFP    | BGA | Name   | Description                                                 |

| 45      | M11 | DOUTA- | ADC A Digital Output Complement                             |

| 46      | L11 | DOUTA+ | ADC A Digital Output True                                   |

| 48      | K11 | STBY   | Standby Power-Down                                          |

| 49      | J11 | PDWN   | Full Power-Down                                             |

| 51      | K12 | SCLK   | Serial Clock                                                |

| 52      | J12 | SDIO   | Serial Data Input/Output                                    |

| 53      | H12 | CSB    | Chip Select Bar                                             |

| 56      | B9  | LG-A   | LNA Ground for Channel A                                    |

| 57      | A9  | LI-A   | LNA Analog Input for Channel A                              |

| 58      | D9  | LOSW-A | LNA Analog Switched Output for Channel A                    |

| 59      | C9  | LO-A   | LNA Analog Inverted Output for Channel A                    |

| 62      | B10 | LG-B   | LNA Ground for Channel B                                    |

| 63      | A10 | LI-B   | LNA Analog Input for Channel B                              |

| 64      | D10 | LOSW-B | LNA Analog Switched Output for Channel B                    |

| 65      | C10 | LO-B   | LNA Analog Inverted Output for Channel B                    |

| 68      | B11 | LG-C   | LNA Ground for Channel C                                    |

| 69      | A11 | LI-C   | LNA Analog Input for Channel C                              |

| 70      | D11 | LOSW-C | LNA Analog Switched Output for Channel C                    |

| 71      | C11 | LO-C   | LNA Analog Inverted Output for Channel C                    |

| 74      | B12 | LG-D   | LNA Ground for Channel D                                    |

| 75      | A12 | LI-D   | LNA Analog Input for Channel D                              |

| 76      | D12 | LOSW-D | LNA Analog Switched Output for Channel D                    |

| 77      | C12 | LO-D   | LNA Analog Inverted Output for Channel D                    |

| 78      | K10 | CWD0-  | CW Doppler Output Complement for Channel 0                  |

| 79      | J10 | CWD0+  | CW Doppler Output True for Channel 0                        |

| 80      | K9  | CWD1–  | CW Doppler Output Complement for Channel 1                  |

| 81      | J9  | CWD1+  | CW Doppler Output True for Channel 1                        |

| 82      | K8  | CWD2-  | CW Doppler Output Complement for Channel 2                  |

| 83      | J8  | CWD2+  | CW Doppler Output True for Channel 2                        |

| 84      | K7  | CWD3-  | CW Doppler Output Complement for Channel 3                  |

| 85      | J7  | CWD3+  | CW Doppler Output True for Channel 3                        |

| 87      | A8  | GAIN-  | Gain Control Voltage Input Complement                       |

| 88      | A7  | GAIN+  | Gain Control Voltage Input True                             |

| 89      | A6  | RBIAS  | External Resistor to Set the Internal ADC Core Bias Current |

| 90      | A5  | VREF   | Voltage Reference Input/Output                              |

| 91      | K6  | CWD4-  | CW Doppler Output Complement for Channel 4                  |

| 92      | J6  | CWD4+  | CW Doppler Output True for Channel 4                        |

| 93      | K5  | CWD5-  | CW Doppler Output Complement for Channel 5                  |

| 94      | J5  | CWD5+  | CW Doppler Output True for Channel 5                        |

| 95      | K4  | CWD6-  | CW Doppler Output Complement for Channel 6                  |

| 96      | J4  | CWD6+  | CW Doppler Output True for Channel 6                        |

| 97      | K3  | CWD7-  | CW Doppler Output Complement for Channel 7                  |

| 98      | J3  | CWD7+  | CW Doppler Output True for Channel 7                        |

| 99      | C1  | LO-E   | LNA Analog Inverted Output for Channel E                    |

| 100     | D1  | LOSW-E | LNA Analog Switched Output for Channel E                    |

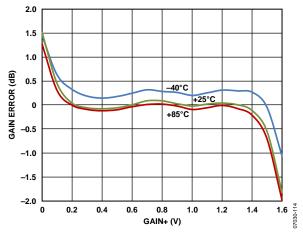

### TYPICAL PERFORMANCE CHARACTERISTICS

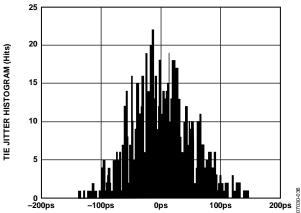

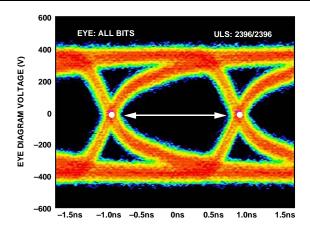

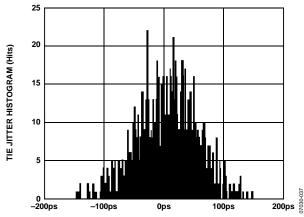

$f_{SAMPLE} = 40$  MSPS,  $f_{IN} = 5$  MHz,  $R_S = 50$   $\Omega$ , LNA gain = 21.3 dB, LNA bias = mid-high, PGA gain = 24 dB, AAF LPF cutoff =  $f_{SAMPLE}/3$ , HPF = LPF cutoff/20.7 (default), GAIN- = 0.8 V

Figure 6. Gain Error vs. GAIN+ at Three Temperatures

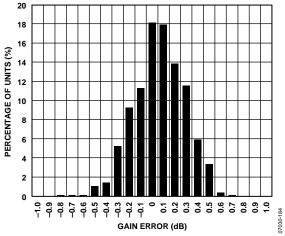

Figure 7. Gain Error Histogram, GAIN+ = 0.16 V

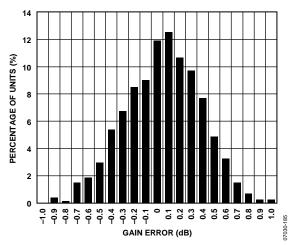

Figure 8. Gain Error Histogram, GAIN+ = 0.8 V

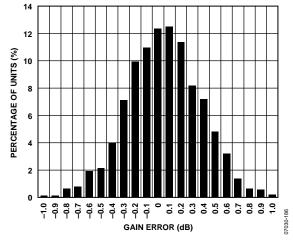

Figure 9. Gain Error Histogram, GAIN+ = 1.44 V

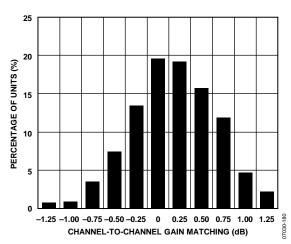

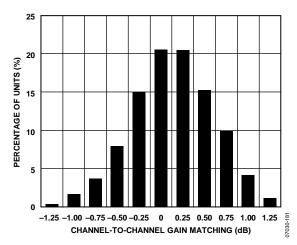

Figure 10. Gain Match Histogram, GAIN+ = 0.3 V

Figure 11. Gain Match Histogram, GAIN+ = 1.3 V

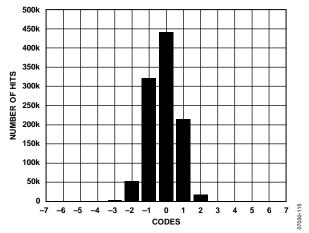

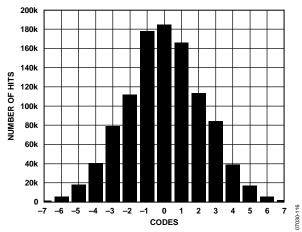

Figure 12. Output-Referred Noise Histogram, GAIN+ = 0.0 V

Figure 13. Output-Referred Noise Histogram, GAIN+ = 1.6 V

Figure 14. Short-Circuit, Input-Referred Noise vs. Frequency, PGA Gain = 30 dB, GAIN+ = 1.6 V

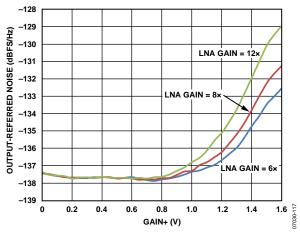

Figure 15. Short-Circuit, Output-Referred Noise vs. GAIN+

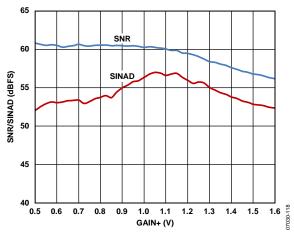

Figure 16. SNR/SINAD vs. GAIN+, AIN = -1.0 dBFS

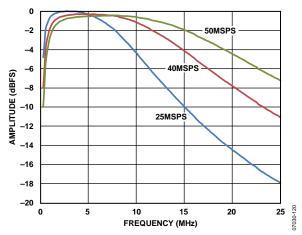

Figure 17. Antialiasing Filter (AAF) Pass-Band Response,  $LPF Cutoff = 1 \times (1/3) \times f_{SAMPLE}$

Figure 18. Antialiasing Filter (AAF) Group Delay Response

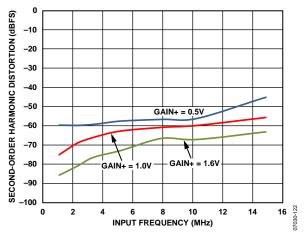

Figure 19. Second-Order Harmonic Distortion vs. Input Frequency, AIN = -1.0 dBFS

Figure 20. Third-Order Harmonic Distortion vs. Input Frequency, AIN = -1.0 dBFS

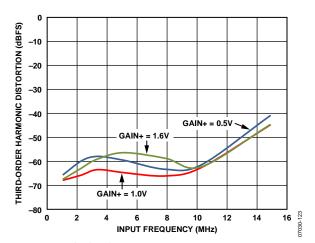

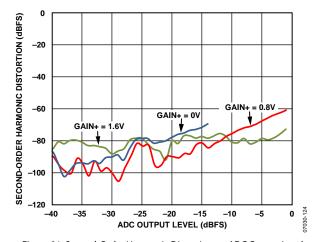

Figure 21. Second-Order Harmonic Distortion vs. ADC Output Level

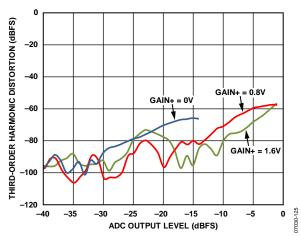

Figure 22. Third-Order Harmonic Distortion vs. ADC Output Level

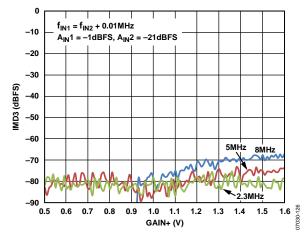

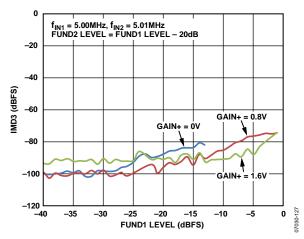

Figure 23. IMD3 vs. GAIN+

Figure 24. IMD3 vs. Fundamental 1 Amplitude (FUND1) Level

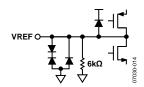

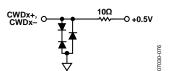

# **EQUIVALENT CIRCUITS**

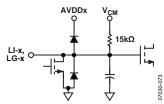

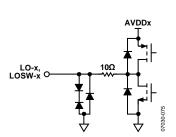

Figure 25. Equivalent LNA Input Circuit

Figure 26. Equivalent LNA Output Circuit

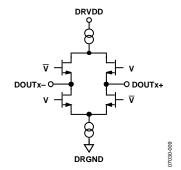

Figure 29. Equivalent Digital Output Circuit

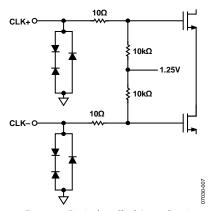

Figure 27. Equivalent Clock Input Circuit

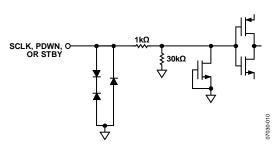

Figure 30. Equivalent SCLK, PDWN, or STBY Input Circuit

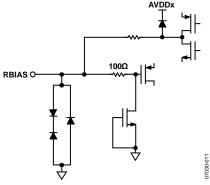

Figure 31. Equivalent RBIAS Circuit

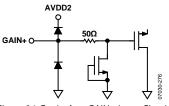

Figure 34. Equivalent GAIN+ Input Circuit

Figure 32. Equivalent CSB Input Circuit

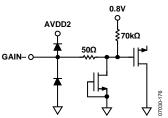

Figure 35. Equivalent GAIN- Input Circuit

Figure 33. Equivalent VREF Circuit

Figure 36. Equivalent CWDx± Output Circuit

### THEORY OF OPERATION

#### **ULTRASOUND**

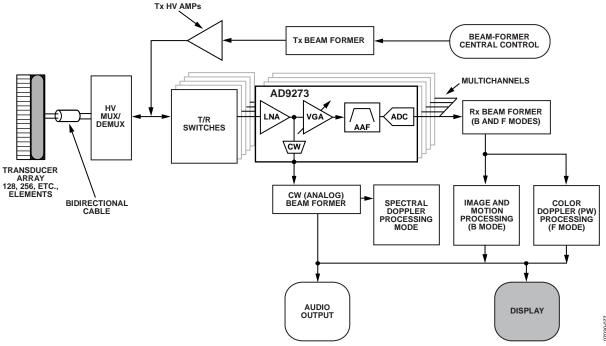

The primary application for the AD9273 is medical ultrasound. Figure 37 shows a simplified block diagram of an ultrasound system. A critical function of an ultrasound system is the time gain control (TGC) compensation for physiological signal attenuation. Because the attenuation of ultrasound signals is exponential with respect to distance (time), a linear-in-dB VGA is the optimal solution.

Key requirements in an ultrasound signal chain are very low noise, active input termination, fast overload recovery, low power, and differential drive to an ADC. Because ultrasound machines use beam-forming techniques requiring a large binary-weighted number of channels (for example, 32 to 512 channels), using the lowest power at the lowest possible noise is of chief importance.

Most modern machines use digital beam forming. In this technique, the signal is converted to digital format immediately

following the TGC amplifier, and then beam forming is accomplished digitally.

The ADC resolution of 12 bits with up to 50 MSPS sampling satisfies the requirements of both general-purpose and highend systems.

Power conservation and low cost are two of the most important factors in low-end and portable ultrasound machines, and the AD9273 is designed to meet these criteria.

For additional information regarding ultrasound systems, refer to "How Ultrasound System Considerations Influence Front-End Component Choice," *Analog Dialogue*, Volume 36, Number 3, May–July 2002, and "The AD9271—A Revolutionary Solution for Portable Ultrasound," *Analog Dialogue*, Volume 41, Number 3, July 2007.

Figure 37. Simplified Ultrasound System Block Diagram

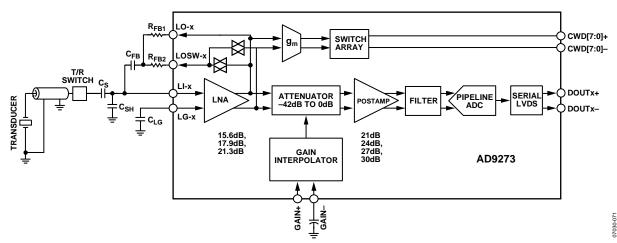

Figure 38. Simplified Block Diagram of a Single Channel

#### **CHANNEL OVERVIEW**

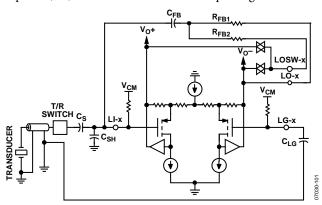

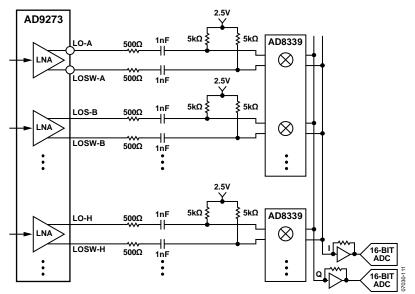

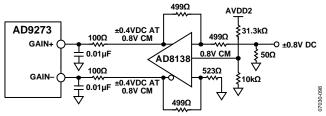

Each channel contains both a TGC signal path and a CW Doppler signal path. Common to both signal paths, the LNA provides useradjustable input impedance termination. The CW Doppler path includes a transconductance amplifier and a crosspoint switch. The TGC path includes a differential X-AMP® VGA, an antialiasing filter, and an ADC. Figure 38 shows a simplified block diagram with external components.

The signal path is fully differential throughout to maximize signal swing and reduce even-order distortion; however, the LNA is designed to be driven from a single-ended signal source.

### Low Noise Amplifier (LNA)

Good noise performance relies on a proprietary ultralow noise LNA at the beginning of the signal chain, which minimizes the noise contribution in the following VGA. Active impedance control optimizes noise performance for applications that benefit from input impedance matching.

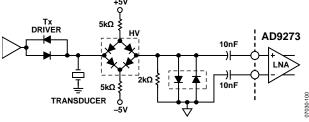

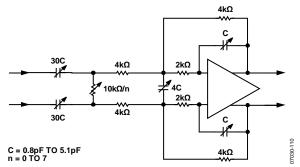

A simplified schematic of the LNA is shown in Figure 39. LI-x is capacitively coupled to the source. An on-chip bias generator establishes dc input bias voltages of around 0.9 V and centers the output common-mode levels at 1.5 V (AVDD2 divided by 2). A capacitor,  $C_{LG}$ , of the same value as the input coupling capacitor,  $C_{S}$ , is connected from the LG-x pin to ground.

Figure 39. Simplified LNA Schematic

The LNA supports differential output voltages as high as  $4.4~\rm V$  p-p with positive and negative excursions of  $\pm 1.1~\rm V$  from a common-mode voltage of 1.5 V. The LNA differential gain sets the maximum input signal before saturation. One of three gains is set through the SPI. The corresponding full-scale input for the gain settings of 6, 8, and 12 is 733 mV p-p, 550 mV p-p, and 367 mV p-p, respectively. Overload protection ensures quick recovery time from large input voltages. Because the inputs are capacitively coupled to a bias voltage near midsupply, very large inputs can be handled without interacting with the ESD protection.

Low value feedback resistors and the current-driving capability of the output stage allow the LNA to achieve a low input-referred noise voltage of 1.26 nV/ $\sqrt{\rm Hz}$  at a gain of 21.3 dB. This is achieved with a current consumption of only 10 mA per channel (30 mW). On-chip resistor matching results in precise single-ended gains, which are critical for accurate impedance control. The use of a fully differential topology and negative feedback minimizes distortion. Low second-order harmonic distortion is particularly important in second-order harmonic ultrasound imaging applications. Differential signaling enables smaller swings at each output, further reducing third-order distortion.

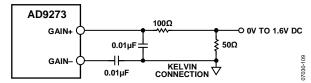

#### Recommendation

It is highly recommended that the LG-x pins form a Kelvin type connection to the input or probe connection ground. Simply connecting the LG pin to ground near the device may allow differences in potential to be amplified through the LNA. This generally shows up as a dc offset voltage that can vary from channel to channel and part to part, depending on the application and layout of the PCB (see Figure 38).

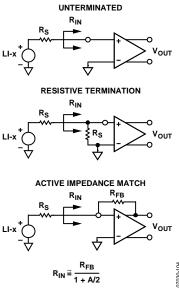

### **Active Impedance Matching**

The LNA consists of a single-ended voltage gain amplifier with differential outputs and the negative output available externally. For example, with a fixed gain of  $8\times (17.9 \text{ dB})$ , an active input termination is synthesized by connecting a feedback resistor between the negative output pin, LO-x, and the positive input pin, LI-x. This well-known technique is used for interfacing multiple probe impedances to a single system. The input resistance is shown in Equation 1.

$$R_{IN} = \frac{R_{FB}}{(1 + \frac{A}{2})} \tag{1}$$

where A/2 is the single-ended gain or the gain from the LI-x inputs to the LO-x outputs, and  $R_{FB}$  is the resulting impedance of the  $R_{FB1}$  and  $R_{FB2}$  combination (see Figure 39).

Because the amplifier has a gain of 8× from its input to its differential output, it is important to note that the gain A/2 is the gain from Pin LI-x to Pin LO-x, and it is 6 dB less than the gain of the amplifier, or 12.1 dB (4×). The input resistance is reduced by an internal bias resistor of 15 k $\Omega$  in parallel with the source resistance connected to Pin LI-x while Pin LG-x is ac grounded. Equation 2 can be used to calculate the needed R<sub>FB</sub> for a desired R<sub>IN</sub>, even for higher values of R<sub>IN</sub>.

$$R_{IN} = \frac{R_{FB}}{(1+3)} || 15 \text{ k}\Omega$$

(2)

For example, to set  $R_{\rm IN}$  to 200  $\Omega$ , the value of  $R_{\rm FB}$  must be 1000  $\Omega$ . If the simplified equation (Equation 2) is used to calculate  $R_{\rm IN}$ , the value is 188  $\Omega$ , resulting in a gain error less than 0.6 dB. Some factors, such as the presence of a dynamic source resistance, might influence the absolute gain accuracy more significantly. At higher frequencies, the input capacitance of the LNA needs to be considered. The user must determine the level of matching accuracy and adjust  $R_{\rm FB}$  accordingly.

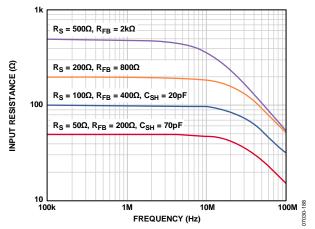

The bandwidth (BW) of the LNA is greater than 100 MHz. Ultimately, the BW of the LNA limits the accuracy of the synthesized  $R_{\rm IN}$ . For  $R_{\rm IN}=R_{\rm S}$  up to about 200  $\Omega$ , the best match is between 100 kHz and 10 MHz, where the lower frequency limit is determined by the size of the ac-coupling capacitors, and the upper limit is determined by the LNA BW. Furthermore, the input capacitance and  $R_{\rm S}$  limit the BW at higher frequencies. Figure 40 shows  $R_{\rm IN}$  vs. frequency for various values of  $R_{\rm FB}$ .

Figure 40.  $R_{IN}$  vs. Frequency for Various Values of  $R_{FB}$  (Effects of  $R_{S}$  and  $C_{SH}$  Are Also Shown)

Note that at the lowest value (50  $\Omega$ ),  $R_{\rm IN}$  peaks at frequencies greater than 10 MHz. This is due to the BW roll-off of the LNA, as mentioned previously.

However, as can be seen for larger  $R_{IN}$  values, parasitic capacitance starts rolling off the signal BW before the LNA can produce peaking.  $C_{SH}$  further degrades the match; therefore,  $C_{SH}$  should not be used for values of  $R_{IN}$  that are greater than  $100~\Omega$ . Table 7 lists the recommended values for  $R_{FB}$  and  $C_{SH}$  in terms of  $R_{IN}$ .