# LC<sup>2</sup>MOS High Speed, Quad SPST Switch

# ADG201HS

#### **FEATURES**

50ns max Switching Time Over Full Temperature Range

Low R<sub>ON</sub> (30Ω typ)

Single Supply Specifications for +10.8V to +16.5V Operation

Extended Plastic Temperature Range (-40°C to +85°C)

Break-Before-Make Switching

Low Leakage (100pA typ)

44V Supply max Rating

Available in 16-Lead DIP/SOIC and 20-Lead LCCC/PLCC Packages

ADG201HS (K, B, T) Replaces HI-201HS ADG201HS (J, A, S) Replaces DG271

### GENERAL DESCRIPTION

The ADG201HS is a monolithic CMOS device comprising four independently selectable SPST switches. It is designed on an enhanced  $LC^2MOS$  process which gives very fast switching speeds and low  $R_{ON}$ .

The switches also feature break-before-make switching action for use in multiplexer applications and low charge injection for minimum transients on the output when switching the digital inputs.

#### **ORDERING GUIDE**

| Model <sup>1</sup>      | Temperature<br>Range                           | Package<br>Option <sup>2</sup> |

|-------------------------|------------------------------------------------|--------------------------------|

| ADG201HSJN              | $-40^{\circ}$ C to $+85^{\circ}$ C             | N-16                           |

| ADG201HSKN              | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | N-16                           |

| ADG201HSKR              | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | R-16                           |

| ADG201HSAQ              | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | Q-16                           |

| ADG201HSBQ              | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | Q-16                           |

| ADG201HSJP              | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | P-20A                          |

| ADG201HSKP              | $-40^{\circ}\text{C}$ to $+85^{\circ}\text{C}$ | P-20A                          |

| ADG201HSSQ              | -55°C to +125°C                                | Q-16                           |

| ADG201HSTQ <sup>3</sup> | −55°C to +125°C                                | Q-16                           |

| ADG201HSTE <sup>3</sup> | $-55^{\circ}\text{C to} + 125^{\circ}\text{C}$ | E-20A                          |

### NOTES

<sup>1</sup>To order MIL-STD-883, Class B processed parts, add /883B to T grade part numbers. See the Analog Devices Military Products Databook (1994) for military data sheet. <sup>2</sup>E = Leadless Ceramic Chip Carrier; N = Narrow Plastic DIP; P = Plastic Leaded Chip Carrier; Q = Cerdip; R = 0.15" Small Outline IC (SOIC). <sup>3</sup>Standard Military Drawing (SMD) approved by DESC.

SMD numbers are

5962-86716012X (ADG201HSTE/883B) 5962-8671601EX (ADG201HSTQ/883B)

### REV. B

Information furnished by Analog Devices is believed to be accurate and reliable. However, no responsibility is assumed by Analog Devices for its use, nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Analog Devices.

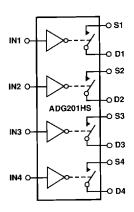

### FUNCTIONAL BLOCK DIAGRAM

#### PRODUCT HIGHLIGHTS

1. 50ns max t<sub>ON</sub> and t<sub>OFF</sub>:

The ADG201HS top grades (K, B, T) have guaranteed 50ns max turn-on and turn-off times over the full operating temperature range. The lower grades (J,A,S) have guaranteed 75ns switching times over the full operating temperature range.

2. Single Supply Specifications:

The ADG201HS is fully specified for applications which require a single positive power supply in the +10.8V to +16.5V range.

3. Low Leakage:

Leakage currents in the range of 100pA make these switches suitable for high precision circuits. The added feature of break-before-make allows for multiple outputs to be tied together for multiplexer applications while keeping leakage errors to a minimum.

| IN | Switch<br>Condition |  |  |

|----|---------------------|--|--|

| 0  | ON                  |  |  |

| 1  | OFF                 |  |  |

Truth Table

## **ADG201HS\* Product Page Quick Links**

Last Content Update: 08/30/2016

### Comparable Parts

View a parametric search of comparable parts

### Documentation <a>□</a>

### **Application Notes**

• AN-355: Behind the Switch Symbol

### **Data Sheet**

ADG201HS: LC<sup>2</sup>MOS High Speed, Quad SPST Switches Data Sheet

### Reference Materials

### **Analog Dialogue**

• Choosing High-Speed Signal Processing Components for Ultrasound Systems

### **Product Selection Guide**

• Switches and Multiplexers Product Selection Guide

### **Technical Articles**

- CMOS Switches Offer High Performance in Low Power, Wideband Applications

- · Data-acquisition system uses fault protection

- Enhanced Multiplexing for MEMS Optical Cross Connects

- Temperature monitor measures three thermal zones

## Design Resources -

- ADG201HS Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### Discussions <a>□</a>

View all ADG201HS EngineerZone Discussions

## Sample and Buy -

Visit the product page to see pricing options

### Technical Support -

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# ADG201HS — SPECIFICATIONS

**DUAL SUPPLY** ( $V_{DD}=+13.5V$  to +16.5V, =-13.5V to -16.5V, GND =0V,  $V_{IN}=-100$  (Logic High Level) or 0.8 V (Logic Low Level) unless otherwise noted)

| Parameter                                             | Version    | +25°C    | $T_{min} - T_{max}^{1}$ | Units        | Comments                                                  |

|-------------------------------------------------------|------------|----------|-------------------------|--------------|-----------------------------------------------------------|

| ANALOG SWITCH                                         |            |          |                         |              |                                                           |

| Analog Signal Range                                   | All        | $V_{SS}$ | $V_{SS}$                | Vmin         |                                                           |

|                                                       | All        | $V_{DD}$ | $V_{DD}$                | V max        |                                                           |

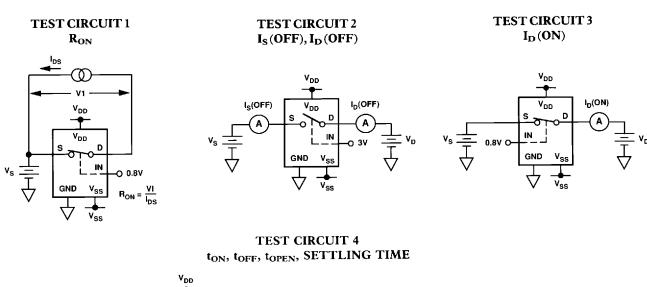

| R <sub>ON</sub>                                       | All        | 30       | _                       | $\Omega$ typ | $-10V \le V_S \le +10V$ , $I_{DS} = 1mA$ ; Test Circuit 1 |

| NON                                                   | All        | 50       | 75                      | Ωmax         | 201 113 1 201                                             |

| R <sub>ON</sub> Drift                                 | All        | 0.5      | _                       | %/°C typ     | $-10V \le V_S \le +10V, I_{DS} = 1mA$                     |

| R <sub>ON</sub> Match                                 | All        | 3        | _                       | % typ        | $-10V \leqslant V_{S} \leqslant +10V, I_{DS} = 1mA$       |

|                                                       |            |          |                         |              | _                                                         |

| I <sub>S</sub> (OFF), Off Input Leakage <sup>2</sup>  | All        | 0.1      | 20                      | nA typ       | $V_D = \pm 14V$ ; $V_S = \mp 14V$ ; Test Circuit 2        |

|                                                       | J, K, A, B | 1        | 20                      | nA max       |                                                           |

|                                                       | S, T       | 1        | 60                      | nA max       | N . 14V V14V TCiris 2                                     |

| I <sub>D</sub> (OFF), Off Output Leakage <sup>2</sup> | All        | 0.1      | ••                      | nA typ       | $V_D = \pm 14V$ ; $V_S = \mp 14V$ ; Test Circuit 2        |

|                                                       | J, K, A, B | 1        | 20                      | nA max       |                                                           |

|                                                       | S,T        | 1        | 60                      | nA max       | 37 37 - 1 1437. Teet Oinit 2                              |

| I <sub>D</sub> (ON), On Channel Leakage <sup>2</sup>  | All        | 0.1      |                         | nA typ       | $V_D = V_S = \pm 14V$ ; Test Circuit 3                    |

|                                                       | J, K, A, B | 1        | 20                      | nA max       |                                                           |

|                                                       | S,T        | 1        | 60                      | nA max       |                                                           |

| DIGITAL CONTROL                                       |            |          |                         |              |                                                           |

| V <sub>INH</sub> , Input High Voltage                 | All        | 2.4      | 2.4                     | V min        |                                                           |

| V <sub>INL</sub> , Input Low Voltage                  | All        | 0.8      | 0.8                     | V max        |                                                           |

| I <sub>INL</sub> or I <sub>INH</sub>                  | All        | 1        | 1                       | μA max       |                                                           |

| C <sub>IN</sub>                                       | All        | 8        | 8                       | pF max       |                                                           |

| DYNAMIC CHARACTERISTICS                               | 100        | -        | •                       |              |                                                           |

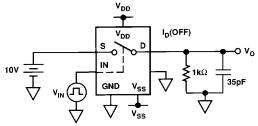

| t <sub>on</sub>                                       | K, B, T    | 50       | 50                      | ns max       | Test Circuit 4                                            |

| ON                                                    | J, A, S    | 75       | 75                      | ns max       |                                                           |

| t <sub>OFF1</sub>                                     | K, B, T    | 50       | 50                      | ns max       | Test Circuit 4                                            |

| OFFI                                                  | J,A,S      | 75       | 75                      | ns max       |                                                           |

| t <sub>OFF2</sub>                                     | All        | 150      | _                       | ns typ       | Test Circuit 4                                            |

| topen                                                 | Ali        | 5        | 5                       | ns typ       | t <sub>ON</sub> -t <sub>OFF1</sub> ; Test Circuit 4       |

| Output Settling Time to 0.1%                          | All        | 180      | _                       | ns typ       | $V_{IN} = 3V \text{ to } 0V$ ; Test Circuit 4             |

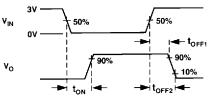

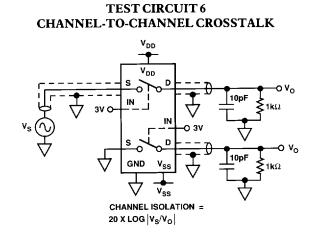

| OFF Isolation                                         | All        | 72       | _                       | dB typ       | $V_S = 3V \text{ rms}, f = 100kHz, R_L = 1k\Omega;$       |

|                                                       |            |          |                         |              | $C_L = 10pF$ ; Test Circuit 5                             |

| Channel-to-Channel Crosstalk                          | All        | 86       | _                       | dB typ       | $V_S = 3V \text{ rms}, f = 100kHz, R_L = 1k\Omega;$       |

| CIMILE TO CIMILED OF COOKING                          |            |          |                         |              | $C_L = 10 pF$ ; Test Circuit 6                            |

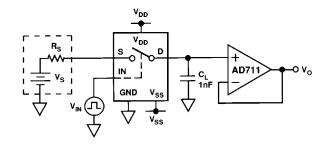

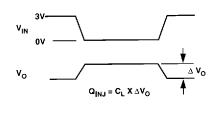

| Q <sub>INI</sub> , Charge Injection                   | All        | 10       | _                       | pC typ       | $R_S = 0\Omega$ , $V_S = 0V$ ; Test Circuit 7             |

| C <sub>S</sub> (OFF)                                  | All        | 10       | _                       | pF typ       |                                                           |

| C <sub>D</sub> (OFF)                                  | All        | 10       | _                       | pF typ       |                                                           |

| $C_D, C_S(ON)$                                        | All        | 30       | _                       | pF typ       |                                                           |

| C <sub>DS</sub> (OFF)                                 | All        | 0.5      | _                       | pF typ       |                                                           |

| POWER SUPPLY                                          |            |          |                         |              | <u> </u>                                                  |

| I <sub>DD</sub>                                       | All        | 10       | 10                      | mA max       |                                                           |

| I <sub>SS</sub>                                       | All        | 6        | 6                       | mA max       |                                                           |

|                                                       |            |          |                         |              | $V_{DD} = +15V, V_{SS} = -15V$                            |

| Power Dissipation                                     | Ali        | 240      | 240                     | mW max       | VDD - T13V, VSS13V                                        |

NOTES

Temperature ranges are as follows: ADG201HSJ, K; -40°C to +85°C

ADG201HSA, B; -40°C to +85°C

ADG201HSS, T; -55°C to +125°C

$<sup>^2</sup>Leakage \ specifications \ apply \ with \ a\ V_D \quad (V_S) \ of \ \pm \ 14V \ or \ with \ a\ V_D (V_S) \ of \ 0.5V \ within \ the \ supply \ voltages \ (V_{DD},V_{SS}), \ whichever \ is \ the \ minimum.$

Specifications subject to change without notice.

$\textbf{SINGLE SUPPLY} \ \ (\textbf{V}_{DD} = +\ 10.8 \textbf{V to}\ +\ 16.5 \textbf{V}, \ \textbf{V}_{SS} = \textbf{GND} = \textbf{OV}, \ \textbf{V}_{IN} = \textbf{3V} \ \, [\textbf{Logic High Level}] \ \, \text{or } \textbf{0.8V} \ \, [\textbf{Logic Low Level}] \ \, \text{unless otherwise noted})$

| Parameter                                            | Version     | + 25°C   | $T_{min} - T_{max}$ | Units          | Comments                                                 |

|------------------------------------------------------|-------------|----------|---------------------|----------------|----------------------------------------------------------|

| ANALOG SWITCH                                        |             |          |                     |                |                                                          |

| Analog Signal Range                                  | All         | $V_{SS}$ | $V_{SS}$            | Vmin           |                                                          |

|                                                      | All         | $V_{DD}$ | $V_{DD}$            | V max          |                                                          |

| R <sub>ON</sub>                                      | All         | 65       | _                   | $\Omega$ typ   | $0V \le V_S \le +10V$ , $I_{DS} = 1mA$ ; Test Circuit 1  |

| ···                                                  | All         | 90       | 120                 | $\Omega$ max   |                                                          |

| R <sub>ON</sub> Drift                                | All         | 0.5      | _                   | %/°C typ       | $0V \leq V_S \leq +10V$ , $I_{DS} = 1mA$                 |

| R <sub>ON</sub> Match                                | All         | 3        | _                   | % typ          | $0V \leq V_S \leq +10V$ , $I_{DS} = 1mA$                 |

| I <sub>S</sub> (OFF), Off Input Leakage <sup>1</sup> | All         | 0.1      |                     | nA typ         | $V_D = +10V/+0.5V$ ; $V_S = +0.5V/+10V$ ; Test Circuit 2 |

|                                                      | J, K, A, B  | 1        | 20                  | пA max         |                                                          |

|                                                      | S, T        | 1        | 60                  | nA max         |                                                          |

| ID (OFF), Off Output Leakage <sup>1</sup>            | All         | 0.1      |                     | nA typ         | $V_D = +10V/+0.5V$ ; $V_S = +0.5V/+10V$ ; Test Circuit 2 |

|                                                      | J, K, A, B  | 1        | 20                  | nA max         |                                                          |

|                                                      | S, T        | 1        | 60                  | nA max         |                                                          |

| I <sub>D</sub> (ON), On Channel Leakage <sup>1</sup> | All         | 0.1      |                     | nA typ         | $V_D = V_S = +10V/+0.5V$ ; Test Circuit 3                |

|                                                      | J, K, A, B  | 1        | 20                  | nA max         |                                                          |

|                                                      | S, T        | 1        | 60                  | nA max         |                                                          |

| DIGITAL CONTROL                                      |             |          |                     |                |                                                          |

| V <sub>INH</sub> , Input High Voltage                | All         | 2.4      | 2.4                 | V min          |                                                          |

| V <sub>INL</sub> , Input Low Voltage                 | All         | 0.8      | 0.8                 | V max          |                                                          |

| I <sub>INL</sub> or I <sub>INH</sub>                 | All         | 1        | 1                   | μA max         |                                                          |

| C <sub>IN</sub>                                      | All         | 8        | 8                   | pF max         |                                                          |

| DYNAMIC CHARACTERISTICS                              |             |          | -                   |                |                                                          |

| t <sub>ON</sub>                                      | K, B, T     | 50       | 70                  | ns max         | Test Circuit 4                                           |

|                                                      | J, A, S     | 75       | 90                  | ns max         |                                                          |

| t <sub>OFF1</sub>                                    | K, B, T     | 50       | 70                  | ns max         | Test Circuit 4                                           |

| •••                                                  | J, A, S     | 75       | 90                  | ns max         |                                                          |

| t <sub>OFF2</sub>                                    | All         | 150      | _                   | ns typ         | Test Circuit 4                                           |

| topen                                                | All         | 5        | 5                   | ns typ         | t <sub>ON</sub> -t <sub>OFF1</sub> ; Test Circuit 4      |

| Output Settling Time to 0.1%                         | All         | 180      | _                   | ns typ         | $V_{IN} = 3V \text{ to } 0V$ ; Test Circuit 4            |

| OFF Isolation                                        | All         | 72       | _                   | dB typ         | $V_S = 3V \text{ rms}, f = 100kHz, R_L = 1k\Omega;$      |

|                                                      |             |          |                     |                | $C_L = 10pF$ ; Test Circuit 5                            |

| Channel-to-Channel Crosstalk                         | All         | 86       | _                   | d <b>B</b> typ | $V_S = 3V \text{ rms}, f = 100kHz, R_L = 1k\Omega;$      |

|                                                      |             |          |                     |                | $C_L = 10pF$ ; Test Circuit 6                            |

| Q <sub>INJ</sub> , Charge Injection                  | All         | 10       | -                   | pC typ         | $R_S = 0\Omega$ , $V_S = 0V$ ; Test Circuit 7            |

| $C_S(OFF)$                                           | All         | 10       | _                   | pF typ         |                                                          |

| $C_{D}(OFF)$                                         | <b>A</b> 11 | 10       | _                   | pF typ         |                                                          |

| $C_D, C_S(ON)$                                       | All         | 30       | _                   | pF typ         |                                                          |

| C <sub>DS</sub> (OFF)                                | All         | 0.5      |                     | pF typ         |                                                          |

| POWER SUPPLY                                         |             |          |                     |                |                                                          |

| $I_{ m DD}$                                          | All         | 10       | 10                  | mA max         |                                                          |

| Power Dissipation                                    | All         | 150      | 150                 | mW max         | $V_{DD} = +15V$                                          |

NOTE  ${}^{l} The \ leakage \ specifications \ degrade \ marginally \ (typically \ lnA \ at \ 25^{\circ}C) \ with \ V_D(V_S) = V_{SS}.$

Specifications subject to change without notice.

### ADG201HS

| ABSOLUTE MAXIMUM RATINGS*                                                                                                      | Power Dissipation (Any Package)                                                                                                                                                         |

|--------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| $(T_{\Lambda} = 25^{\circ}\text{C unless otherwise noted})$                                                                    | Up to $+75^{\circ}$ C 470mW                                                                                                                                                             |

|                                                                                                                                | Derates above $+75^{\circ}$ C by 6mW/°C                                                                                                                                                 |

| $V_{\mathrm{DD}}$ to $V_{\mathrm{SS}}$                                                                                         | Operating Temperature                                                                                                                                                                   |

| $V_{DD}$ to GND                                                                                                                | Commercial (J, K Version) $-40^{\circ}$ C to $+85^{\circ}$ C                                                                                                                            |

| $V_{SS}$ to $GND^1$                                                                                                            | Industrial (A, B Version) $\dots \dots -40^{\circ}$ C to $+85^{\circ}$ C                                                                                                                |

| Analog Inputs <sup>2</sup>                                                                                                     | Extended (S, T Version) $\dots \dots -55^{\circ}$ C to $+125^{\circ}$ C                                                                                                                 |

| Voltage at S, D $\dots \dots $ | Storage Temperature Range65°C to +150°C                                                                                                                                                 |

| $V_{DD} + 2V or$                                                                                                               | Lead Temperature (Soldering 10sec) + 300°C                                                                                                                                              |

| 20mA, Whichever Occurs First                                                                                                   |                                                                                                                                                                                         |

| Continuous Current, S or D 20mA                                                                                                | NOTES                                                                                                                                                                                   |

| Pulsed Current S or D                                                                                                          | <sup>1</sup> If $V_{SS}$ is open circuited with $V_{DD}$ and GND applied, the $V_{SS}$ pin will be pulled positive, exceeding the Absolute Maximum Ratings. If this possibility exists, |

| 1ms Duration, 10% Duty Cycle 70mA                                                                                              | a Schottky diode from $V_{SS}$ to GND (cathode end to GND) ensures that the                                                                                                             |

| Digital Inputs <sup>2</sup>                                                                                                    | Absolute Maximum Ratings will be observed.                                                                                                                                              |

| Voltage at IN $V_{SS}$ -4V to                                                                                                  | <sup>2</sup> Overvoltage at IN, S or D, will be clamped by diodes. Current                                                                                                              |

| $V_{\mathrm{DD}} + 4 \mathrm{V}  \mathrm{or}$                                                                                  | should be limited to the maximum rating above.                                                                                                                                          |

| 20mA, Whichever Occurs First                                                                                                   |                                                                                                                                                                                         |

<sup>\*</sup>COMMENT: Stresses above those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### CAUTION:

ESD (electrostatic discharge) sensitive device. The digital control inputs are diode protected; however, permanent damage may occur on unconnected devices subject to high energy electrostatic fields. Unused devices must be stored in conductive foam or shunts. The protective foam should be discharged to the destination socket before devices are inserted.

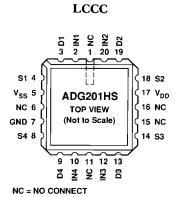

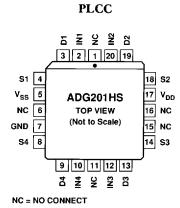

### **PIN CONFIGURATIONS**

#### IN1 16 IN2 D1 2 15 D2 S1 S2 ADG201HS 13 V<sub>DD</sub> $v_{ss}$ TOP VIEW GND 5 12 NC (Not to Scale) 6 S3 **S4** 7 10 D3 D4 8 IN4 9 IN3 NC = NO CONNECT

DIP, SOIC

# Typical Performance Characteristics—ADG201HS

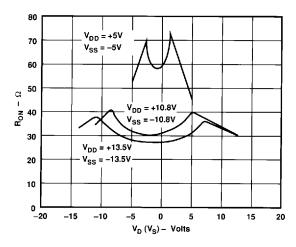

The switches are guaranteed functional with reduced single or dual supplies down to 4.5V.

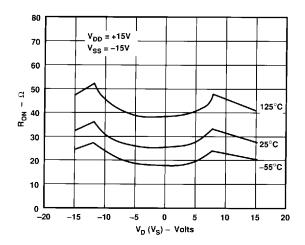

$R_{ON}$  as a Function of  $V_D$  ( $V_S$ ): Dual Supply Voltage

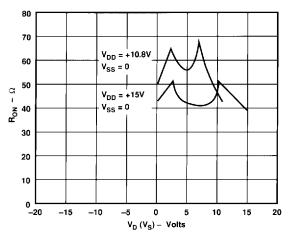

$R_{ON}$  as a Function of  $V_D$  ( $V_S$ ): Single Supply Voltage,  $T_A = +25^{\circ}C$

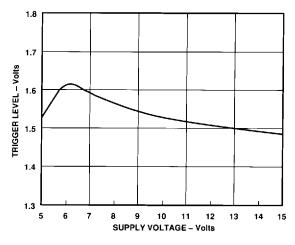

Trigger Levels vs. Power Supply Voltage, Dual or Single Supply,  $T_A = +25^{\circ}C$

$R_{ON}$  as a Function of  $V_D$  ( $V_S$ ): Dual Supply Voltage,  $T_A = +25^{\circ}C$

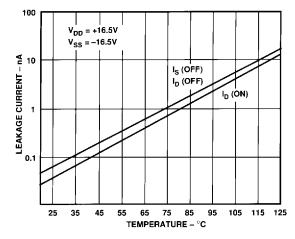

Leakage Current as a Function of Temperature Dual Supply Voltage. (Note: Leakage Currents Reduce as the Supply Voltages Reduce)

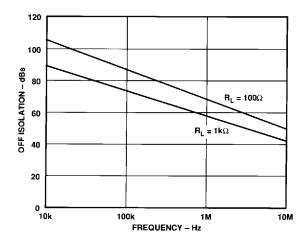

Off Isolation vs. Signal Frequency; Dual or Single 15V Supplies,  $T_A = +25^{\circ}C$

# **ADG201HS**—Typical Performance Characteristics (Continued)

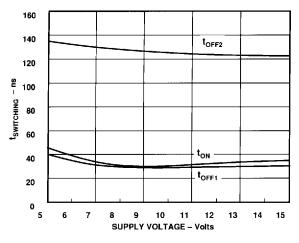

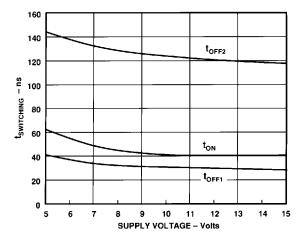

Switching Time vs. Supply Voltage (Dual Supply):  $T_A = +25$ °C. (Note: See Test Circuit 4. For  $V_{DD} < 10V$ ,  $V_S = V_{DD}$ )

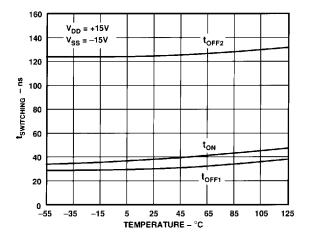

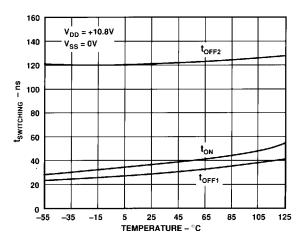

Switching Time vs. Temperature: Dual Supply Voltage

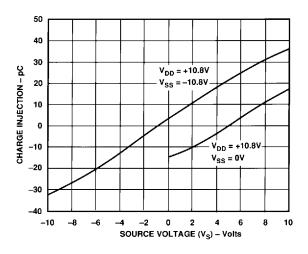

Charge Injection vs. Source Voltage ( $V_S$ ) for Dual and Single 10.8V Supplies:  $T_A = +25^{\circ}C$

Switching Time vs. Supply Voltage (Single Supply):  $T_A - +25^{\circ}C$ . (Note: See Test Circuit 4. For  $V_{DD} < 10V$ ,  $V_S = V_{DD}$ )

Switching Time vs. Temperature: Single Supply Voltage

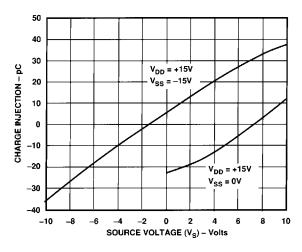

Charge Injection vs. Source Voltage ( $V_S$ ) for Dual and Single 15V Supplies:  $T_A = +25^{\circ}C$

# Test Circuits—ADG201HS

Note: All digital input signal rise and fall times measured from 10% to 90% of 3V.  $t_R=t_F=5 ns$ . Decoupling capacitors (0.01 $\mu F$  min) from  $V_{\rm DD}$  and  $V_{\rm SS}$  to GND are recommended to achieve specified performance.

**TEST CIRCUIT 5**

### TEST CIRCUIT 7 CHARGE INJECTION

### ADG201HS

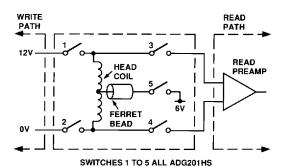

### SINGLE SUPPLY DISK DRIVE APPLICATION

The excellent performance of the ADG201HS with single supply operation makes it suitable in applications such as disk drives where only positive power supply voltages are normally available. The accompanying circuit shows a typical application for the ADG201HS in the read/write head switching section of a disk drive. The circuit allows data (0s and 1s) to be written to and read from a disk. The principal advantage offered by the ADG201HS is that it retains very fast switching speed with single supply operation (see Single Supply Specifications). This allows disk drives to run at higher data rates.

| SWITCH STATES/FUNCTION |     |     |      |  |

|------------------------|-----|-----|------|--|

| SWITCH                 | WR  |     |      |  |

| NUMBER                 | "0" | "1" | READ |  |

| 1                      | OFF | ON  | OFF  |  |

| 2                      | ON  | OFF | OFF  |  |

| 3                      | OFF | OFF | ON   |  |

| 4                      | OFF | OFF | ON   |  |

| 5                      | ON  | ON  | OFF  |  |

ADG201HS in the Read/Write Head Switching Circuit of a Disk Drive

#### **OUTLINE DIMENSIONS**

Dimensions shown in inches and (mm).

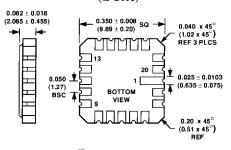

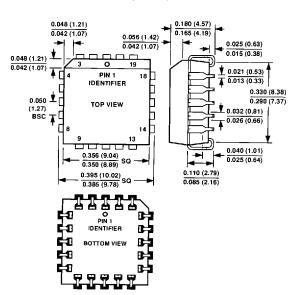

# 20-Terminal Plastic Leaded Chip Carrier (P-20A)

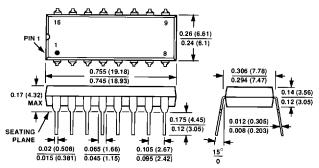

### 16-Pin Plastic DIP (N-16)

LEAD NO. 1 IDENTIFIED BY DOT OR NOTCH LEADS ARE SOLDER OR TIN-PLATED KOVAR OR ALLOY 42

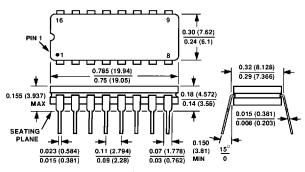

### 16-Pin Cerdip (Q-16)

LEAD NO. 1 IDENTIFIED BY DOT OR NOTCH

LEADS ARE SOLDER OR TIN-PLATED KOVAR OR ALLOY 42

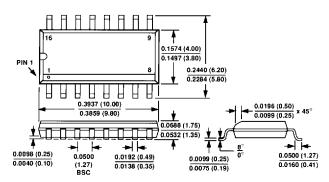

### 16-Lead Narrow Body SOIC (R-16A)

# 20-Terminal Leadless Ceramic Chip Carrier (E-20A)