Is Now Part of

# **ON Semiconductor**®

To learn more about ON Semiconductor, please visit our website at <u>www.onsemi.com</u>

ON Semiconductor and the ON Semiconductor logo are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at www.onsemi.com/site/pdf/Patent-Marking.pdf. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor dates sheds, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor dates sheds and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights of others. ON Semiconductor products are not designed, intended, or authorized for use on similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor and its officers, employees, subsidiaries, affliates, and distributors harmless against all claims, costs, damages, and expenses, and reasonable attorney fees arising out or i, directly or indirectly, any lay bed ON Semiconductor and its officers, employees, ween if such claim alleges that ON Semiconductor was negligent regarding the d

SEMICONDUCTOR®

# KA4558 Dual Operational Amplifier

#### Features

- No frequency compensation required.

- No latch up.

- Large common mode and differential voltage range.

- Parameter tracking over temperature range.

- Gain and phase match between amplifiers.

- Internally frequency compensated.

- Low noise input transistors.

## Descriptions

The KA4558 is a monolithic integrated circuit designed for dual operational amplifier.

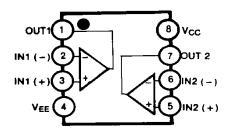

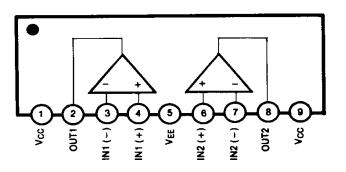

#### **Internal Block Diagram**

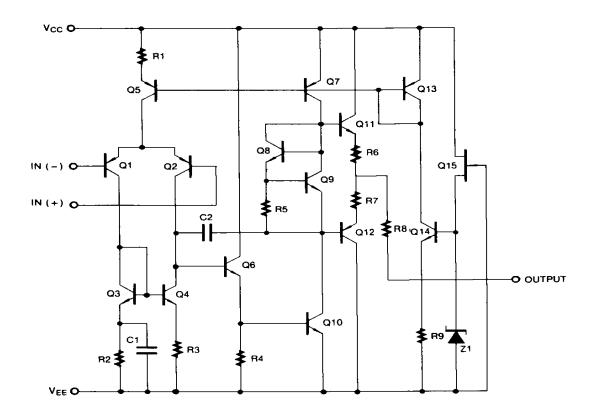

## **Schematic Diagram**

(One Section Only)

## **Absolute Maximum Ratings**

| Parameter                                        | Symbol   | Value              | Unit |

|--------------------------------------------------|----------|--------------------|------|

| Supply Voltage                                   | Vcc      | ±22                | V    |

| Differential Input Voltage                       | VI(DIFF) | 30                 | V    |

| Input Voltage                                    | VI       | ±15                | V    |

| Power Dissipation                                | PD       | 400                | mW   |

| Operating Temperature Range<br>KA4558<br>KA4558I | Topr     | 0 ~ 70<br>-40 ~ 85 | °C   |

| Storage Temperature Range                        | TSTG     | -65 ~ 150          | °C   |

#### **Electrical Characteristics**

(VCC = 15V, VEE = - 15V , TA = 25 °C unless otherwise specified)

| Devemeter                              | Cumhal  | Conditions                   |                                      | KA4558/KA4558I |     |     | 11     |

|----------------------------------------|---------|------------------------------|--------------------------------------|----------------|-----|-----|--------|

| Parameter                              | Symbol  |                              |                                      | Min            | Тур | Max | Unit   |

| Input Offset Voltage                   | N/IC    | Rs≤10KΩ                      |                                      | -              | 2   | 6   | mV     |

|                                        | VIO     |                              | Note 1                               | -              | -   | 7.5 | IIIV   |

| Input Offset Current                   |         |                              |                                      | -              | 5   | 200 |        |

|                                        | lio     |                              | TA=TA(MAX)                           | -              | -   | 300 | nA     |

|                                        |         |                              | TA =TA(MIN)                          | -              | -   | 300 |        |

| Input Bias Current                     |         |                              | T <sub>A</sub> =T <sub>A</sub> (MAX) |                | 30  | 500 | nA     |

|                                        | IBIAS   |                              |                                      |                | -   | 800 |        |

|                                        |         |                              | TA =TA(MIN)                          | -              | -   | 800 |        |

| Large Signal                           |         | VO(P-P)= ±1                  | 0V,RL≤2KΩ                            | 20             | 200 | -   | V/mV   |

| Voltage Gain                           | 0,      |                              | Note 1                               | -              | -   | -   | V/IIIV |

| Common Mode Input<br>Voltage Range     | VI(R)   |                              |                                      |                | ±13 | -   | V      |

|                                        | VI(R)   |                              | Note 1                               | -              | -   | -   | v      |

| Common Mode<br>Rejection Ratio         | CMRR    | Rs≤10KΩ                      |                                      | 70             | 90  | -   | - dB   |

|                                        | CIMICIC |                              | Note 1                               | -              | -   | -   |        |

| Supply Voltage<br>Rejection Ratio      | PSRR    | Rs≤10KΩ                      |                                      | 76             | 90  | -   | dB     |

|                                        | 1 OKK   |                              | Note 1                               | 76             | 90  | -   | чЪ     |

| Output Voltage Swing                   | VO(P-P) | RL≥10KΩ                      | - Note1                              | ±12            | ±14 | -   | V      |

|                                        | VO(P-P) | RL≥2KΩ                       | Noter                                | ±10            | ±13 | -   |        |

| Supply Current<br>(Both Amplifiers)    |         |                              |                                      | -              | 3.5 | 5.8 | mA     |

|                                        | ICC     |                              | TA =TA(MAX)                          | 1              | -   | 5.0 |        |

|                                        |         |                              | TA =TA(MIN)                          | -              | -   | 6.7 |        |

| Power Consumption<br>(Both Amplifiers) |         | TA =TA(MAX)                  |                                      | 1              | 70  | 170 | mW     |

|                                        | PC      |                              |                                      | -              | -   | 150 |        |

|                                        |         |                              | $T_a = T_A(MIN)$                     | -              | -   | 200 |        |

| Slew Rate (Note2)                      | SR      | VI =10V, RL≥2KΩ<br>CI≤100pF  |                                      | 1.2            | -   | -   | V/µs   |

| Rise Time (Note2)                      | TR      | VI =20mV, RL≥2KΩ<br>CI≤100pF |                                      | -              | 0.3 | -   | μs     |

| Overshoot (Note2)                      | OS      | VI =20mV, RL≥2KΩ<br>CI≤100pF |                                      | -              | 15  | -   | %      |

#### Note :

$1. \text{ KA4558}: \text{T}_{A}(\text{MIN}) \leq \text{T}_{A} \leq \text{T}_{A}(\text{MAX}) = 0 \leq \text{T}_{A} \leq 70 \ ^{\circ}\text{C} \ , \ \text{KA4558I}: \text{T}_{A}(\text{MIN}) \leq \text{T}_{A} \leq \text{T}_{A}(\text{MAX}) = -40 \leq \text{T}_{A} \leq +85 \ ^{\circ}\text{C}$

2. Guaranteed by design.

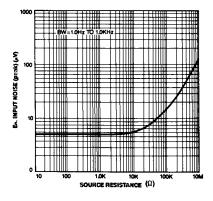

Figure 1. Burst Noise vs Source Resistance

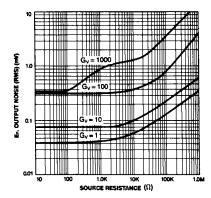

Figure 3. Output Noise vs Source Resistance

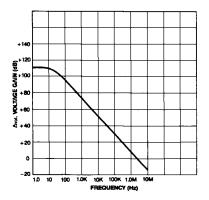

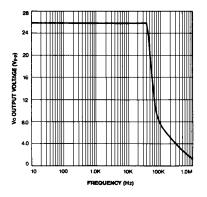

Figure 5. Open Loop Frequency Response

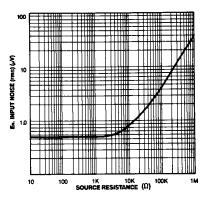

Figure 2. RMS Noise vs Source Resistance

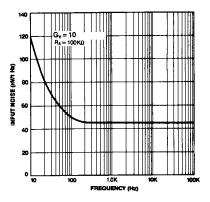

Figure 4. Spectral Noise Density

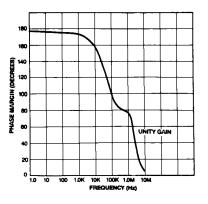

Figure 6. Phase Margin vs Frequency

## **Typical Performance Characteristics (continued)**

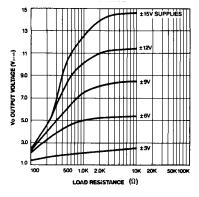

Figure 7. Positive Output Voltage Swing vs Load Resistance

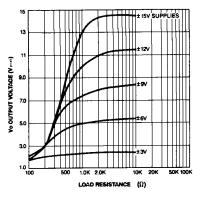

Figure 8. Negative Output Voltage Swing vs Load Resistance

Figure 9. Power Bandwidth (Large Signal Output Swing vs Frequency)

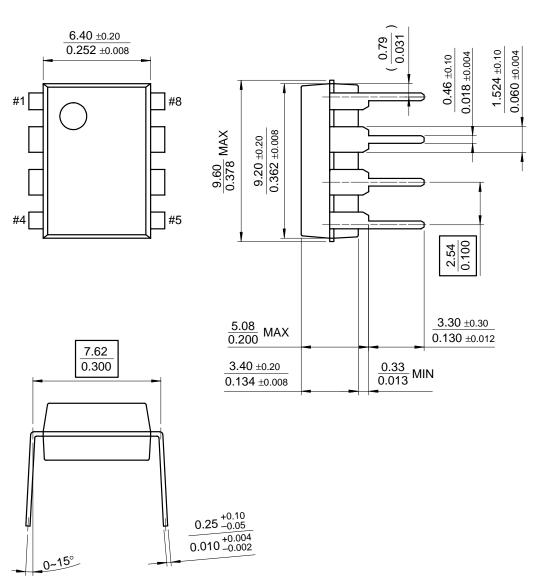

#### **Mechanical Dimensions**

#### Package

8-DIP

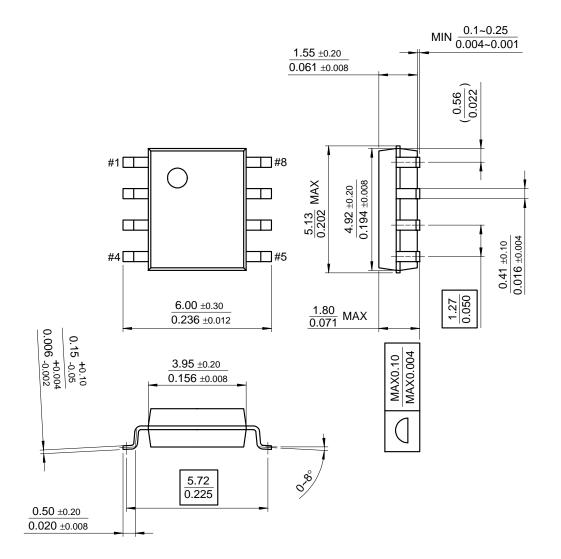

#### **Mechanical Dimensions** (Continued)

#### Package

# 8-SOP

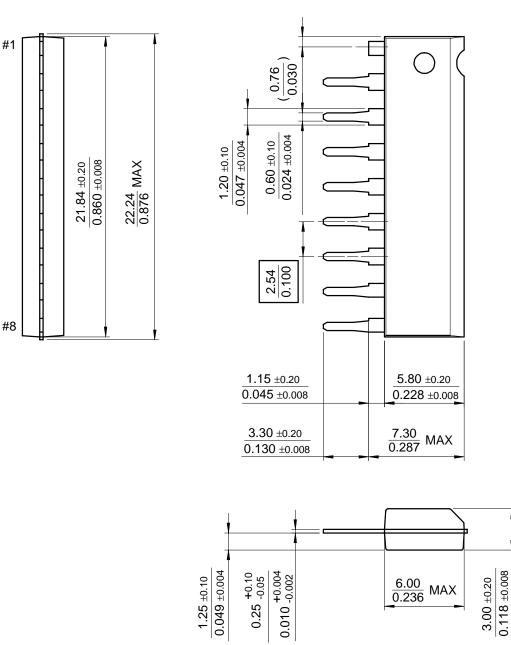

#### Mechanical Dimensions (Continued)

#### Package

9-SIP

# **Ordering Information**

| Product Number | Package | Operating Temperature |  |  |

|----------------|---------|-----------------------|--|--|

| KA4558         | 8-DIP   |                       |  |  |

| KA4558D        | 8-SOP   | 0 ~ + 70°C            |  |  |

| KA4558S        | 9-SIP   |                       |  |  |

| KA4558I        | 8-DIP   | -40 ~ + 85°C          |  |  |

#### DISCLAIMER

FAIRCHILD SEMICONDUCTOR RESERVES THE RIGHT TO MAKE CHANGES WITHOUT FURTHER NOTICE TO ANY PRODUCTS HEREIN TO IMPROVE RELIABILITY, FUNCTION OR DESIGN. FAIRCHILD DOES NOT ASSUME ANY LIABILITY ARISING OUT OF THE APPLICATION OR USE OF ANY PRODUCT OR CIRCUIT DESCRIBED HEREIN; NEITHER DOES IT CONVEY ANY LICENSE UNDER ITS PATENT RIGHTS, NOR THE RIGHTS OF OTHERS.

#### LIFE SUPPORT POLICY

FAIRCHILD'S PRODUCTS ARE NOT AUTHORIZED FOR USE AS CRITICAL COMPONENTS IN LIFE SUPPORT DEVICES OR SYSTEMS WITHOUT THE EXPRESS WRITTEN APPROVAL OF THE PRESIDENT OF FAIRCHILD SEMICONDUCTOR CORPORATION. As used herein:

- Life support devices or systems are devices or systems which, (a) are intended for surgical implant into the body, or (b) support or sustain life, and (c) whose failure to perform when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury of the user.

- A critical component in any component of a life support device or system whose failure to perform can be reasonably expected to cause the failure of the life support device or system, or to affect its safety or effectiveness.

www.fairchildsemi.com