## 4:1 HDMI/DVI Switch with Equalization

AD8197B

#### **FEATURES**

4 inputs, 1 output HDMI/DVI links **Enables HDMI 1.3-compliant receiver** Pin-to-pin compatible with the AD8197A

4 TMDS channels per link

Supports 250 Mbps to 2.25 Gbps data rates Supports 25 MHz to 225 MHz pixel clocks Equalized inputs allow use of long HDMI cables (20 meters at 2.25 Gbps)

Fully buffered unidirectional inputs/outputs Per input switchable, 50  $\Omega$  on-chip terminations Switchable output 50  $\Omega$  on-chip terminations **Pre-emphasized outputs** Low added jitter

Single-supply operation (3.3 V)

4 auxiliary channels per link

**Bidirectional unbuffered inputs/outputs**

Flexible supply operation (3.3 V to 5 V)

**HDCP standard compatible**

Allows switching of DDC bus and 2 additional signals

#### **Output disable feature**

**Reduced power dissipation** Removable output termination Allows building of larger arrays

Two AD8197Bs support HDMI/DVI dual link Standards compatible: HDMI receiver, HDCP, DVI Serial (I<sup>2</sup>C slave) and parallel control interface 100-lead, 14 mm × 14 mm LQFP, Pb-free package

#### **APPLICATIONS**

Multiple input displays **Projectors** A/V receivers **Set-top boxes** Advanced television (HDTV) sets

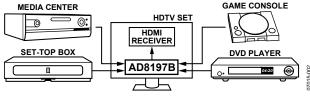

#### TYPICAL APPLICATION

Figure 1. Typical HDTV Application

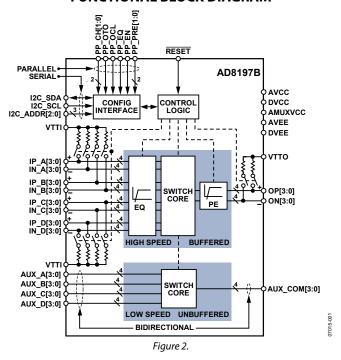

#### FUNCTIONAL BLOCK DIAGRAM

#### **GENERAL DESCRIPTION**

The AD8197B is an HDMI™/DVI switch featuring equalized TMDS\* inputs and pre-emphasized TMDS outputs, ideal for systems with long cable runs. The AD8197B offers individual control of the on/off state of the TMDS input termination resistors via I<sup>2</sup>C° control. Outputs can be set to a high impedance state to reduce the power dissipation and/or to allow the construction of larger arrays using the wire-OR technique.

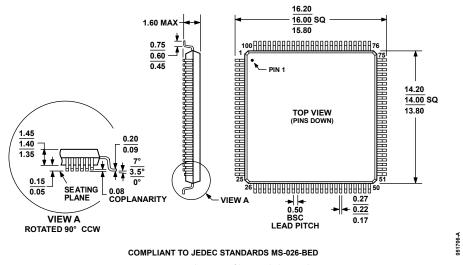

The AD8197B is provided in a 100-lead LQFP, Pb-free, surfacemount package, specified to operate over the -40°C to +85°C temperature range.

#### **PRODUCT HIGHLIGHTS**

- Supports data rates up to 2.25 Gbps, enabling 1080p deep color (12-bit color) HDMI formats and greater than UXGA  $(1600 \times 1200)$  DVI resolutions.

- Input cable equalizer enables use of long cables at the input (more than 20 meters of 24 AWG cable at 2.25 Gbps).

- Auxiliary switch routes a DDC bus and two additional signals for a single-chip, HDMI 1.3 receive-compliant solution.

## **AD8197B\* Product Page Quick Links**

Last Content Update: 08/30/2016

### Comparable Parts

View a parametric search of comparable parts

### Evaluation Kits <a> □</a>

• AD8197B Evaluation Board

### Documentation <a>□</a>

#### **Data Sheet**

AD8197B: 4:1 HDMI/DVI Switch with Equalization Data Sheet

### Reference Materials

#### Informational

• Advantiv<sup>TM</sup> Advanced TV Solutions

#### **Technical Articles**

• Analysis of Common Failures of HDMI CT

## Design Resources -

- AD8197B Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### Discussions <a>□</a>

View all AD8197B EngineerZone Discussions

## Sample and Buy 🖳

Visit the product page to see pricing options

### Technical Support <a> □</a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

## **TABLE OF CONTENTS**

| Features                                    | 1 |

|---------------------------------------------|---|

| Applications                                | 1 |

| Typical Application                         | 1 |

| Functional Block Diagram                    | 1 |

| General Description                         | 1 |

| Product Highlights                          | 1 |

| Revision History                            | 2 |

| Specifications                              | 3 |

| Absolute Maximum Ratings                    | 5 |

| Thermal Resistance                          | 5 |

| Maximum Power Dissipation                   | 5 |

| ESD Caution                                 | 5 |

| Pin Configuration and Function Descriptions | 6 |

| Typical Performance Characteristics         | 9 |

| Theory of Operation1                        | 3 |

| Introduction1                               | 3 |

| Input Channels1                             | 3 |

| Output Channels1                            | 3 |

| Auxiliary Switch1                           | 4 |

| Serial Control Interface1                   | 5 |

| Reset                                       | 5 |

| Write Procedure1                            | 5 |

| Read Procedure1                             | 6 |

|    | Switching/Update Delay                             | 16 |  |  |  |  |  |  |

|----|----------------------------------------------------|----|--|--|--|--|--|--|

| P  | arallel Control Interface                          | 17 |  |  |  |  |  |  |

| Se | Serial Interface Configuration Registers           |    |  |  |  |  |  |  |

|    | High Speed Device Modes Register                   | 19 |  |  |  |  |  |  |

|    | Auxiliary Device Modes Register                    | 19 |  |  |  |  |  |  |

|    | Receiver Settings Register                         | 19 |  |  |  |  |  |  |

|    | Input Termination Select Register 1 and Register 2 | 19 |  |  |  |  |  |  |

|    | Receive Equalizer Register 1 and Register 2        | 19 |  |  |  |  |  |  |

|    | Transmitter Settings Register                      | 20 |  |  |  |  |  |  |

| P  | arallel Interface Configuration Registers          | 21 |  |  |  |  |  |  |

|    | High Speed Device Modes Register                   | 22 |  |  |  |  |  |  |

|    | Auxiliary Device Modes Register                    | 22 |  |  |  |  |  |  |

|    | Input Termination Resistor Control Register 1      |    |  |  |  |  |  |  |

|    | and Register 2                                     | 22 |  |  |  |  |  |  |

|    | Receive Equalizer Register 1 and Register 2        | 22 |  |  |  |  |  |  |

|    | Transmitter Settings Register                      | 22 |  |  |  |  |  |  |

| A  | pplication Information                             | 23 |  |  |  |  |  |  |

|    | Pinout                                             | 23 |  |  |  |  |  |  |

|    | Cable Lengths and Equalization                     | 23 |  |  |  |  |  |  |

|    | PCB Layout Guidelines                              | 24 |  |  |  |  |  |  |

| 0  | Outline Dimensions                                 | 28 |  |  |  |  |  |  |

|    | Ordering Guide                                     | 28 |  |  |  |  |  |  |

#### **REVISION HISTORY**

1/08—Revision 0: Initial Version

## **SPECIFICATIONS**

$T_A$  = 27°C, AVCC = 3.3 V, VTTI = 3.3 V, VTTO = 3.3 V, DVCC = 3.3 V, AMUXVCC = 5 V, AVEE = 0 V, DVEE = 0 V, differential input swing = 1000 mV, TMDS outputs terminated with external 50  $\Omega$  resistors to 3.3 V, unless otherwise noted.

Table 1.

| Parameter                                     | Conditions/Comments                                  | Min        | Тур  | Max                 | Unit     |

|-----------------------------------------------|------------------------------------------------------|------------|------|---------------------|----------|

| DYNAMIC PERFORMANCE                           |                                                      |            |      |                     |          |

| Maximum Data Rate (DR) per Channel            | NRZ                                                  | 2.25       |      |                     | Gbps     |

| Bit Error Rate (BER)                          | PRBS 2 <sup>23</sup> – 1                             |            |      | 10 <sup>-9</sup>    |          |

| Added Deterministic Jitter                    | $DR \le 2.25 \text{ Gbps}, PRBS 2^7 - 1, EQ = 12 dB$ |            | 25   |                     | ps (p-p) |

| Added Random Jitter                           |                                                      |            | 1    |                     | ps (rms) |

| Differential Intrapair Skew                   | At output                                            |            | 1    |                     | ps       |

| Differential Interpair Skew <sup>1</sup>      | At output                                            |            | 40   |                     | ps       |

| EQUALIZATION PERFORMANCE                      |                                                      |            |      |                     | -        |

| Receiver (Highest Setting) <sup>2</sup>       | Boost frequency = 825 MHz                            |            | 12   |                     | dB       |

| Transmitter (Highest Setting) <sup>3</sup>    | Boost frequency = 825 MHz                            |            | 6    |                     | dB       |

| INPUT CHARACTERISTICS                         | , ,                                                  |            |      |                     |          |

| Input Voltage Swing                           | Differential                                         | 150        |      | 1200                | mV       |

| Input Common-Mode Voltage (V <sub>ICM</sub> ) |                                                      | AVCC - 800 |      | AVCC                | mV       |

| OUTPUT CHARACTERISTICS                        |                                                      |            |      |                     |          |

| High Voltage Level                            | Single-ended high speed channel                      | AVCC – 10  |      | AVCC + 10           | mV       |

| Low Voltage Level                             | Single-ended high speed channel                      | AVCC – 600 |      | AVCC – 400          | mV       |

| Rise/Fall Time (20% to 80%)                   | ζ , , , , , , , , , , , , , , , , , , ,              | 75         | 135  | 200                 | ps       |

| INPUT TERMINATION                             |                                                      |            |      |                     | F        |

|                                               | Single-ended                                         |            | FO   |                     |          |

| Resistance                                    | Single-ended                                         |            | 50   |                     | Ω        |

| AUXILIARY CHANNELS                            |                                                      |            | 100  |                     |          |

| On Resistance, R <sub>AUX</sub>               | DC his 25 V 25 V f 100 hts                           |            | 100  |                     | Ω        |

| On Capacitance, C <sub>AUX</sub>              | DC bias = 2.5 V, ac voltage = 3.5 V, f = 100 kHz     | D)/FF      | 8    | A A A L I V V V C C | pF       |

| Input/Output Voltage Range                    |                                                      | DVEE       |      | AMUXVCC             | V        |

| POWER SUPPLY                                  |                                                      |            |      | 2.6                 | .,       |

| AVCC                                          | Operating range                                      | 3          | 3.3  | 3.6                 | V        |

| QUIESCENT CURRENT                             |                                                      |            |      |                     |          |

| AVCC                                          | Outputs disabled                                     | 30         | 40   | 44                  | mA       |

|                                               | Outputs enabled, no pre-emphasis                     | 52         | 60   | 66                  | mA       |

|                                               | Outputs enabled, maximum pre-emphasis                | 95         | 110  | 122                 | mA       |

| VTTI                                          | Input termination on <sup>4</sup>                    | 5          | 40   | 54                  | mA       |

| VTTO                                          | Output termination on, no pre-emphasis               | 35         | 40   | 46                  | mA       |

|                                               | Output termination on, maximum pre-emphasis          | 72         | 80   | 90                  | mA       |

| DVCC                                          |                                                      | 3.2        | 7    | 8                   | mA       |

| AMUXVCC                                       |                                                      |            | 0.01 | 0.1                 | mA       |

| POWER DISSIPATION                             |                                                      |            |      |                     |          |

|                                               | Outputs disabled                                     | 115        | 271  | 361                 | mW       |

|                                               | Outputs enabled, no pre-emphasis                     | 384        | 574  | 671                 | mW       |

|                                               | Outputs enabled, maximum pre-emphasis                | 704        | 910  | 1050                | mW       |

| TIMING CHARACTERISTICS                        |                                                      |            | -    |                     |          |

| Switching/Update Delay                        | High speed switching register: HS_CH                 |            |      | 200                 | ms       |

|                                               | All other configuration registers                    |            |      | 1.5                 | ms       |

| RESET Pulse Width                             |                                                      | 50         |      |                     | ns       |

| Parameter                             | Conditions/Comments | Min | Тур Мах | Unit |

|---------------------------------------|---------------------|-----|---------|------|

| SERIAL CONTROL INTERFACE <sup>5</sup> |                     |     |         |      |

| Input High Voltage, V <sub>IH</sub>   |                     | 2   |         | V    |

| Input Low Voltage, V <sub>IL</sub>    |                     |     | 0.8     | V    |

| Output High Voltage, V <sub>OH</sub>  |                     | 2.4 |         | V    |

| Output Low Voltage, Vol               |                     |     | 0.4     | V    |

| PARALLEL CONTROL INTERFACE            |                     |     |         |      |

| Input High Voltage, V <sub>IH</sub>   |                     | 2   |         | V    |

| Input Low Voltage, V <sub>IL</sub>    |                     |     | 0.8     | V    |

Differential interpair skew is measured between the TMDS pairs of a single link.

AD8197B output meets the transmitter eye diagram as defined in the DVI Standard Revision 1.0 and the HDMI Standard Revision 1.3.

Cable output meets the receiver eye diagram mask as defined in the DVI Standard Revision 1.0 and the HDMI Standard Revision 1.3.

Typical value assumes only the selected HDMI/DVI link is active with nominal signal swings and that the unselected HDMI/DVI links are deactivated. Minimum and maximum limits are measured at the respective extremes of input termination resistance and input voltage swing.

<sup>&</sup>lt;sup>5</sup> The AD8197B is an I<sup>2</sup>C slave and its serial control interface is based on the 3.3 V I<sup>2</sup>C bus specification.

### **ABSOLUTE MAXIMUM RATINGS**

Table 2.

| Parameter                                         | Rating                                           |

|---------------------------------------------------|--------------------------------------------------|

| AVCC to AVEE                                      | 3.7 V                                            |

| DVCC to DVEE                                      | 3.7 V                                            |

| DVEE to AVEE                                      | ±0.3 V                                           |

| VTTI                                              | AVCC + 0.6 V                                     |

| VTTO                                              | AVCC + 0.6 V                                     |

| AMUXVCC                                           | 5.5 V                                            |

| Internal Power Dissipation                        | 2.2 W                                            |

| High Speed Input Voltage                          | AVCC - 1.4 V < V <sub>IN</sub> < AVCC + 0.6 V    |

| High Speed Differential Input Voltage             | 2.0 V                                            |

| Low Speed Input Voltage                           | DVEE - 0.3 V < V <sub>IN</sub> < AMUXVCC + 0.6 V |

| I <sup>2</sup> C and Parallel Logic Input Voltage | DVEE - 0.3 V < V <sub>IN</sub> < DVCC + 0.6 V    |

| Storage Temperature Range                         | −65°C to +125°C                                  |

| Operating Temperature Range                       | −40°C to +85°C                                   |

| Junction Temperature                              | 150°C                                            |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### THERMAL RESISTANCE

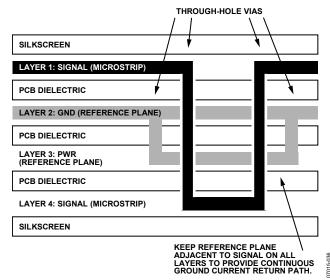

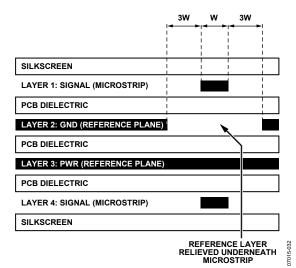

$\theta_{JA}$  is specified for the worst-case conditions: a device soldered in a 4-layer JEDEC circuit board for surface-mount packages.  $\theta_{JC}$  is specified for no airflow.

**Table 3. Thermal Resistance**

| Package Type  | $\theta_{JA}$ | θ <sub>JC</sub> | Unit |

|---------------|---------------|-----------------|------|

| 100-Lead LQFP | 56            | 19              | °C/W |

#### **MAXIMUM POWER DISSIPATION**

The maximum power that can be safely dissipated by the AD8197B is limited by the associated rise in junction temperature. The maximum safe junction temperature for plastic encapsulated devices is determined by the glass transition temperature of the plastic, approximately 150°C. Temporarily exceeding this limit may cause a shift in parametric performance due to a change in the stresses exerted on the die by the package.

Exceeding a junction temperature of 175°C for an extended period can result in device failure. To ensure proper operation, it is necessary to observe the maximum power rating as determined by the coefficients in Table 3.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

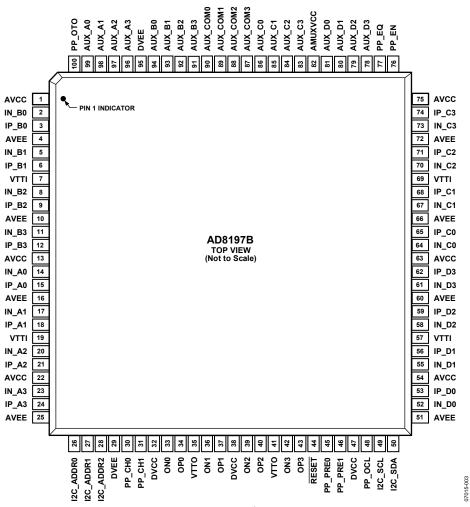

## PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 3. Pin Configuration

**Table 4. Pin Function Descriptions**

| Pin No.                       | Mnemonic | Type <sup>1</sup> | Description                                            |

|-------------------------------|----------|-------------------|--------------------------------------------------------|

| 1, 13, 22, 54, 63, 75         | AVCC     | Power             | Positive Analog Supply. 3.3 V nominal.                 |

| 2                             | IN_B0    | HS I              | High Speed Input Complement.                           |

| 3                             | IP_B0    | HS I              | High Speed Input.                                      |

| 4, 10, 16, 25, 51, 60, 66, 72 | AVEE     | Power             | Negative Analog Supply. 0 V nominal.                   |

| 5                             | IN_B1    | HS I              | High Speed Input Complement.                           |

| 6                             | IP_B1    | HS I              | High Speed Input.                                      |

| 7, 19, 57, 69                 | VTTI     | Power             | Input Termination Supply. Nominally connected to AVCC. |

| 8                             | IN_B2    | HS I              | High Speed Input Complement.                           |

| 9                             | IP_B2    | HS I              | High Speed Input.                                      |

| 11                            | IN_B3    | HS I              | High Speed Input Complement.                           |

| 12                            | IP_B3    | HS I              | High Speed Input.                                      |

| 14                            | IN_A0    | HS I              | High Speed Input Complement.                           |

| 15                            | IP_A0    | HS I              | High Speed Input.                                      |

| 17                            | IN_A1    | HS I              | High Speed Input Complement.                           |

| 18                            | IP_A1    | HS I              | High Speed Input.                                      |

| 20                            | IN_A2    | HS I              | High Speed Input Complement.                           |

| 21                            | IP_A2    | HS I              | High Speed Input.                                      |

Rev. 0 | Page 6 of 28

| Pin No.             | Mnemonic             | Type <sup>1</sup> | Description                                                           |

|---------------------|----------------------|-------------------|-----------------------------------------------------------------------|

| 23                  | IN_A3                | HS I              | High Speed Input Complement.                                          |

| 24                  | IP_A3                | HS I              | High Speed Input.                                                     |

| 26                  | I2C_ADDR0            | Control           | I <sup>2</sup> C Address 1 <sup>st</sup> LSB.                         |

| 27                  | I2C_ADDR1            | Control           | I <sup>2</sup> C Address 2 <sup>nd</sup> LSB.                         |

| 28                  | I2C_ADDR2            | Control           | I <sup>2</sup> C Address 3 <sup>rd</sup> LSB.                         |

| 29, 95              | DVEE                 | Power             | Negative Digital and Auxiliary Multiplexer Power Supply. 0 V nominal. |

| 30                  | PP_CH0               | Control           | High Speed Source Selection Parallel Interface LSB.                   |

| 31                  | PP_CH1               | Control           | High Speed Source Selection Parallel Interface MSB.                   |

| 32, 38, 47          | DVCC                 | Power             | Positive Digital Power Supply. 3.3 V nominal.                         |

| 33                  | ON0                  | HS O              | High Speed Output Complement.                                         |

| 34                  | OP0                  | HS O              | High Speed Output.                                                    |

| 35, 41              | VTTO                 | Power             | Output Termination Supply. Nominally connected to AVCC.               |

| 36                  | ON1                  | HS O              | High Speed Output Complement.                                         |

| 37                  | OP1                  | HS O              | High Speed Output.                                                    |

| 39                  | ON2                  | HS O              | High Speed Output Complement.                                         |

| 40                  | OP2                  | HS O              | High Speed Output.                                                    |

| 42                  | ON3                  | HS O              | High Speed Output Complement.                                         |

| 43                  | OP3                  | HS O              | High Speed Output.                                                    |

| +3<br>14            | RESET                | Control           | Configuration Registers Reset. Normally pulled up to AVCC.            |

| <del>44</del><br>45 | PP_PRE0              | Control           | High Speed Pre-Emphasis Selection Parallel Interface LSB.             |

|                     |                      |                   |                                                                       |

| 46                  | PP_PRE1              | Control           | High Speed Pre-Emphasis Selection Parallel Interface MSB.             |

| 48                  | PP_OCL               | Control           | High Speed Output Current Level Parallel Interface.                   |

| 49<br>              | I2C_SCL              | Control           | I <sup>2</sup> C Clock.                                               |

| 50                  | I2C_SDA              | Control           | I <sup>2</sup> C Data.                                                |

| 52                  | IN_D0                | HS I              | High Speed Input Complement.                                          |

| 53                  | IP_D0                | HS I              | High Speed Input.                                                     |

| 55                  | IN_D1                | HS I              | High Speed Input Complement.                                          |

| 56                  | IP_D1                | HS I              | High Speed Input.                                                     |

| 58                  | IN_D2                | HS I              | High Speed Input Complement.                                          |

| 59                  | IP_D2                | HS I              | High Speed Input.                                                     |

| 61                  | IN_D3                | HS I              | High Speed Input Complement.                                          |

| 62                  | IP_D3                | HS I              | High Speed Input.                                                     |

| 64                  | IN_C0                | HS I              | High Speed Input Complement.                                          |

| 65                  | IP_C0                | HS I              | High Speed Input.                                                     |

| 67                  | IN_C1                | HSI               | High Speed Input Complement.                                          |

| 68                  | IP_C1                | HS I              | High Speed Input.                                                     |

| 70                  | IN_C2                | HS I              | High Speed Input Complement.                                          |

| 71                  | IP_C2                | HS I              | High Speed Input.                                                     |

| 73                  | IN_C3                | HSI               | High Speed Input Complement.                                          |

| 74                  | IP_C3                | HSI               | High Speed Input.                                                     |

| 76                  | PP_EN                | Control           | High Speed Output Enable Parallel Interface.                          |

| 77                  | PP_EQ                | Control           | High Speed Equalization Selection Parallel Interface.                 |

| 78                  | AUX_D3               | LS I/O            | Low Speed Input/Output.                                               |

| 79                  | AUX_D2               | LS I/O            | Low Speed Input/Output.                                               |

| 80                  | AUX_D1               | LS I/O            | Low Speed Input/Output.                                               |

| 81                  | AUX_D0               | LS I/O            | Low Speed Input/Output.                                               |

| 82                  | AMUXVCC              | Power             | Positive Auxiliary Multiplexer Supply. 5 V typical.                   |

| 83                  | AUX_C3               | LS I/O            | Low Speed Input/Output.                                               |

| 84                  | AUX_C2               | LS I/O            | Low Speed Input/Output.                                               |

| 85                  | AUX_C2<br>AUX_C1     | LS I/O            | Low Speed Input/Output.  Low Speed Input/Output.                      |

|                     |                      |                   |                                                                       |

| 86<br>97            | AUX_CO               | LS I/O            | Low Speed Input/Output.                                               |

| 87<br>88            | AUX_COM3<br>AUX_COM2 | LS I/O<br>LS I/O  | Low Speed Common Input/Output.  Low Speed Common Input/Output.        |

| Pin No. | Mnemonic | Type <sup>1</sup> | Description                                                 |

|---------|----------|-------------------|-------------------------------------------------------------|

| 89      | AUX_COM1 | LS I/O            | Low Speed Common Input/Output.                              |

| 90      | AUX_COM0 | LS I/O            | Low Speed Common Input/Output.                              |

| 91      | AUX_B3   | LS I/O            | Low Speed Input/Output.                                     |

| 92      | AUX_B2   | LS I/O            | Low Speed Input/Output.                                     |

| 93      | AUX_B1   | LS I/O            | Low Speed Input/Output.                                     |

| 94      | AUX_B0   | LS I/O            | Low Speed Input/Output.                                     |

| 96      | AUX_A3   | LS I/O            | Low Speed Input/Output.                                     |

| 97      | AUX_A2   | LS I/O            | Low Speed Input/Output.                                     |

| 98      | AUX_A1   | LS I/O            | Low Speed Input/Output.                                     |

| 99      | AUX_A0   | LS I/O            | Low Speed Input/Output.                                     |

| 100     | PP_OTO   | Control           | High Speed Output Termination Selection Parallel Interface. |

$<sup>^{1}</sup>$  HS = high speed, LS = low speed, I = input, O = output.

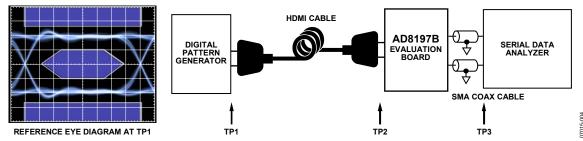

### TYPICAL PERFORMANCE CHARACTERISTICS

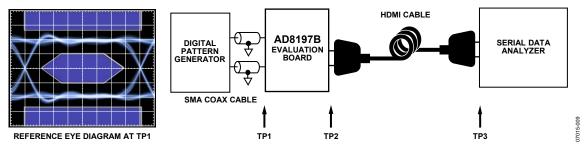

Figure 4. Test Circuit Diagram for Rx Eye Diagram

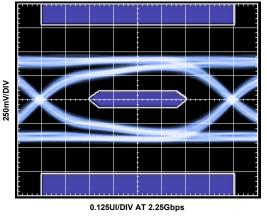

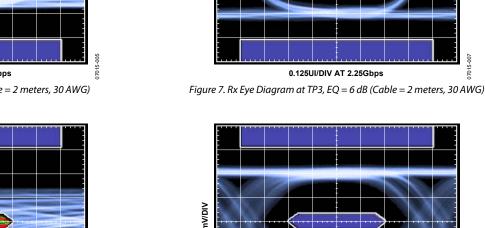

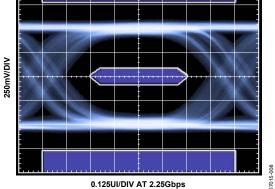

Figure 5. Rx Eye Diagram at TP2 (Cable = 2 meters, 30 AWG)

Figure 6. Rx Eye Diagram at TP2 (Cable = 20 meters, 24 AWG)

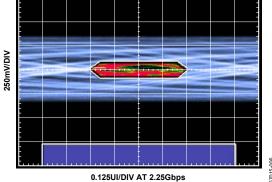

Figure 8. Rx Eye Diagram at TP3, EQ = 12 dB (Cable = 20 meters, 24 AWG)

Figure 9. Test Circuit Diagram for Tx Eye Diagrams

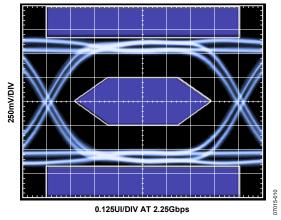

Figure 10. Tx Eye Diagram at TP2, PE = 2 dB

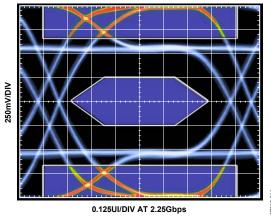

Figure 12. Tx Eye Diagram at TP3, PE = 2 dB (Cable = 2 meters, 30 AWG)

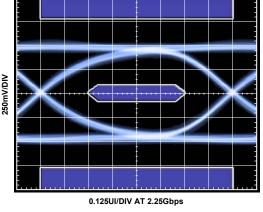

Figure 11. Tx Eye Diagram at TP2, PE = 6 dB

Figure 13. Tx Diagram at TP3, PE = 6 dB (Cable = 10 meters, 28 AWG)

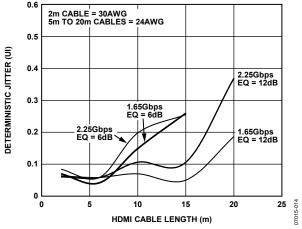

Figure 14. Jitter vs. Input Cable Length (See Figure 4 for Test Setup)

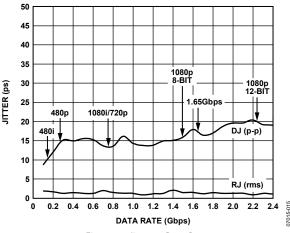

Figure 15. Jitter vs. Data Rate

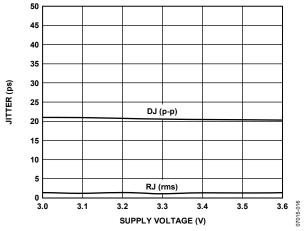

Figure 16. Jitter vs. Supply Voltage

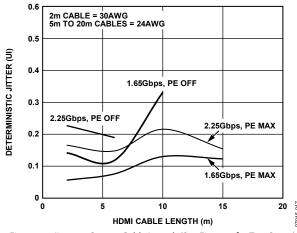

Figure 17. Jitter vs. Output Cable Length (See Figure 9 for Test Setup)

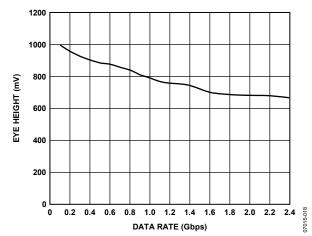

Figure 18. Eye Height vs. Data Rate

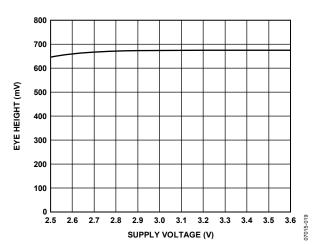

Figure 19. Eye Height vs. Supply Voltage

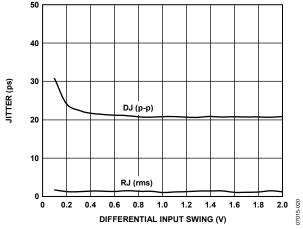

Figure 20. Jitter vs. Differential Input Swing

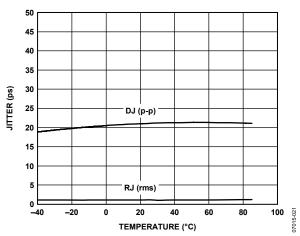

Figure 21. Jitter vs. Temperature

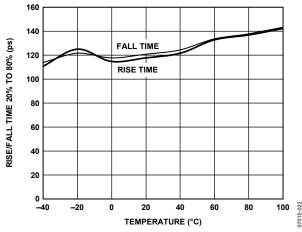

Figure 22. Rise and Fall Time vs. Temperature

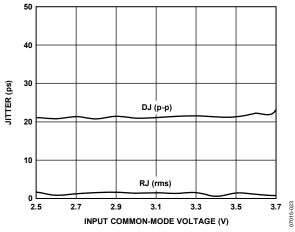

Figure 23. Jitter vs. Input Common-Mode Voltage

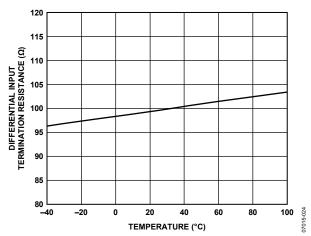

Figure 24. Differential Input Termination Resistance vs. Temperature

# THEORY OF OPERATION INTRODUCTION

The AD8197B is a pin-to-pin HDMI 1.3 receive-compliant replacement for the AD8197A. The primary function of the AD8197B is to switch one of four (HDMI or DVI) single link sources to one output. Each HDMI/DVI link consists of four differential, high speed channels and four auxiliary single-ended, low speed control signals. The high speed channels include a data-word clock and three transition minimized differential signaling (TMDS) data channels running at 10× the data-word clock frequency for data rates up to 2.25 Gbps. The four low speed control signals are 5 V tolerant bidirectional lines that can carry configuration signals, HDCP encryption, and other information, depending upon the specific application.

All four high speed TMDS channels in a given link are identical; that is, the pixel clock can be run on any of the four TMDS channels. Transmit and receive channel compensation is provided for the high speed channels where the user can (manually) select among a number of fixed settings.

The AD8197B has two control interfaces. Users have the option of controlling the part through either the parallel control interface or the  $\rm I^2C$  serial control interface. However, the parallel control interface is not able to control the switch status of the input termination resistors and therefore has limited usefulness in practical systems. Most systems use only the  $\rm I^2C$  serial interface.

The AD8197B has eight user-programmable I<sup>2</sup>C slave addresses to allow multiple AD8197Bs to be controlled by a single I<sup>2</sup>C bus. A RESET pin is provided to restore the control registers of the AD8197B to the parallel control interface and some default values. In all cases, serial programming values override any prior parallel programming values, and any use of the serial control interface disables the parallel control interface until the AD8197B is reset.

#### **INPUT CHANNELS**

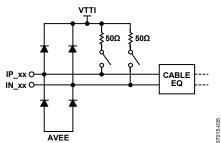

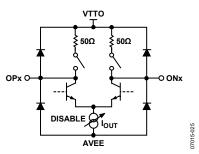

Each high speed input differential pair terminates to the 3.3 V VTTI power supply through a pair of single-ended 50  $\Omega$  onchip resistors, as shown in Figure 25. The input termination status for each individual high speed differential (TMDS) input pair can be controlled by programming the appropriate RX\_TO bit in the receiver settings register. Refer to Table 5 and Table 12. By default, the input terminations are disabled (switched open) after reset. The input terminations cannot be switched when programming the AD8197B through the parallel control interface. This limits the usefulness of the parallel control interface.

Some systems require that the input terminations be switched on only for the one selected HDMI source. The input terminations for the three unselected HDMI sources require their input termination switches to be open. The AD8197B can perform

this operation, but it is not automatic. To obtain this functionality, the channel selection and the input termination status must be separately programmed via the I<sup>2</sup>C serial control interface.

Figure 25. High Speed Input Simplified Schematic

The input equalizer can be manually configured to provide two different levels of high frequency boost: 6 dB or 12 dB. The user can individually control the equalization level of the eight high speed input channels by selectively programming the associated RX\_EQ bits in the receive equalizer register through the serial control interface. Alternately, the user can globally control the equalization level of all eight high speed input channels by setting the PP\_EQ pin of the parallel control interface. No specific cable length is suggested for a particular equalization setting because cable performance varies widely between manufacturers; however, in general, the equalization of the AD8197B can be set to 12 dB without degrading the signal integrity, even for short input cables. At the 12 dB setting, the AD8197B can equalize more than 20 meters of 24 AWG cable at 2.25 Gbps.

#### **OUTPUT CHANNELS**

Each high speed output differential pair is terminated to the 3.3 V VTTO power supply through two 50  $\Omega$  on-chip resistors (see Figure 26). This termination is user-selectable; it can be turned on or off by programming the TX\_PTO bit of the transmitter settings register through the serial control interface, or by setting the PP\_OTO pin of the parallel control interface.

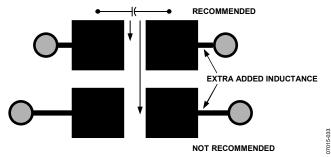

The output termination resistors of the AD8197B back-terminate the output TMDS transmission lines. These back-terminations, as recommended in the HDMI 1.3 specification, act to absorb reflections from impedance discontinuities on the output traces, improving the signal integrity of the output traces and adding flexibility to how the output traces can be routed. For example, interlayer vias can be used to route the AD8197B TMDS outputs on multiple layers of the PCB without severely degrading the quality of the output signal.

The AD8197B output has a disable feature that places the outputs in a tristate mode. This mode is enabled by programming the HS\_EN bit of the high speed device modes register through the serial control interface or by setting the PP\_EN pin of the parallel control interface. Larger wire-ORed arrays can be constructed using the AD8197B in this mode.

Figure 26. High Speed Output Simplified Schematic

The AD8197B requires output termination resistors when the high speed outputs are enabled. Termination can be internal and/or external. The internal terminations of the AD8197B are enabled by programming the TX\_PTO bit of the transmitter settings register or by setting the PP\_OTO pin of the parallel control interface. The internal terminations of the AD8197B default to the setting indicated by PP\_OTO upon reset. External terminations can be provided either by on-board resistors or by the input termination resistors of an HDMI/DVI receiver. If both the internal terminations are enabled and external terminations are present, set the output current level to 20 mA by programming the TX\_OCL bit of the transmitter settings register through the serial control interface or by setting the PP OCL pin of the parallel control interface. The output current level defaults to the level indicated by PP\_OCL upon reset. If only external terminations are provided (if the internal terminations are disabled), set the output current level to 10 mA by programming the TX\_OCL bit of the transmitter settings register or by setting the PP OCL pin of the parallel control interface. The high speed outputs must be disabled if there are no output termination resistors present in the system.

The output pre-emphasis can be manually configured to provide one of four different levels of high frequency boost. The specific boost level is selected by programming the TX\_PE bits of the transmitter settings register through the serial control interface, or by setting the PP\_PE bus of the parallel control interface. No specific cable length is suggested for a particular pre-emphasis setting because cable performance varies widely between manufacturers.

#### **AUXILIARY SWITCH**

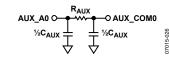

The auxiliary (low speed) lines have no amplification. They are routed using a passive switch that is bandwidth compatible with standard speed I<sup>2</sup>C. The schematic equivalent for this passive connection is shown in Figure 27.

Figure 27. Auxiliary Channel Simplified Schematic, AUX\_A0 to AUX\_COM0 Routing Example

When turning off the AD8197B, care needs to be taken with the AMUXVCC supply to ensure that the auxiliary multiplexer pins remain in a high impedance state. A scenario that illustrates this requirement is one where the auxiliary multiplexer is used to switch the display data channel (DDC) bus. In some applications, additional devices can be connected to the DDC bus (such as an EEPROM with EDID information) upstream of the AD8197B.

Extended display identification data (EDID) is a VESA standard-defined data format for conveying display configuration information to sources to optimize display use. EDID devices may need to be available via the DDC bus, regardless of the state of the AD8197B and any downstream circuit. For this configuration, the auxiliary inputs of the powered down AD8197B need to be in a high impedance state to avoid pulling down on the DDC lines and preventing these other devices from using the bus.

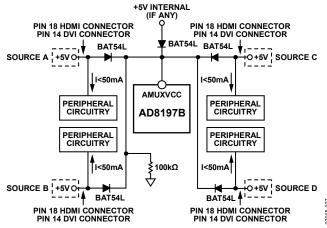

The AD8197B requires +5 V on its supply pin, AMUXVCC, in order for the AUXMUX channels to be high impedance. When a TV is powered off, it cannot provide such a supply. However, it can be provided from any HDMI source that is plugged into it. A Schottky diode network, as shown in Figure 28, uses the 5 V supply (Pin 18) from any HDMI/DVI source to power AMUXVCC and guarantee high impedance of the auxiliary multiplexer pins. The AMUXVCC supply does not draw any significant static current. The use of diodes ensures that connected HDMI sources do not load this circuit if their +5 V pin is low impedance when powered off. The 100  $k\Omega$  resistor ensures that a minimum of current flows through the diodes to keep them forward biased.

This precaution does not need to be taken if the DDC peripheral circuitry is connected to the bus downstream of the AD8197B.

Figure 28. Suggested AMUXVCC Power Scheme

# SERIAL CONTROL INTERFACE RESET

On initial power-up, or at any point in operation, the AD8197B register set can be restored to the status of the parallel control interface pins and some preprogrammed default values by pulling the RESET pin to low, in accordance with the specifications in Table 1. During normal operation, however, the RESET pin must be pulled up to 3.3 V. Following a reset, the preprogrammed default values of the AD8197B register set correspond to the state of the parallel interface configuration registers and defaults, as listed in Table 18. The AD8197B can be controlled through the parallel control interface until the first serial control event occurs. As soon as any serial control event occurs, the serial programming values, corresponding to the state of the serial interface configuration registers (Table 5), override any prior parallel programming values, and the parallel control interface is disabled until the part is subsequently reset.

Note that the input termination resistor switch control is only via I<sup>2</sup>C control. Therefore, any system that requires control of these switches cannot operate in parallel control mode.

#### WRITE PROCEDURE

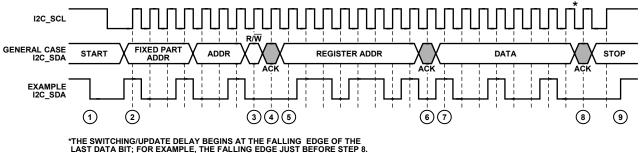

To write data to the AD8197B register set, an  $I^2C$  master (such as a microcontroller) needs to send the appropriate control signals to the AD8197B slave device. The signals are controlled by the  $I^2C$  master, unless otherwise specified. For a diagram of the procedure, see Figure 29. The steps for a write procedure are as follows:

- 1. Send a start condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line low).

- Send the AD8197B part address (seven bits). The upper four bits of the AD8197B part address are the static value [1001] and the three LSBs are set by Input Pin I2C\_ADDR2, Input Pin I2C\_ADDR1, and Input Pin I2C\_ADDR0 (LSB). This transfer should be MSB first.

- 3. Send the write indicator bit (0).

- 4. Wait for the AD8197B to acknowledge the request.

- 5. Send the register address (eight bits) to which data is to be written. This transfer should be MSB first.

- 6. Wait for the AD8197B to acknowledge the request.

- Send the data (eight bits) to be written to the register whose address was set in Step 5. This transfer should be MSB first.

- 8. Wait for the AD8197B to acknowledge the request.

- 9. Perform one of the following:

- 9a. Send a stop condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line high) and release control of the bus to end the transaction (shown in Figure 29).

- 9b. Send a repeated start condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line low) and continue with Step 2 in this procedure to perform another write.

- 9c. Send a repeated start condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line low) and continue with Step 2 of the read procedure (in the Read Procedure section) to perform a read from another address.

- 9d. Send a repeated start condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line low) and continue with Step 8 of the read procedure (in the Read Procedure section) to perform a read from the same address set in Step 5.

Figure 29. I<sup>2</sup>C Write Diagram

#### **READ PROCEDURE**

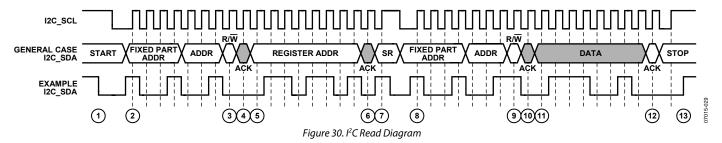

To read data from the AD8197B register set, an I<sup>2</sup>C master (such as a microcontroller) needs to send the appropriate control signals to the AD8197B slave device. The signals are controlled by the I<sup>2</sup>C master, unless otherwise specified. For a diagram of the procedure, see Figure 30. The steps for a read procedure are as follows:

- 1. Send a start condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line low).

- Send the AD8197B part address (seven bits). The upper four bits of the AD8197B part address are the static value [1001] and the three LSBs are set by Input Pin I2C\_ADDR2, Input Pin I2C\_ADDR1, and Input Pin I2C\_ADDR0 (LSB). This transfer should be MSB first.

- 3. Send the write indicator bit (0).

- 4. Wait for the AD8197B to acknowledge the request.

- 5. Send the register address (eight bits) from which data is to be read. This transfer should be MSB first.

- 6. Wait for the AD8197B to acknowledge the request.

- 7. Send a repeated start condition (Sr) by holding the I2C\_SCL line high and pulling the I2C\_SDA line low.

- 8. Resend the AD8197B part address (seven bits) from Step 2. The upper four bits of the AD8197B part address are the static value [1001] and the three LSBs are set by the Input Pin I2C\_ADDR2, I2C\_ADDR1 and Input Pin I2C\_ADDR0 (LSB). This transfer should be MSB first.

- 9. Send the read indicator bit (1).

- 10. Wait for the AD8197B to acknowledge the request.

- 11. The AD8197B serially transfers the data (eight bits) held in the register indicated by the address set in Step 5. This data is sent MSB first.

- 12. Acknowledge the data from the AD8197B.

#### 13. Perform one of the following:

- 13a. Send a stop condition (while holding the I2C\_SCL line high, pull the SDA line high) and release control of the bus to end the transaction (shown in Figure 30).

- 13b. Send a repeated start condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line low) and continue with Step 2 of the write procedure (previous Write Procedure section) to perform a write.

- 13c. Send a repeated start condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line low) and continue with Step 2 of this procedure to perform a read from another address.

- 13d. Send a repeated start condition (while holding the I2C\_SCL line high, pull the I2C\_SDA line low) and continue with Step 8 of this procedure to perform a read from the same address.

#### **SWITCHING/UPDATE DELAY**

There is a delay between when a user writes to the configuration registers of the AD8197B and when that state change takes physical effect. This update delay occurs regardless of whether the user programs the AD8197B via the serial or the parallel control interface. When using the serial control interface, the update delay begins at the falling edge of I2C\_SCL for the last data bit transferred, as shown in Figure 29. When using the parallel control interface, the update delay begins at the transition edge of the relevant parallel interface pin. This update delay is register-specific and the times are specified in Table 1.

During a delay window, new values can be written to the configuration registers, but the AD8197B does not physically update until the end of that register's delay window. Writing new values during the delay window does not reset the window; new values supersede the previously written values. At the end of the delay window, the AD8197B physically assumes the state indicated by the last set of values written to the configuration registers. If the configuration registers are written after the delay window ends, the AD8197B immediately updates and a new delay window begins.

### PARALLEL CONTROL INTERFACE

The AD8197B can be partially controlled through the parallel interface using the PP\_EN, PP\_CH[1:0], PP\_EQ, PP\_PRE[1:0], PP\_OTO, and PP\_OCL pins. Logic levels for the parallel interface pins are set in accordance with the specifications listed in Table 1. Setting these pins updates the parallel control interface registers, as listed in Table 18. Following a reset, the AD8197B can be controlled through the parallel control interface until the first serial control event occurs. As soon as any serial control event occurs, the serial programming values override any prior parallel programming values, and the parallel control interface is disabled until the part is subsequently reset. The default serial programming values correspond to the state of the serial interface configuration registers, as listed in Table 5.

Note that after changing the status of the channel selection (PP\_CH[1:0]), it is necessary to assert a low logic level to RESET to ensure that the channel select status is properly updated.

Note also that the input termination resistor switches can be controlled only via serial programming. Therefore, as most systems require controlling these resistors, serial control is required and parallel control is of little use. However, the parallel control pins determine the AD8197B status between the time of the assertion of reset and the first serial programming event.

### SERIAL INTERFACE CONFIGURATION REGISTERS

The serial interface configuration registers can be read and written using the I²C serial control interface, Pin I2C\_SDA, and Pin I2C\_SCL. The least significant bits of the AD8197B I²C part address are set by tying the Pin I2C\_ADDR2, Pin I2C\_ADDR1, and Pin I2C\_ADDR0 to 3.3 V (Logic 1) or 0 V (Logic 0). As soon as the serial control interface is used, the parallel control interface is disabled until the AD8197B is reset as described in the Serial Control Interface section.

Table 5. Serial (I<sup>2</sup>C) Interface Register Map

| Name                             | Bit 7                                           | Bit 6                             | Bit 5       | Bit 4          | Bit 3           | Bit 2                           | Bit 1                                         | Bit 0                                                    | Addr. | Default  |

|----------------------------------|-------------------------------------------------|-----------------------------------|-------------|----------------|-----------------|---------------------------------|-----------------------------------------------|----------------------------------------------------------|-------|----------|

| High<br>Speed<br>Device<br>Modes |                                                 | High<br>speed<br>switch<br>enable |             |                |                 |                                 | High speed                                    | source select                                            | 0x00  | 0x40     |

|                                  |                                                 | HS_EN                             | 0           | 0              | 0               | 0                               | HS_CH[1]                                      | HS_CH[0]                                                 |       |          |

| Auxiliary<br>Device<br>Modes     |                                                 | Auxiliary<br>switch<br>enable     |             |                |                 |                                 |                                               | vitch source<br>lect                                     | 0x01  | 0x40     |

|                                  |                                                 | AUX_EN                            | 0           | 0              | 0               | 0                               | AUX_CH[1]                                     | AUX_CH[0]                                                |       |          |

| Receiver<br>Settings             |                                                 |                                   |             |                |                 |                                 |                                               | High speed<br>input<br>termination<br>resistor<br>select | 0x10  | 0x01     |

|                                  |                                                 |                                   |             |                |                 |                                 |                                               | RX_TS                                                    |       |          |

| Input                            |                                                 | 1                                 |             |                | 3: input termii | 1                               | 1                                             | 1                                                        | 0x11  | 0x00     |

| Term.<br>Resistor<br>Control 1   | RX_TO[7]                                        | RX_TO[6]                          | RX_TO[5]    | RX_TO[4]       | RX_TO[3]        | RX_TO[2]                        | RX_TO[1]                                      | RX_TO[0]                                                 |       |          |

| Input                            | Source C and Source D: input termination select |                                   |             |                |                 |                                 |                                               |                                                          |       |          |

| Term.<br>Resistor<br>Control 2   | RX_TO[15]                                       | RX_TO[14]                         | RX_TO[13]   | RX_TO[12]      | RX_TO[11]       | RX_TO[10]                       | RX_TO[9]                                      | RX_TO[8]                                                 |       |          |

| Receive                          |                                                 |                                   | Source A an | d Source B: ir | put equaliza    | tion level sele                 | ct                                            |                                                          | 0x13  | 0x00     |

| Equalizer 1                      | RX_EQ[7]                                        | RX_EQ[6]                          | RX_EQ[5]    | RX_EQ[4]       | RX_EQ[3]        | RX_EQ[2]                        | RX_EQ[1]                                      | RX_EQ[0]                                                 |       |          |

| Receive                          |                                                 |                                   | Source C an | d Source D: ir | nput equaliza   | tion level sele                 | ct                                            |                                                          | 0x14  | 0x00     |

| Equalizer 2                      | RX_EQ[15]                                       | RX_EQ[14]                         | RX_EQ[13]   | RX_EQ[12]      | RX_EQ[11]       | RX_EQ[10]                       | RX_EQ[9]                                      | RX_EQ[8]                                                 |       |          |

| Transmitter<br>Settings          |                                                 |                                   |             |                | pre-empl<br>sel | ed output<br>hasis level<br>ect | High speed<br>output<br>termination<br>select | High speed<br>output<br>current<br>level select          | 0x20  | 0x03     |

|                                  |                                                 |                                   |             |                | TX_PE[1]        | TX_PE[0]                        | TX_PTO                                        | TX_OCL                                                   |       | <u> </u> |

#### **HIGH SPEED DEVICE MODES REGISTER**

HS\_EN: High Speed (TMDS) Channels Enable Bit

Table 6. HS\_EN Description

| HS_EN | Description                                     |

|-------|-------------------------------------------------|

| 0     | High speed channels off, low power/standby mode |

| 1     | High speed channels on                          |

#### HS\_CH[1:0]: High Speed (TMDS) Switch Source Select Bus

Table 7. HS\_CH Mapping

|            |        | · ·                                    |

|------------|--------|----------------------------------------|

| HS_CH[1:0] | O[3:0] | Description                            |

| 00         | A[3:0] | High Speed Source A switched to output |

| 01         | B[3:0] | High Speed Source B switched to output |

| 10         | C[3:0] | High Speed Source C switched to output |

| 11         | D[3:0] | High Speed Source D switched to output |

#### **AUXILIARY DEVICE MODES REGISTER**

AUX\_EN: Auxiliary (Low Speed) Switch Enable Bit

Table 8. AUX\_EN Description

| AUX_EN | Description          |  |  |  |

|--------|----------------------|--|--|--|

| 0      | Auxiliary switch off |  |  |  |

| 1      | Auxiliary switch on  |  |  |  |

## AUX\_CH[1:0]: Auxiliary (Low Speed) Switch Source Select Bus

Table 9. AUX\_CH Mapping

| AUX_CH[ | 3:0] AUX_COM[3: | 0] Description                        |

|---------|-----------------|---------------------------------------|

| 00      | AUX_A[3:0]      | Auxiliary Source A switched to output |

| 01      | AUX_B[3:0]      | Auxiliary Source B switched to output |

| 10      | AUX_C[3:0]      | Auxiliary Source C switched to output |

| 11      | AUX_D[3:0]      | Auxiliary Source D switched to output |

#### **RECEIVER SETTINGS REGISTER**

## RX\_TS: High Speed (TMDS) Channels Input Termination On/Off Select Bit

Table 10. RX\_TS Description

| RX_TS | Description                                                                                                                   |

|-------|-------------------------------------------------------------------------------------------------------------------------------|

| 0     | All input terminations off (switches open)                                                                                    |

| 1     | Input termination resistor switch is controlled by RX_TO[x] control bits from Input Term. Resistor Control Registers 1 and 2. |

## INPUT TERMINATION SELECT REGISTER 1 AND REGISTER 2

## RX\_TO[X]: High Speed (TMDS) Input Channel X Termination Select Bit

Table 11. RX\_TO[X] Description

| RX_TO[X] | Description                                       |

|----------|---------------------------------------------------|

| 0        | Input termination for TMDS Channel X disconnected |

| 1        | Input termination for TMDS Channel X connected    |

Table 12. RX\_TO[X] Mapping

| Tuble 12. Kit_1 O[K] Niupping |                                  |  |  |  |

|-------------------------------|----------------------------------|--|--|--|

| RX_TO[X]                      | Corresponding Input TMDS Channel |  |  |  |

| Bit 0                         | B0                               |  |  |  |

| Bit 1                         | B1                               |  |  |  |

| Bit 2                         | B2                               |  |  |  |

| Bit 3                         | B3                               |  |  |  |

| Bit 4                         | A0                               |  |  |  |

| Bit 5                         | A1                               |  |  |  |

| Bit 6                         | A2                               |  |  |  |

| Bit 7                         | A3                               |  |  |  |

| Bit 8                         | C3                               |  |  |  |

| Bit 9                         | C2                               |  |  |  |

| Bit 10                        | C1                               |  |  |  |

| Bit 11                        | CO                               |  |  |  |

| Bit 12                        | D3                               |  |  |  |

| Bit 13                        | D2                               |  |  |  |

| Bit 14                        | D1                               |  |  |  |

| Bit 15                        | D0                               |  |  |  |

#### **RECEIVE EQUALIZER REGISTER 1 AND REGISTER 2**

RX\_EQ[X]: High Speed (TMDS) Input X Equalization Level Select Bit

Table 13. RX EQ[X] Description

| RX_EQ[X] | Description               |  |  |  |

|----------|---------------------------|--|--|--|

| 0        | Low equalization (6 dB)   |  |  |  |

| 1        | High equalization (12 dB) |  |  |  |

Table 14. RX EQ[X] Mapping

| Table 14. KA_LQ[A] Mapping |                                  |  |  |  |

|----------------------------|----------------------------------|--|--|--|

| $RX_EQ[X]$                 | Corresponding Input TMDS Channel |  |  |  |

| Bit 0                      | B0                               |  |  |  |

| Bit 1                      | B1                               |  |  |  |

| Bit 2                      | B2                               |  |  |  |

| Bit 3                      | B3                               |  |  |  |

| Bit 4                      | A0                               |  |  |  |

| Bit 5                      | A1                               |  |  |  |

| Bit 6                      | A2                               |  |  |  |

| Bit 7                      | A3                               |  |  |  |

| Bit 8                      | C3                               |  |  |  |

| Bit 9                      | C2                               |  |  |  |

| Bit 10                     | C1                               |  |  |  |

| Bit 11                     | C0                               |  |  |  |

| Bit 12                     | D3                               |  |  |  |

| Bit 13                     | D2                               |  |  |  |

| Bit 14                     | D1                               |  |  |  |

| Bit 15                     | D0                               |  |  |  |

#### TRANSMITTER SETTINGS REGISTER

TX\_PE[1:0]: High Speed (TMDS) Output Pre-Emphasis Level Select Bus (For All TMDS Channels)

Table 15. TX\_PE[1:0] Description

| · · · ·    |                            |  |  |

|------------|----------------------------|--|--|

| TX_PE[1:0] | Description                |  |  |

| 00         | No pre-emphasis (0 dB)     |  |  |

| 01         | Low pre-emphasis (2 dB)    |  |  |

| 10         | Medium pre-emphasis (4 dB) |  |  |

| 11         | High pre-emphasis (6 dB)   |  |  |

## TX\_PTO: High Speed (TMDS) Output Termination On/Off Select Bit (For All Channels)

Table 16. TX\_PTO Description

| TX_PTO | Description            |

|--------|------------------------|

| 0      | Output termination off |

| 1      | Output termination on  |

## TX\_OCL: High Speed (TMDS) Output Current Level Select Bit (For All Channels)

Table 17. TX\_OCL Description

| TX_OCL | Description                 |

|--------|-----------------------------|

| 0      | Output current set to 10 mA |

| 1      | Output current set to 20 mA |

### PARALLEL INTERFACE CONFIGURATION REGISTERS

The parallel interface configuration registers can be directly set using the PP\_EN, PP\_CH[1:0], PP\_EQ, PP\_PRE[1:0], PP\_OTO, and PP\_OCL pins. This interface is accessible only after the part is reset and before any registers are accessed using the serial control interface. Because most systems use serial control for the input termination resistors, the parallel control interface is limited to controlling the AD8197B status after reset and before serial logic control. The state of each pin is set by tying it to 3.3 V (Logic 1) or 0 V (Logic 0).

Table 18. Parallel Interface Register Map

| Name                                                                                                   | Bit 7                                                 | Bit 6                                                 | Bit 5      | Bit 4                    | Bit 3          | Bit 2                   | Bit 1                            | Bit 0                                                                                 |  |

|--------------------------------------------------------------------------------------------------------|-------------------------------------------------------|-------------------------------------------------------|------------|--------------------------|----------------|-------------------------|----------------------------------|---------------------------------------------------------------------------------------|--|

| High Speed Device<br>Modes                                                                             |                                                       | High speed switch enable                              |            |                          |                |                         | High speed source select         |                                                                                       |  |

|                                                                                                        |                                                       | PP_EN                                                 | 0          | 0                        | 0              | 0                       | PP_CH[1]                         | PP_CH[0]                                                                              |  |

| Auxiliary Device<br>Modes                                                                              |                                                       | Auxiliary switch enable                               |            |                          |                |                         | Auxiliary switch source select   |                                                                                       |  |

|                                                                                                        |                                                       | 1                                                     | 0          | 0                        | 0              | 0                       | PP_CH[1]                         | PP_CH[0]                                                                              |  |

| Receiver Settings                                                                                      |                                                       |                                                       |            |                          |                |                         |                                  | Input term.<br>select<br>(terminations<br>always open in<br>parallel control<br>mode) |  |

|                                                                                                        |                                                       |                                                       | <u> </u>   |                          |                |                         |                                  | 1                                                                                     |  |

| Input Termination                                                                                      |                                                       | Source A and So                                       | urce B inp | ut termin                | ation select ( | No parallel coi         | ntrol termination, alway         | ys open)                                                                              |  |

| Resistor Control.1                                                                                     | 0                                                     | 0                                                     | 0          | 0                        | 0              | 0                       | 0                                | 0                                                                                     |  |

| Input Termination Source C and Source D input termination select (No parallel control termination, alw |                                                       |                                                       |            | ntrol termination, alway | ys open)       |                         |                                  |                                                                                       |  |

| Resistor Control 2                                                                                     | 0                                                     | 0                                                     | 0          | 0                        | 0              | 0                       | 0                                | 0                                                                                     |  |

| Receive Equalizer 1                                                                                    | Source A and Source B input equalization level select |                                                       |            |                          |                |                         |                                  |                                                                                       |  |

|                                                                                                        | PP_EQ                                                 | PP_EQ                                                 | PP_EQ      | PP_EQ                    | PP_EQ          | PP_EQ                   | PP_EQ                            | PP_EQ                                                                                 |  |

| Receive Equalizer 2                                                                                    |                                                       | Source C and Source D input equalization level select |            |                          |                |                         |                                  |                                                                                       |  |

|                                                                                                        | PP_EQ                                                 | PP_EQ                                                 | PP_EQ      | PP_EQ                    | PP_EQ          | PP_EQ                   | PP_EQ                            | PP_EQ                                                                                 |  |

| Transmitter Settings                                                                                   |                                                       |                                                       |            |                          |                | re-emphasis<br>I select | Output termination on/off select | Output current level select                                                           |  |

|                                                                                                        |                                                       |                                                       |            |                          | PP_PE[1]       | PP_PE[0]                | PP_OTO                           | PP_OCL                                                                                |  |

#### **HIGH SPEED DEVICE MODES REGISTER**

PP\_EN: High Speed (TMDS) Channels Enable Bit

Table 19. PP\_EN Description

| PP_EN | Description                                     |

|-------|-------------------------------------------------|

| 0     | High speed channels off, low power/standby mode |

| 1     | High speed channels on                          |

#### PP\_CH[1:0]: High Speed (TMDS) Switch Source Select Bus

#### Table 20. PP\_CH Mapping

| PP_CH[1:0] | O[3:0] | Description                            |

|------------|--------|----------------------------------------|

| 00         | A[3:0] | High Speed Source A switched to output |

| 01         | B[3:0] | High Speed Source B switched to output |

| 10         | C[3:0] | High Speed Source C switched to output |

| 11         | D[3:0] | High Speed Source D switched to output |

Note that after changing the status of the channel selection (PP\_CH[1:0]0), it is necessary to assert a low logic level to RESET to ensure that the channel select status is properly updated.

#### **AUXILIARY DEVICE MODES REGISTER**

#### PP\_CH[1:0]: Auxiliary Switch Source Select Bus

Table 21. PP\_CH Mapping

| PP_CH[1:0] | AUX_COM[3:0] | Description                           |

|------------|--------------|---------------------------------------|

| 00         | AUX_A[3:0]   | Auxiliary Source A switched to output |

| 01         | AUX_B[3:0]   | Auxiliary Source B switched to output |

| 10         | AUX_C[3:0]   | Auxiliary Source C switched to output |

| 11         | AUX_D[3:0]   | Auxiliary Source D switched to output |

## INPUT TERMINATION RESISTOR CONTROL REGISTER 1 AND REGISTER 2

High speed input (TMDS) channels input terminations are off when using the parallel interface. This can be changed only via serial programming.

#### **RECEIVE EQUALIZER REGISTER 1 AND REGISTER 2**

## PP\_EQ: High Speed (TMDS) Inputs Equalization Level Select Bit (For All TMDS Input Channels)

The input equalization cannot be set individually (per channel) when using the parallel interface; one equalization setting affects all input channels.

#### Table 22. PP\_EQ Description

| PP_EQ | Description               |  |

|-------|---------------------------|--|

| 0     | Low equalization (6 dB)   |  |

| 1     | High equalization (12 dB) |  |

#### TRANSMITTER SETTINGS REGISTER

#### PP\_PE[1:0]: High Speed (TMDS) Output Pre-Emphasis Level Select Bus (For All TMDS Channels)

Table 23. PP PE[1:0] Description

| PP_PE[1:0] | Description                |

|------------|----------------------------|

| 00         | No pre-emphasis (0 dB)     |

| 01         | Low pre-emphasis (2 dB)    |

| 10         | Medium pre-emphasis (4 dB) |

| 11         | High pre-emphasis (6 dB)   |

## PP\_OTO: High Speed (TMDS) Output Termination On/Off Select Bit (For All TMDS Channels)

Table 24. PP\_OTO Description

| PP_OTO | Description            |  |

|--------|------------------------|--|

| 0      | Output termination off |  |

| 1      | Output termination on  |  |

## PP\_OCL: High Speed (TMDS) Output Current Level Select Bit (For All TMDS Channels)

Table 25. TX\_OCL Description

| PP_OCL | Description                 |  |

|--------|-----------------------------|--|

| 0      | Output current set to 10 mA |  |

| 1      | Output current set to 20 mA |  |

### APPLICATION INFORMATION

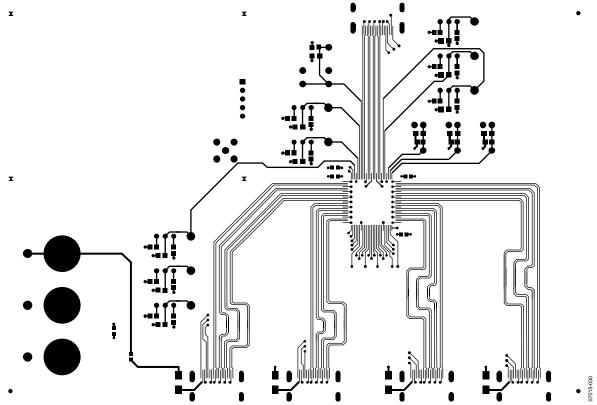

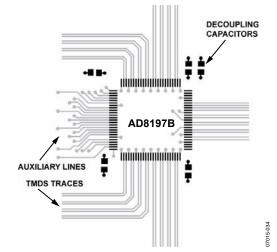

Figure 31. Layout of the TMDS Traces on the AD8197B Evaluation Board (Only Top Signal Routing Layer is Shown)

The AD8197B is an HDMI/DVI switch, featuring equalized TMDS inputs and pre-emphasized TMDS outputs. It is intended for use as a 4:1 switch in systems with long cable runs on both the input and/or the output, and is fully HDMI 1.3 receive-compliant.

#### **PINOUT**

The AD8197B is designed to have an HDMI/DVI receiver pinout at its input and a transmitter pinout at its output. This makes the AD8197B ideal for use in AVR-type applications where a designer routes both the inputs and the outputs directly to HDMI/DVI connectors, as shown in Figure 31. When the AD8197B is used in receiver type applications, it is necessary to change the order of the output pins on the PCB to align with the on-board receiver.

One advantage of the AD8197B in an AVR-type application is that all of the high speed signals can be routed on one side (the topside) of the board, as shown in Figure 31. In addition to 12 dB of input equalization, the AD8197B provides up to 6 dB of output pre-emphasis that boosts the output TMDS signals and allows the AD8197B to precompensate when driving long PCB traces or output cables. The net effect of the input equalization and output pre-emphasis of the AD8197B is that the AD8197B can compensate for the signal degradation of both input and output cables; it acts to reopen a closed input data eye