# **Dual PLL Precision Synthesizer**

Data Sheet AD9578

#### **FEATURES**

Any output frequency precision synthesis

11.8 MHz to 919 MHz

Better than 0.1 ppb frequency resolution

Ultralow rms jitter (12 kHz to 20 MHz)

<300 fs rms using integer synthesis

<405 fs rms using fractional synthesis

Dual reference inputs support LVPECL, LVDS, 1.8 V LVCMOS,

or fundamental mode AT cut crystals from 22 MHz to

54 MHz or reference clocks from 20 MHz to 60 MHz

Numerical (NCO) frequency control

Dynamically pullable output frequency enables FPGAbased PLLs (HDL available)

Fast serial peripheral interface (SPI) bus write speeds up to 100 MHz

On-the-fly frequency changes

Dual PLL in compact 7 mm × 7 mm package

Replaces multiple large clock ICs, PLLs, fanout buffers, crystal oscillators (XOs), and voltage controlled crystal oscillators (VCXOs)

Mix and match output buffers

In-circuit programmable LVPECL/LVDS/HCSL/LVCMOS

Independent buffer (VDDOx) drives multiple technologies

Enhanced power supply noise rejection

#### **APPLICATIONS**

FPGA-based jitter attenuators and low jitter PLLs Precision disciplined clocks and clock synthesizers

Multirate clock synthesizers Optical: OTN/SDH/SONET

Broadcast video: 3G SDI, HD SDI, SDI

Networking and storage: Ethernet/SAS/Fibre Channel

Wireless infrastructure: OBSAI/CPRI

**Industrial: IEEE 1588**

Numerically controlled oscillators (NCOs)

#### GENERAL DESCRIPTION

The AD9578 is a programmable synthesizer intended for jitter attenuation and asynchronous clocking applications in high performance telecommunications, networking, data storage, serializer/deserializer (SERDES), and physical layer (PHY) applications. The device incorporates two low jitter PLLs that provide any frequency with precision better than 0.1 ppb, each with two separate output dividers, for a total of four programmable outputs, delivering maximum flexibility and jitter performance. Each output is independently programmable to provide frequencies of up to 919 MHz with <410 fs typical rms jitter (12 kHz to 20 MHz) utilizing compact, low cost fundamental mode crystals (XTALs) that enable a robust supply chain. Using integer frequency synthesis, the AD9578 is capable of achieving rms jitter as low as 290 fs.

The AD9578 is packaged with a factory programmed default power-on configuration. After power-on, all settings including output frequency are reconfigurable through a fast SPI.

The AD9578 architecture permits it to be used as a numerically controlled oscillator (NCO). This allows the user to dynamically change the frequency using the fast SPI bus. FPGAs and other devices can take advantage of this function to implement digital PLLs with configurable loop bandwidths for jitter attenuation applications, precision disciplined clocks that lock to tight stability references, or digitally controlled precision timing applications, such as network timing and IEEE 1588 applications. The SPI bus can operate up to 50 MHz, enabling fast FPGA loops while multiple devices share the same bus. The AD9578 can also be used in multirate precision applications, such as broadcast video or OTN. HDL FPGA code for digital PLL applications is available from Analog Devices, Inc.

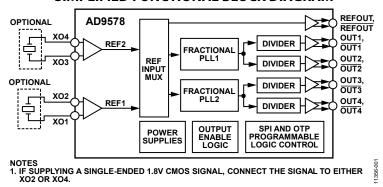

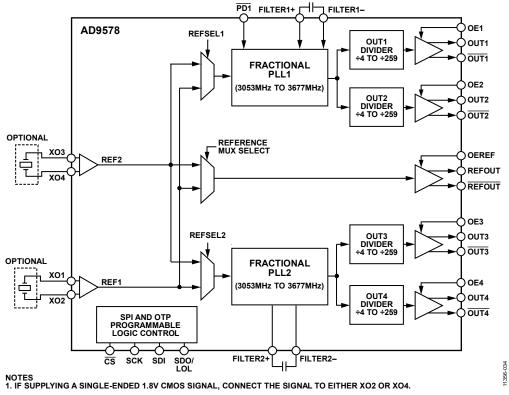

#### SIMPLIFIED FUNCTIONAL BLOCK DIAGRAM

Figure 1.

# **AD9578\* Product Page Quick Links**

Last Content Update: 10/26/2016

# Comparable Parts <a> □</a>

View a parametric search of comparable parts

### Evaluation Kits <a> □</a>

• AD9578 Evaluation Board

# Documentation <a>□</a>

#### **Data Sheet**

• AD9578: Dual PLL Precision Synthesizer Data Sheet

# Design Resources -

- AD9578 Material Declaration

- · PCN-PDN Information

- Quality And Reliability

- · Symbols and Footprints

### Discussions <a>□</a>

View all AD9578 EngineerZone Discussions

# Sample and Buy 🖳

Visit the product page to see pricing options

# Technical Support <a> Image: Page 1</a> <a> Image: Page 2</a> <a> Image: Page 3</a> <a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

# **TABLE OF CONTENTS**

| Features                                                   | Overview                                                    |

|------------------------------------------------------------|-------------------------------------------------------------|

| Applications1                                              | Crystal Oscillator Gain25                                   |

| General Description1                                       | Crystal Load Capacitors25                                   |

| Simplified Functional Block Diagram1                       | PLLs                                                        |

| Revision History 3                                         | Overview                                                    |

| Specifications4                                            | PLL Modes of Operation                                      |

| Supply Voltage and Current (2.5 V Operation)4              | VCO27                                                       |

| Supply Voltage and Current (3.3 V Operation)4              | Charge Pump                                                 |

| Power Dissipation4                                         | Output Dividers27                                           |

| Logic Inputs (CS, PD1, OEREF, OE1, OE2, OE3, OE4) 5        | Loss of Lock Indicator27                                    |

| Reference Inputs (XO1, XO2, XO3, XO4)5                     | Resets                                                      |

| Distribution Clock Outputs (Including REFOUT/REFOUT)6      | Example Values for 49.152 MHz crystal28                     |

| Serial Port9                                               | SPI Programming                                             |

| Digital PLL                                                | Overview                                                    |

| Digital Functions Timing10                                 | SPI Description29                                           |

| Jitter Generation Using 49.152 MHz Crystal 10              | OTP Programming                                             |

| Jitter Generation Using 25 MHz Square wave11               | Register Map32                                              |

| Absolute Maximum Ratings                                   | Register Map Bit Descriptions34                             |

| ESD Caution                                                | Chip and Manufacturer ID (Register 0, Address 0x00) 34      |

| Pin Configuration and Function Descriptions13              | Product ID, Chip ID, and User Programing Space (Register 1, |

| Typical Performance Characteristics                        | Address 0x01)                                               |

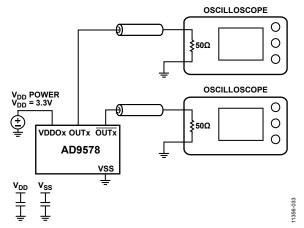

| Test Setup and Configuration Circuits                      | External Pin Readback and Override (Register 2, Address     |

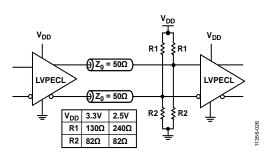

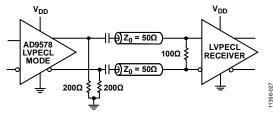

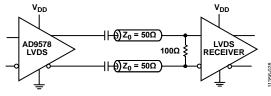

| Input/Output Termination Recommendations19                 | 0x02)                                                       |

| Getting Started20                                          | REFOUT/OUTPUT Divider Enable (Register 3, Address 0x03)     |

| Chip Power Monitor and Startup20                           | XTAL1 and Output Buffer Configuration (Register 4,          |

| Device Register Programming Using a Register Setup File 20 | Address 0x04)                                               |

| OTP Programming20                                          | Output Driver Configuration (Register 5, Address 0x05) 38   |

| Theory of Operation21                                      | PLL1 Configuration (Register 6, Address 0x06)38             |

| Overview21                                                 | PLL1 Configuration (Register 7, Address 0x07)39             |

| PLL and Output Driver Control22                            | PLL2 Configuration (Register 8, Address 0x08)40             |

| Overview                                                   | PLL2 Configuration (Register 9, Address 0x09)40             |

| PLL Enable/Disable22                                       | XTAL2 Configuration (Register 10, Address 0x0A) 42          |

| Output Driver Format23                                     | Reserved (Register 11, Address 0x0B)42                      |

| Output Configuration Example23                             | PLL1 K <sub>VCO</sub> Band (Register 12, Address 0x0C)42    |

| Reference Input24                                          | Reserved (Register 13, Address 0x0D)42                      |

| Overview24                                                 | PLL2 K <sub>VCO</sub> Band (Register 14, Address 0x0E)43    |

| Reference Input24                                          | PLL Lock Detect (Register 15, Address 0x0F)43               |

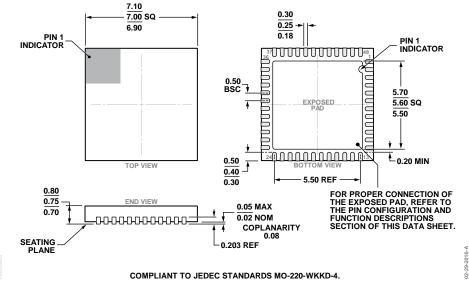

| Crystal Oscillator Amplifier Enable24                      | Outline Dimensions                                          |

| REFOUT/REFOUT Source Selection                             | Ordering Guide44                                            |

| Crystal Oscillator Inputs25                                |                                                             |

|                                                            |                                                             |

### **REVISION HISTORY**

| 10/2016—Rev. 0 to Rev. A                         |    |

|--------------------------------------------------|----|

| Changes to Figure 3                              | 13 |

| Changes to Table 29                              | 28 |

| Added Exposed Pad Notation to Outline Dimensions | 44 |

10/2014—Revision 0: Initial Version

### **SPECIFICATIONS**

### **SUPPLY VOLTAGE AND CURRENT (2.5 V OPERATION)**

$V_{\rm DD}$  = 2.5 V ± 5%,  $T_{\rm A}$  = -25°C to +85°C.

Table 1.

| Parameter      | Symbol          | Min   | Тур  | Max   | Unit | Test Conditions/Comments                          |

|----------------|-----------------|-------|------|-------|------|---------------------------------------------------|

| SUPPLY VOLTAGE | $V_{DD}$        | 2.375 | 2.50 | 2.625 | V    |                                                   |

| SUPPLY CURRENT | I <sub>DD</sub> | 229   | 247  | 265   | mA   | Using typical configuration in Table 3            |

|                |                 | 337   | 365  | 388   | mA   | Using all blocks running configuration in Table 3 |

### **SUPPLY VOLTAGE AND CURRENT (3.3 V OPERATION)**

$V_{DD}$  = 3.3 V  $\pm$  10%,  $T_A$  = -25°C to +85°C.

Table 2.

| Parameter      | Symbol            | Min  | Тур  | Max            | Unit | Test Conditions/Comments                                                                                                                           |

|----------------|-------------------|------|------|----------------|------|----------------------------------------------------------------------------------------------------------------------------------------------------|

| SUPPLY VOLTAGE | $V_{DD}$          | 2.97 | 3.30 | 3.63           | V    |                                                                                                                                                    |

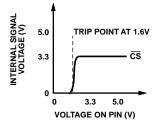

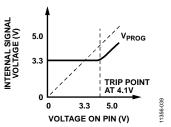

|                | V <sub>PROG</sub> | 5.25 | 5.5  | $V_{DD} + 2.5$ | V    | $\overline{\text{CS}}$ pin only; used only for one time programmable (OTP) programming; perform OTP programming only with $V_{DD} = 3.3 \text{ V}$ |

| SUPPLY CURRENT | I <sub>DD</sub>   |      | 252  | 268            | mA   | Using typical configuration in Table 3                                                                                                             |

|                |                   |      | 373  | 397            | mA   | Using all blocks running configuration in Table 3                                                                                                  |

#### **POWER DISSIPATION**

$V_{DD}$  = 2.5 V ± 5%,  $T_A$  = -25°C to +85°C. Maximum power is at  $V_{DD}$  = 2.625 V and is usually 11% higher than typical.

Table 3.

| Parameter                         | Min | Тур | Max  | Unit | Test Conditions/Comments                                                             |

|-----------------------------------|-----|-----|------|------|--------------------------------------------------------------------------------------|

| POWER DISSIPATION                 |     |     |      |      |                                                                                      |

| Typical Configuration             |     | 618 | 696  | mW   | XTAL: 25 MHz                                                                         |

|                                   |     |     |      |      | REFOUT driver: disabled                                                              |

|                                   |     |     |      |      | PLL1: one LVPECL driver at 644.53125 MHz                                             |

|                                   |     |     |      |      | PLL2: one single-ended LVCMOS driver (with 80 pF load) at 100 MHz                    |

| All Blocks Running                |     | 913 | 1018 | mW   | XTAL: 49.152 MHz XTAL on both XTAL inputs                                            |

|                                   |     |     |      |      | REFOUT driver: LVPECL mode, 49.152 MHz                                               |

|                                   |     |     |      |      | PLL1: two LVPECL drivers at 693.812 MHz                                              |

|                                   |     |     |      |      | PLL2: two LVPECL drivers at 693.812 MHz                                              |

| Full Power-Down                   |     | 67  | 75   | mW   | $\overline{PD1}$ pin grounded; Register 0x02 = 0x015555 to disable remainder of chip |

| Incremental Power Dissipation     |     |     |      |      | Starting with typical configuration; change in power due to the indicated operation  |

| Crystal Reference On/Off          |     | 25  |      | mW   |                                                                                      |

| PLL On/Off                        |     | 259 |      | mW   | PLL1 or PLL2 on/off, including output drivers or channel dividers                    |

| Output Distribution Driver On/Off |     |     |      |      |                                                                                      |

| HCSL (at 644.53 MHz)              |     | 75  |      | mW   | Each output of a differential pair has $50 \Omega$ to ground                         |

| LVDS (at 644.53 MHz)              |     | 43  |      | mW   | $100\Omega$ across differential pair                                                 |

| LVPECL (at 644.53 MHz)            |     | 107 |      | mW   | $50 \Omega$ to $V_{DD} - 2 V$                                                        |

| 3.3 V LVCMOS (at 25 MHz)          |     | 75  |      | mW   | A single 3.3 V LVCMOS output with an 80 pF load                                      |

# LOGIC INPUTS $(\overline{\text{CS}}, \overline{\text{PD1}}, \text{OEREF}, \text{OE1}, \text{OE2}, \text{OE3}, \text{OE4})$

Table 4.

| Parameter                                            | Min  | Тур | Max            | Unit | Test Conditions/Comments                                                                         |

|------------------------------------------------------|------|-----|----------------|------|--------------------------------------------------------------------------------------------------|

| LOGIC INPUTS (CS in OTP                              |      |     |                |      | Specifications apply to the CS pin while in OTP programming mode                                 |

| FUNCTION)                                            |      |     |                |      |                                                                                                  |

| Input Voltage (V <sub>PROG</sub> )                   | 5.25 | 5.5 | $V_{DD} + 2.5$ | V    | See $V_{PROG}$ definition in Table 1; OTP programming must be done with $V_{DD} = 3.3 \text{ V}$ |

| Input Current                                        |      | 20  | 25             | mA   | Current consumed during OTP programming                                                          |

| Time to OTP Program                                  | 800  |     |                | μs   | Time required per bit programmed                                                                 |

| LOGIC INPUTS (PD1,OEREF, OE1,                        |      |     |                |      | Numbers are valid for $V_{DD} = 2.5 \text{ V}$ and $3.3 \text{ V}$                               |

| OE2, OE3, OE4, $\overline{CS}$ )                     |      |     |                |      |                                                                                                  |

| Input Voltage                                        |      |     |                |      |                                                                                                  |

| High (V <sub>IH</sub> )                              | 2.2  |     |                | V    |                                                                                                  |

| Low (V <sub>IL</sub> )                               |      |     | 8.0            | V    |                                                                                                  |

| Input Current (I <sub>INH</sub> , I <sub>INL</sub> ) |      | 38  | 60             | μΑ   |                                                                                                  |

| Input Capacitance (C <sub>IN</sub> )                 |      | 3   |                | pF   |                                                                                                  |

# REFERENCE INPUTS (XO1, XO2, XO3, XO4)

Table 5.

| Parameter                                      | Min  | Тур | Max  | Unit   | Test Conditions/Comments                                                                                                                                                                                                           |

|------------------------------------------------|------|-----|------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| REFERENCE INPUT DRIVEN BY CRYSTAL RESONATOR    |      |     |      |        |                                                                                                                                                                                                                                    |

| Crystal Resonator<br>Frequency Range           | 20   |     | 60   | MHz    | Fundamental mode, AT cut crystal                                                                                                                                                                                                   |

| Crystal Motional Resistance                    |      |     | 100  | Ω      | Guaranteed by design                                                                                                                                                                                                               |

| REFERENCE INPUT DRIVEN BY A DIFFERENTIAL CLOCK |      |     |      |        | This input is a source follower and must be either dc-coupled 1.8 V LVCMOS on the XO2 or XO4 pin, or ac-coupled                                                                                                                    |

| Input Frequency Range                          | 20   |     | 60   | MHz    | Assumes ac-coupled LVDS (494 mV p-p across the differential pair)                                                                                                                                                                  |

| Input Slew Rate                                | 133  |     |      | V/µs   | Minimum limit imposed for jitter performance                                                                                                                                                                                       |

| Differential Input Voltage<br>Sensitivity      | 250  |     |      | mV p-p | Minimum voltage across pins required to ensure switching between logic states; the instantaneous voltage on either pin must not exceed the supply rails; can accommodate single-ended input by ac grounding of complementary input |

| REFERENCE INPUT DRIVEN BY A SINGLE-ENDED CLOCK |      |     |      |        | The XO2 pin (for PLL1) and XO4 pin (for PLL2) input accepts dc-<br>coupled 1.8 V LVCMOS                                                                                                                                            |

| Input Frequency Range                          | 20   |     | 60   | MHz    | DC-coupled                                                                                                                                                                                                                         |

| Input Slew Rate                                | 67   |     |      | V/µs   | Minimum limit imposed for jitter performance                                                                                                                                                                                       |

| Single-Ended Input (XO2,<br>XO4 Pins Only)     |      |     |      |        |                                                                                                                                                                                                                                    |

| Input Voltage                                  |      |     |      | V      |                                                                                                                                                                                                                                    |

| High (V <sub>IH</sub> )                        | 1.48 |     |      |        |                                                                                                                                                                                                                                    |

| Low (V <sub>IL</sub> )                         |      |     | 0.98 | V      |                                                                                                                                                                                                                                    |

# DISTRIBUTION CLOCK OUTPUTS (INCLUDING REFOUT/ $\overline{\text{REFOUT}}$ )

Table 6.

| Parameter                                  | Min  | Тур             | Max  | Unit | Test Conditions/Comments                                                                                             |

|--------------------------------------------|------|-----------------|------|------|----------------------------------------------------------------------------------------------------------------------|

| 3.3 V LVPECL MODE                          |      |                 |      |      | $V_{DD} = 3.3V$ ; 50 $\Omega$ to $V_{DD} - 2V$ termination at output pins                                            |

| Output Frequency                           | 11.8 |                 | 919  | MHz  | REFOUT/REFOUT limited to 60 MHz                                                                                      |

| Rise Time (20% to 80%)                     |      | 130             | 183  | ps   |                                                                                                                      |

| Fall Time (80% to 20%)                     |      | 142             | 203  | ps   |                                                                                                                      |

| Duty Cycle, OUTPUT1 and OUTPUT4            |      |                 |      | '    |                                                                                                                      |

| 111.8 ≤ f <sub>out</sub> ≤ 357 MHz         | 50   | 52              | 54   | %    | Output divider settings other than 4.5                                                                               |

| $357 < f_{OUT} \le 919 \text{ MHz}$        | 43   | 47              | 51   | %    | Output divider settings other than 4.5                                                                               |

| Output Divider = 4.5                       | 46   | 50              | 54   | %    | Measured at 765 MHz                                                                                                  |

| Duty Cycle, OUTPUT2 and OUTPUT3            |      |                 |      |      |                                                                                                                      |

| 111.8 ≤ fouт ≤ 357 MHz                     | 49   | 51              | 53   | %    | Output divider settings other than 4.5                                                                               |

| 357 < f <sub>OUT</sub> ≤ 919 MHz           | 45   | 49              | 51   | %    | Output divider settings other than 4.5                                                                               |

| Output Divider = 4.5                       | 51   | 57              | 63   | %    | Measured at 765 MHz                                                                                                  |

| Differential Output Voltage Swing          | 700  | 850             | 1000 | mV   | Voltage across pins at minimum output frequency; if                                                                  |

| Differential output voltage 5wing          | 700  | 030             | 1000 | 1111 | a differential probe is used, peak-to-peak voltage (V <sub>PP</sub> is 2× this value                                 |

| Common-Mode Output Voltage                 | 1.81 | 1.91            | 2.01 | V    |                                                                                                                      |

| 2.5 V LVPECL MODE                          |      |                 |      |      | $V_{DD} = 2.5 \text{ V}$ ; 50 $\Omega$ to $V_{DD} - 2 \text{ V}$ termination at output pins                          |

| Output Frequency                           | 11.8 |                 | 919  | MHz  | REFOUT/REFOUT limited to 60 MHz                                                                                      |

| Rise Time (20% to 80%)                     |      | 137             | 186  | ps   |                                                                                                                      |

| Fall Time (80% to 20%)                     |      | 148             | 209  | ps   |                                                                                                                      |

| Duty Cycle, OUTPUT1 and OUTPUT4            |      | 110             | 203  | ۲    |                                                                                                                      |

| $111.8 \le f_{OUT} \le 357 \text{ MHz}$    | 50   | 52              | 54   | %    | Output divider settings other than 4.5                                                                               |

| 357 < f <sub>OUT</sub> ≤ 919 MHz           | 49   | 51              | 54   | %    | Output divider settings other than 4.5                                                                               |

| Output Divider = 4.5                       | 46   | 50              | 54   | %    | Measured at 765 MHz                                                                                                  |

| Duty Cycle, OUTPUT2 and OUTPUT3            | 1 40 | 30              | J-1  | /0   | Wedsured at 705 Wil 12                                                                                               |

| 111.8 ≤ $f_{OUT}$ ≤ 357 MHz                | 43   | 48              | 51   | %    | Output divider settings other than 4.5                                                                               |

| 357 < f <sub>out</sub> ≤ 919 MHz           | 44   | 48              | 52   | %    | Output divider settings other than 4.5                                                                               |

| Output Divider = 4.5                       | 51   | <del>-1</del> 0 | 63   | %    | Measured at 765 MHz                                                                                                  |

| Differential Output Voltage Swing          | 700  | 850             | 1000 | mV   | Voltage across pins at minimum output frequency; if                                                                  |

| Common Mada Output Valtaga                 | 1.05 | 1 15            | 1 25 | V    | a differential probe is used, $V_{PP}$ is $2\times$ this value                                                       |

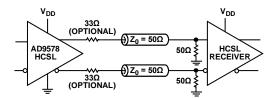

| Common-Mode Output Voltage 3.3 V HCSL MODE | 1.05 | 1.15            | 1.25 | V    | $50 \Omega$ to ground termination at output pins                                                                     |

|                                            | 11.8 |                 | 919  | MHz  | REFOUT/REFOUT limited to 60 MHz                                                                                      |

| Output Frequency                           | 11.0 | 100             |      |      | REPOOT/REPOOT IIITIILEG to 60 MINZ                                                                                   |

| Rise Time (20% to 80%)                     |      | 180             | 266  | ps   |                                                                                                                      |

| Fall Time (80% to 20%)                     |      | 186             | 286  | ps   |                                                                                                                      |

| Duty Cycle, OUTPUT1 and OUTPUT4            |      | =-              | - 4  | 0,   |                                                                                                                      |

| 111.8 ≤ f <sub>OUT</sub> ≤ 357 MHz         | 51   | 52              | 54   | %    | Output divider settings other than 4.5                                                                               |

| $357 < f_{OUT} \le 919 \text{ MHz}$        | 48   | 51              | 54   | %    | Output divider settings other than 4.5                                                                               |

| Output Divider = 4.5                       | 49   | 52              | 56   | %    | Measured at 765 MHz                                                                                                  |

| Duty Cycle, OUTPUT2 and OUTPUT3            |      |                 |      |      |                                                                                                                      |

| 111.8 ≤ f <sub>OUT</sub> ≤ 357 MHz         | 50   | 53              | 54   | %    | Output divider settings other than 4.5                                                                               |

| 357 < f <sub>OUT</sub> ≤ 919 MHz           | 48   | 51              | 53   | %    | Output divider settings other than 4.5                                                                               |

| Output Divider = 4.5                       | 53   | 59              | 67   | %    | Measured at 765 MHz                                                                                                  |

| Output High Voltage                        | 624  | 750             | 850  | mV   |                                                                                                                      |

| Output Low Voltage                         | -50  | 0               | +50  | mV   |                                                                                                                      |

| Output Voltage Swing (V <sub>SWING</sub> ) | 624  | 750             | 850  | mV   | Voltage across pins at minimum output frequency; when a differential probe is used, $V_{PP}$ is $2\times$ this value |

| Absolute Crossing Point (Vox)              | 295  | 360             | 400  | mV   |                                                                                                                      |

| Short-Circuit Output Current               |      | 14              | 17   | mA   |                                                                                                                      |

Rev. A | Page 6 of 44

| Parameter                                                           | Min  | Тур  | Max   | Unit | Test Conditions/Comments                                                                                           |

|---------------------------------------------------------------------|------|------|-------|------|--------------------------------------------------------------------------------------------------------------------|

| 2.5 V HCSL MODE                                                     |      |      |       |      | $50\Omega$ to ground termination at output pins                                                                    |

| Output Frequency                                                    | 11.8 |      | 919   | MHz  | REFOUT/REFOUT limited to 60 MHz                                                                                    |

| Rise Time (20% to 80%)                                              |      |      |       |      |                                                                                                                    |

| OUTPUT1, OUTPUT2, OUTPUT3                                           |      | 199  | 275   | ps   | Output divider settings other than 4.5                                                                             |

| OUTPUT4                                                             |      | 243  | 370   | ps   | Output divider settings other than 4.5                                                                             |

| Fall Time (80% to 20%)                                              |      |      |       | '    |                                                                                                                    |

| OUTPUT1, OUTPUT2, OUTPUT3                                           |      | 191  | 287   | ps   | Output divider settings other than 4.5                                                                             |

| OUTPUT4                                                             |      | 226  | 329   | ps   | Output divider settings other than 4.5                                                                             |

| Duty Cycle, OUTPUT1 and OUTPUT4                                     |      |      |       |      |                                                                                                                    |

| 111.8 ≤ $f_{OUT}$ ≤ 357 MHz                                         | 50   | 52   | 54    | %    | Output divider settings other than 4.5                                                                             |

| 357 < f <sub>OUT</sub> ≤ 919 MHz                                    | 47   | 50   | 53    | %    | Output divider settings other than 4.5                                                                             |

| Output Divider = 4.5                                                | 39   | 52   | 55    | %    | Measured at 765 MHz                                                                                                |

| Duty Cycle, OUTPUT2 and OUTPUT3                                     |      |      |       |      |                                                                                                                    |

| 111.8 ≤ $f_{OUT}$ ≤ 357 MHz                                         | 50   | 52   | 54    | %    | Output divider settings other than 4.5                                                                             |

| $357 < f_{OUT} \le 919 \text{ MHz}$                                 | 48   | 50   | 53    | %    | Output divider settings other than 4.5                                                                             |

| Output Divider = 4.5                                                | 45   | 59   | 65    | %    | Measured at 765 MHz                                                                                                |

| Output High Voltage                                                 | 624  | 750  | 850   | mV   |                                                                                                                    |

| Output Low Voltage                                                  | -50  | 0    | 50    | mV   |                                                                                                                    |

| Output Voltage Swing (V <sub>SWING</sub> )                          | 624  | 750  | 850   | mV   | Voltage across pins at minimum output frequency; if a differential probe is used, V <sub>PP</sub> is 2× this value |

| Absolute Crossing Point (Vox)                                       | 295  | 360  | 400   | mV   |                                                                                                                    |

| Short-Circuit Output Current                                        |      | 14   | 17    | mA   |                                                                                                                    |

| LVDS MODE ( $V_{DD} = 3.3 \text{ V} \text{ and } 2.5 \text{ V}$ )   |      |      |       |      | $100 \Omega$ termination across the output pair                                                                    |

| Output Frequency                                                    | 11.8 |      | 919   | MHz  | REFOUT/REFOUT limited to 54 MHz                                                                                    |

| Rise Time (20% to 80%)                                              |      | 173  | 215   | ps   |                                                                                                                    |

| Fall Time (80% to 20%)                                              |      | 177  | 223   | ps   |                                                                                                                    |

| OUTPUT1 and OUTPUT4 Duty Cycle                                      |      |      |       |      |                                                                                                                    |

| 111.8 ≤ f <sub>OUT</sub> ≤ 357 MHz                                  | 50   | 52   | 54    | %    | Output divider settings other than 4.5                                                                             |

| $357 < f_{OUT} \le 919 \text{ MHz}$                                 | 46   | 50   | 54    | %    | Output divider settings other than 4.5                                                                             |

| Output Divider = 4.5                                                | 49   | 52   | 55    | %    | Measured at 765 MHz                                                                                                |

| OUTPUT2 and OUTPUT3 Duty Cycle                                      |      |      |       |      |                                                                                                                    |

| 111.8 ≤ f <sub>OUT</sub> ≤ 357 MHz                                  | 50   | 52   | 54    | %    | Output divider settings other than 4.5                                                                             |

| $357 < f_{OUT} \le 919 \text{ MHz}$                                 | 46   | 50   | 53    | %    | Output divider settings other than 4.5                                                                             |

| Output Divider = 4.5                                                | 51   | 59   | 66    | %    | Measured at 765 MHz                                                                                                |

| Differential Output Voltage Swing                                   |      |      |       |      |                                                                                                                    |

| Balanced, V <sub>OD</sub>                                           | 247  |      | 454   | mV   | Voltage across pins at minimum output frequency; if a differential probe is used, V <sub>PP</sub> is 2× this value |

| Unbalanced, $\Delta V_{\text{OD}}$                                  |      |      | 50    | mV   | Absolute difference between voltage swing of true pin and complementary pin                                        |

| Offset Voltage                                                      |      |      |       |      |                                                                                                                    |

| Common Mode, Vos                                                    | 1.08 | 1.26 | 1.375 | V    |                                                                                                                    |

| Common-Mode Difference, ΔVos                                        |      |      | 50    | mV   | Voltage difference between pins at minimum output frequency                                                        |

| Short-Circuit Output Current                                        |      | 16   | 24    | mA   |                                                                                                                    |

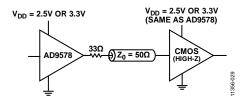

| LVCMOS MODE ( $V_{DD} = 3.3 \text{ V} \text{ and } 2.5 \text{ V}$ ) |      | ·    |       |      |                                                                                                                    |

| Output Frequency                                                    | 11.8 |      | 250   | MHz  | REFOUT limited to 60 MHz                                                                                           |

| Rise Time (20% to 80%)                                              |      |      |       |      | Capacitor load (C <sub>LOAD</sub> ) = 10 pF                                                                        |

| 330 Ω Pull-Down Resistor                                            |      | 1.3  | 1.9   | ns   |                                                                                                                    |

| 3.3 k $\Omega$ Pull-Down Resistor                                   |      | 1.2  | 1.7   | ns   |                                                                                                                    |

| Fall Time (20% to 80%)                                              |      |      |       |      | $C_{LOAD} = 10 \text{ pF}$                                                                                         |

| 330 $\Omega$ Pull-Down Resistor                                     |      | 1.3  | 2     | ns   |                                                                                                                    |

| 3.3 kΩ Pull-Down Resistor                                           |      | 1.5  | 2.4   | ns   |                                                                                                                    |

| Parameter                              | Min  | Тур  | Max  | Unit | Test Conditions/Comments                                                  |

|----------------------------------------|------|------|------|------|---------------------------------------------------------------------------|

| Duty Cycle (20% to 80%)                |      |      |      | ns   | C <sub>LOAD</sub> = 10 pF                                                 |

| 330 Ω Pull-Down Resistor               | 43   | 52   | 62   | %    |                                                                           |

| 3.3 kΩ Pull-Down Resistor              | 44   | 53   | 63   | %    |                                                                           |

| Output Voltage High (V <sub>OH</sub> ) |      |      |      |      | At minimum output frequency; outputs terminated $50 \Omega$ to $V_{DD}/2$ |

| $V_{DD} = 3.3 V$                       | 3.0  | 3.1  | 3.35 | V    |                                                                           |

| $V_{DD} = 2.5 \text{ V}$               | 1.9  | 2.0  | 2.1  | V    |                                                                           |

| Output Voltage Low (Vol)               |      |      |      |      | At minimum output frequency; outputs terminated $50\Omega$ to $V_{DD}/2$  |

| $V_{DD} = 3.3 \text{ V}$               | 0.22 | 0.32 | 0.42 | V    |                                                                           |

| $V_{DD} = 2.5 V$                       | 0.2  | 0.3  | 0.4  | V    |                                                                           |

| OUTPUT TIMING SKEW                     |      |      |      |      | OUTPUT2 lags OUTPUT1; OUTPUT3 lags OUTPUT4                                |

| LVPECL                                 |      |      |      |      |                                                                           |

| Between OUTPUT1 and OUTPUT2 Drivers    |      | 90   |      | ps   | LVPECL mode on both drivers; rising edge only; any divide value           |

| Between OUTPUT3 and OUTPUT4 Drivers    |      | 102  |      | ps   | LVPECL mode on both drivers; rising edge only; any divide value           |

| LVDS                                   |      |      |      |      | ,                                                                         |

| Between OUTPUT1 and OUTPUT2 Drivers    |      | 94   |      | ps   | LVDS mode on both drivers; rising edge only; any divide value             |

| Between OUTPUT3 and OUTPUT4 Drivers    |      | 100  |      | ps   | LVDS mode on both drivers; rising edge only; any divide value             |

| HCSL                                   |      |      |      |      | ,                                                                         |

| Between OUTPUT1 and OUTPUT2 Drivers    |      | 48   |      | ps   | HCSL mode on both drivers; rising edge only; any divide value             |

| Between OUTPUT3 and OUTPUT4 Drivers    |      | 59   |      | ps   | HCSL mode on both drivers; rising edge only; any divide value             |

| LVCMOS                                 |      |      |      |      |                                                                           |

| Between OUTPUT1 and OUTPUT2 Drivers    |      | 64   |      | ps   | LVCMOS mode on both drivers; rising edge only; any divide value           |

| Between OUTPUT3 and OUTPUT4 Drivers    |      | 59   |      | ps   | LVCMOS mode on both drivers; rising edge only; any divide value           |

### **SERIAL PORT**

Table 7.

| Parameter                           | Min                   | Тур | Max | Unit | Test Conditions/Comments                                                                                    |

|-------------------------------------|-----------------------|-----|-----|------|-------------------------------------------------------------------------------------------------------------|

| <u>CS</u>                           |                       |     |     |      | See Table 4 for using CS while in OTP programming mode                                                      |

| Input Voltage                       |                       |     |     |      |                                                                                                             |

| Logic 1                             | 2.2                   |     |     | V    |                                                                                                             |

| Logic 0                             |                       |     | 1.2 | V    |                                                                                                             |

| Input Current                       |                       | 44  |     | μΑ   |                                                                                                             |

| Logic 1                             |                       |     |     |      |                                                                                                             |

| Logic 0                             |                       | 88  |     | μΑ   |                                                                                                             |

| Input Capacitance                   |                       | 2   |     | рF   |                                                                                                             |

| SCK                                 |                       |     |     |      | Internal 30 kΩ pull-down resistor                                                                           |

| Input Voltage                       |                       |     |     |      | ·                                                                                                           |

| Logic 1                             | 2.2                   |     |     | V    |                                                                                                             |

| Logic 0                             |                       | 0.8 | 1.2 | V    |                                                                                                             |

| Input Current                       |                       |     |     |      |                                                                                                             |

| Logic 1                             |                       | 200 |     | μΑ   |                                                                                                             |

| Logic 0                             |                       | 1   |     | μA   |                                                                                                             |

| Input Capacitance                   |                       | 2   |     | pF   |                                                                                                             |

| SDI                                 |                       |     |     |      |                                                                                                             |

| Input Voltage                       |                       |     |     |      |                                                                                                             |

| Logic 1                             | 2.2                   |     |     | V    |                                                                                                             |

| Logic 0                             |                       |     | 1.2 | V    |                                                                                                             |

| Input Current                       |                       |     |     |      |                                                                                                             |

| Logic 1                             |                       | 1   |     | μΑ   |                                                                                                             |

| Logic 0                             |                       | 1   |     | μA   |                                                                                                             |

| Input Capacitance                   |                       | 2   |     | pF   |                                                                                                             |

| SDO/LOL                             |                       |     |     |      |                                                                                                             |

| Output Logic 1 Voltage              | V <sub>DD</sub> – 0.6 |     |     | V    | 1 mA load current                                                                                           |

| Output Logic 0 Voltage              |                       |     | 0.4 | V    | 1 mA load current                                                                                           |

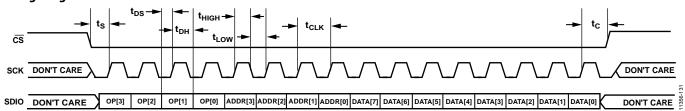

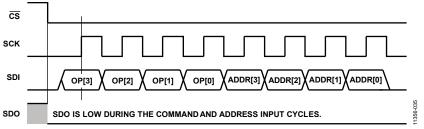

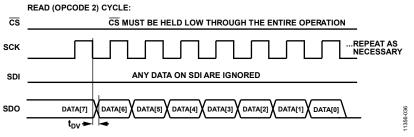

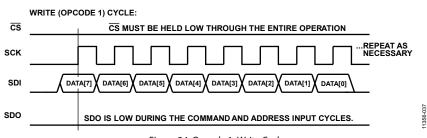

| TIMING                              |                       |     |     |      | See Figure 2                                                                                                |

| SCK                                 |                       |     |     |      |                                                                                                             |

| Clock Rate, 1/t <sub>CLK</sub>      |                       |     | 50  | MHz  | SDO/LOL pin maximum speed may be limited by excess capacitance on the receiver connected to the SDO/LOL pin |

| Write Only                          |                       |     | 100 | MHz  | ,                                                                                                           |

| Pulse Width High, t <sub>HIGH</sub> | 2                     |     | -   | ns   |                                                                                                             |

| Pulse Width Low, t <sub>Low</sub>   | 2                     |     |     | ns   |                                                                                                             |

| SDI to SCK Setup, t <sub>DS</sub>   | 1.5                   |     |     | ns   |                                                                                                             |

| SCK to SDI Hold, t <sub>DH</sub>    | 2                     |     |     | ns   |                                                                                                             |

| SCK to Valid SDO, t <sub>DV</sub>   |                       |     | 8   | ns   | SDO function of SDO/LOL pin (see Figure 33)                                                                 |

| CS to SCK Setup, ts                 | 65                    |     |     | ns   | CS is normally held low during a complete SPI transaction                                                   |

| CS to SCK Hold, tc                  | 0                     |     |     | ns   | ,                                                                                                           |

| 22 10 2011 1010/10                  |                       |     |     | 1    |                                                                                                             |

Figure 2. Serial Port Timing Diagram

#### **DIGITAL PLL**

Table 8.

| Parameter           | Min | Тур | Max | Unit | Test Conditions/Comments |

|---------------------|-----|-----|-----|------|--------------------------|

| FREQUENCY STEP SIZE | 0.1 |     |     | ppb  |                          |

### **DIGITAL FUNCTIONS TIMING**

Table 9.

| Parameter                     | Min | Тур | Max | Unit | it Test Conditions/Comments                                        |  |  |

|-------------------------------|-----|-----|-----|------|--------------------------------------------------------------------|--|--|

| OTP PROGRAMMING TIME, PER BIT | 0.8 | 1   | 2   | ms   | See Table 4 for using CS while in OTP programming mode (the AD9578 |  |  |

|                               |     |     |     |      | has 444 bits; therefore, the total programming time is <1 sec)     |  |  |

| POWER-ON RESET TIME           | 4   |     |     | ms   | Do not access serial port during power-on reset.                   |  |  |

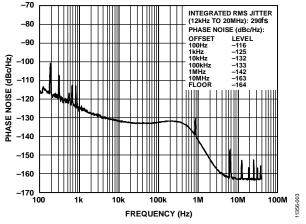

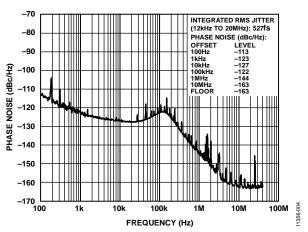

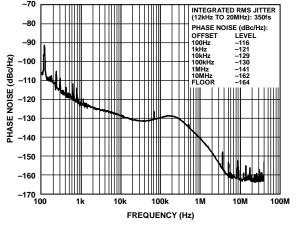

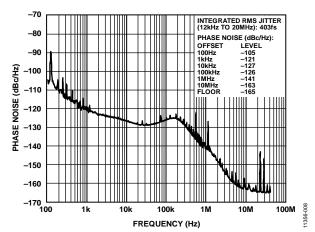

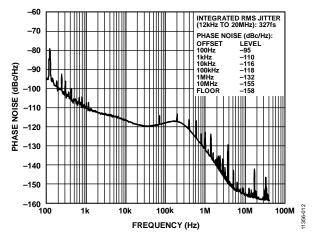

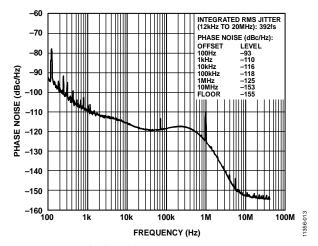

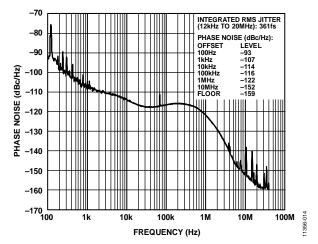

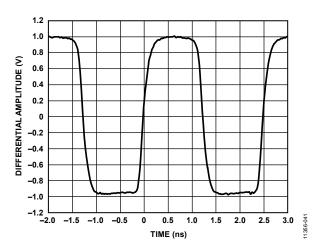

#### **JITTER GENERATION USING 49.152 MHZ CRYSTAL**

Both PLLs are generating the same output frequency and use a 49.152 MHz crystal for the input reference. The loop bandwidth is set to the default value of 300 kHz. Where multiple driver types are listed, there is no significant difference between driver types.

Table 10.

| Parameter                         | Min Typ | Max | Unit   | Test Conditions/Comments                               |

|-----------------------------------|---------|-----|--------|--------------------------------------------------------|

| JITTER GENERATION                 |         |     |        | Fractional mode on, f <sub>REF</sub> = 49.152 MHz XTAL |

| LVPECL, HCSL, LVDS Driver         |         |     |        |                                                        |

| $f_{OUT} = 622.08 \text{ MHz}$    |         |     |        |                                                        |

| Bandwidth: 12 kHz to 20 MHz       | 320     |     | fs rms |                                                        |

| Bandwidth: 20 kHz to 80 MHz       | 370     |     | fs rms |                                                        |

| $f_{OUT} = 693.48 \text{ MHz}$    |         |     |        |                                                        |

| Bandwidth: 12 kHz to 20 MHz       | 403     |     | fs rms |                                                        |

| Bandwidth: 20 kHz to 80 MHz       | 408     |     | fs rms |                                                        |

| $f_{OUT} = 174.703 \text{ MHz}$   |         |     |        |                                                        |

| Bandwidth: 12 kHz to 20 MHz       | 403     |     | fs rms |                                                        |

| Bandwidth: 20 kHz to 80 MHz       | 410     |     | fs rms |                                                        |

| $f_{OUT} = 161.1328 \text{ MHz}$  |         |     |        |                                                        |

| Bandwidth: 12 kHz to 20 MHz       | 361     |     | fs rms |                                                        |

| Bandwidth: 20 kHz to 80 MHz       | 363     |     | fs rms |                                                        |

| LVPECL, HCSL, LVDS, LVCMOS Driver |         |     |        |                                                        |

| f <sub>оит</sub> = 156.25 MHz     |         |     |        |                                                        |

| Bandwidth: 12 kHz to 20 MHz       | 350     |     | fs rms |                                                        |

| Bandwidth: 1.875 MHz to 20 MHz    | 77      |     | fs rms |                                                        |

| Bandwidth: 20 kHz to 80 MHz       | 352     |     | fs rms |                                                        |

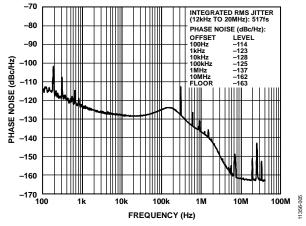

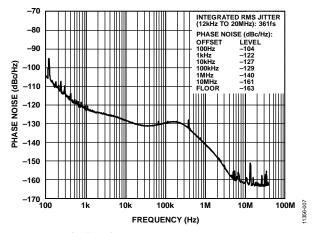

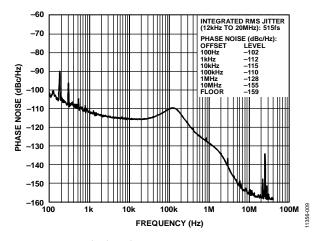

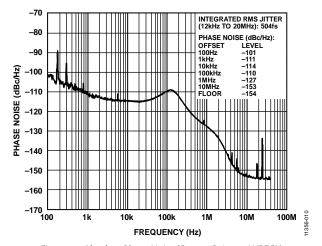

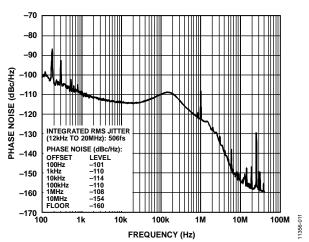

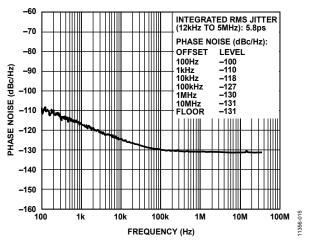

### **JITTER GENERATION USING 25 MHZ SQUARE WAVE**

Both PLLs are generating the same output frequency and use a 25 MHz square wave for the input reference. The loop bandwidth is set to the default value of 300 kHz. Where multiple driver types are listed, there is no significant difference between driver types. Fractional mode turned on, unless otherwise stated.

Table 11.

| Parameter                         | Min | Тур | Max | Unit   | Test Conditions/Comments              |

|-----------------------------------|-----|-----|-----|--------|---------------------------------------|

| JITTER GENERATION                 |     |     |     |        | f <sub>REF</sub> = 25 MHz square wave |

| LVPECL, HCSL, LVDS Driver         |     |     |     |        |                                       |

| $f_{OUT} = 622.08 \text{ MHz}$    |     |     |     |        |                                       |

| Bandwidth: 12 kHz to 20 MHz       |     | 515 |     | fs rms |                                       |

| Bandwidth: 20 kHz to 80 MHz       |     | 516 |     | fs rms |                                       |

| f <sub>оит</sub> = 693.48 MHz     |     |     |     |        |                                       |

| Bandwidth: 12 kHz to 20 MHz       |     | 504 |     | fs rms |                                       |

| Bandwidth: 20 kHz to 80 MHz       |     | 505 |     | fs rms |                                       |

| $f_{OUT} = 174.703 \text{ MHz}$   |     |     |     |        |                                       |

| Bandwidth: 12 kHz to 20 MHz       |     | 517 |     | fs rms |                                       |

| Bandwidth: 20 kHz to 80 MHz       |     | 523 |     | fs rms |                                       |

| $f_{OUT} = 161.1328 \text{ MHz}$  |     |     |     |        |                                       |

| Bandwidth: 12 kHz to 20 MHz       |     | 527 |     | fs rms |                                       |

| Bandwidth: 20 kHz to 80 MHz       |     | 530 |     | fs rms |                                       |

| LVPECL, HCSL, LVDS, LVCMOS Driver |     |     |     |        |                                       |

| f <sub>ουτ</sub> = 156.25 MHz     |     |     |     |        | Integer mode operation                |

| Bandwidth: 12 kHz to 20 MHz       |     | 290 |     | fs rms |                                       |

| Bandwidth: 1.875 MHz to 20 MHz    |     | 61  |     | fs rms |                                       |

| Bandwidth: 20 kHz to 80 MHz       |     | 292 |     | fs rms |                                       |

### **ABSOLUTE MAXIMUM RATINGS**

Table 12.

| Parameter                                                | Rating                                                                                       |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Supply Voltage (VDD)                                     | 4.6 V                                                                                        |

| Inputs (V <sub>IN</sub> ) (Except for CS Pin)            | $-0.50  V$ to $V_{DD} + 0.5  V$                                                              |

| CS Pin                                                   | V <sub>DD</sub> + 2.5 V                                                                      |

| Outputs (Vouт)                                           | $-0.50 \text{ V to V}_{DD} + 0.5 \text{ V}$<br>$-25^{\circ}\text{C to } +85^{\circ}\text{C}$ |

| Operating Temperature Range (T <sub>A</sub> ) Industrial | −25°C to +85°C                                                                               |

| Storage Temperature Range (Ts)                           | −65°C to +150°C                                                                              |

Stresses at or above those listed under Absolute Maximum Ratings may cause permanent damage to the product. This is a stress rating only; functional operation of the product at these or any other conditions above those indicated in the operational section of this specification is not implied. Operation beyond the maximum operating conditions for extended periods may affect product reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

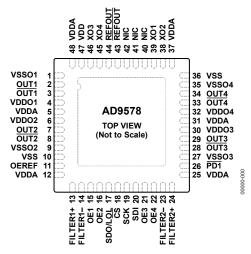

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

NOTES

1. NIC = NOT INTERNALLY CONNECTED. LEAVE THIS PIN UNCONNECTED.

2. THE EXPOSED PAD ON THE BOTTOM OF THE PACKAGE MUST

BE CONNECTED TO GROUND FOR PROPER OPERATION.

Figure 3. Pin Configuration

**Table 13. Pin Function Descriptions**

| Pin No.                  | Mnemonic  | Туре                      | Description                                                                                                                                                                                                      |

|--------------------------|-----------|---------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1                        | VSSO1     | Negative power            | Return Path Ground for Clock Output 1.                                                                                                                                                                           |

| 2                        | OUT1      | Output                    | Clock Output 1 Derived from PLL1. Supports frequencies up to the device maximum. OUT1 is a selectable <sup>1</sup> pin. When used in LVCMOS mode, OUT1 is the active pin.                                        |

| 3                        | OUT1      | Output                    | Active Low Clock Output 1 Derived from PLL1. Supports frequencies up to the device maximum. OUT1 is a selectable pin. OUT1 is not used in LVCMOS mode; it is high-Z in LVCMOS mode.                              |

| 4                        | VDDO1     | Supply,<br>positive power | Power Supply for Clock Output 1.                                                                                                                                                                                 |

| 5, 12, 25,<br>31, 37, 48 | VDDA      | Supply, positive power    | 2.5 V or 3.3 V Analog Power Supply.                                                                                                                                                                              |

| 6                        | VDDO2     | Supply, positive power    | Power Supply for Clock Output 2.                                                                                                                                                                                 |

| 7                        | OUT2      | Output                    | Clock Output 2 Derived from PLL1. Supports frequencies up to the device maximum. OUT2 is a selectable <sup>1</sup> pin. When used in LVCMOS mode, OUT2 is the active pin.                                        |

| 8                        | OUT2      | Output                    | Active Low <u>Clock</u> Output 2 Derived from PLL1. Supports frequencies up to the device maximum. OUT1 is a selectable pin. OUT2 is not used in LVCMOS mode; it is high-Z in LVCMOS mode.                       |

| 9                        | VSSO2     | Negative power            | Return Path Ground for Clock Output 2.                                                                                                                                                                           |

| 10, 36                   | VSS       | Negative power            | Device Ground.                                                                                                                                                                                                   |

| 11                       | OEREF     | Input                     | Output Enable for REFOUT and $\overline{\text{REFOUT}}$ Pins, LVCMOS. Active high. This pin has an internal 75 k $\Omega$ pull-down resistor.                                                                    |

| 13                       | FILTER1+  | Filter                    | Phase-Locked Loop 1 (PLL1) Filter Node, Positive Side. Connect a 220 nF capacitor between this pin and Pin 14.                                                                                                   |

| 14                       | FILTER1-  | Filter                    | PLL1 Filter Node, Negative Side. Connect a 220 nF capacitor between this pin and Pin 13.                                                                                                                         |

| 15                       | OE1       | Input                     | Output Enable 1 for Clock Output 1, LVCMOS. Places OUT1 and OUT1 in a high-Z state.                                                                                                                              |

|                          |           |                           | Active high. This pin has an internal 75 k $\Omega$ pull-up resistor.                                                                                                                                            |

| 16                       | OE2       | Input                     | Output Enable 2 for Clock Output 2, LVCMOS. Places OUT2 and OUT2 in a high-Z state.                                                                                                                              |

|                          |           |                           | Active high. This pin has an internal 75 $k\Omega$ pull-up resistor.                                                                                                                                             |

| 17                       | SDO/LOL   | Output                    | Serial Data Output for SPI Control/Loss of Lock, LVCMOS.                                                                                                                                                         |

| 18                       | <u>cs</u> | Input                     | Chip Select for SPI Control, LVCMOS. Active low. When this pin is set to 5 V, OTP programming is enabled (see Table 4 and the OTP Programming section). This pin has an internal 75 k $\Omega$ pull-up resistor. |

| 19                       | SCK       | Input                     | Serial Clock Input for SPI Control, LVCMOS.                                                                                                                                                                      |

| Pin No.    | Mnemonic | Туре                   | Description                                                                                                                                                                                                                                                                         |  |  |  |

|------------|----------|------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| 18         | CS       | Input                  | Chip Select for SPI Control, LVCMOS. Active low. When this pin is set to 5 V, OTP                                                                                                                                                                                                   |  |  |  |

|            |          |                        | programming is enabled (see Table 4 and the OTP Programming section). This pin has an internal 75 k $\Omega$ pull-up resistor.                                                                                                                                                      |  |  |  |

| 19         | SCK      | Input                  | Serial Clock Input for SPI Control, LVCMOS.                                                                                                                                                                                                                                         |  |  |  |

| 20         | SDI      | Input                  | Serial Data Input for SPI Control, LVCMOS.                                                                                                                                                                                                                                          |  |  |  |

| 21         | OE3      | Input                  | Output Enable 3 for Clock Output 3, LVCMOS. Places OUT3 and $\overline{\text{OUT3}}$ in a high-Z state. Active high is the default but active low is programmable. This pin has an internal 75 k $\Omega$ pull-up resistor.                                                         |  |  |  |

| 22         | OE4      | Input                  | Output Enable 4 for Clock Output 4, LVCMOS. Places OUT4 and $\overline{\text{OUT4}}$ in a high-Z state. Active high is the default but active low is programmable. This pin has an internal 75 k $\Omega$ pull-up resistor.                                                         |  |  |  |

| 23         | FILTER2- | Filter                 | PLL2 Filter Node, Negative Side. Connect a 220 nF capacitor between this pin and Pin 24.                                                                                                                                                                                            |  |  |  |

| 24         | FILTER2+ | Filter                 | PLL2 Filter Node, Positive Side. Connect a 220 nF capacitor between this pin and Pin 23.                                                                                                                                                                                            |  |  |  |

| 26         | PD1      | Input                  | Active Low Power-Down for PLL1, LVCMOS. This pin has an internal 75 kΩ pull-up resistor.                                                                                                                                                                                            |  |  |  |

| 27         | VSSO3    | Negative power         | Return Path Ground for Clock Output 3.                                                                                                                                                                                                                                              |  |  |  |

| 28         | OUT3     | Output                 | Active Low Clock Output 3 Derived from PLL2. Supports frequencies up to the device maximum. OUT3 is a selectable pin. OUT3 is not used in LVCMOS mode; it is high-Z in LVCMOS mode.                                                                                                 |  |  |  |

| 29         | OUT3     | Output                 | Clock Output 3 Derived from PLL2. Supports frequencies up to the device maximum. OUT3 is a selectable pin. When used in LVCMOS mode, OUT3 is the active pin.                                                                                                                        |  |  |  |

| 30         | VDDO3    | Supply, positive power | Power Supply for Clock Output 3.                                                                                                                                                                                                                                                    |  |  |  |

| 32         | VDDO4    | Supply, positive power | Power Supply for Clock Output 4.                                                                                                                                                                                                                                                    |  |  |  |

| 33         | OUT4     | Output                 | Clock Output 4 Derived from PLL2. Supports frequencies up to the device maximum. OUT4 is not used in LVCMOS mode and is high-Z. OUT4 is a selectable pin.                                                                                                                           |  |  |  |

| 34         | OUT4     | Output                 | Clock Output 4 Derived from PLL2. Supports frequencies up to the device maximum. OUT4 is a selectable pin. When used in LVCMOS mode, OUT4 is the active pin.                                                                                                                        |  |  |  |

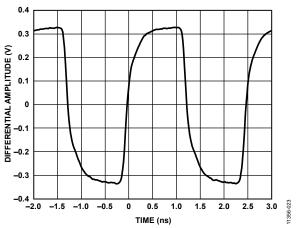

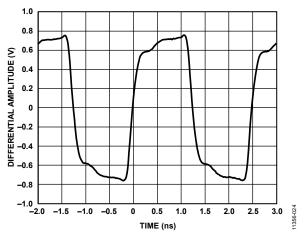

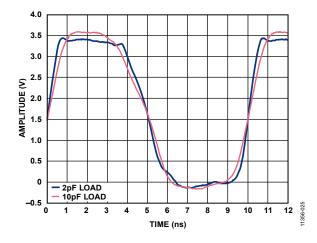

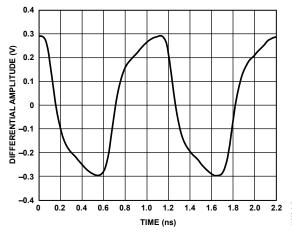

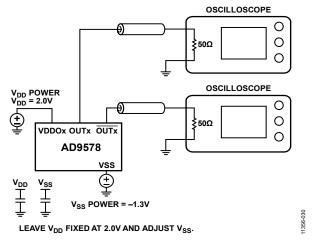

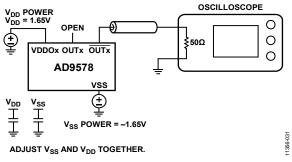

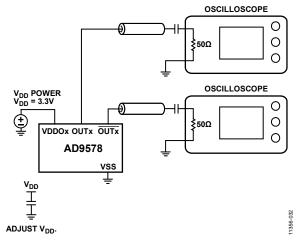

| 35         | VSSO4    | Negative power         | Return Path Ground for Clock Output 4.                                                                                                                                                                                                                                              |  |  |  |