# 100 MHz to 1000 MHz Integrated Broadband Receiver

**ADRF6850**

#### **FEATURES**

IQ quadrature demodulator Integrated fractional-N PLL and VCO

Gain control range: 60 dB

Input frequency range: 100 MHz to 1000 MHz

Input P1dB: +12 dBm at 0 dB gain Input IP3: +22.5 dBm at 0 dB gain

Noise figure: 11 dB at >39 dB gain, 49 dB at 0 dB gain Baseband 1 dB bandwidth: 250 MHz in wideband mode,

50 MHz in narrow-band mode

SPI/I<sup>2</sup>C serial interface

Power supply: +3.3 V/350 mA

#### **APPLICATIONS**

Broadband communications

Cellular communications

Satellite communications

#### **GENERAL DESCRIPTION**

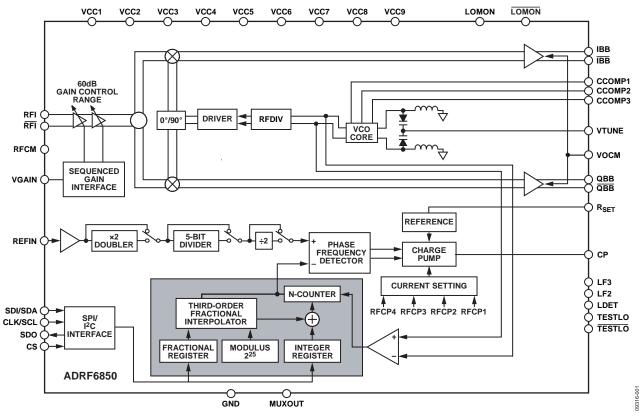

The ADRF6850 is a highly integrated broadband quadrature demodulator, frequency synthesizer, and variable gain amplifier (VGA). The device covers an operating frequency range from 100 MHz to 1000 MHz for use in both narrow-band and wideband communications applications, performing quadrature demodulation from IF directly to baseband frequencies.

The ADRF6850 demodulator includes a high modulus fractional-N frequency synthesizer with integrated VCO, providing better than 1 Hz frequency resolution, and a 60 dB gain control range provided by a front-end VGA.

Control of all the on-chip registers is through a user-selected SPI interface or I<sup>2</sup>C interface. The device operates from a single power supply ranging from 3.15 V to 3.45 V.

#### **FUNCTIONAL BLOCK DIAGRAM**

Figure 1.

### **ADRF6850\* Product Page Quick Links**

Last Content Update: 11/01/2016

### Comparable Parts

View a parametric search of comparable parts

### Evaluation Kits <a> □</a>

• ADRF6850 Evaluation Board

### Documentation <a>□</a>

#### **Data Sheet**

ADRF6850: 100 MHz to 1000 MHz Integrated Broadband Receiver Data Sheet

### Tools and Simulations

- ADIsimPLL<sup>TM</sup>

- ADIsimRF

### Reference Materials

#### **Product Selection Guide**

• RF Source Booklet

### Design Resources -

- ADRF6850 Material Declaration

- · PCN-PDN Information

- · Quality And Reliability

- · Symbols and Footprints

### Discussions <a>□</a>

View all ADRF6850 EngineerZone Discussions

### Sample and Buy -

Visit the product page to see pricing options

### Technical Support <a> Image: Page 1</a> <a> Image: Page 2</a> <a> Image: Page 3</a> <a>

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

### **TABLE OF CONTENTS**

| Features                                    | 1  |

|---------------------------------------------|----|

| Applications                                | 1  |

| General Description                         | 1  |

| Functional Block Diagram                    | 1  |

| Revision History                            | 2  |

| Specifications                              | 3  |

| Timing Characteristics                      | 5  |

| Absolute Maximum Ratings                    | 7  |

| ESD Caution                                 | 7  |

| Pin Configuration and Function Descriptions | 8  |

| Typical Performance Characteristics         | 10 |

| Theory of Operation                         | 18 |

| Overview                                    | 18 |

| PLL Synthesizer and VCO                     | 18 |

| Quadrature Demodulator                      | 20 |

| Variable Gain Amplifier (VGA)               | 20 |

| I <sup>2</sup> C Interface      |

|---------------------------------|

| SPI Interface                   |

| Program Modes                   |

| Register Map                    |

| Register Map Summary            |

| Register Bit Descriptions       |

| Suggested Power-Up Sequence30   |

| Initial Register Write Sequence |

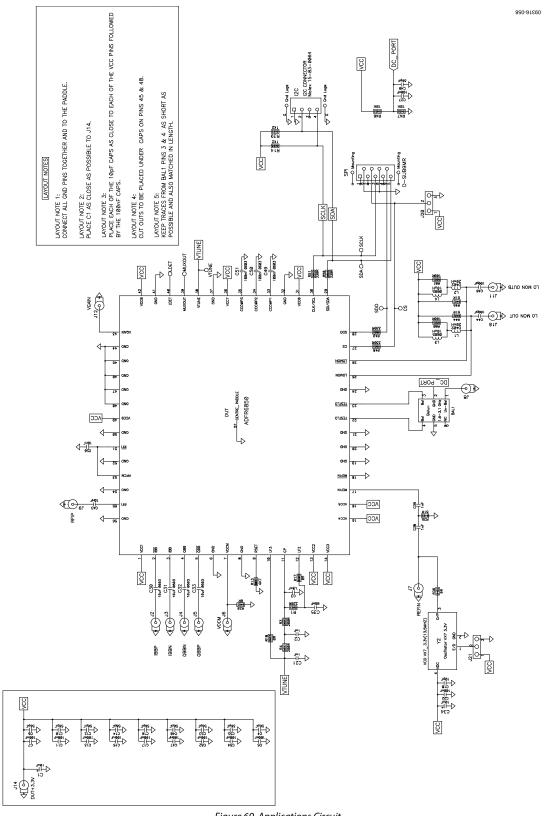

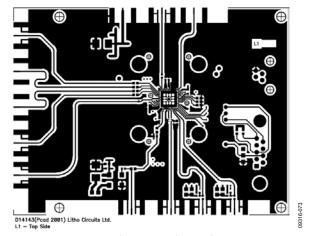

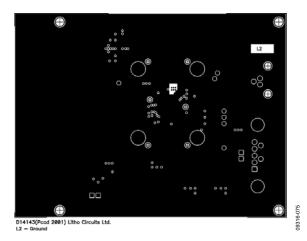

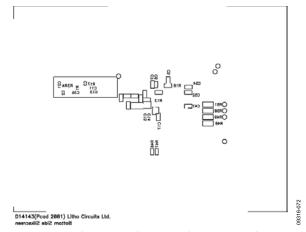

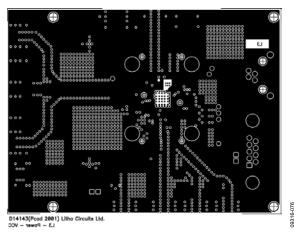

| Evaluation Board                |

| General Description31           |

| Hardware Description31          |

| PCB Schematic                   |

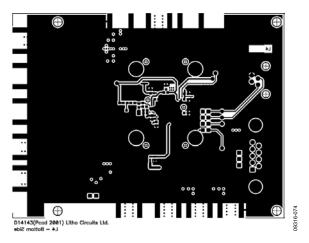

| PCB Artwork34                   |

| Bill of Materials35             |

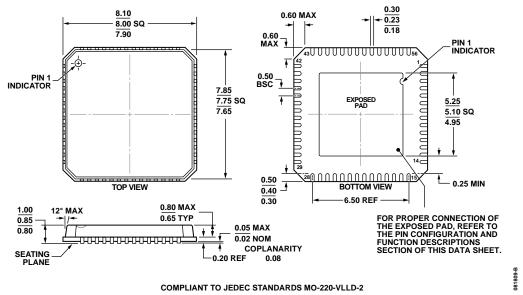

| Outline Dimensions              |

| Ordering Guide                  |

#### **REVISION HISTORY**

10/10—Revision 0: Initial Version

### **SPECIFICATIONS**

$V_{CC}$  = 3.3 V; ambient temperature ( $T_A$ ) = 25°C;  $Z_S$  = 50  $\Omega$ ;  $Z_L$  = 100  $\Omega$  differential; PLL loop bandwidth = 50 kHz; REFIN = 13.5 MHz; PFD = 27 MHz; baseband frequency = 20 MHz, narrow-band mode, unless otherwise noted.

Table 1.

| Parameter                           | Test Conditions/Comments                                        | Min | Тур          | Max             | Unit   |

|-------------------------------------|-----------------------------------------------------------------|-----|--------------|-----------------|--------|

| RF INPUT                            | RFI, RFI, VGAIN pins                                            |     |              |                 |        |

| Operating Frequency Range           |                                                                 | 100 |              | 1000            | MHz    |

| Input P1dB                          | 0 dB gain                                                       |     | +12          |                 | dBm    |

| ·                                   | 60 dB gain                                                      |     | -48          |                 | dBm    |

| Input IP3                           | 0 dB gain                                                       |     | +22.5        |                 | dBm    |

| ·                                   | 60 dB gain                                                      |     | -38          |                 | dBm    |

| Input IP2                           | 0 dB gain, single-ended input                                   |     | +40          |                 | dBm    |

| ·                                   | 60 dB gain, single-ended input                                  |     | -20          |                 | dBm    |

| Noise Figure (NF)                   | 0 dB gain                                                       |     | 49           |                 | dB     |

| 3 . ,                               | <39 dB gain NF rises 1:1 as gain in dB falls                    |     |              |                 |        |

|                                     | >39 dB gain                                                     |     | 11           |                 | dB     |

| Maximum Gain                        | $Z_s = 50 \Omega$ single-ended, $Z_L = 100 \Omega$ differential |     | 60           |                 | dB     |

| Minimum Gain                        | $Z_s = 50 \Omega$ single-ended, $Z_L = 100 \Omega$ differential |     | 0            |                 | dB     |

| Gain Conformance Error <sup>1</sup> | V <sub>GAIN</sub> from 200 mV to 1.3 V                          |     | 0.5          |                 | dB     |

| Gain Slope                          | GAIN                                                            |     | 25           |                 | mV/dB  |

| VGAIN Input Impedance               |                                                                 |     | 20           |                 | kΩ     |

| Return Loss                         | Relative to $Z_s = 50 \Omega$ , 100 MHz to 1 GHz                |     | 15           |                 | dB     |

| REFERENCE CHARACTERISTICS           | REFIN pin                                                       |     |              |                 |        |

| Input Frequency                     | With R divide-by-2 divider enabled                              | 10  |              | 300             | MHz    |

| input requeity                      | With R divide-by-2 divider disabled                             | 10  |              | 165             | MHz    |

| REFIN Input Sensitivity             | William and by 2 and an ansablea                                | 0.4 |              | V <sub>CC</sub> | V p-p  |

| REFIN Input Capacitance             |                                                                 | 0   |              | 10              | pF     |

| REFIN Input Current                 |                                                                 |     |              | ±100            | μΑ     |

| CHARGE PUMP                         | CP and RSET pins                                                |     |              |                 | μ, τ   |

| I <sub>CP</sub> Sink/Source         | Programmable                                                    |     |              |                 |        |

| High Value                          | With $R_{SFT} = 4.7 \text{ k}\Omega$                            |     | 5            |                 | mA     |

| Low Value                           | SEI WALL                                                        |     | 312.5        |                 | μΑ     |

| Absolute Accuracy                   | With $R_{SET} = 4.7 \text{ k}\Omega$                            |     | 2.5          |                 | %      |

| VCO                                 | SEI WIEL                                                        |     |              |                 | 1      |

| Gain                                | K <sub>vco</sub>                                                |     | 15           |                 | MHz/V  |

| SYNTHESIZER SPECIFICATIONS          | Loop bandwidth = 50 kHz                                         |     |              |                 |        |

| Frequency Increment                 | 2006 201101110111                                               |     | 1            |                 | Hz     |

| Phase Frequency Detector            |                                                                 | 10  | ·            | 30              | MHz    |

| Spurs                               |                                                                 |     |              |                 |        |

| Spais                               | Integer boundary < loop bandwidth                               |     | -55          |                 | dBc    |

|                                     | >10 MHz offset from carrier                                     |     | -70          |                 | dBc    |

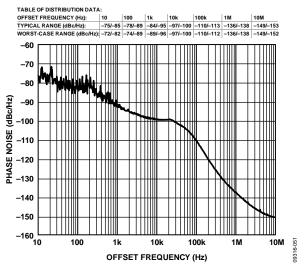

| Phase Noise                         | LO frequency = 1000 MHz                                         |     | 70           |                 | abc    |

| Thuse Wolse                         | @ 10 Hz offset                                                  |     | <b>-75</b>   |                 | dBc/Hz |

|                                     | @ 100 Hz offset                                                 |     | -80          |                 | dBc/Hz |

|                                     | @ 1 kHz offset                                                  |     | -90          |                 | dBc/Hz |

|                                     | @ 10 kHz offset                                                 |     | -98          |                 | dBc/Hz |

|                                     | @ 100 kHz offset                                                |     | -110         |                 | dBc/Hz |

|                                     | @ 1 MHz offset                                                  |     | -110<br>-136 |                 | dBc/Hz |

|                                     | >10 MHz offset                                                  |     | -149         |                 | dBc/Hz |

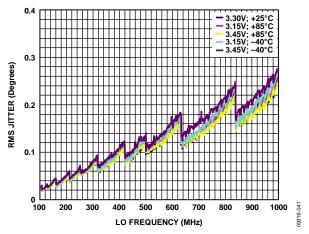

| Integrated Phase Noise              | 1 kHz to 8 MHz integration bandwidth                            |     | 0.26         |                 | °rms   |

| Parameter                                         | Test Conditions/Comments                                                    |      | Тур            | Max  | Unit     |  |

|---------------------------------------------------|-----------------------------------------------------------------------------|------|----------------|------|----------|--|

| Frequency Settling                                | Any step size, maximum frequency error = 1 kHz                              |      | 260            |      | μs       |  |

| Maximum Frequency Step for No<br>Autocalibration  | Frequency step with no autocalibration routine;<br>Register CR24, Bit 0 = 1 |      |                | 100  | kHz      |  |

| BASEBAND OUTPUTS                                  | IBB, IBB, QBB, QBB, VOCM pins                                               |      |                |      |          |  |

| Maximum Swing                                     | Driving $Z_1 = 100 \Omega$ differential                                     |      | 2.5            |      | V p-p    |  |

| Common-Mode Range                                 |                                                                             | 1.2  |                | 1.6  | V        |  |

| Output Impedance                                  | Differential                                                                |      | 28             |      | Ω        |  |

| Output DC Offset                                  | RFI terminated in $Z_s = 50 \Omega$                                         |      | ±20            |      | mV       |  |

| 1 dB Bandwidth                                    |                                                                             |      |                |      |          |  |

| Wideband Mode                                     |                                                                             |      | 250            |      | MHz      |  |

| Narrow-Band Mode                                  |                                                                             |      | 50             |      | MHz      |  |

| IQ Balance                                        |                                                                             |      |                |      |          |  |

| Amplitude                                         |                                                                             |      |                |      |          |  |

| Wideband Mode                                     | Baseband frequency ≤ 250 MHz                                                |      | ±0.1           |      | dB       |  |

| Narrow-Band Mode                                  | Baseband frequency ≤ 33.2 MHz                                               |      | ±0.1           |      | dB       |  |

| Phase                                             | , ,                                                                         |      |                |      |          |  |

| Wideband Mode                                     | Baseband frequency ≤ 250 MHz                                                |      | ±0.5           |      | Degree   |  |

| Narrow-Band Mode                                  | Baseband frequency ≤ 33.2 MHz                                               |      | ±0.25          |      | Degree   |  |

| IQ Output Impedance Mismatch                      | Baseband frequency = 10 MHz                                                 |      | ±0.3           |      | %        |  |

| Group Delay Variation                             | ,                                                                           |      |                |      |          |  |

| Wideband Mode                                     | Baseband frequency ≤ 210 MHz                                                |      | 0.25           |      | ns       |  |

|                                                   | Baseband frequency ≤ 250 MHz                                                |      | 0.35           |      | ns       |  |

| Narrow-Band Mode                                  | Baseband frequency ≤ 33.2 MHz                                               |      | 0.2            |      | ns       |  |

| LO to IQ Leakage                                  | 1×LO                                                                        |      | -40            |      | dBm      |  |

|                                                   | 2×LO                                                                        |      | -60            |      | dBm      |  |

|                                                   | 4×LO                                                                        |      | -60            |      | dBm      |  |

| RF to IQ Leakage                                  | Relative to IQ output level                                                 |      | -40            |      | dBc      |  |

| MONITOR OUTPUT                                    | LOMON and LOMON pins                                                        |      |                |      |          |  |

| Nominal Output Power                              | ·                                                                           |      | -24            |      | dBm      |  |

| LOGIC INPUTS                                      | SDI/SDA, CLK/SCL, CS pins                                                   |      |                |      |          |  |

| Input High Voltage, V <sub>INH</sub>              | CS                                                                          | 1.4  |                |      | V        |  |

| Input Low Voltage, V <sub>INI</sub>               | CS                                                                          |      |                | 0.6  | V        |  |

| Input High Voltage, V <sub>INH</sub>              | SDI/SDA, CLK/SCL                                                            | 2.1  |                |      | V        |  |

| Input Low Voltage, V <sub>INI</sub>               | SDI/SDA, CLK/SCL                                                            |      |                | 1.1  | V        |  |

| Input Current, I <sub>INH</sub> /I <sub>INL</sub> | CS, SDI/SDA, CLK/SCL                                                        |      |                | ±1   | μΑ       |  |

| Input Capacitance, C <sub>IN</sub>                | CS, SDI/SDA, CLK/SCL                                                        |      |                | 10   | pF       |  |

| LOGIC OUTPUTS                                     |                                                                             |      |                |      | <b>'</b> |  |

| Output High Voltage, V <sub>OH</sub>              | SDO, LDET pins; I <sub>OH</sub> = 500 μA                                    | 2.8  |                |      | V        |  |

| Output Low Voltage, V <sub>OL</sub>               | SDO, LDET pins; $I_{OI} = 500 \mu A$                                        |      |                | 0.4  | V        |  |

| 2 0 1 0 1 2 1 1 1 1 1 1 1 1 1 1 1 1 1 1           | SDA (SDI/SDA) pins; I <sub>OL</sub> = 3 mA                                  |      |                | 0.4  | V        |  |

| POWER SUPPLIES                                    | VCC1, VCC2, VCC3, VCC4, VCC5, VCC6, VCC7, VCC8, and VCC9 pins               |      |                |      |          |  |

| Voltage Range                                     | ·                                                                           | 3.15 | 3.3            | 3.45 | V        |  |

| Supply Current                                    |                                                                             |      | 350            | 440  | mA       |  |

| Operating Temperature                             |                                                                             | -40  | · <del>-</del> | +85  | °C       |  |

$<sup>^{\</sup>rm 1}$  Difference between channel gain and linear fit to channel gain.

### **TIMING CHARACTERISTICS**

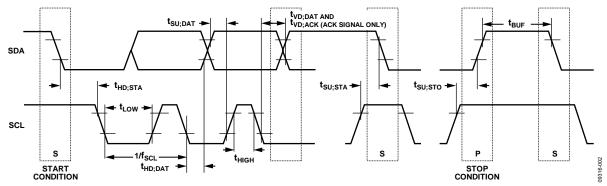

#### I<sup>2</sup>C Interface Timing

Table 2.

| Parameter <sup>1</sup>      | Symbol              | Limit | Unit    |  |

|-----------------------------|---------------------|-------|---------|--|

| SCL Clock Frequency         | f <sub>SCL</sub>    | 400   | kHz max |  |

| SCL Pulse Width High        | t <sub>HIGH</sub>   | 600   | ns min  |  |

| SCL Pulse Width Low         | t <sub>LOW</sub>    | 1300  | ns min  |  |

| Start Condition Hold Time   | t <sub>HD;STA</sub> | 600   | ns min  |  |

| Start Condition Setup Time  | t <sub>su;sta</sub> | 600   | ns min  |  |

| Data Setup Time             | t <sub>SU;DAT</sub> | 100   | ns min  |  |

| Data Hold Time              | t <sub>HD;DAT</sub> | 300   | ns min  |  |

| Stop Condition Setup Time   | t <sub>SU;STO</sub> | 600   | ns min  |  |

| Data Valid Time             | t <sub>VD;DAT</sub> | 900   | ns max  |  |

| Data Valid Acknowledge Time | t <sub>VD;ACK</sub> | 900   | ns max  |  |

| Bus Free Time               | t <sub>BUF</sub>    | 1300  | ns min  |  |

<sup>&</sup>lt;sup>1</sup> See Figure 2.

Figure 2. I<sup>2</sup>C Port Timing Diagram

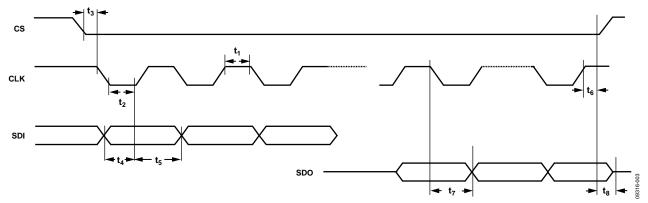

### SPI Interface Timing

Table 3.

| Parameter <sup>1</sup>    | Symbol           | Limit | Unit    |

|---------------------------|------------------|-------|---------|

| CLK Frequency             | f <sub>CLK</sub> | 20    | MHz max |

| CLK Pulse Width High      | t <sub>1</sub>   | 15    | ns min  |

| CLK Pulse Width Low       | t <sub>2</sub>   | 15    | ns min  |

| Start Condition Hold Time | t <sub>3</sub>   | 5     | ns min  |

| Data Setup Time           | t <sub>4</sub>   | 10    | ns min  |

| Data Hold Time            | t <sub>5</sub>   | 5     | ns min  |

| Stop Condition Setup Time | t <sub>6</sub>   | 5     | ns min  |

| SDO Access Time           | t <sub>7</sub>   | 15    | ns min  |

| CS to SDO High Impedance  | t <sub>8</sub>   | 25    | ns max  |

<sup>&</sup>lt;sup>1</sup> See Figure 3.

Figure 3. SPI Port Timing Diagram

### **ABSOLUTE MAXIMUM RATINGS**

**Table 4. Absolute Maximum Ratings**

| Parameter                                                                  | Rating           |

|----------------------------------------------------------------------------|------------------|

| Supply Voltage Pins (VCC1, VCC2, VCC3, VCC4, VCC5, VCC6, VCC7, VCC8, VCC9) | -0.3 V to +4.0 V |

| Analog Input/Output                                                        | -0.3 V to +4.0 V |

| Digital Input/Output                                                       | -0.3 V to +4.0 V |

| RFI, RFCM                                                                  | 0 V to 3.0 V     |

| $\theta_{JA}$ (Exposed Paddle Soldered Down)                               | 26°C/W           |

| Maximum Junction Temperature                                               | 125°C            |

| Storage Temperature Range                                                  | −65°C to +150°C  |

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### **ESD CAUTION**

**ESD** (electrostatic discharge) sensitive device. Charged devices and circuit boards can discharge without detection. Although this product features patented or proprietary protection circuitry, damage may occur on devices subjected to high energy ESD. Therefore, proper ESD precautions should be taken to avoid performance degradation or loss of functionality.

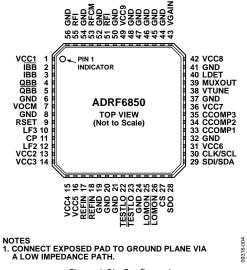

### PIN CONFIGURATION AND FUNCTION DESCRIPTIONS

Figure 4. Pin Configuration

**Table 5. Pin Function Descriptions**

| Pin No.                                                                       | Mnemonic              | Description                                                                                                                                                                                                                                                           |

|-------------------------------------------------------------------------------|-----------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 13, 14, 15, 16,<br>31, 36, 42, 49                                          | VCC1 to VCC9          | Positive Power Supplies. Apply a 3.3 V power supply to all VCCx pins. Decouple each pin with a power supply decoupling capacitor.                                                                                                                                     |

| 6, 8, 19, 20, 21,<br>24, 32, 37, 41,<br>44, 45, 46, 47,<br>48, 50, 52, 54, 56 | GND                   | Analog Ground. Connect to a low impedance ground plane.                                                                                                                                                                                                               |

| 2, 3, 4, 5                                                                    | IBB, IBB, QBB,<br>QBB | Differential In-Phase and Quadrature Baseband Outputs. These low impedance outputs can drive 2.5 V p-p into $100\Omega$ differential loads.                                                                                                                           |

| 7                                                                             | VOCM                  | Baseband Common-Mode Voltage Input. When ac coupling the baseband output pins, ground VOCM. There is an option to apply an external voltage, which may be relevant when dc coupling the baseband output pins. Note that Register CR29, Bit 6 must be set accordingly. |

| 33                                                                            | CCOMP1                | Internal Compensation Node. This pin must be decoupled to ground with a 100 nF capacitor.                                                                                                                                                                             |

| 34                                                                            | CCOMP2                | Internal Compensation Node. This pin must be decoupled to ground with a 100 nF capacitor.                                                                                                                                                                             |

| 35                                                                            | CCOMP3                | Internal Compensation Node. This pin must be decoupled to ground with a 100 nF capacitor.                                                                                                                                                                             |

| 38                                                                            | VTUNE                 | Control Input to the VCO. This voltage determines the output frequency and is derived from filtering the CP output voltage.                                                                                                                                           |

| 9                                                                             | RSET                  | Charge Pump Current Set. Connecting a resistor between this pin and ground sets the maximum charge pump output current. The relationship between $I_{CP}$ and $R_{SET}$ is                                                                                            |

|                                                                               |                       | $I_{CPmax} = \frac{23.5}{R_{SET}}$                                                                                                                                                                                                                                    |

|                                                                               |                       | where $R_{SET} = 4.7 \text{ k}\Omega$ and $I_{CPmax} = 5 \text{ mA}$ .                                                                                                                                                                                                |

| 11                                                                            | СР                    | Charge Pump Output. When enabled, this provides $\pm I_{CP}$ to the external loop filter, which in turn, drives the internal VCO.                                                                                                                                     |

| 27                                                                            | CS                    | Chip Select. CMOS input. When CS is high, the data stored in the shift registers is loaded into one of the 31 registers. In I <sup>2</sup> C mode, when CS is high, the slave address of the device is 0x78, and when CS is low, the slave address is 0x58.           |

| 29                                                                            | SDI/SDA               | Serial Data Input for SPI Port, Serial Data Input/Output for I <sup>2</sup> C Port. In SPI mode. This input is a high impedance CMOS data input, and data is loaded in an 8-bit word. In I <sup>2</sup> C mode, this pin is a bidirectional port.                     |

| 30                                                                            | CLK/SCL               | Serial Clock Input for SPI/I <sup>2</sup> C Port. This serial clock is used to clock in the serial data to the registers. This input is a high impedance CMOS input.                                                                                                  |

| 28                                                                            | SDO                   | Serial Data Output for SPI Port. Register states can be read back on the SDO data output line in an 8-bit word.                                                                                                                                                       |

| 17                                                                            | REFIN                 | Reference Input. AC couple this high impedance CMOS input.                                                                                                                                                                                                            |

| 18                                                                            | REFIN                 | Reference Input Bar. Ground this pin.                                                                                                                                                                                                                                 |

| Pin No. | Mnemonic        | Description                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|---------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 51, 55  | RFI, RFI        | RF Inputs. 50 $\Omega$ internally biased RF inputs. For single-ended operation, RFI must be ac-coupled to the source, and $\overline{\text{RFI}}$ must be ac-coupled to the ground plane.                                                                                                                                                                                                                            |  |

| 53      | RFCM            | RF Input Common Mode. Connect to RFI when driving the input in single-ended mode. When driving the input differentially using a balun, connect this pin to the common terminal of the output coil of the balun. Decouple RFCM to the ground plane.                                                                                                                                                                   |  |

| 25, 26  | LOMON,<br>LOMON | Differential Monitor Outputs. These pins provide a replica of the internal local oscillator frequency (1× LO) at four different power levels: –6 dBm, –12 dBm, –18 dBm, and –24 dBm, approximately. These open-collector outputs must be terminated with external resistors to VCCx. These outputs can be disabled through serial port programming and should be connected to VCCx if not used.                      |  |

| 10, 12  | LF3/LF2         | Extra Loop Filter Pins for Fastlock. Use these pins to reduce lock time.                                                                                                                                                                                                                                                                                                                                             |  |

| 40      | LDET            | Lock Detect. This pin provides an active high output when the PLL frequency is locked. The lock detect timing is controlled by Register CR14 (Bit 7) and Register CR23 (Bit 3).                                                                                                                                                                                                                                      |  |

| 39      | MUXOUT          | Muxout. This output is a test output for diagnostic use only. Allow this pin to remain open circuit.                                                                                                                                                                                                                                                                                                                 |  |

| 22, 23  | TESTLO, TESTLO  | Differential Test Inputs. For internal use only. These pins should be grounded.                                                                                                                                                                                                                                                                                                                                      |  |

| 43      | VGAIN           | VGA Gain Input. Drive this pin by a voltage in the range from 0 V to 1.5 V. This voltage controls the gain of the VGA. A 0 V input sets the VGA gain to 0 dB, whereas a 1.5 V input sets the VGA gain to +60 dB if the VGA Gain Mode Polarity Bit CR30, Bit 2, is set to 0. If the VGA gain mode polarity bit is set to 1, a 0 V input sets the VGA gain to +60 dB, whereas a 1.5 V input sets the VGA gain to 0 dB. |  |

|         | EP              | Exposed Paddle. Connect the exposed pad to the ground plane via a low impedance path.                                                                                                                                                                                                                                                                                                                                |  |

### TYPICAL PERFORMANCE CHARACTERISTICS

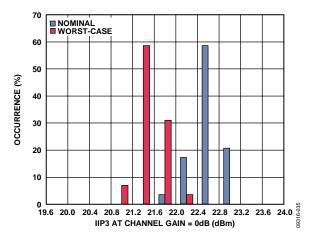

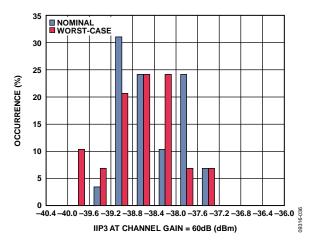

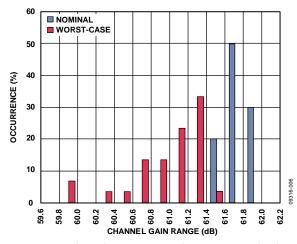

A nominal condition is defined as 25°C, 3.30 V, and worst-case frequency. A worst-case condition is defined as having the worst-case temperature, supply voltage, and frequency.

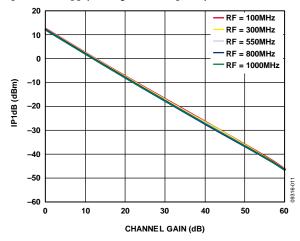

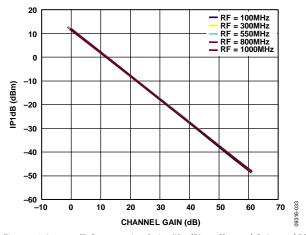

Figure 5. Input 1dB Compression Point (IP1dB) vs. Channel Gain, and RF Input Frequency, Nominal Conditions, Narrow-Band Mode

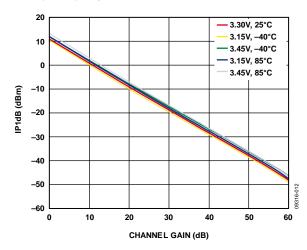

Figure 6. Input 1dB Compression Point (IP1dB) vs. Channel Gain, Supply, and Temperature, RF Input Frequency = 100 MHz, Narrow-Band Mode

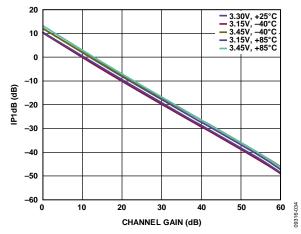

Figure 7. Input 1dB Compression Point (IP1dB) vs. Channel Gain, Supply, and Temperature, RF Input Frequency = 1000 MHz, Narrow-Band Mode

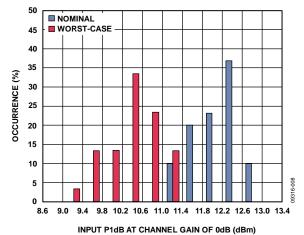

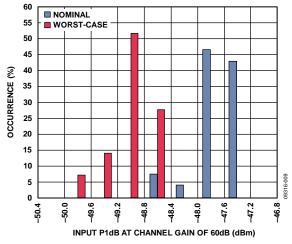

Figure 8. Input 1dB Compression Point (IP1dB) Distribution with Channel Gain = 0 dB at Nominal and Worst-Case Conditions

Figure 9. Input 1dB Compression Point (IP1dB) Distribution with Channel Gain = 60 dB at Nominal and Worst-Case Conditions

Figure 10. Input 1dB Compression Point (IP1dB) vs. Channel Gain, and RF Input Frequency,  $V_{\rm OCM}$  = 1.2 V, Nominal Conditions, Narrow-Band Mode

Figure 11. Input 1dB Compression Point (IP1dB) vs. Channel Gain, and RF Input Frequency,  $V_{\rm OCM}=1.6$  V, Nominal Conditions, Narrow-Band Mode

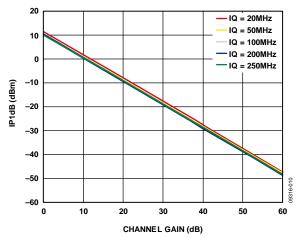

Figure 12. Input 1dB Compression Point (IP1dB) vs. Channel Gain, and IQ Output Frequency, LO = 1000 MHz, Nominal Conditions, Wideband Mode

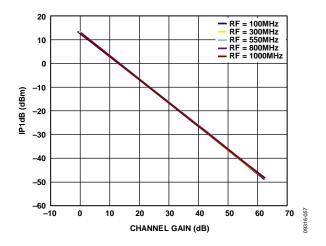

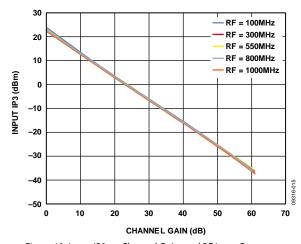

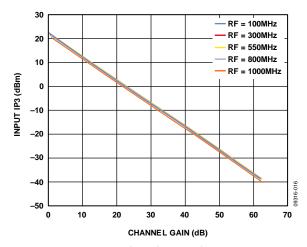

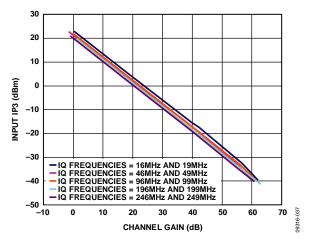

Figure 13. Input IP3 vs. Channel Gain, and RF Input Frequency, Nominal Conditions

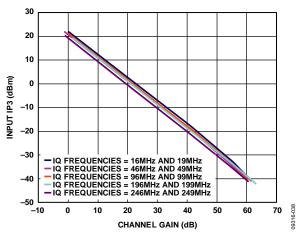

Figure 14. Input IP3 vs. Channel Gain, and RF Input Frequency, Worst-Case Conditions

Figure 15. Input IP3 Distribution with Channel Gain = 0 dB at Nominal and Worst-Case Conditions

Figure 16. Input IP3 Distribution with Channel Gain = 60 dB at Nominal and Worst-Case Conditions

Figure 17. Input IP3 vs. Channel Gain, and IQ Output Frequency, Wideband Mode, Nominal Conditions

Figure 18. Input IP3 vs. Channel Gain, and IQ Output Frequency, Wideband Mode, Worst-Case Conditions

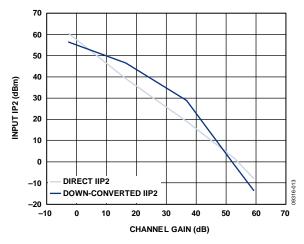

Figure 19. Input IP2 vs. Channel Gain, Wideband Mode, Nominal Conditions

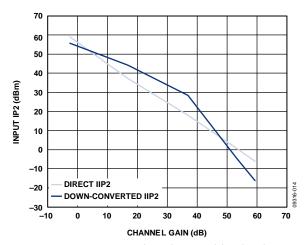

Figure 20. Input IP2 vs. Channel Gain, Wideband Mode, Worst-Case Conditions

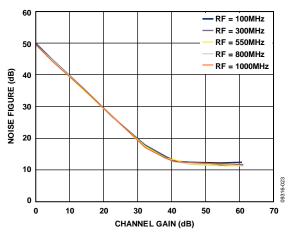

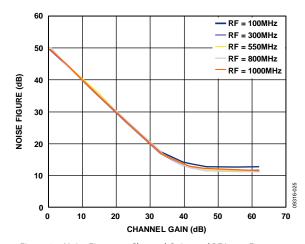

Figure 21. Noise Figure vs. Channel Gain, and RF Input Frequency, Narrow-Band Mode, Nominal Conditions

Figure 22. Noise Figure vs. Channel Gain, and RF Input Frequency, Narrow-Band Mode, Worst-Case Conditions

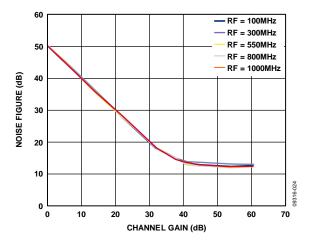

Figure 23. Noise Figure Distribution vs. Channel Gain, Narrow-Band Mode, Nominal Conditions

Figure 24. Noise Figure Distribution vs. Channel Gain, Narrow-Band Mode, Worst-Case Conditions

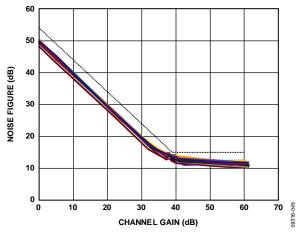

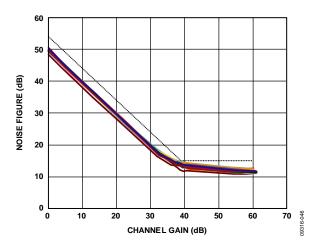

Figure 25. Noise Figure vs. Channel Gain, and RF Input Frequency, Wideband Mode, Nominal Conditions

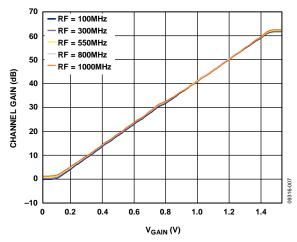

Figure 26. Channel Gain vs. V<sub>GAIN</sub> and RF Input Frequency, Nominal Conditions

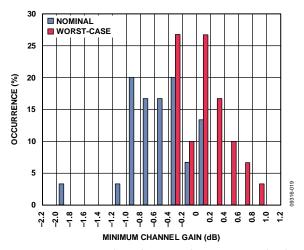

Figure 27. Channel Gain Range Distribution at Nominal and Worst-Case Conditions

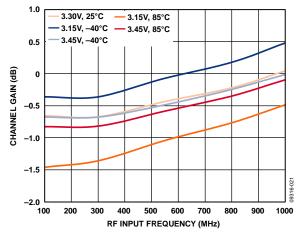

Figure 28. Minimum Channel Gain vs. RF Input Frequency, Supply, and Temperature

Figure 29. Minimum Channel Gain Distribution at Nominal and Worst-Case Conditions

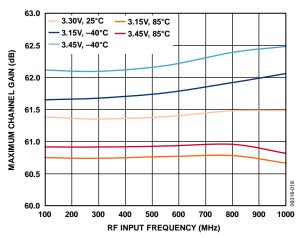

Figure 30. Maximum Channel Gain vs. RF Input Frequency, Supply, and Temperature

Figure 31. Maximum Channel Gain Distribution at Nominal and Worst-Case Conditions

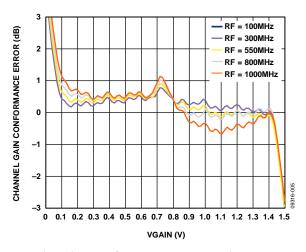

Figure 32. Channel Gain Conformance Error vs. V<sub>GAIN</sub> and RF Input Frequency, Nominal Conditions

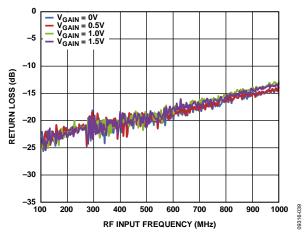

Figure 33. Input Return Loss vs. RF Input Frequency and Channel Gain, Nominal Conditions

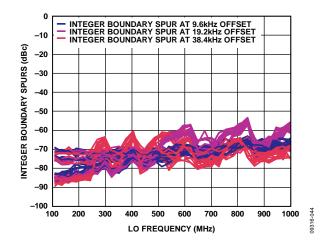

Figure 34. Integer Boundary Spurs vs. LO Frequency, Channel Gain, Supply, and Temperature

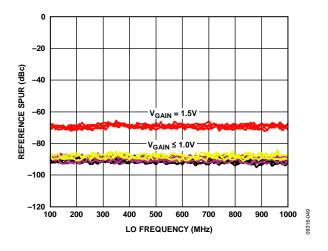

Figure 35. Reference Spurs at 13.5 MHz from Carrier vs. LO Frequency, Channel Gain, Supply, and Temperature

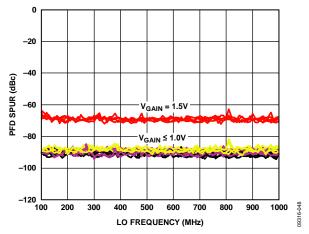

Figure 36. PFD Spurs at 27 MHz from Carrier vs. LO Frequency, Channel Gain, Supply, and Temperature

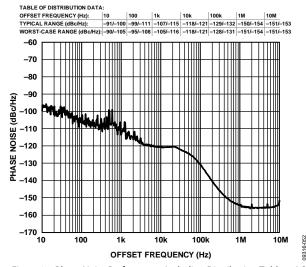

Figure 37. Phase Noise Performance Including Distribution Table at LO Frequency = 100 MHz at Nominal and Worst-Case Conditions

Figure 38. Phase Noise Performance Including Distribution Table at LO Frequency = 1000 MHz at Nominal and Worst-Case Conditions

Figure 39. Integrated Phase Noise vs. LO Frequency, Supply, and Temperature

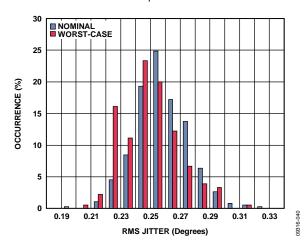

Figure 40. Integrated Phase Noise Distribution with LO Frequency = 1000 MHz at Nominal and Worst-Case Conditions

Figure 41. PLL Frequency Settling Time with Typical, Best-Case, and Worst-Case Frequency Hop with Lock Detect Shown, Nominal Conditions

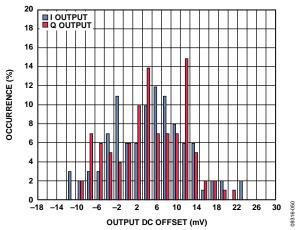

Figure 42. Output DC Offset Distribution for I and Q Outputs, Nominal Conditions

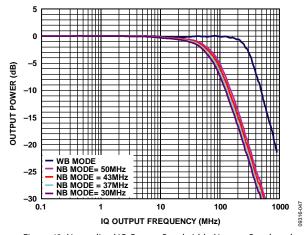

Figure 43. Normalized IQ Output Bandwidth, Narrow-Band, and Wideband Modes, Nominal Conditions

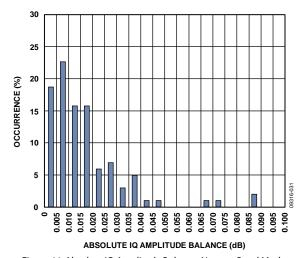

Figure 44. Absolute IQ Amplitude Balance, Narrow-Band Mode, Nominal Conditions

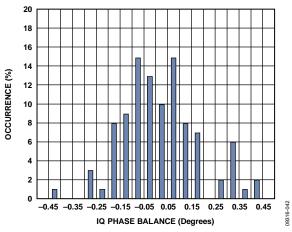

Figure 45. IQ Phase Balance, Narrow-Band Mode, Nominal Conditions

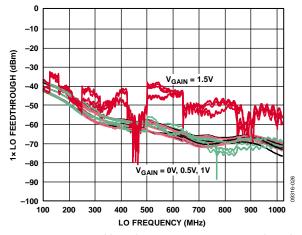

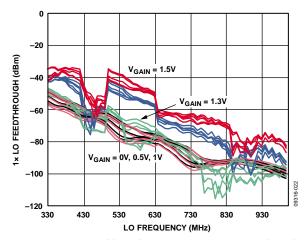

Figure 46.  $1 \times$  LO Feedthrough vs. LO Frequency,  $V_{\text{GAIN}}$  Supply, and Temperature (Narrow-Band Mode)

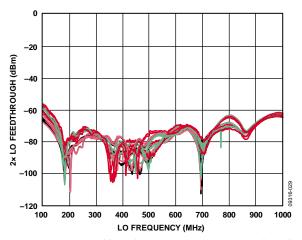

Figure 47. 2×LO Feedthrough vs. LO Frequency, V<sub>GAIN</sub> Supply, and Temperature (Narrow-Band Mode)

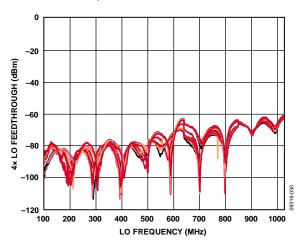

Figure 48. 4× LO Feedthrough vs. LO Frequency, V<sub>GAIN</sub> Supply, and Temperature (Narrow-Band Mode)

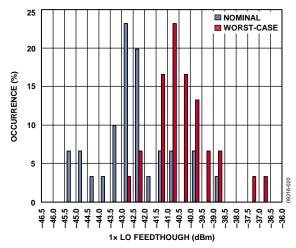

Figure 49. 1× LO Feedthrough Distribution at Nominal and Worst-Case Conditions with LO Frequency > 300 MHz, Narrow-Band Mode

Figure 50. 1×LO Feedthrough vs. LO Frequency, V<sub>GAIN</sub>, Supply, and Temperature, Fourth-Order Filter at 300 MHz Applied, Wideband Mode

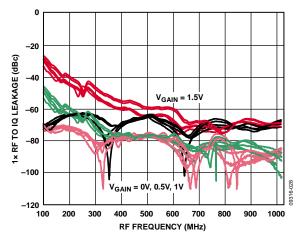

Figure 51. 1× RF Feedthrough vs. RF Input Frequency, V<sub>GAIN</sub>, Supply, and Temperature, Narrow-Band Mode

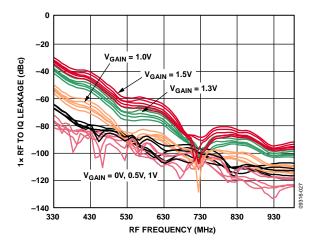

Figure 52. 1× RF Feedthrough vs. RF Input Frequency, V<sub>GAIN</sub>, Supply, and Temperature, Fourth-Order Filter at 300 MHz Applied, Wideband Mode

### THEORY OF OPERATION

#### **OVERVIEW**

The ADRF6850 device can be separated into the following basic building blocks:

- PLL synthesizer and VCO

- Quadrature demodulator

- Variable gain amplifier (VGA)

- I<sup>2</sup>C/SPI interface

Each of these building blocks is described in detail in the sections that follow.

#### **PLL SYNTHESIZER AND VCO**

#### Overview

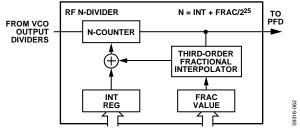

The phase-locked loop (PLL) consists of a fractional-N frequency synthesizer with a 25-bit fixed modulus, allowing a frequency resolution of less than 1 Hz over the entire frequency range. It also has an integrated voltage controlled oscillator (VCO) with a fundamental output frequency ranging from 2000 MHz to 4000 MHz. An RF divider, controlled by Register CR28, Bits[2:0], extends the lower limit of the frequency range to less than 400 MHz. This 400 MHz to 4000 MHz frequency output is then applied to a divide-by-4 quadrature circuit to provide a local oscillator (LO) ranging from 100 MHz to 1000 MHz to the quadrature demodulator.

#### **Reference Input Section**

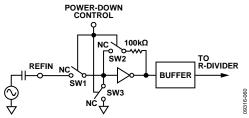

The reference input stage is shown in Figure 53. SW1 and SW2 are normally closed switches. SW3 is normally open. When power-down is initiated, SW3 is closed, and SW1 and SW2 are open. This ensures that there is no loading of the REFIN pin at power-down.

Figure 53. Reference Input Stage

#### Reference Input Path

The on-chip reference frequency doubler allows the input frequency of the reference signal to be doubled. This is useful for increasing the PFD comparison frequency. Making the PFD frequency higher improves the noise performance of the system. Doubling the PFD frequency usually improves the in-band phase noise performance by 3 dBc/Hz.

The 5-bit R-divider allows the input reference frequency ( $REF_{IN}$ ) to be divided down to produce the reference clock to the PFD. Division ratios from 1 to 32 are allowed.

An additional divide-by-2 (÷2) function in the reference input path allows for a greater division range.

Figure 54. Reference Input Path

The PFD frequency equation is

$$f_{PFD} = f_{REFIN} \times [(1+D)/(R \times (1+T))]$$

(1)

where:

$f_{REFIN}$  is the reference input frequency.

*D* is the doubler bit.

*R* is the programmed divide ratio of the binary 5-bit programmable reference divider (1 to 32).

T is the  $\div 2$  bit (0 or 1).

#### RF Fractional-N Divider

The RF fractional-N divider allows a division ratio in the PLL feedback path that can range from 23 to 4095. The relationship between the fractional-N divider and the LO frequency is described in the following section.

#### INT and FRAC Relationship

The integer (INT) and fractional (FRAC) values make it possible to generate output frequencies that are spaced by fractions of the phase frequency detector (PFD) frequency. See the Programming the Correct LO Frequency section for more information.

The LO frequency equation is

$$LO = f_{PFD} \times (INT + (FRAC/2^{25}))/2 \times 2^{RFDIV}$$

(2)

where

LO is the local oscillator frequency.

$f_{PFD}$  is the PFD frequency.

$\it INT$  is the integer component of the required division factor and is controlled by the CR6 and CR7 registers.

FRAC is the fractional component of the required division factor and is controlled by the CR0 to CR3 registers. RFDIV is the setting in Register CR28, Bits[2:0], and controls the setting of a divider at the output of the PLL.

Figure 55. RF Fractional-N Divider

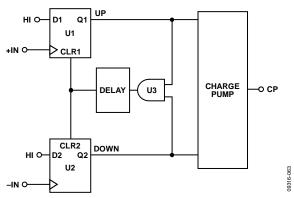

#### Phase Frequency Detector (PFD) and Charge Pump

The PFD takes inputs from the R-divider and the N-counter and produces an output proportional to the phase and frequency difference between them (see Figure 56 for a simplified schematic). The PFD includes a fixed delay element that sets the width of the antibacklash pulse, ensuring that there is no dead zone in the PFD transfer function.

(3)

Figure 56. PFD Simplified Schematic

#### Lock Detect (LDET)

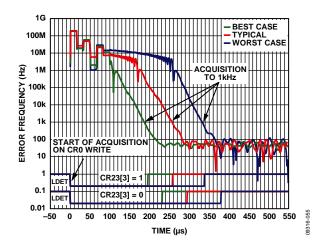

LDET (Pin 40) signals when the PLL has achieved lock to an error frequency of less than 1 kHz. On a write to Register CR0, a new PLL acquisition cycle starts, and the LDET signal goes low. When lock has been achieved, this signal returns high.

#### **Voltage Controlled Oscillator (VCO)**

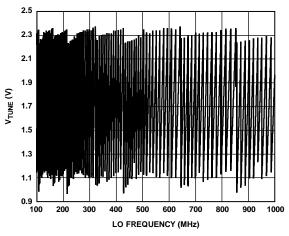

The VCO core in the ADRF6850 consists of three separate VCOs, each with 16 overlapping bands. This configuration of 48 bands allows the VCO frequency range to extend from 2000 MHz to 4000 MHz. The three VCOs are divided externally by a programmable divider (RFDIV controlled by Register CR28, Bits[2:0]). This divider provides divisions of 1, 2, 4, and 8 to ensure that the frequency range is extended from 250 MHz (2000 MHz/8) to 4000 MHz (4000 MHz/1). A lower limit of only 400 MHz is required. A divide-by-4 quadrature circuit provides the full LO frequency range from 100 MHz to 1000 MHz. Figure 57 shows a sweep of V<sub>TUNE</sub> vs. LO frequency demonstrating the three VCOs overlapping and the multiple overlapping bands within each VCO at the LO frequency range of 100 MHz to 1000 MHz. Note that this plot includes the RFDIV divider being incorporated to provide further divisions of the fundamental VCO frequency; thus, each VCO is used on four different occasions throughout the full LO frequency range. The choice of three 16-band VCOs and an RFDIV divider allows the wide frequency range to be covered without large VCO sensitivity (K<sub>VCO</sub>) or resultant poor phase noise and spurious performance.

Figure 57. V<sub>TUNE</sub> vs. LO Frequency

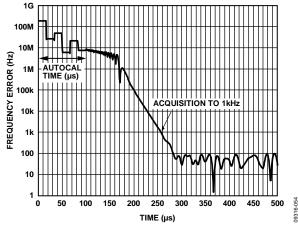

The correct VCO and band are chosen automatically by the VCO and band select circuitry when Register CR0 is updated. This is referred to as autocalibration. The autocalibration time is set by Register CR25.

Autocalibration Time =

$$(BSCDIV \times 24)/PFD$$

where:

BSCDIV = Register CR25, Bits[7:0].

PFD = PFD frequency.

For a PFD frequency of 27 MHz, BSCDIV = 112 to set an autocalibration time of 100  $\mu s$ .

Note that BSCDIV must be recalculated if the PFD frequency is changed. The recommended autocalibration setting is 100  $\mu s$ . During this time, the VCO  $V_{\text{TUNE}}$  is disconnected from the output of the loop filter and is connected to an internal reference voltage. A typical frequency acquisition is shown in Figure 58.

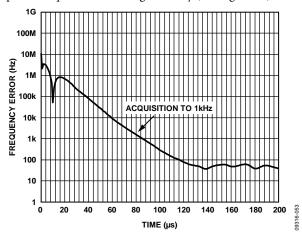

Figure 58. PLL Acquisition

After autocalibration, normal PLL action resumes, and the correct frequency is acquired to within a frequency error of 1 kHz in 260  $\mu$ s typically. For a maximum cumulative step of 100 kHz, autocalibration can be turned off by Register CR24, Bit 0. This enables cumulative PLL acquisitions of 100 kHz or less to occur without the autocalibration procedure, which improves acquisition times significantly (see Figure 59).

Figure 59. PLL Acquisition Without Autocalibration for a 100 kHz Step

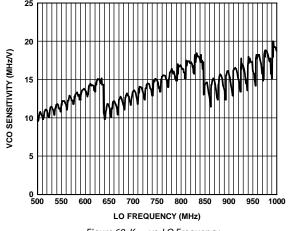

The VCO displays a variation of  $K_{\text{VCO}}$  as  $V_{\text{TUNE}}$  varies within the band and from band to band. Figure 60 shows how the  $K_{\text{VCO}}$  varies across the fundamental LO frequency range from 500 MHz to 1000 MHz. Note that  $K_{\text{VCO}}$  is shown at the LO frequency rather than at the VCO frequency. Figure 60 is useful when calculating the loop filter bandwidth and individual loop filter components using ADISimPLL\*. ADISimPLL is an Analog Devices, Inc., simulator that aids in PLL design, particularly with respect to the loop filter. It reports parameters such as phase noise, integrated phase noise, acquisition time, and so forth for a particular set of input conditions. ADISimPLL can be downloaded from www.analog.com.

Figure 60.  $K_{VCO}$  vs. LO Frequency

#### **Programming the Correct LO Frequency**

There are two steps to programming the correct LO frequency. The user can calculate the N-divider ratio that is required in the PLL and the RFDIV value based on the required LO frequency and PFD frequency.

1. Calculate the value of RFDIV, which is used to program Register CR28, Bits[2:0], from the following lookup table (Table 6). See also Table 24.

Table 6. RFDIV Lookup Table

| LO Frequency (MHz) | RFDIV = Register CR28[2:0] |

|--------------------|----------------------------|

| 500 to 1000        | 000 = divide-by-1          |

| 250 to 500         | 001 = divide-by-2          |

| 125 to 250         | 010 = divide-by-4          |

| 100 to 125         | 011 = divide-by-8          |

Using the following equation, calculate the value of the N-divider:

$$N = (2^{RFDIV} \times 2 \times LO)/(f_{PFD}) \tag{4}$$

where:

N is the N-divider value.

RFDIV is the setting in Register CR28, Bits[2:0].

LO is the local oscillator frequency.

$f_{PFD}$  is the PFD frequency.

This equation is a different representation of Equation 2.

#### **Example to Program the Correct LO Frequency**

Assume that the PFD frequency is 27 MHz and the required LO frequency is 330 MHz.

Step 1. From Table 6,  $2^{RFDIV} = 2$ .

Step 2.  $N = (2 \times 2 \times 330E+6)/(27E+6) = 48.888888889$ .

The N-divider value is composed of integer (INT) and fractional (FRAC) components according to the following equation:

$$N = INT + FRAC/2^{25} \tag{5}$$

INT = 48 and FRAC = 29,826,162.

The appropriate registers must then be programmed according to the register map, ensuring that Register CR0 is the last register to be programmed because this write starts a new PLL acquisition cycle.

#### **QUADRATURE DEMODULATOR**

The quadrature demodulator can be powered up by Register CR29, Bit 0. It has an output filter with narrow-band and wideband modes, which are selected by Register CR29, Bit 3. Wideband mode has a 1 dB filter cutoff of 250 MHz. Narrow-band mode has selectable cutoff filters of 30 MHz through 50 MHz by programming Register CR29, Bits[5:4]. A dc bias voltage of 1.4 V ( $V_{\rm OCM}$ ) can be set internally by setting Register CR29, Bit 6 = 1. To select an external dc bias voltage, set Register CR29, Bit 6 = 0, and drive Pin 7, VOCM, with the requisite external bias voltage.

#### **VARIABLE GAIN AMPLIFIER (VGA)**

The variable gain amplifier (VGA) at the input to the demodulator can be driven either single-ended or differentially.

To drive single-ended, connect Pin 53, RFCM, to Pin 51,  $\overline{\text{RFI}}$ , and decouple both pins to ground with a 10 nF capacitor. Drive the input signal through Pin 55, RFI.

To drive differentially, use a balun with the RFI and  $\overline{\text{RFI}}$  pins driven by the balanced outputs of the balun, and connect the RFCM pin to the common balun output terminal. Decouple RFCM to ground.

The VGA gain range is approximately 60 dB and is achieved by varying the VGAIN voltage from 0 V to 1.5 V. The Typical Performance Characteristics section has more information on the VGA gain performance. A 0 V input on VGAIN sets the VGA gain to 0 dB, whereas a 1.5 V input sets the VGA gain to +60 dB if the VGA Gain Mode Polarity Bit CR30, Bit 2, is set to 0. If the VGA gain mode polarity bit is set to 1, a 0 V input voltage on VGAIN sets the VGA gain to +60 dB, whereas a 1.5 V input sets the VGA gain to 0 dB.

The VGA can be powered down by setting Register CR30, Bit 0, to 0 and can be powered up by setting this same bit to 1.

#### I<sup>2</sup>C INTERFACE

The ADRF6850 supports a 2-wire, I<sup>2</sup>C-compatible serial bus that drives multiple peripherals. The part powers up in I<sup>2</sup>C mode but is not locked in this mode. To remain in I<sup>2</sup>C mode, it is

recommended that the user tie the CS line to either 3.3 V or GND, thus disabling SPI mode.

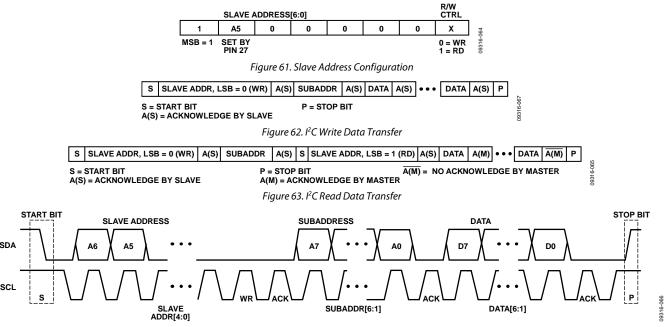

The serial data (SDA) and serial clock (SCL) inputs carry information between any devices that are connected to the bus. Each slave device is recognized by a unique address. The ADRF6850 has two possible 7-bit slave addresses for both read and write operations, 0x78 and 0x58. The MSB of the 7-bit slave address is set to 1. Bit 5 of the slave address is set by the CS pin (Pin 27). Bits[4:0] of the slave address are set to 11000. The slave address consists of the seven MSBs of an 8-bit word. The LSB of the word sets either a read or a write operation (see Figure 61). Logic 1 corresponds to a read operation, whereas Logic 0 corresponds to a write operation.

To control the device on the bus, the following protocol must be followed:

- The master initiates a data transfer by establishing a start condition, defined by a high-to-low transition on SDA while SCL remains high. This indicates that an address/ data stream follows.

- 2. All peripherals respond to the start condition and shift the next eight bits (the 7-bit address and the R/W bit). The bits are transferred from MSB to LSB.

- The peripheral that recognizes the transmitted address responds by pulling the data line low during the ninth clock pulse. This is known as an acknowledge bit.

- 4. All other devices then withdraw from the bus and maintain an idle condition. During the idle condition, the device

- monitors the SDA and SCL lines waiting for the start condition and the correct transmitted address.

- 5. The R/W bit determines the direction of the data. Logic 0 on the LSB of the first byte indicates that the master writes information to the peripheral. Logic 1 on the LSB of the first byte indicates that the master reads information from the peripheral.

The ADRF6850 acts as a standard slave device on the bus. The data on the SDA pin is eight bits long, supporting the 7-bit addresses plus the R/W bit. The ADRF6850 has 34 subaddresses to enable the user-accessible internal registers; therefore, it interprets the first byte as the device address and the second byte as the starting subaddress.

Auto-increment mode is supported, which allows data to be read from or written to the starting subaddress, and each subsequent address, without manually addressing the subsequent subaddress. A data transfer is always terminated by a stop condition. The user can also access any unique subaddress register on a one-by-one basis without updating all registers.

Stop and start conditions can be detected at any stage of the data transfer. If these conditions are asserted out of sequence with normal read and write operations, they cause an immediate jump to the idle condition. If an invalid subaddress is issued by the user, the ADRF6850 does not issue an acknowledge and returns to the idle condition. In a no acknowledge condition, the SDA line is not pulled low on the ninth pulse. See Figure 62 and Figure 63 for sample write and read data transfers, Figure 64 for the timing protocol, and Figure 2 for a more detailed timing diagram.

#### **SPI INTERFACE**

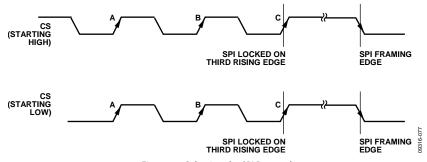

The ADRF6850 supports the SPI protocol; however, the part powers up in I<sup>2</sup>C mode. To select and lock the SPI mode, three pulses must be sent to the CS pin, as shown in Figure 65. When the SPI protocol is locked in, it cannot be unlocked while the device remains powered up. To reset the serial interface, the part must be powered down and powered up again.

#### Serial Interface Selection

The CS pin controls selection of the I<sup>2</sup>C or SPI interface. Figure 65 shows the selection process that is required to lock in the SPI mode. To communicate with the part using the SPI protocol, three pulses must be sent to the CS pin. On the third rising edge, the part selects and locks the SPI protocol. Consistent with most SPI standards, the CS pin must be held low during all SPI communication to the part and held high at all other times.

#### **SPI Serial Interface Functionality**

The SPI serial interface of the ADRF6850 consists of the CS, SDI (SDI/SDA), CLK (CLK/SCL), and SDO pins. CS is used to select the device when more than one device is connected to the serial clock and data lines. CLK is used to clock data in and out

of the part. The SDI line is used to write to the registers. The SDO pin is a dedicated output for the read mode. The part operates in slave mode and requires an externally applied serial clock to the CLK pin. The serial interface is designed to allow the part to be interfaced to systems that provide a serial clock that is synchronized to the serial data.

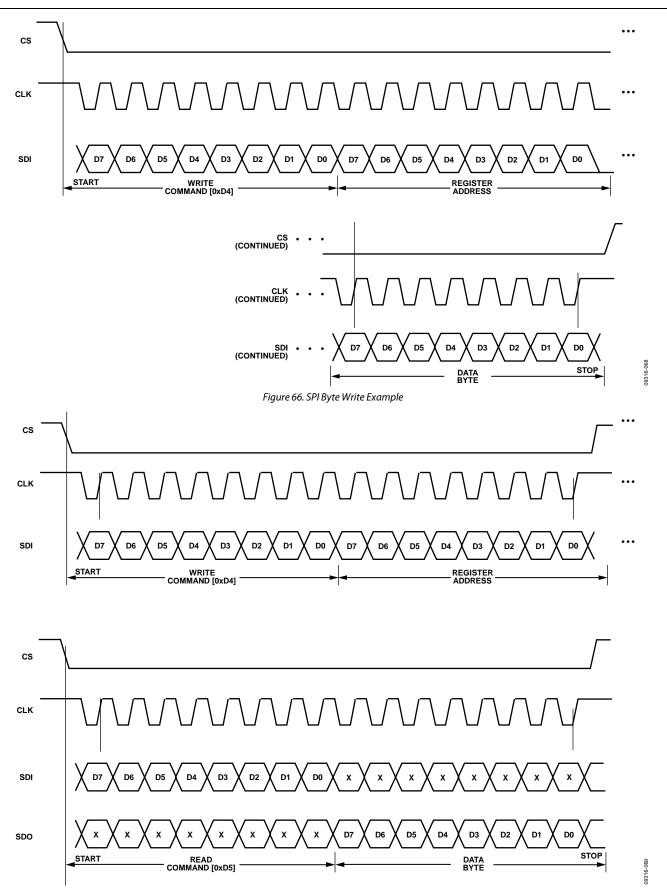

Figure 66 shows an example of a write operation to the ADRF6850. Data is clocked into the registers on the rising edge of CLK using a 24-bit write command. The first eight bits represent the write command (0xD4), the next eight bits are the register address, and the final eight bits are the data to be written to the specific register. Figure 67 shows an example of a read operation. In this example, a shortened 16-bit write command is first used to select the appropriate register for a read operation, the first eight bits representing the write command (0xD4) and the final eight bits representing the specific register. Then the CS line is pulsed low for a second time to retrieve data from the selected register using a 16-bit read command, the first eight bits representing the read command (0xD5) and the final eight bits representing the contents of the register being read. Figure 3 shows the timing for both SPI read and SPI write operations.

Figure 65. Selecting the SPI Protocol

Figure 67. SPI Byte Read Example

#### **PROGRAM MODES**

The ADRF6850 has 34 8-bit registers to allow program control of a number of functions. Only 31 of these registers are writeable. Either an SPI or an I<sup>2</sup>C interface can be used to program the register set. For details about the interfaces and timing, see Figure 61 to Figure 67. The registers are documented in Table 8 to Table 27.

Several settings in the ADRF6850 are double buffered. These settings include the FRAC value, the INT value, the RFDIV value, the 5-bit R-divider value, the reference doubler, the R  $\div 2$  divider, and the charge pump current setting. This means that two events must occur before the part uses a new value for any of the double buffered settings. First, the new value is latched into the device by writing to the appropriate register. Next, a new write must be performed on Register CR0. When Register CR0 is written, a new PLL acquisition occurs.

For example, updating the fractional value involves a write to Register CR3, Register CR2, Register CR1, and Register CR0. Register CR3 should be written to first, followed by Register CR2 and Register CR1 and, finally, Register CR0. The new acquisition begins after the write to Register CR0. Double buffering ensures that the bits written to do not take effect until after the write to Register CR0.

#### 12-Bit Integer Value

Register CR7 and Register CR6 program the integer value (INT) of the feedback division factor (N); see Equation 5 for details. The INT value is a 12-bit number whose MSBs are programmed through Register CR7, Bits[3:0]. The LSBs are programmed through Register CR6, Bits[7:0]. The LO frequency setting is described by Equation 2. An alternative to this equation is provided by Equation 4, which details how to set the N-divider value. Note that these registers are double buffered.

#### 25-Bit Fractional Value

Register CR3 to Register CR0 program the fractional value (FRAC) of the feedback division factor (N); see Equation 5 for details. The FRAC value is a 25-bit number whose MSB is programmed through Register CR3, Bit 0. The LSB is programmed through Register CR0, Bit 0. The LO frequency setting is described by Equation 2. Again, an alternative to this equation is described by Equation 4, which details how to set the N-divider value. Note that these registers are double buffered.

#### **RFDIV Value**

The RFDIV value is dependent on the value of the LO frequency. The RFDIV value can be selected from the list in Table 6. Apply the selected RFDIV value to Equation 4, together with the LO frequency and PFD frequency values, to calculate the correct N-divider value.

#### Reference Input Path

The reference input path consists of a reference doubler, a 5-bit frequency divider, and a divide-by-2 function (see Figure 54). The doubler is programmed through Register CR10, Bit 5. The

5-bit divider is enabled by programming Register CR5, Bit 4; and the division ratio is programmed through Register CR10, Bits[4:0]. The R  $\div$ 2 divider is programmed through Register CR10, Bit 6. Note that these registers are double buffered.

#### **Charge Pump Current**

Register CR9, Bits[7:4], set the charge pump current setting. With an R<sub>SET</sub> value of 4.7 k $\Omega$ , the maximum charge pump current is 5 mA. The following equation applies:

$$I_{CP max} = 23.5/R_{SET} \tag{6}$$

The charge pump current has 16 settings from 325 µA to 5 mA.

#### Power-Down/Power-Up Control Bits

The four programmable power-up and power-down control bits are as follows:

- Register CR12, Bit 2. Master power control bit for the PLL, including the VCO. This bit is normally set to a default value of 0 to power up the PLL.

- Register CR27, Bit 2. Controls the LO monitor outputs, LOMON and LOMON. The default is 0 when the monitor outputs are powered down. Setting this bit to 1 powers up the monitor outputs to one of -6 dBm, -12 dBm, -18 dBm, or -24 dBm, as controlled by Register CR27, Bits[1:0].

- Register CR29, Bit 0. Controls the quadrature demodulator power. The default is 0, which powers down the demodulator.

Write a 1 to this bit to power up the demodulator.

- Register CR30, Bit 0. This bit controls the VGA power and must be set to a 1 to power up the VGA.

#### Lock Detect (LDET)

Lock detect is enabled by setting Register CR23, Bit 4, to 1. Register CR23, Bit 3, in conjunction with Register CR14, Bit 7, sets the number of up/down pulses generated by the PFD before lock detect is declared by the LDET pin returning high. The options are 2048 pulses, 3072 pulses, and 4096 pulses.

The default setting is 3072 pulses, which is selected by programming Register CR23, Bit 3, to 0, and Register CR14, Bit 7, to 0. A more aggressive setting of 2048 is selected when Register CR23, Bit 3, is set to 1 and Register CR14, Bit 7, is set to 0. This improves the lock detect time by 50  $\mu s$  (for a PFD frequency of 27 MHz). Note, however, that it does not affect the acquisition time to an error frequency of 1 kHz. A setting of 4096 pulses is selected when Register CR14, Bit 7, is set to 1. For best operation, set Register CR23, Bit 2 to 0. This bit sets up the PFD up/down pulses to a coarse or low precision setting.

#### **Baseband VOCM Reference**

Register CR29, Bit 6, selects whether the common-mode reference for the baseband outputs is internal or external. When the baseband outputs are ac-coupled, then the internal reference must be selected by setting Register CR29, Bit 6, to 1, and by grounding Pin 7, VOCM.

When the baseband outputs are dc-coupled, it is likely that an external bias is needed unless the internal dc bias provided is

within a suitable range to match the specification of the followon device. This is accomplished by setting Register CR29, Bit 6, to 0, and driving Pin 7, VOCM, with the requisite external bias voltage.

#### Narrow-Band and Wideband Filter Mode

By default, the second-order low-pass filter in the output buffers of the baseband output signal paths is selected, and the baseband outputs are in narrow-band mode. By setting Register CR29, Bits[5:4], this filter can be set to a cutoff frequency of 50 MHz, 43 MHz, 37 MHz, or 30 MHz. By setting Register CR29, Bit 3, to 1, this filter is bypassed and wideband mode is selected.

**Table 7. Baseband Filter Settings**

| CR29[5:4] | Filter Cutoff Frequency (MHz) |  |

|-----------|-------------------------------|--|

| 00        | 50                            |  |

| 01        | 43                            |  |

| 10        | 37                            |  |

| 11        | 30                            |  |

#### **VGA Gain Mode Polarity**

The polarity of the VGA gain is set by programming Bit 2 of Register CR30. By setting Register CR30, Bit 2, to 0, a positive gain slope is selected where  $V_{GAIN}=0$  V sets the VGA gain to be 0 dB, and  $V_{GAIN}=1.5$  V sets the VGA gain to be 60 dB. By setting Register CR30, Bit 2, to 1, a negative gain slope is selected.

# REGISTER MAP REGISTER MAP SUMMARY

**Table 8. Register Map Summary**

| Register Address (Hex) | Register Name | Туре       | Description                            |

|------------------------|---------------|------------|----------------------------------------|

| 0x00                   | CR0           | Read/write | Fractional Word 4                      |

| 0x01                   | CR1           | Read/write | Fractional Word 3                      |

| 0x02                   | CR2           | Read/write | Fractional Word 2                      |

| 0x03                   | CR3           | Read/write | Fractional Word 1                      |

| 0x04                   | CR4           | Read/write | Reserved                               |

| 0x05                   | CR5           | Read/write | Reference 5-bit, R-divider enable      |

| 0x06                   | CR6           | Read/write | Integer Word 2                         |

| 0x07                   | CR7           | Read/write | Integer Word 1                         |

| 0x08                   | CR8           | Read/write | Reserved                               |

| 0x09                   | CR9           | Read/write | Charge pump current setting            |

| 0x0A                   | CR10          | Read/write | Reference frequency control            |

| 0x0B                   | CR11          | Read/write | Reserved                               |

| 0x0C                   | CR12          | Read/write | PLL power-up                           |

| 0x0D                   | CR13          | Read/write | Reserved                               |

| 0x0E                   | CR14          | Read/write | Lock Detector Control 2                |

| 0x0F                   | CR15          | Read/write | Reserved                               |

| 0x10                   | CR16          | Read/write | Reserved                               |

| 0x11                   | CR17          | Read/write | Reserved                               |

| 0x12                   | CR18          | Read/write | Reserved                               |

| 0x13                   | CR19          | Read/write | Reserved                               |

| 0x14                   | CR20          | Read/write | Reserved                               |

| 0x15                   | CR21          | Read/write | Reserved                               |

| 0x16                   | CR22          | Read/write | Reserved                               |

| 0x17                   | CR23          | Read/write | Lock Detector Control 1                |

| 0x18                   | CR24          | Read/write | Autocalibration                        |

| 0x19                   | CR25          | Read/write | Autocalibration timer                  |

| 0x1A                   | CR26          | Read/write | Reserved                               |

| 0x1B                   | CR27          | Read/write | LO monitor output                      |

| 0x1C                   | CR28          | Read/write | LO selection                           |

| 0x1D                   | CR29          | Read/write | Demodulator power and filter selection |

| 0x1E                   | CR30          | Read/write | VGA                                    |

| 0x1F                   | CR31          | Read only  | Reserved                               |

| 0x20                   | CR32          | Read only  | Reserved                               |

| 0x21                   | CR33          | Read only  | Revision code                          |

#### **REGISTER BIT DESCRIPTIONS**

Table 9. Register CR0 (Address 0x00), Fractional Word 4

| Bit | Description                           |

|-----|---------------------------------------|

| 7   | Fractional Word F7 <sup>1</sup>       |

| 6   | Fractional Word F6 <sup>1</sup>       |

| 5   | Fractional Word F5 <sup>1</sup>       |

| 4   | Fractional Word F4 <sup>1</sup>       |

| 3   | Fractional Word F3 <sup>1</sup>       |

| 2   | Fractional Word F2 <sup>1</sup>       |

| 1   | Fractional Word F1 <sup>1</sup>       |

| 0   | Fractional Word F0 (LSB) <sup>1</sup> |

|     | -                                     |

<sup>&</sup>lt;sup>1</sup> Double buffered. Load on the write to Register CR0.

Table 10. Register CR1 (Address 0x01), Fractional Word 3

| Bit | Description                      |

|-----|----------------------------------|

| 7   | Fractional Word F15 <sup>1</sup> |

| 6   | Fractional Word F14 <sup>1</sup> |

| 5   | Fractional Word F13 <sup>1</sup> |

| 4   | Fractional Word F12 <sup>1</sup> |

| 3   | Fractional Word F11 <sup>1</sup> |

| 2   | Fractional Word F10 <sup>1</sup> |

| 1   | Fractional Word F9 <sup>1</sup>  |

| 0   | Fractional Word F8 <sup>1</sup>  |

|     |                                  |

<sup>&</sup>lt;sup>1</sup> Double buffered. Load on the write to Register CR0.

Table 11. Register CR2 (Address 0x02), Fractional Word 2

| 14010 11. 10650001 0102 (11441000 0102), 11400101141 11 014 2 |                                  |

|---------------------------------------------------------------|----------------------------------|

| Bit                                                           | Description                      |

| 7                                                             | Fractional Word F23 <sup>1</sup> |

| 6                                                             | Fractional Word F22 <sup>1</sup> |

| 5                                                             | Fractional Word F21 <sup>1</sup> |

| 4                                                             | Fractional Word F20 <sup>1</sup> |

| 3                                                             | Fractional Word F19 <sup>1</sup> |

| 2                                                             | Fractional Word F18 <sup>1</sup> |

| 1                                                             | Fractional Word F17 <sup>1</sup> |

| 0                                                             | Fractional Word F16 <sup>1</sup> |

<sup>&</sup>lt;sup>1</sup> Double buffered. Load on the write to Register CR0.

Table 12. Register CR3 (Address 0x03), Fractional Word 1

| 8                                      |

|----------------------------------------|

| Description                            |

| Reserved                               |

| Fractional Word F24 (MSB) <sup>1</sup> |

|                                        |

<sup>&</sup>lt;sup>1</sup> Double buffered. Load on the write to Register CR0.

Table 13. Register CR5 (Address 0x05), Reference 5-Bit, R-Divider Enable

| Bit | Description                           |

|-----|---------------------------------------|

| 7   | Reserved                              |

| 6   | Reserved                              |

| 5   | Reserved                              |

| 4   | 5-bit R-divider enable <sup>1</sup>   |

|     | 0 = disable 5-bit R-divider (default) |

|     | 1 = enable 5-bit R-divider            |

| 3   | Reserved                              |

| 2   | Reserved                              |

| 1   | Reserved                              |

| 0   | Reserved                              |

<sup>&</sup>lt;sup>1</sup> Double buffered. Load on the write to Register CR0.

Table 14. Register CR6 (Address 0x06), Integer Word 2

| Bit | Description                  |

|-----|------------------------------|

| 7   | Integer Word N7 <sup>1</sup> |

| 6   | Integer Word N6 <sup>1</sup> |

| 5   | Integer Word N5 <sup>1</sup> |

| 4   | Integer Word N4 <sup>1</sup> |

| 3   | Integer Word N3 <sup>1</sup> |

| 2   | Integer Word N2 <sup>1</sup> |

| 1   | Integer Word N1 <sup>1</sup> |

| 0   | Integer Word N0 <sup>1</sup> |

<sup>&</sup>lt;sup>1</sup> Double buffered. Load on the write to Register CR0.

Table 15. Register CR7 (Address 0x07), Integer Word 1

| Bit   | Description                   |

|-------|-------------------------------|

| [7:4] | MUXOUT control                |

|       | 0000 = tristate               |

|       | 0001 = logic high             |

|       | 0010 = logic low              |

|       | 1101 = RCLK/2                 |

|       | 1110 = NCLK/2                 |

| 3     | Integer Word N11 <sup>1</sup> |

| 2     | Integer Word N10 <sup>1</sup> |

| 1     | Integer Word N9 <sup>1</sup>  |

| 0     | Integer Word N8 <sup>1</sup>  |

<sup>&</sup>lt;sup>1</sup> Double buffered. Load on the write to Register CR0.

Table 16. Register CR9 (Address 0x09), Charge Pump Current Setting

| Current Setting |                                  |

|-----------------|----------------------------------|

| Bit             | Description                      |

| [7:4]           | Charge pump current <sup>1</sup> |

|                 | 0000 = 0.31 mA (default)         |

|                 | 0001 = 0.63 mA                   |

|                 | 0010 = 0.94 mA                   |

|                 | 0011 = 1.25 mA                   |

|                 | 0100 = 1.57 mA                   |

|                 | 0101 = 1.88 mA                   |

|                 | 0110 = 2.19 mA                   |

|                 | 0111 = 2.50 mA                   |

|                 | 1000 = 2.81 mA                   |

|                 | 1001 = 3.13 mA                   |

|                 | 1010 = 3.44 mA                   |

|                 | 1011 = 3.75 mA                   |

|                 | 1100 = 4.06 mA                   |

|                 | 1101 = 4.38 mA                   |

|                 | 1110 = 4.69 mA                   |

|                 | 1111 = 5.00 mA                   |

| 3               | Reserved                         |

| 2               | Reserved                         |

| 1               | Reserved                         |

| 0               | Reserved                         |

<sup>&</sup>lt;sup>1</sup> Double buffered. Load on the write to Register CR0.

Table 17. Register CR10 (Address 0x0A), Reference Frequency Control

| Trequency Control |                                           |

|-------------------|-------------------------------------------|

| Bit               | Description                               |

| 7                 | Reserved <sup>1</sup>                     |

| 6                 | R divide-by-2 divider enable <sup>1</sup> |

|                   | 0 = bypass R divide-by-2 divider          |

|                   | 1 = enable R divide-by-2 divider          |

| 5                 | R-doubler enable <sup>1</sup>             |

|                   | 0 = disable doubler (default)             |

|                   | 1 = enable doubler                        |

| [4:0]             | 5-bit R-divider setting <sup>1</sup>      |

|                   | 00000 = divide by 32 (default)            |

|                   | 00001 = divide by 1                       |

|                   | 00010 = divide by 2                       |

|                   |                                           |

|                   | 11110 = divide by 30                      |

|                   | 11111 = divide by 31                      |

$<sup>^{\</sup>rm 1}$  Double buffered. Load on the write to Register CR0.

Table 18. Register CR12 (Address 0x0C), PLL Power-Up

| Bit | Description                |

|-----|----------------------------|

| 7   | Reserved                   |

| 6   | Reserved                   |

| 5   | Reserved                   |