# Analog Devices Welcomes Hittite Microwave Corporation

NO CONTENT ON THE ATTACHED DOCUMENT HAS CHANGED

www.hittite.com

www.analog.com

## HMC1023\* Product Page Quick Links

Last Content Update: 11/01/2016

## Comparable Parts

View a parametric search of comparable parts

## Evaluation Kits

• HMC1023LP5 Evaluation Board

## Documentation 🖵

#### Data Sheet

• HMC1023 Data Sheet

## Reference Materials

#### **Quality Documentation**

• Semiconductor Qualification Test Report: BiCMOS-A (QTR: 2013-00235)

## Design Resources 🖵

- HMC1023 Material Declaration

- PCN-PDN Information

- Quality And Reliability

- Symbols and Footprints

## Discussions 🖵

View all HMC1023 EngineerZone Discussions

## Sample and Buy

Visit the product page to see pricing options

## Technical Support

Submit a technical question or find your regional support number

<sup>\*</sup> This page was dynamically generated by Analog Devices, Inc. and inserted into this data sheet. Note: Dynamic changes to the content on this page does not constitute a change to the revision number of the product data sheet. This content may be frequently modified.

THIS PAGE INTENTIONALLY LEFT BLANK

#### **Typical Applications**

The HMC1023LP5E is ideal for:

- Baseband filtering before or after data converters for point-to-point fixed wireless and cellular infrastructure transceivers

- · Software defined radio applications

- · Anti-aliasing and reconstruction filters

- · Test and measurement equipment

- ADC driver applications

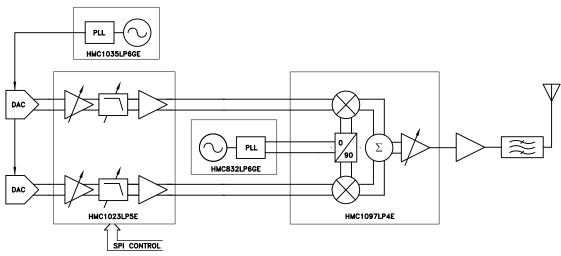

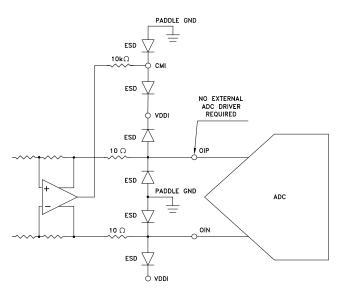

#### **Functional Diagram**

# HMC1023LP5E

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### Features

Low Noise Figure: 10 dB High linearity: In-Band Output IP3 > +30 dBm In-Band Output IP2 > +60 dBm Pre-programmed and/or Programmable Bandwidth: 5 MHz to 72 MHz. (Please see HMC1023LP5E Ordering Information) Exceptional 3 dB Bandwidth Accuracy: ±2.5% Programmable Gain: 0 or 10 dB Integrated ADC Driver Amplifier 6th order Butterworth Magnitude & Phase Response Automatic Filter Calibration Externally Controlled Common Mode Output Level Filter Bypass Option Pin & Register Compatible to HMC900LP5E Read/Write Serial Port Interface (SPI) 32 Lead 5x5 mm SMT Package 25 mm<sup>2</sup>

#### **General Description**

The HMC1023LP5E is a 6th order, programmable bandwidth, fully calibrated, dual low pass filter. It features programmable 0 or 10 dB gain and supports arbitrary bandwidths from 5 MHz to 72 MHz. When calibrated, the bandwidth is accurate to +/-2.5%. Built-in filter bypass option enables wider bandwidths while maintaining programmed gain and common mode control settings.

Integrated ADC driver, programmable input impedance, and adjustable output common mode voltage from 0.9 V to 3 V with 2 Vppd signal, or lower than 0.9 V common mode with lower signal swing enables simple interface while achieving maximum performance. Programmable bias settings enable performance/power dissipation trade-off optimized for each application.

Filter calibration is accomplished with any reference clock rate from 20 to 80 MHz. One time programmable (OTP) memory offers unsurpassed flexibility allowing the user "set and forget" parameters like gain and bandwidth setting.

Housed in a compact 5x5 mm SMT QFN package, the HMC1023LP5E is pin and register compatible to the existing HMC900LP5E programmable bandwidth Low Pass Filter. It requires minimal external components and provides a low cost alternative to more complicated switched discrete filter architectures.

The 6th order Butterworth transfer function delivers superior stop band rejection while maintaining both a flat passband and minimal group delay variation.

# ROHS V

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

### **Table 1. Electrical Specifications**

$T_{a} = +25^{\circ}C$ , VDDI, VDDQ, VDDCAL, VDDBG, DVDD = 5V +/-5%, GND = 0V, 400  $\Omega$  load unless otherwise stated.

| Parameter                                            | Conditions                                                                                          | Min.     | Тур.       | Max.  | Units      |

|------------------------------------------------------|-----------------------------------------------------------------------------------------------------|----------|------------|-------|------------|

| Analog Performance                                   |                                                                                                     |          |            |       |            |

| Passband Gain <sup>[1]</sup>                         | min gain setting<br>max gain setting                                                                |          | 0<br>10    |       | dB<br>dB   |

| 3 dB corner frequency (fc)                           | [1]                                                                                                 | 5        |            | 72    | MHz        |

| Programmable to any frequency in this range          | Bypass mode                                                                                         | 75       | 100        |       | MHz        |

|                                                      | uncalibrated                                                                                        |          |            | ± 20  | %          |

| 3 dB corner frequency variation                      | calibrated                                                                                          |          | ±2.5       | ± 3.5 | %          |

| 3 dB corner frequency variation vs temperature       | over -40°C to +85°C                                                                                 |          |            | ±0.03 | % / °C     |

| Max passband gain error <sup>[2]</sup>               | vs ideal 6th order LPF H(s)                                                                         |          |            | ±0.5  | dB         |

| Max passband group delay variation                   | at 0.1 dB BW (~0.73 fc)                                                                             |          |            | 0.250 |            |

| (group delay * 3 dB frequency fc )                   | at 0.5 dB BW (~0.83 fc)                                                                             |          |            | 0.350 |            |

| e.g. for 1.0 dB BW of 40 MHz (fc ~ 44.9 MHz):        | at 1.0 dB BW (~ 0.89 fc)                                                                            |          |            | 0.400 |            |

| max group delay variation = 0.400/ 44.9 MHz = 8.9 ns | at 3.0 dB BW (at fc)                                                                                |          |            | 0.400 |            |

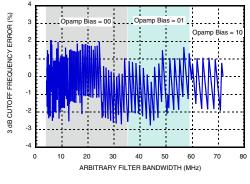

|                                                      | min gain, fc = 5 MHz                                                                                |          | 22         |       | nV/rtHz    |

| Output Noise (f = 1 MHz)                             | min gain, fc = 28 MHz                                                                               |          | 22         |       | nV/rtHz    |

|                                                      | max gain fc = 5 MHz                                                                                 |          | 25         |       | nV/rtHz    |

|                                                      | max gain, fc = 28 MHz                                                                               |          | 25         |       | nV/rtHz    |

|                                                      | min gain, fc = 5 MHz                                                                                |          | 8          |       | nV/rtHz    |

| Output noise (f > 10*fc)                             | max gain, fc = 5 MHz                                                                                |          | 8          |       | nV/rtHz    |

|                                                      | min gain fc = 28 MHz                                                                                |          | 8          |       | nV/rtHz    |

|                                                      | max gain, fc = 28 MHz                                                                               |          | 8          |       | nV/rtHz    |

| Noise Figure (100 $\Omega$ source)                   | min gain                                                                                            |          | 25         |       | dB         |

|                                                      | max gain                                                                                            |          | 17         |       | dB         |

| Noise Figure (1 kΩ source)                           | min gain                                                                                            |          | 19         |       | dB         |

|                                                      | max gain                                                                                            |          | 12         |       | dB         |

| Input referred Passband IM3                          | half scale tones at 0.8fc and<br>0.6fc<br>fc = 20 MHz<br>fc = 72 MHz <sup>[2]</sup>                 |          | -60<br>-50 |       | dBc<br>dBc |

| Input referred Out of Band IM3                       | half scale tones at 1.2fc and<br>1.6fc. IM3 product at 0.8fc<br>fc = 20 MHz<br>fc = 72 MHz $^{[2]}$ |          | -60<br>-50 |       | dBc<br>dBc |

| Input referred Out of Band IM3                       | half scale tones at 2fc and 3fc.<br>IM3 product at 0.5fc<br>fc = 20  MHz<br>fc = 72  MHz            |          | -50<br>-45 |       | dBc<br>dBc |

| Output IP3 (inband)                                  | half scale tones at 0.8fc and<br>0.6fc<br>fc = 20 MHz<br>fc = 72 MHz                                | 25<br>17 | 30<br>20   |       | dBm<br>dBm |

| Output IP3 (out of band)                             | half scale tones at 1.2fc and<br>1.6fc. IM3 product at 0.8fc<br>fc = 20 MHz<br>fc = 72 MHz $^{[2]}$ | 25<br>17 | 30<br>20   |       | dBm<br>dBm |

| Output IP3 (out of band)                             | half scale tones at 2fc and 3fc. IM3 product at fc fc = 20 MHz fc = 72 MHz^{[2]}                    | 25<br>17 | 30<br>20   |       | dBm<br>dBm |

| Output IP2 (inband)                                  | half scale tones at 0.8fc and<br>0.6fc IM2 product at 0.2fc<br>fc = 20 MHz<br>fc = 72 MHz $^{[2]}$  | 55<br>55 | 60<br>60   |       | dBm<br>dBm |

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### Electrical Specifications, TA = +25°C (Continued)

| Parameter                               | Parameter Conditions                                         |           | Тур.                | Max.    | Units   |

|-----------------------------------------|--------------------------------------------------------------|-----------|---------------------|---------|---------|

| Output IP2 (out of band) <sup>[2]</sup> | half scale tones at 1.2fc and<br>1.6fc. IM2 product at 0.4fc | 60        | 65                  |         | dBm     |

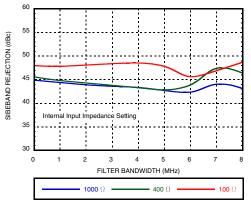

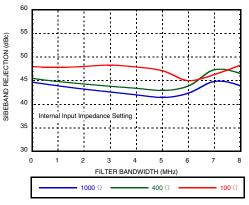

| Sideband Suppression (Uncalibrated)     | complex signal measured at<br>0.8fc vs -0.8fc                | 35        | 45                  |         | dB      |

| I/Q Channel Balance                     |                                                              |           |                     |         |         |

| magnitude                               |                                                              |           | 0.04                |         | dB<br>o |

| phase                                   |                                                              |           | 0.5                 |         | -       |

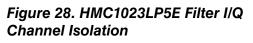

| I/Q Channel Isolation                   |                                                              | 60        | 80                  |         | dB      |

| Analog I/O                              |                                                              | 1         |                     |         |         |

| Differential Input Impedance            | Programmable                                                 |           | 1000 /<br>400 / 100 |         | Ω       |

| Full Scale Differential Input           | min gain                                                     |           |                     | 2       | Vppd    |

| (400 Ω Differential Load)               | max gain                                                     |           |                     | 0.613   | Vppd    |

| Full Scale Differential Input           | min gain                                                     |           |                     | 0.5     | Vppd    |

| (100 Ω Differential Load)               | max gain                                                     |           |                     | 0.156   | Vppd    |

| Input Common Mode Voltage Range         | 1                                                            |           |                     | 4       | V       |

| Full Scale Differential Output          | 400 $\Omega$ Differential Load                               |           |                     | 2       | Vppd    |

| Full Scale Differential Output          | 100 $\Omega$ Differential Load                               |           |                     | 0.5     | Vppd    |

| Output Voltage Range                    |                                                              | 0.5       |                     | Vdd-0.5 | V       |

| Output Common Mode Voltage Range        |                                                              | 0.9       |                     | 3       | V       |

| Digital I/O                             |                                                              |           | -                   |         |         |

| CALCK Frequency                         | Use doubler mode for clocks between 20 MHz and 40 MHz        | 20        | 40                  | 80      | MHz     |

| CALCK Duty Cycle                        |                                                              | 40        | 50                  | 60      | %       |

| SCLK Frequency                          |                                                              |           | 20                  | 30      | MHz     |

| Digital Input Low Level (VIL)           |                                                              |           |                     | 0.4     | V       |

| Digital Input High Level (VIH)          |                                                              | 1.5       |                     |         | V       |

| Digital Output Low Level (VOL)          |                                                              |           |                     | 0.4     | V       |

| Digital Output High Level (VOH)         |                                                              | Vdd - 0.4 |                     |         |         |

| Power Supply                            | Analog & Digital Supplies                                    | 4.75      | 5                   | 5.25    | V       |

| Supply Current                          | Dependent on Bias                                            |           | 240                 |         | mA      |

| Power on Reset                          |                                                              |           | 250                 |         | us      |

[1] The attenuation of the filter transfer function can be calculated directly at any frequency f as: attenuation =  $10*\log_{10}(1+(f/f_0)^{1/2+6})$ , where  $f_0$  is the 3 dB bandwidth or corner frequency for the filter. Similarly, for a given maximum attenuation and 3 dB bandwidth,  $f_0$ , the frequency at which the attenuation is achieved can be calculated as:  $f=(10^{(4ttenuation/10)} - 1)^{(1/(2+6))} * f_0$ . Note that for a 6th order Butterworth filter the 1 dB bandwidth is at ~89% of the filter bandwidth and 0.5 dB bandwidth is at 84% of the filter bandwidth.

[2] Specified distortion is measured with opamp\_bias (Reg 02h[1:0]) settings recommended in Table 9. .

#### Table 2. Test Conditions

| Unless otherwise specified, the following test conditions were used |                          |  |  |

|---------------------------------------------------------------------|--------------------------|--|--|

| Parameter                                                           | Condition                |  |  |

| Temperature                                                         | +25 °C                   |  |  |

| Reg 06h Setting                                                     | 150                      |  |  |

| Gain Setting                                                        | 0 dB                     |  |  |

| bias settings (opamp_bias Reg 02h[1:0]/ drvr_bias Reg 02h[3:2])     | 00/10                    |  |  |

| Input Signal Level                                                  | 2 Vppd                   |  |  |

| Input/Output Common Mode Level                                      | 2V                       |  |  |

| Output Load                                                         | 200 Ω / Output           |  |  |

| Supply                                                              | Analog: +5V, Digital +5V |  |  |

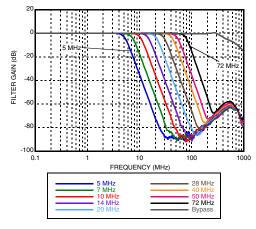

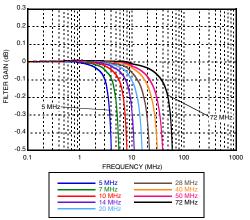

# Figure 1. Filter Attenuation (all Bandwidths) [1]

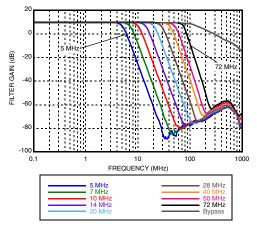

Figure 3. Filter Attenuation, 10dB Gain [1]

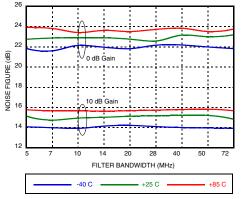

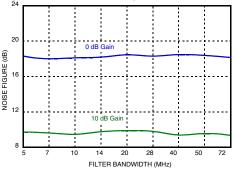

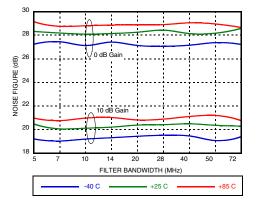

Figure 5. Noise Figure, 100  $\Omega$  Source Impedance, 1 k $\Omega$  Impedance Selected <sup>[2]</sup>

## HMC1023LP5E

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

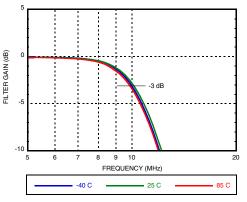

### Figure 2. Filter Passband Gain Response

Figure 4. Filter 3 dB Cutoff vs Temperature, 10 MHz Bandwidth

Figure 6. Noise Figure, 1 k $\Omega$  Source Impedance, 1 k $\Omega$  Impedance Selected <sup>[2]</sup>

IF / BASEBAND PROCESSING - SMT

[1] Degrated stop-band rejection at frequencies > 100 MHz caused by the test fixture. [2] 1 k $\Omega$  input impedance into the HMC1023LP5E selected by writing Reg 02h[10]=0 and Reg 01h[9] = 0.

## Figure 7. Noise Figure, 1 k $\Omega$ Source Impedance, 100 $\Omega$ Impedance Selected

Figure 9. Uncalibrated Sideband Rejection, 0 dB Gain

#### [3] 100 $\Omega$ source impedance used, and input impedanceo of HMC1023LP5E set to 1 k $\Omega$

[4] 100  $\Omega$  input impedance into the HMC1023LP5E selected by writing Reg 02h[10]=1.

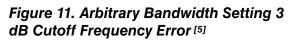

[5] Used recommended OpAmp bias settings (Reg 02h[1:0]) in Table 9.

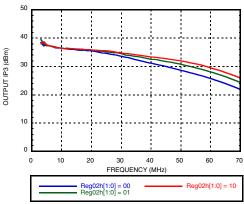

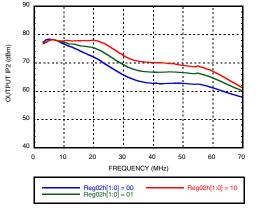

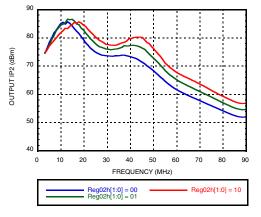

[6] OIP3 and OIP2 measured from 100  $\Omega$  differential source into 400  $\Omega$  differential load. Used recommended OpAmp bias settings (Reg 02h[1:0]) in Table 9. OIP3 and OIP2 measurements can be translated from dBm into dBVrms as follows: IPx [dBVrms] = IPx [dBm] -4 dB.

For price, delivery and to place orders: Hittite Microwave Corporation, 2 Elizabeth Drive, Chelmsford, MA 01824 Phone: 978-250-3343 Fax: 978-250-3373 Order On-line at www.hittite.com Application Support: Phone: 978-250-3343 or apps@hittite.com

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### Figure 8. Filter Output Noise [3]

## Figure 10. UncalibratedSidebandRejection, 10 dB Gain

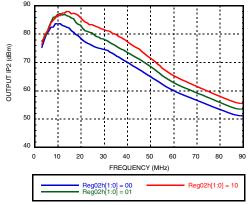

Figure 12. Output IP3, 72 MHz Bandwidth Setting, 0 dB Gain [6]

90

Rea02h[1:0] = 10

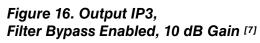

#### Figure 13. Output IP2, 72 MHz Bandwidth Setting, 0 dB Gain [7]

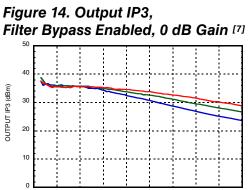

Figure 15. Output IP2, Filter Bypass Mode Enabled, 0 dB Gain [7]

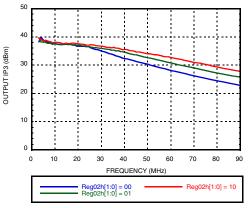

Figure 17. Output IP2, Filter Bypass Enabled, 10 dB Gain [7]

10 40 50 60 20 30 70 80 FREQUENCY (MHz)

Reg02h[1:0] =00 Reg02h[1:0] = 01

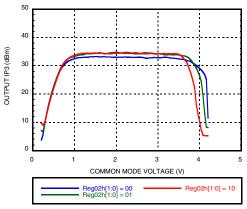

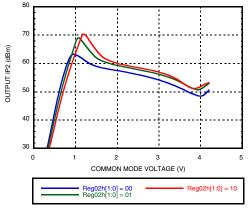

Figure 18. Output IP3 vs Output Common Mode Voltage, 30 MHz Input [8]

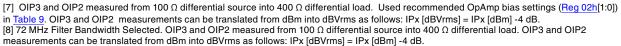

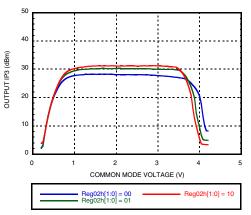

## Figure 19. Output IP2 vs Output Common Mode Voltage, 30 MHz Input <sup>[9]</sup>

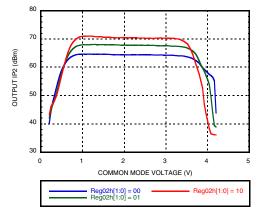

Figure 21. Output IP2 vs Output Common Mode Voltage, 50 MHz Input [9]

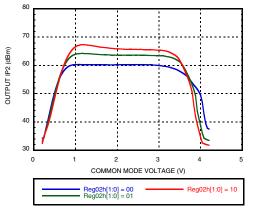

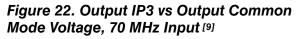

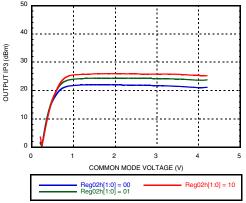

Figure 23. Output IP2 vs Output Common Mode Voltage, 70 MHz Input <sup>[9]</sup>

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

Figure 20. Output IP3 vs Output Common Mode Voltage, 50 MHz Input <sup>[9]</sup>

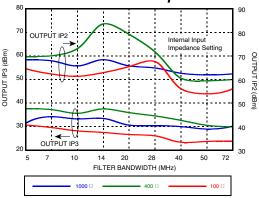

Figure 24. In-band Output IP3 & Output IP2 vs Filter Bandwidth & Impedance [10]

[9] 72 MHz Filter Bandwidth selected. OIP3 and OIP2 measured from 100  $\Omega$  differential source into 400  $\Omega$  differential load. OIP3 and OIP2 measurements can be translated from dBm into dBVrms as follows: IPx [dBVrms] = IPx [dBm] -4 dB [10] OIP3 and OIP2 measured from 100  $\Omega$  differential source into 400  $\Omega$  differential load. Used recommended OpAmp bias settings (Reg 02h[1:0]) in Table 9. OIP3 and OIP2 measurements can be translated from dBm into dBVrms as follows: IPx [dBVrms] = IPx [dBm] -4 dB.

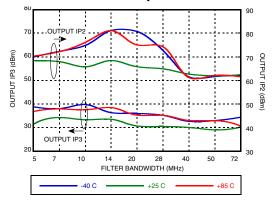

## Figure 25. In-band Output IP3 & Output IP2 vs Bandwidth & Temperature [11]

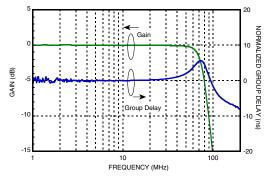

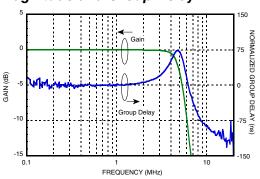

Figure 27. 72 MHz Bandwidth Filter Magnitude and Group Delay

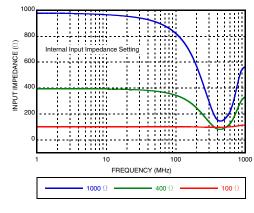

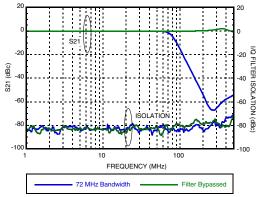

Figure 29. Input Impedance

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

Figure 26. 5 MHz Bandwidth Filter Magnitude and Group Delay

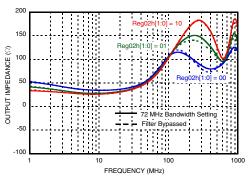

Figure 30. Output Impedance

[11] OIP3 and OIP2 measured from 100  $\Omega$  differential source into 400  $\Omega$  differential load. Used recommended OpAmp bias settings (Reg 02h[1:0]) in Table 9. OIP3 and OIP2 measurements can be translated from dBm into dBVrms as follows: IPx [dBVrms] = IPx [dBm] -4 dB

## ROHSV EARTH FRIEND

### Table 3. Absolute Maximum Ratings

| Nominal 5V Supply to GND<br>VDDCAL, VDDI, VDDQ, VDDBG,<br>DVDD       | -0.3 to 5.5 V         |

|----------------------------------------------------------------------|-----------------------|

| Common Mode Inputs Pins<br>(CMI, CMQ)                                | -0.3 to 5.5 V         |

| Input and Output Pins<br>IIP, IIN, IQP, IQN, OIP, OIN, OQP,<br>OQN   | -0.3 to 5.5 V         |

| Digital Pins<br>SEN, SDI, SCK, SDO, CALCK<br>SDO min load impedance  | -0.3 to 5.5 V<br>1 kΩ |

| Operating Ambient Temperature<br>Range                               | -40 to +85 °C         |

| Storage Temperature                                                  | -65 to + 150 °C       |

| Maximum Junction Temperature                                         | 150 °C                |

| Thermal Resistance (Θ <sub>JC</sub> )<br>(junction to ground paddle) | 10 °C/W               |

| Reflow Soldering<br>Peak Temperature<br>Time at Peak Temperature     | 260 °C<br>40 μs       |

| ESD Sensitivity (HBM)                                                | 1 kV Class 1C         |

## HMC1023LP5E

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

Stresses above those listed under Absolute Maximum Ratings may cause permanent damage to the device. This is a stress rating only; functional operation of the device at these or any other conditions above those indicated in the operational section of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

#### Table 4. Recommended Operating Conditions

| Parameter                      | Condition   | Min. | Тур. | Max. | Units |

|--------------------------------|-------------|------|------|------|-------|

| Temperature                    | Temperature |      |      |      |       |

| Junction Temperature           |             |      |      | 125  | °C    |

| Ambient Temperature            |             | -40  |      | 85   | °C    |

| Supply Voltage                 |             |      |      |      |       |

| VDDCAL, VDDI, VDDQ, VDDBG,DVDD |             | 4.75 | 5    | 5.25 | V     |

[1] Layout design guidelines set out in Qualification Test Report are strongly recommended.

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

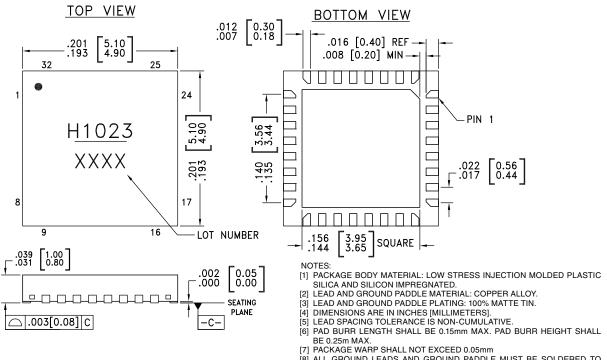

### **Outline Drawing**

[3] ALL GROUND LEADS AND GROUND PADDLE MUST BE SOLDERED TO PCB RF GOUND.

[9] REFER TO HITTITE APPLICATION NOTE FOR SUGGESTED PCB LAND PATTERN.

#### Table 5. Package Information

| Part Number | Package Body Material                              | Lead Finish   | MSL Rating <sup>[1]</sup> | Package Marking <sup>[2]</sup> |

|-------------|----------------------------------------------------|---------------|---------------------------|--------------------------------|

| HMC1023LP5E | RoHS-compliant Low Stress Injection Molded Plastic | 100% matte Sn | MSL1                      | <u>H1023</u><br>XXXX           |

[1] Max peak reflow temperature of 260 °C

[2] 4-Digit lot number XXXX

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### Table 6. Pin Descriptions

| Pin Number                      | Function      | Description                                                                                                                                    | Interface Schematic    |

|---------------------------------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| 1, 3, 8 - 10,<br>17, 24, 25, 32 | N/C           | The pins are not connected internally; however, all data<br>shown herein was measured with these pins connected to<br>RF/DC ground externally. |                        |

| 2, 4                            | VDDQ          | Quadrature (Q) Channel 5V Supply.<br>Must be locally decoupled to GND                                                                          |                        |

| 5                               | СМQ           | Quadrature (Q) channel output common mode level                                                                                                |                        |

| 6, 7                            | OQP, OQN      | Quadrature (Q) channel positive and negative differential outputs                                                                              |                        |

| 11                              | CALCK         | Calibration clock input                                                                                                                        |                        |

| 12, 14, 15                      | SCK, SDI, SEN | SPI Data clock, data input and enable respectively.                                                                                            | SDI<br>SEN<br>SCK      |

| 13                              | SDO           | SPI Data Output                                                                                                                                |                        |

| 16                              | DVDD          | Digital 5V Supply. Must be locally decoupled to GND.                                                                                           |                        |

| 18, 19                          | OIN, OIP      | Inphase (I) channel negative and positive differential outputs respectively                                                                    | VDD<br>OOP<br>OQN<br>= |

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### Table 6. Pin Descriptions (Continued)

| Pin Number | Function | Description                                                                   | Interface Schematic |

|------------|----------|-------------------------------------------------------------------------------|---------------------|

| 20         | СМІ      | Inphase (I) channel output common mode level                                  |                     |

| 21, 23     | VDDi     | Inphase (I) Channel 5V Supply. Must be locally decoupled to GND               |                     |

| 22         | VDDCAL   | Calibration 5V Supply. Must be locally decoupled to GND                       |                     |

| 26, 27     | IIP, IIN | Inphase (I) channel positive and negative differential inputs respectively    |                     |

| 28         | VDDBG    | Bias 5V Supply. Must be locally decoupled to GND.                             |                     |

| 29         | VBG      | 1.2V Bandgap output (testing only)                                            | VBG OF              |

| 30, 31     | IQN, IQP | Quadrature (Q) channel negative and positive differential inputs respectively |                     |

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

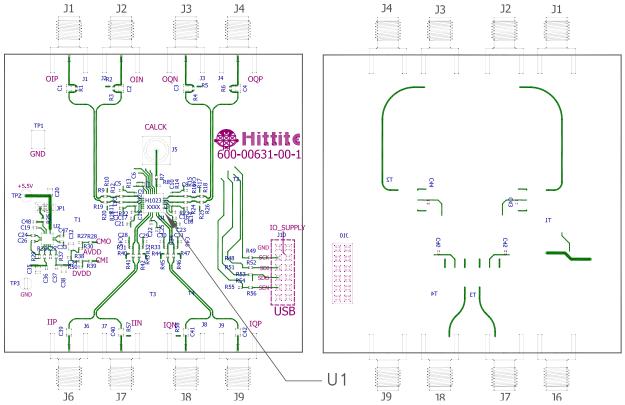

## **Evaluation PCB**

The circuit board used in the application should use RF circuit design techniques. Signal lines should have 50 Ohms impedance while the package ground leads and exposed paddle should be connected directly to the ground plane similar to that shown. A sufficient number of via holes should be used to connect the top and bottom ground planes. The evaluation circuit board shown is available from Hittite upon request.

| Item           | Contents                                                                                                                                                                 | Part Number        |

|----------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------|

| Evaluation Kit | HMC1023LP5E Evaluation PCB<br>USB Interface Board<br>6' USB A Male to USB B Female Cable<br>CD ROM (Contains User Manual, Evaluation PCB Schematic, Evaluation Software) | EKIT01-HMC1023LP5E |

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### **Evaluation PCB Schematic**

To view <u>Evaluation PCB Schematic</u> please visit <u>www.hittite.com</u> and choose HMC1023LP5E from the "Search by Part Number" pull down menu to view the product splash page.

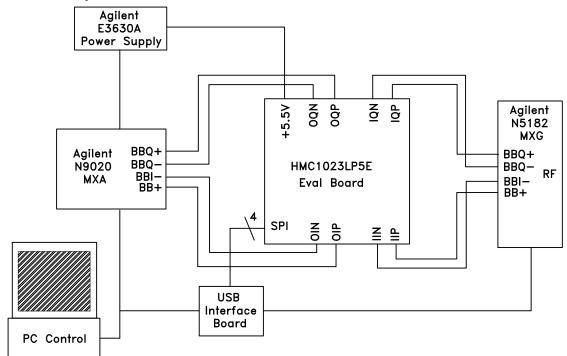

#### **Evaluation Setup**

Figure 31. Characterization Setup Block Diagram

# ROHS

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### HMC1023LP5E Usage Information

The HMC1023LP5E addresses different filter applications such as fixed frequency or variable bandwidth implementations dependent on the part selected (see <u>HMC1023LP5E Ordering Information</u>) and the control provided to the HMC1023LP5E. These modes provide the user with different filter options depending on the system implementation.

An overview of these trade-offs are shown below.

| Function                                                                                                    | Unprogrammed<br>HMC1023LP5E-00000                                                      | Pre-programmed<br>HMC1023LP5E-BBBGL                                   | SPI<br>Req'd | CALCK<br>Req'd | Comments                                                                                                                                                                                                                                                                                                                                                                         |                                                  |

|-------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------|-----------------------------------------------------------------------|--------------|----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

| Fixed Bandwidth Filter                                                                                      | Yes                                                                                    | Yes                                                                   |              |                |                                                                                                                                                                                                                                                                                                                                                                                  |                                                  |

| Default Bandwidth and Gain<br>setting after Power On Reset<br>(POR)                                         | Default Bandwidth<br>and Gain as defined<br>by register defaults.<br>(5 MHz /0dB gain) | Bandwidth and<br>Gain as defined by<br>pre-programming at<br>factory. | No           | No             | Pre-programmed gain and bandwidth<br>are defined when ordering the part. See<br>HMC1023LP5E Ordering Information.                                                                                                                                                                                                                                                                |                                                  |

| Typical Corner Frequency Ac-<br>curacy at Default Bandwidth                                                 | +/- 20 %                                                                               | +/- 2.5 %                                                             |              |                | Accuracy is with respect to bandwidth after POR.                                                                                                                                                                                                                                                                                                                                 |                                                  |

| Variable Bandwidth Filter                                                                                   | Yes                                                                                    | Yes                                                                   |              |                | Full control over HMC1023LP5E requires access via the digital serial port (SPI).                                                                                                                                                                                                                                                                                                 |                                                  |

| Default Bandwidth and Gain<br>setting after Power On Reset<br>(POR)                                         | Default Bandwidth<br>and Gain as defined<br>by register defaults.<br>(5 MHz /0dB gain) | Bandwidth and<br>Gain as defined by<br>pre-programming at<br>factory. |              |                | Pre-programmed gain and bandwidth are defined when ordering the part. See HMC1023LP5E Ordering Information.                                                                                                                                                                                                                                                                      |                                                  |

| Typical Corner Frequency Ac-<br>curacy at Default Bandwidth                                                 | +/- 20 %                                                                               | +/- 2.5 %                                                             | Yes          | Yes No         | Yes No                                                                                                                                                                                                                                                                                                                                                                           | Accuracy is with respect to bandwidth after POR. |

| Typical Corner Frequency<br>Accuracy at all other Band-<br>widths                                           | +/- 20 %                                                                               | +/- 5.0 %                                                             |              |                | Accuracy is with respect to the desired<br>bandwidth.<br>See "Filter Bandwidth Setting" for informa-<br>tion regarding changing the bandwidth<br>after when calibration is not possible.                                                                                                                                                                                         |                                                  |

| Variable Bandwidth Filter<br>(with ability to execute User<br>Calibration to calibrate filter<br>bandwidth) | Yes                                                                                    | Yes                                                                   |              |                | Full control over HMC1023LP5E requires<br>access via the digital serial port (SPI).<br>Filter calibration requires valid calibration<br>clock (via CALCK pin). See <u>"RC Calibra-<br/>tion Circuit"</u>                                                                                                                                                                         |                                                  |

| Default Bandwidth and Gain<br>setting after Power On Reset<br>(POR)                                         | Default Bandwidth<br>and Gain as defined<br>by register defaults.<br>(5 MHz /0dB gain) | Bandwidth and<br>Gain as defined by<br>pre-programming at<br>factory. |              |                | Pre-programmed gain and bandwidth<br>are defined when ordering the part. See<br>"HMC1023LP5E Ordering Information 20".                                                                                                                                                                                                                                                           |                                                  |

| Typical Corner Frequency<br>Accuracy after POR (before<br>User Calibration)                                 | +/- 20 %                                                                               | +/- 2.5 %                                                             |              |                | Accuracy is with respect to bandwidth after POR.                                                                                                                                                                                                                                                                                                                                 |                                                  |

| Typical Corner Frequency Ac-<br>curacy after User Calibration<br>at <b>calibrated</b> bandwidth             | +/- 2.5 %                                                                              | +/- 2.5 %                                                             | Yes Yes      | Yes            | Accuracy is with respect to calibrated<br>bandwidth.<br>User Calibration requires access to the<br>HMC1023LP5E via the digital serial port<br>(SPI) and requires a valid calibration clock<br>(via CALCK pin).                                                                                                                                                                   |                                                  |

| Typical Corner Frequency Ac-<br>curacy after User Calibration<br>at <b>non calibrated</b> bandwidths        | +/- 5.0 %                                                                              | +/- 5.0 %                                                             |              |                | Accuracy is with respect to the desired<br>bandwidth.<br>User Calibration requires access to the<br>HMC1023LP5E via the digital serial port<br>(SPI) and requires a valid calibration clock<br>(via pin CALCK).<br>See <u>"Filter Bandwidth Setting"</u> for informa-<br>tion regarding changing the bandwidth<br>after calibration when further calibration is<br>not possible. |                                                  |

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### HMC1023LP5E Application Information

Accurate, arbitrary, user defined bandwidths, programmable gain, and flexible programmable IO interface provide the HMC1023LP5E with unmatched flexibility. This flexibility together with market leading performance, in terms of linearity, Noise Figure, and bandwidth accuracy enable a universal solution capable of supporting numerous radio standards, frequencies, and/or bandwidths with a single hardware platform.

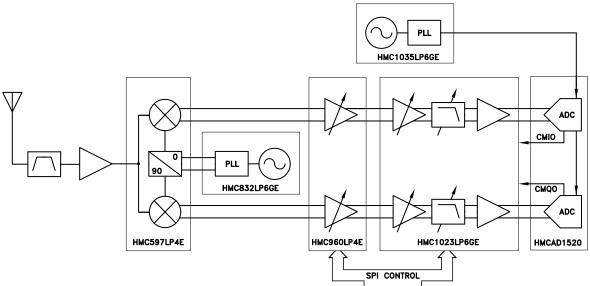

The HMC1023LP5E is relevant in both transmitter and receiver applications (Figure 32 and Figure 33). In transmitter applications the HMC1023LP5E serves as an anti-aliasing filter that rejects Digital-to-Analog Converter aliases and ensures the desired transmitted spectral mask. In receiver applications the HMC1023LP5E serves as an Analog-to-Digital converter driver, an anti-aliasing filter, and a blocker rejection filter all in one.

In both transmitter and receiver applications, excellent 6th order butterworth filter response with virtually no pass-band ripple and exceptional +/-2.5% bandwidth accuracy enables simple modem designs that need not utilize complex adaptive equalization schemes to compensate for filter ripple and group delay variation.

In such applications, together with Hittite's Wideband PLLVCOs, the HMC1023LP5E enables truly wideband multistandard multi-carrier hardware platforms, software configurable to the demands of each particular application.

Compared to discrete filters, the HMC1023LP5E saves valuable board area and cost. Typically higher order discrete filters are required to achieve comparable rejection as the HMC1023LP5E due to the inherent error tolerances in the value of each individual component. In addition, discrete filters are fixed in bandwidth, typically requiring multiple band specific hardware versions that tends to increase the cost relative to supporting only one hardware version for all bands supported by the HMC1023LP5E.

The HMC1023LP5E overcomes the matching problem that discrete filters present with respect to baseband signal processing. The matched dual filter paths provide excellent gain and phase balance between the two channels eliminating the image problem which results from poor matching.

Figure 32. Typical Receive Path Block Diagram showing HMC1023LP5E

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

Figure 33. Typical Transmit Path Block DiagramHMC1023LP5E Ordering Information

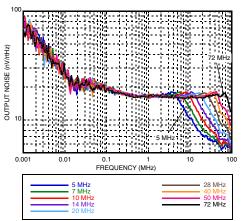

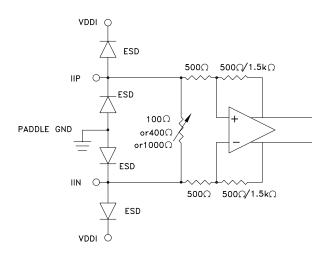

#### Input Interface

Input stage features a programmable input impedance (100  $\Omega$  / 400  $\Omega$  / 1 k $\Omega$  differential, or 50  $\Omega$  / 200  $\Omega$  / 500  $\Omega$  single-ended) that is configured via <u>Reg 01h[9]</u> and <u>Reg 02h[10]</u>. Programmable impedance enables a configurable interface, tailored to the requirements of the component driving the HMC1023LP5E. It enables maximum Noise Figure (NF) performance regardless of the device driving the HMC1023LP5E. NF of the HMC1023LP5E with various input impedance settings is provided in <u>Figure 5</u>, <u>Figure 6</u> and <u>Figure 7</u>. Actual input impedance over frequency is shown in <u>Figure 29</u>.

Wide input common mode voltage range further simplifies input interface. The HMC1023LP5E does not require any configuration for input common mode voltage as long as the part is operated within the specifications outlined in Table  $\underline{1}$ .

The HMC1023LP5E does not require any specific impedance at the input. Input interface should be designed according to the demands of the device driving the HMC1023LP5E, while programmable input impedance of the HMC1023LP5E permits optimal matching and/or NF performance. Both ac-coupled and dc-coupled interfaces are supported at the input.

#### **Output Interface**

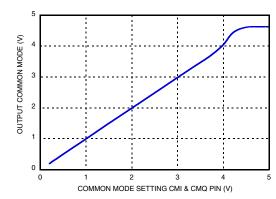

Output common mode voltage of the HMC1023LP5E is set via CMI and CMQ pins for the in-phase and quadrature outputs respectively. Wide output common mode voltage range simplifies interface with numerous devices. The HMC1023LP5E's 0.9 V to 3 V output common mode voltage range is specified with a 2 Vppd output signal swing. Lower common mode output voltage is supported with lower signal swing. The key requirement is that the signal swing in combination with common mode voltage does not go below 0.5 V single-ended. Hence, as an example a 0.7 V output common mode voltage level is supported with 0.8 Vppd signal swing. Figure 18 to Figure 23 show the effect of output common mode voltage on linearity performance (Output IP2 & Output IP3) of the HMC1023LP5E. The plots indicate that even for a large output signal swing of 2 Vppd, the HMC1023LP5E typically maintains high linearity performance below 0.9 V nominal output common mode limit. Figure 34 shows measured output common mode voltage as a function of input common mode voltage follows the settings on CMI & CMQ pins well beyond the rated 0.9 V to 3 V.

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

Figure 34. Output vs. Input Common Mode Voltage

Output impedance of the HMC1023LP5E is nominally 10  $\Omega$  single-ended or 20  $\Omega$  differential. The HMC1023LP5E does not require any special impedance matching at the output. The output of the HMC1023LP5E is an OpAmp driver capable of driving small and large loads alike. Output interface of the HMC1023LP5E should be designed according to the demands of the device the HMC1023LP5E is driving.

to the demands of the device the HMC1023LP5E is driving.

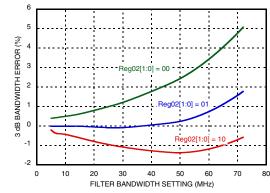

#### Linearity, Bandwidth Accuracy, and Current Consumption

As shown in Figure 25, the HMC1023LP5E is a high linearity device, typically exhibiting in excess of 30 dBm Output IP3, and over 60 dBm Output IP2 throughout the operating range of the part. To maintain maximum performance as measured by linearity (Output IP2 and Output IP3) and bandwidth accuracy it is recommended to use OpAmp bias settings (Reg 02h[1:0]) outlined in Table 9. Table 9 shows that higher OpAmp bias setting, and thereby higher current consumption is required to maintain maximum linearity performance as well as bandwidth accuracy ( < 2.5% bandwidth error) at bandwidth settings  $\geq$  10 MHz. Figure 12 to Figure 23 show the effect of OpAmp bias setting (Reg 02h[1:0]) on linearity (OIP2 and OIP3) performance of the HMC1023LP5E.

| Table 9. TIMCT025EF JE DIAS TAble |                                                           |                                                                                      |                                                    |  |  |  |  |  |

|-----------------------------------|-----------------------------------------------------------|--------------------------------------------------------------------------------------|----------------------------------------------------|--|--|--|--|--|

| Coarse Bandwidth (MHz)            | Coarse<br>Bandwidth<br>Setting<br>( <u>Reg 02h[</u> 9:6]) | Recommended<br>OpAmp Bias<br>Setting For Best<br>Performance<br><u>Reg 02h[</u> 1:0] | HMC1023LP5E<br>Typical Current<br>Consumption (mA) |  |  |  |  |  |

| 5                                 | 0000                                                      | 00                                                                                   | 172                                                |  |  |  |  |  |

| 7                                 | 0001                                                      | 00                                                                                   | 172                                                |  |  |  |  |  |

| 10                                | 0010                                                      | 00                                                                                   | 172                                                |  |  |  |  |  |

| 14                                | 0011                                                      | 01                                                                                   | 227                                                |  |  |  |  |  |

| 20                                | 0100                                                      | 01                                                                                   | 227                                                |  |  |  |  |  |

| 28                                | 0101                                                      | 01                                                                                   | 227                                                |  |  |  |  |  |

| 40                                | 0110                                                      | 01                                                                                   | 227                                                |  |  |  |  |  |

| 50                                | 0111                                                      | 01                                                                                   | 227                                                |  |  |  |  |  |

| 72                                | 1000                                                      | 10                                                                                   | 260                                                |  |  |  |  |  |

| Tabla Q  | HMC1023L          | DEE Bias | Tabla |

|----------|-------------------|----------|-------|

| Taple 9. | <b>HIVICIUZ3L</b> | PSE Blas |       |

Figure 12 to Figure 23 show that the higher OpAmp bias setting typically increases linearity OIP3 & OIP2 by 5 to 10 dB at high bandwidth setting. However, they also show that the HMC1023LP5E maintains excellent linearity performance (~60 dBm OIP2 & ~30 dBm OIP3), even at minimum OpAmp bias setting (Reg 02h[1:0] = 0).

<u>Figure 35</u> shows typical calibrated filter bandwidth error (accuracy) vs OpAmp bias setting (<u>Reg 02h[1:0]</u>). It shows that higher OpAmp bias is required at filter bandwidth settings  $\geq$  10 MHz in order to achieve  $\leq$  +/-2.5 % bandwidth accuracy. However it also shows that excellent bandwidth accuracy ( $\leq$  +/-5.5 %) is achievable at all filter bandwidth settings with even the lowest OpAmp bias setting (Reg 02h[1:0]).

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

Figure 35. Calibrated HMC1023LP5E Bandwidth Error vs. OpAmp Bias (Reg 02h[1:0])

Hence for applications in which current consumption is an important performance criteria it is possible to reduce the HMC1023LP5E current consumption by ~90 mA or ~450 mW at a cost of ~5 dB lower linearity performance and lower, but still excellent bandwidth accuracy performance of  $\leq$  +/-5.5 %.

#### Non-Volatile One Time Programmable (OTP) Memory

The HMC1023LP5E includes OTP (One Time Programmable) memory that enables the user to program the default configuration of the HMC1023LP5E on start-up. The programmable settings are shown in <u>Reg 0Ah</u> they include:

- Bandwidth

- Filter bypass enable

- Gain

- Input impedance (100 Ω or 1kΩ differential), 400 Ω differential is also available but can only be set via SPI interface.

- OpAmp bias

- Driver bias

Once the OTP memory is programmed, by default on power-up, the HMC1023LP5E enters the state programmed in OTP memory. However, even after the OTP memory is programmed HMC1023LP5E retains full functionality, and can be re-configured to any other state via Serial Port Interface. Therefore the configuration burned in OTP memory is only a default configuration of the HMC1023LP5E on power up, which can be changed to any user defined configuration after power-up using the SPI.

Detailed instructions on programming the OTP memory are provided in <u>"One Time Programmable Memory (OTP)</u>" section.

#### Filter Programming & Calibration

Detailed description of filter bandwidth programming is provided in <u>"Filter Bandwidth Setting"</u> section. To achieve the rated accuracy, each HMC1023LP5E device requires calibration at least once. Once calibrated, the settings are always valid for that particular HMC1023LP5E.

Filter calibration requires an input clock. More information about calibration clock and calibration procedure is provided in <u>"RC Calibration Circuit"</u> section. The calibration clock is only required during calibration. It is not required for the operation of the HMC1023LP5E.

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### HMC1023LP5E Ordering Information

The HMC1023LP5E is available as product that is either un-programmed or pre-programmed. Programming is available to a variety of filter bandwidths (defined in this context as the 3dB bandwidth).

Other options available for pre-programmed product include the single path gain and bias state as described below. Gain and bias settings are described in Reg 02h.

When placing an order for the HMC1023LP5E please observe the following guidelines.

- 1. To order the un-programmed standard part please place order using the part number HMC1023LP5E-000000.

- 2. To order a pre-programmed HMC1023LP5E please determine the part number as described below and then contact Hittite Sales at sales@hittite.com or call (978) 250-3343.

2.1 Minimum quantity order for the pre-programmed HMC1023LP5E-BBBGLL is 500 pieces.

- 3. Pre-Programmed part number description: HMC1023LP5E-BBBGL.

- 3.1 'BBB' represents a three digit number from the Table 10 that represents the desired bandwidth setting (3 dB bandwidth) from 5 MHz to 72 MHz (for example BBB = 050 specifies a 5 MHz corner frequency).

- 3.2 'G' represents the gain setting of either 0 dB (G = 0) or 10 dB (G = 1).

- 3.3 'LL' represents the OpAmp bias setting of the HMC1023LP5E. For more information please see "Linearity. Bandwidth Accuracy, and Current Consumption" section.

For example, to order the HMC1023LP5E pre-programmed for 72 MHz 3 dB frequency, 10 dB gain, and standard low '00' OpAmp bias setting please specify part number HMC1023LP5E-720100.

| Table 10. Custom Part Frequency Options                           |     |     |     |     |     |     |     |     |     |

|-------------------------------------------------------------------|-----|-----|-----|-----|-----|-----|-----|-----|-----|

| BBB frequency for custom part (actual frequency is BBB x 0.1 MHz) |     |     |     |     |     |     |     |     |     |

| 050                                                               | 069 | 093 | 128 | 171 | 229 | 307 | 411 | 554 | 709 |

| 052                                                               | 070 | 095 | 131 | 175 | 235 | 315 | 422 | 565 | 720 |

| 053                                                               | 071 | 098 | 134 | 179 | 240 | 322 | 432 | 576 |     |

| 054                                                               | 073 | 100 | 137 | 180 | 246 | 330 | 443 | 587 |     |

| 056                                                               | 075 | 102 | 140 | 184 | 253 | 338 | 454 | 598 |     |

| 057                                                               | 076 | 105 | 141 | 188 | 259 | 347 | 465 | 609 |     |

| 058                                                               | 078 | 108 | 144 | 193 | 265 | 355 | 476 | 621 |     |

| 060                                                               | 080 | 110 | 148 | 198 | 272 | 364 | 488 | 632 |     |

| 061                                                               | 082 | 113 | 151 | 203 | 278 | 373 | 500 | 643 |     |

| 063                                                               | 084 | 116 | 155 | 208 | 280 | 382 | 510 | 654 |     |

| 064                                                               | 086 | 119 | 159 | 213 | 285 | 392 | 521 | 665 |     |

| 066                                                               | 088 | 121 | 163 | 218 | 292 | 400 | 532 | 676 |     |

| 068                                                               | 091 | 124 | 167 | 224 | 300 | 401 | 543 | 687 |     |

#### able 10 Overlage Dagt Free surgers Orthoge

For additional information or inquiries please contact Hittite Apps Support at apps@hittite.com.

[1] The Output IP2 and Output IP3 for the two linearity settings are shown in Figure 13 and Figure 14. High linearity setting improves linearity for bandwidths greater than 30 MHz at the cost of increased current consumption (additional 25 mA).

# ROHS

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### Theory of Operation

The HMC1023LP5E consists of the following functional blocks

- 1. Input Gain Stage

- 2. 6th Order Butterworth LPF

- 3. Output Driver

- 4. RC Calibration Circuit

- 5. Bias Circuit

- 6. One Time Programmable Memory

- 7. Serial Port interface

- 8. Built in Self Test (RC-BIST)

#### Input Gain Stage

The HMC1023LP5E input stage consists of a programmable 0 or 10 dB gain stage which in turn drives the 6th order LPF. A block diagram showing input impedance of the I channel is presented below, Q channel is similar.

Figure 36. Input Stage Block Diagram

#### 6<sup>th</sup> Order Low Pass Filter (LPF)

The LPF allows for coarse bandwidth tuning by varying the capacitive elements in the filter, while the fine bandwidth tuning is accomplished by varying the resistors. Note that all Op-Amps in the LPF are class AB for minimum power consumption in the filter while maintaining excellent distortion characteristics even in large signal swing conditions.

The attenuation due to the LPF can be calculated for any frequency, f, from the standard Butterworth transfer function for a 6th order filter. Specifically the attenuation of the filter, in dB, can be calculated as:

attenuation =  $10*\log_{10}(1+(f/f_c)^{(2*6)})$

where  $f_c$  is the 3 dB bandwidth or corner frequency for the filter.

Note that for a 6th order Butterworth filter the 1 dB bandwidth is 90% of  $f_c$ , and the 0.3 dB bandwidth is 80% of  $f_c$ .

#### Filter Bandwidth Setting

The 3 dB bandwidth of the HMC1023LP5E is programmable anywhere within the range from 5 MHz to 72 MHz. When calibrated, filter bandwidth is accurate to within  $\pm$ -2.5% of the programmed bandwidth, if not calibrated it is accurate to within  $\pm$ -20% of the programmed bandwidth.

The calibration of HMC1023LP5E is required to be executed only once for each individual HMC1023LP5E. Once

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

executed, if the calibration settings are remembered, they are always valid for a specific HMC1023LP5E.

Please note that best bandwidth accuracy is achieved when the HMC1023LP5E is calibrated at its typical operating temperature. Programmed bandwidth varies 0.03 %/°C.

#### Filter Bandwidth Configuration

The HMC1023LP5E bandwidths are configured using Coarse Bandwidth Settings in <u>Reg 02h[9:6]</u>, and Fine Bandwidth Settings in <u>Reg 03h[3:0]</u>. Coarse Bandwidth Settings select from a choice of coarse bandwidth options in <u>Table 11</u>, and the Fine Bandwidth Settings further refine the selected coarse bandwidth settings according to <u>Table 12</u>.

In all cases, once the <u>Reg 02h[9:6]</u> and/or <u>Reg 03h[3:0]</u> have been programmed it is required to set <u>Reg 01h[4]=1</u> in order to instruct the HMC1023LP5E to use provided settings.

After calculating the settings for a given device they can be stored permanently in the non volatile memory (See <u>"One</u> <u>Time Programmable Memory (OTP)</u>" for more information).

#### Uncalibrated Bandwidth Configuration

When not calibrated, the coarse bandwidth is selected via <u>Reg 02h[9:6]</u> according to the desired coarse bandwidth setting in <u>Table 11</u>.

Example: to select bandwidth of 14 MHz simply write  $\underline{Reg \ 02h}[9:6] = '0011'b$ , then write  $\underline{Reg \ 01h}[4]=1$  to instruct the HMC1023LP5E to use provided settings.

If desired, it is possible to tune to an arbitrary bandwidth choice not provided in <u>Table 11</u>. In that case nearest coarse bandwidth is selected via <u>Reg 02h[9:6]</u> according to <u>Table 11</u>, and the bandwidth is further refined via <u>Reg 03h[3:0]</u> according to <u>Table 12</u>, where

**Reg 03h**[3:0] =

$$f_{WANTED} / f_{BW_norm_coarse_typ}$$

,

where  $f_{BW_norm\_coarse\_typ}$  corresponds to the selected typical coarse bandwidth setting in <u>Table 11</u>, programmed via <u>Reg</u> <u>02h[</u>9:6].

Example: to select the bandwidth of 13 MHz, select the closest typical value in Table 11, and program Reg 02h[9:6] accordingly (ie. Reg 02h[9:6] = '0011'b), then Reg 03h[3:0] =  $f_{WANTED} / f_{BW_norm\_coarse\_typ} = 13$  MHz/14 MHz = 0.9286. Hence from Table 12, Reg 03h[3:0] = '0100'. Finally, write Reg 01h[4]=1 to instruct the HMC1023LP5E to use provided settings.

In all cases, when uncalibrated the bandwidth is accurate to within +/-20% of the programmed bandwidth.

#### Calibrated Bandwidth Configuration

The calibration of HMC1023LP5E is required to be executed only once for each individual HMC1023LP5E. Once executed, if the calibration settings are remembered, they are always valid for that specific HMC1023LP5E. Detailed instructions of how to calibrate the HMC1023LP5E are available in <u>RC Calibration Circuit</u> section.

When calibrated the programmed bandwidth is accurate to +/-2.5%. The HMC1023LP5E calibrated bandwidth can be programmed in two ways, Automatic or Manual.

The automatic calibration supports only Coarse Bandwidth Settings in <u>Table 11</u>, whereas the Manual calibration supports arbitrary bandwidths from 5 MHz to 72 MHz. In both cases the bandwidth is accurate to within +/-2.5%.

#### Calibrated Automatic Bandwidth Configuration

In Automatic bandwidth setting the user simply selects from a choice of Coarse Bandwidths in <u>Table 11</u> via <u>Reg</u> <u>02h[9:6]</u>, and the HMC1023LP5E automatically programs <u>Reg 03h[3:0]</u> during calibration so that the selected bandwidth is accurate to within +/-2.5%.

Example: to select bandwidth of 14 MHz simply write  $\underline{Reg \ 02h}[9:6] = '0011'b$ , then write  $\underline{Reg \ 01h}[4]=1$  to instruct the HMC1023LP5E to use provided settings.

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

#### Calibrated Manual Bandwidth Configuration

Manual bandwidth setting enables arbitrary user defined bandwidths between 5 MHz and 72 MHz accurate to within  $\pm$ -2.5%. The coarse bandwidth is selected from <u>Table 11</u> via <u>Reg 02h[9:6]</u>, and that bandwidth is further refined using selections in <u>Table 12</u> via <u>Reg 03h[3:0]</u>.

Initially the calibration result is read from <u>Reg 09h[</u>23:0]. Then required Coarse Bandwidth selection is calculated as follows:

$$f_{\text{BW norm coarse}} = f_{\text{WANTED}} * (\frac{\text{Reg 09h}}{(23:0]} + 153600)/10370000$$

(EQ 1)

where  $f_{WANTED}$  is the desired arbitrary bandwidth. The Coarse Bandwidth nearest to calculated  $f_{BW_norm_coarse}$  is selected from Table 11 and written to Reg 02h[9:6].

To calculate the Fine Bandwidth Setting fine\_tune\_ratio is calculated as shown in (EQ 2):

$$fine\_tune\_ratio = f_{BW\_norm\_coarse} / f_{BW\_norm\_coarse\_typ}$$

(EQ 2)

where the  $f_{BW\_norm\_coarse}$  is given in (EQ 1), and  $f_{BW\_norm\_coarse\_typ}$  is the nearest corresponding bandwidth in Table 11. Then Fine Bandwidth Setting is selected from a nearest column in Table 12 that corresponds to the calculated fine\_tune\_ ratio and programmed to Reg 03h[3:0].

Example: to select the bandwidth of 13 MHz, initially read <u>Reg 09h[23:0]</u> (in this example <u>Reg 09h[23:0]</u> = 10470000). Then according to (<u>EQ 1</u>),  $f_{BW_norm\_coarse} = 13$  MHz \* (10470000 + 153600)/10370000 = 13.318 MHz. Select the closest typical value in <u>Table 11</u> to 13.318 MHz and program <u>Reg 02h[9:6]</u> accordingly (ie. <u>Reg 02h[9:6]</u> = '0011'b), then <u>Reg 03h[3:0]</u> =  $f_{WANTED} / f_{BW_norm\_coarse\_typ} = 13.317917$  MHz/14 MHz = 0.95128. Hence from <u>Table 12</u>, <u>Reg 03h[3:0]</u> = '0101'. Finally, write <u>Reg 01h[4]</u>=1 to instruct the HMC1023LP5E to use provided settings.

Please note that the HMC1023LP5E Evaluation Software distributed with HMC1023LP5E Evaluation Kits implements this Calibrated Arbitrary Bandwidth algorithm.

|                            | f <sub>BW_norm_coarse</sub> |              |              |  |  |  |

|----------------------------|-----------------------------|--------------|--------------|--|--|--|

| coarse_bandwidth_code[3:0] | min<br>(MHz)                | typ<br>(MHz) | max<br>(MHz) |  |  |  |

| 0000                       | 3.948                       | 5            | 6.050        |  |  |  |

| 0001                       | 5.527                       | 7            | 8.470        |  |  |  |

| 0010                       | 7.896                       | 10           | 12.100       |  |  |  |

| 0011                       | 11.054                      | 14           | 16.940       |  |  |  |

| 0100                       | 15.792                      | 20           | 24.200       |  |  |  |

| 0101                       | 22.109                      | 28           | 33.880       |  |  |  |

| 0110                       | 31.584                      | 40           | 48.400       |  |  |  |

| 0111                       | 39.480                      | 50           | 60.500       |  |  |  |

| 1000                       | 56.851                      | 72           | 87.120       |  |  |  |

#### Table 11. Normalized Bandwidth Look up Table

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

| Table 12. Calibration Code Look up Table |                  |                  |                  |  |  |  |  |

|------------------------------------------|------------------|------------------|------------------|--|--|--|--|

|                                          | fine_tune_ratio  |                  |                  |  |  |  |  |

| fine_bandwidth_code [3:0]                | min<br>(MHz/MHz) | typ<br>(MHz/MHz) | max<br>(MHz/MHz) |  |  |  |  |

| 0000                                     | 0.790            | 0.803            | 0.818            |  |  |  |  |

| 0001                                     | 0.818            | 0.832            | 0.846            |  |  |  |  |

| 0010                                     | 0.846            | 0.862            | 0.878            |  |  |  |  |

| 0011                                     | 0.878            | 0.893            | 0.909            |  |  |  |  |

| 0100                                     | 0.909            | 0.926            | 0.943            |  |  |  |  |

| 0101                                     | 0.943            | 0.959            | 0.976            |  |  |  |  |

| 0110                                     | 0.976            | 0.994            | 1.012            |  |  |  |  |

| 0111                                     | 1.012            | 1.030            | 1.048            |  |  |  |  |

| 1000                                     | 1.048            | 1.063            | 1.078            |  |  |  |  |

| 1001                                     | 1.078            | 1.097            | 1.116            |  |  |  |  |

| 1010                                     | 1.116            | 1.136            | 1.155            |  |  |  |  |

| 1011                                     | 1.155            | 1.183            | 1.210            |  |  |  |  |

#### Table 12. Calibration Code Look up Table

To reprogram the HMC1023LP5E to any other bandwidth simply repeat the steps above.

#### Filter Bandwidth Setting After Calibration

In cases where ctune is unknown but the calibrated and programmed bandwidth is known, it is possible to estimate the value of ctune based on the values of Coarse Bandwidth Code and Fine Bandwidth Code and the corresponding values in <u>Table 11</u> and <u>Table 12</u>.

For example, if the 3 dB bandwidth for the HMC1023LP5E was factory pre-programmed to a customer defined requirement of 34 MHz and  $\frac{\text{Reg 02h}[9:6]}{\text{Reg 02h}[9:6]}$  = "0110" (Coarse Bandwidth Code) and  $\frac{\text{Reg 03h}[3:0]}{\text{Reg 03h}[3:0]}$  = "0010" (Fine Bandwidth Code), as determined from  $\frac{\text{Reg 0Ah}}{\text{Reg 0Ah}}$  for a pre-programmed part or from  $\frac{\text{Reg 02h}}{\text{Reg 03h}}$  &  $\frac{\text{Reg 03h}}{\text{Reg 03h}}$  for a non programmed part, then ctune can be estimated as follows:

- 1. Lookup the nominal coarse bandwidth and fine bandwidth frequencies.

- a. From Table 11 the nominal coarse frequency is 40 MHz

- b. From Table 12 the nominal fine normalized frequency is 0.862 MHz/ MHz or simply 0.862

- 2. Estimate ctune as:

ctune=(40 MHz \* 0.862 )/ 34 MHz = 1.0141

This value of ctune can now be used to calculate any arbitrary filter frequency as described above.

#### **RC Calibration Circuit**

The RC Calibration block uses a known user supplied clock to measure an on chip RC time constant. This measurement is representative of the uncorrected corner frequency error for a given bandwidth for the HMC1023LP5E.

Calibration is normally done at room temperature. Refer to <u>"Table 1. Electrical Specifications"</u> for further details on the variation of the 3 dB cutoff point with temperature. Typically programmed bandwidth varies 0.03 %/°C.

With this information, the HMC1023LP5E can correctly fine tune the LPF by adjusting the resistors in the LPF to center the corner frequency to the desired bandwidth.

To calibrate the HMC1023LP5E proceeds as follows:

1. Apply a clock signal of frequency between 20 MHz and 100 MHz on the CALCK pin (pin 11) of the HMC1023LP5E. The clock signal only needs to be applied during the calibration procedure and is not

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

required at other time. Please note that an integrated clock doubler must be enabled for clock frequencies less than 40 MHz. To enable the clock doubler simply write  $\frac{\text{Reg 01h}[5]}{\text{Reg 01h}[5]} = 1$ .

- 2. Write the applied clock signal period to <u>Reg 05h[14:0]</u> in picoseconds.

- 3. Enable the RC calibration circuit by writing  $\frac{\text{Reg 01h}[1]}{\text{Reg 01h}[1]} = 1$ .

- 4. Write <u>Reg 06h[8:0]</u> = 152d = 96h.

- 5. Write  $\underline{\text{Reg 04h}} = 0$  to initialize the calibration cycle.

The HMC1023LP5E indicates that the calibration is in process when Reg 08h [4]=1. When Reg 08h [4]=0 calibration has finished. When complete, the calibration Fine Bandwidth Value can be retrieved from Reg 08h [3:0] Once calibrated the HMC1023LP5E automatically writes the calibrated fine Fine Bandwidth values to Reg 03h [3:0] (ie. Reg 03h [3:0] = Reg 08h [3:0]) as explained in Calibrated Automatic Bandwidth Configuration section. If desired, the calibration results can be overridden via Reg 03h [3:0], as explained in Calibrated Manual Bandwidth Configuration section.

#### **Output Driver**

The HMC1023LP5E output driver consists of a differential class AB driver which is designed to drive typical ADC loads directly or can drive up to 200  $\Omega$  in parallel with 50 pF to AC ground per differential output. Note that the output common mode of the driver is controlled directly via the CMI/CMQ pin and can be set as per <u>"Table 1. Electrical Specifications"</u>. Also note, that driver loading does not impact filter transfer responses.

A block diagram showing output connections is presented below.

Figure 37. Output Driver Block Diagram

#### **Bias Circuit**

A band gap reference circuit generates the reference currents used by the different sections. The bias circuit is enabled or disabled as required with the I or Q channel as appropriate.

#### One Time Programmable Memory (OTP)

The HMC1023LP5E features one time programmable memory which can be programmed by the end user or ordered from the factory precalibrated.

The OTP memory is programmed via the standard 4 wire serial port (SPI) as follows:

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

- 1. enable OTP write mode (see Reg 0Bh bit 0 enables OTP programming).

- 2. read the status of the OTP active flag (see <u>Reg 08h</u>, bit 5 is the OTP active flag). The Write Pulse Status (OTP active flag) must be 0 to allow the OTP to be programmed.

- 3. write the OTP bit address to be set (<u>Reg 0Ch</u>). This address is a 4 bit number representing the address of the bit to be programmed. Note that when programming a bit we change its state from 0 to 1 and this operation cannot be reversed. OTP bit addresses can be found in <u>Reg 08h</u>.

- 4. start the OTP Write operation. Write any data to the OTP strobe register (Reg 0Dh).

- 5. read the status of the OTP active flag (Reg 08h, bit 5 is the OTP active flag). If bit 5 is set then the Write pulse is still high. Repeat until bit 5 is 0 which indicates that the write pulse is finished.

- 6. Repeat steps 3 to 5 to program the remaining desired bits.

#### Note that bit 13 OTP\_prg\_flag must be set by the user to use OTP values.

7. When completed, disable OTP write mode (Reg 0Bh).

#### Power on Reset and Soft Reset

The HMC1023LP5E has a built in Power On Reset and also a serial port accessible Soft Reset. Power On Reset is accomplished when power is cycled to the HMC1023LP5E, while Soft Reset is accomplished via the SPI by writing  $\underline{\text{Reg 00h}}[5] = 1$  followed by writing  $\underline{\text{Reg 00h}}[5] = 0$ . All chip registers will be reset to default states approximately 250us after power up.

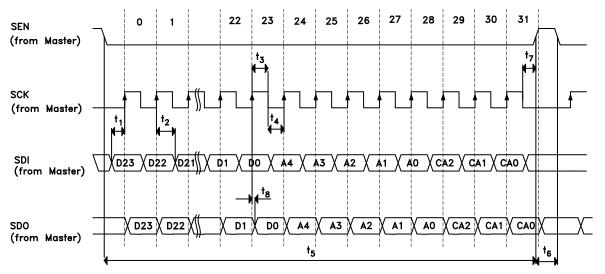

#### Serial Port Interface

The HMC1023LP5E features a four wire SPI. Four wires (SEN,SCK,SDI,SDO) are necessary to implement a SPI Read/Write functionality, while a Write only functionality can be implemented with 3 wires (SEN,SCK,SDI). The HMC1023LP5E SPI features a 3-bit Chip\_ID that enables operation of up to 8 devices on the same SPI bus. Chip\_ID of HMC1023LP5E is set to '101'b.

Please note that every SPI operation is both a Read and a Write. Data is written to the HMC1023LP5E on the SDI line, and read from the HMC1023LP5E on the SDO line every Read/Write cycle, as shown in Figure 38. Every SPI write the HMC1023LP5E returns the data contained in the register whose address is specified in Reg 00h[4:0] prior to the Write/Read cycle.

Hence to read from a particular HMC1023LP5E register, it is necessary to initially write the address of that register to Register 0 (ie. <u>Reg 00h[4:0]</u> = REG\_ADDR, where REG\_ADDR is the address of the register to be read on the next Read/Write cycle). The desired register will be read on the next (2nd) Write/Read cycle. If nothing additional is desired to be written to the HMC1023LP5E on the 2nd Write/Read cycle, simply rewrite <u>Reg 00h[4:0]</u> = REG\_ADDR on the second Read/Write cycle to conclude the register read.

In summary, the Read cycle uses indirect addressing where <u>Reg 00h</u> contains the pointer to the address of the register to be Read. Note that in any SPI cycle the Write data is stored in the register at the end of the cycle when SEN goes high. This means that the address pointer (<u>Reg 00h[4:0]</u>) must be set prior to the Read/Write cycle in which the desired data is read.

Typical serial port operation can be run with SCK at speeds up to 30 MHz.

#### Serial Port WRITE Operation

The host changes the data on the falling edge of SCK and the HMC1023LP5E reads the data on the rising edge.

A typical WRITE cycle is shown in Figure 38. It is 32 clock cycles long.

- 1. The host sets Serial Port Enable (SEN) low and places the MSB of the data on Serial Data Input (SDI) followed by a rising edge on SCK.

- 2. HMC1023LP5E reads SDI (MSB first) on the 1st rising edge of SCK after SEN.

## 72 MHz DUAL PROGRAMMABLE LOW PASS FILTER WITH DRIVER

- 3. HMC1023LP5E registers the data bits, D23:D0, on the next 23 rising edges of SCK (total of 24 data bits).

- 4. Host places the 5 register address bits, A4:A0, on the next 5 falling edges of SCK (MSB to LSB) while the HMC1023LP5E reads the address bits on the corresponding rising edge of SCK.

- 5. Host places the 3 chip address bits, CA2:CA0=[101], on the next 3 falling edges of SCK (MSB to LSB). Note the HMC1023LP5E chip address is fixed as "5d" or "101b".

- 6. SEN goes from low to high after the 32nd rising edge of SCK. This completes the WRITE cycle.

- 7. HMC1023LP5E also exports data back on the Serial Data Out (SDO) line. For details see the section on READ operation.

#### Serial Port READ Operation

The Read data is available on SDO line. This line itself is tri-stated when the device is not being addressed. However when the device is active and has been addressed by the SPI, the HMC1023LP5E controls the SDO line and exports data on this line during the next SPI cycle.

HMC1023LP5E changes the data to the host on the rising edge of SCK and the host reads the data from HMC1023LP5E on the falling edge.

A typical READ cycle is shown in Figure 38. Read cycle is 32 clock cycles long. To specifically read a register, the address of that register must be written to dedicated Reg 00h. This requires two full cycles, one to write the required address, and a 2nd to retrieve the data. A read cycle can then be initiated as follows;