#### MAX40007

# Nanopower Op Amp in Ultra-Tiny WLP and SOT23 Packages

#### **General Description**

The MAX40007 is a single operational amplifier that provides a maximized ratio of gain bandwidth (GBW) to supply current and is ideal for battery-powered applications such as portable instrumentation, portable medical equipment, and wireless handsets.

This CMOS op amp features an ultra-low supply current of only 700nA (typ), ground-sensing inputs, and rail-to-rail outputs; operating from a single 1.7V to 5.5V supply, allowing the amplifier to be powered by the same 1.8V, 2.5V, or 3.3V nominal supply that powers the microcontroller. The MAX40007 amplifier is unity-gain stable with a 20kHz GBW product.

The ultra-low supply current, low operating voltage, and rail-to-rail output capabilities make this operational amplifier ideal for use in single lithium ion (Li+), two-cell NiCd or alkaline battery systems.

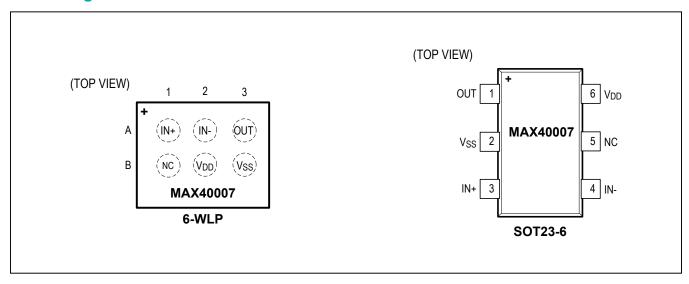

The MAX40007 is available in a 6-pin SOT23 package and an ultra-tiny 6-bump, 1.1mm x 0.76mm wafer-level package (WLP) with a bump pitch of 0.35mm. The amplifier is specified over the -40°C to 125°C operating temperature range.

## **Applications**

- Fitness wearables

- Mobile phones

- Notebook and Tablet Computers

- Portable Medical Devices

- Portable Instrumentation

#### **Benefits and Features**

- Ultra-Low Power Preserves Battery Life

- 700nA Typical Supply Current

- Single 1.7V to 5.5V Supply Voltage Range

- Amplifier Can be Powered From the Same 1.8V/2.5V/3.3V/5V System Rails

- Tiny Packages Save Board Space

- 1.1mm x 0.76mm WLP-6 with 0.35mm Bump Pitch

- SOT23-6 Package

- Precision Specifications for Buffer/Filter/Gain Stages

- Low 300µV Input Offset Voltage

- · Rail-to-Rail Output Voltage

- 20kHz BW

- · Low 40pA Input Bias Current

- Unity-Gain Stable

- -40°C to 125°C Temperature Range

Ordering Information appears at end of data sheet.

# Nanopower Op Amp in Ultra-Tiny WLP and SOT23 Packages

## **Absolute Maximum Ratings**

| V <sub>DD</sub> to V <sub>SS</sub>               | 0.3V to +6V                       | Continu |

|--------------------------------------------------|-----------------------------------|---------|

| IN+, IN- to V <sub>SS</sub>                      | $V_{SS}$ -0.3V to $V_{DD}$ + 0.3V | 6-Bu    |

| IN+ to IN                                        | ±V <sub>DD</sub>                  | SOT     |

| OUT to V <sub>SS</sub>                           | $V_{SS}$ -0.3V to $V_{DD} + 0.3V$ | Operat  |

| Continuous Current Into Any Input Pi             | n±10mA                            | Junctio |

| Continuous Current Into Output Pin               | ±30mA                             | Storage |

| Output Short-Circuit Duration to V <sub>DD</sub> | or V <sub>SS</sub> 10s            | Lead T  |

|                                                  |                                   |         |

| Continuous Power Dissipation ( $T_A = +70^{\circ}C$ ) |                |

|-------------------------------------------------------|----------------|

| 6-Bump WLP (derate 10.19mW/°C at 70°C)                | 816mW          |

| SOT23-6 (derate 4.30mW/°C at 70°C)                    | 347.80mW       |

| Operating Temperature Range                           | 40°C to +125°C |

| Junction Temperature                                  | +150°C         |

| Storage Temperature Range                             | 65°C to +150°C |

| Lead Temperature (soldering, 10s)                     | +300°C         |

| Soldering Temperature (reflow)                        | +260°C         |

|                                                       |                |

Stresses beyond those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

# **Package Thermal Characteristics (Note 1)**

**WLP**

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ) .....98.06°C/W

SOT23

Junction-to-Ambient Thermal Resistance ( $\theta_{JA}$ ).......230°C/W Junction-to-Case Thermal Resistance ( $\theta_{JC}$ ).............76°C/W

Note 1: Package thermal resistances were obtained using the method described in JEDEC specification JESD51-7, using a four-layer board. For detailed information on package thermal considerations, refer to www.maximintegrated.com/thermal-tutorial.

#### **Electrical Characteristics**

$V_{DD}$  = +3V,  $V_{SS}$  = 0V,  $V_{CM}$  = 0.5V,  $V_{OUT}$  =  $V_{DD}/2$ ,  $R_L$  = 1M $\Omega$  to  $V_{DD}/2$ ,  $T_A$  = +25°C, unless otherwise noted. Note 2.

| PARAMETER                          | SYMBOL           | CONDITI                                                                                                                  | ONS                                                    | MIN                    | TYP  | MAX                     | UNITS |

|------------------------------------|------------------|--------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------|------------------------|------|-------------------------|-------|

| Supply Voltage Range               | V <sub>DD</sub>  | Guaranteed by PSRR tests                                                                                                 | Guaranteed by PSRR tests                               |                        |      | 5.5                     | V     |

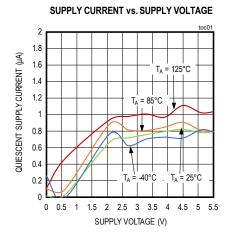

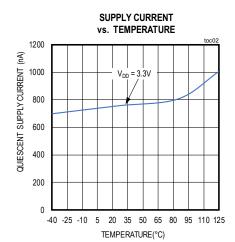

| Supply Current                     | I <sub>DD</sub>  | At 25°C                                                                                                                  |                                                        |                        | 0.7  | 0.9                     | μA    |

| Input Offset Voltage               | Vos              | V <sub>SS</sub> - 0.1V < CMIR < V <sub>DD</sub>                                                                          | V <sub>SS</sub> - 0.1V < CMIR < V <sub>DD</sub> - 1.1V |                        | ±0.3 | ±1.3                    | mV    |

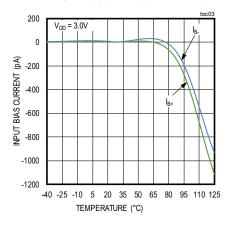

| Input Bias Current (Note 3)        | Ι <sub>Β</sub>   |                                                                                                                          |                                                        |                        | ±40  | ±100                    | pА    |

| Input Offset Current (Note 3)      | los              |                                                                                                                          |                                                        |                        | ±5   | ±50                     | pA    |

| Input Capacitance                  |                  | Either input, over entire cor                                                                                            | mmon mode range                                        |                        | 1.5  |                         | pF    |

| Input Common-Mode<br>Voltage Range | V <sub>CM</sub>  | Guaranteed by the CMRR                                                                                                   | test                                                   | V <sub>SS</sub> - 0.1V |      | V <sub>DD</sub><br>-1.1 | V     |

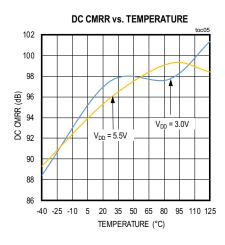

| Common-Mode Rejection              | CMRR             | DC, $(V_{SS} - 0.1) \le V_{CM} \le (V_{DD} - 1.1V)$<br>AC, $100 \text{mV}_{PP} \text{ 1kHz}$ , with output at $V_{DD}/2$ |                                                        | 70                     | 92   |                         | - dB  |

| Ratio                              | CIVIKK           |                                                                                                                          |                                                        |                        | 72   |                         |       |

| Power-Supply Rejection             | DCDD             | DC, +1.7V ≤ V <sub>DD</sub> ≤ +5.5V                                                                                      |                                                        | 75                     | 100  |                         | 40    |

| Ratio                              | PSRR             | AC, 100mV <sub>PP</sub> 1kHz, superimposed on V <sub>DD</sub> /2                                                         |                                                        |                        | 75   |                         | dB    |

| Large-Signal Voltage Gain          | A <sub>VOL</sub> | $R_L = 1M\Omega$ , $V_{OUT} = V_{SS} + 2$<br>$V_{DD} - 25mV$                                                             | $R_L = 1M\Omega$ , $V_{OUT} = V_{SS} + 25mV$ to        |                        | 110  |                         | dB    |

|                                    | V                | Swing high specified as                                                                                                  | R <sub>L</sub> = 100kΩ                                 |                        | 3.2  | 8                       |       |

| Outrot Valtage Codes               | V <sub>OH</sub>  | V <sub>DD</sub> - V <sub>OUT</sub>                                                                                       | $R_L = 10k\Omega$                                      |                        | 32   | 70                      | \/    |

| Output Voltage Swing               |                  | Swing low specified as                                                                                                   | R <sub>L</sub> = 100kΩ                                 |                        | 2.9  | 8                       | mV    |

|                                    |                  | V <sub>OUT</sub> - V <sub>SS</sub>                                                                                       | $R_L = 10k\Omega$                                      |                        | 27   | 70                      | ]     |

| Gain-Bandwidth Product             | GBW              | A <sub>V</sub> = 1, C <sub>L</sub> = 20pF                                                                                |                                                        |                        | 15   |                         | kHz   |

| Phase Margin                       | ΦМ               | C <sub>L</sub> = 20pF                                                                                                    |                                                        |                        | 56   |                         | ٥     |

## **Electrical Characteristics (continued)**

$V_{DD} = +3V, \ V_{SS} = 0V, \ V_{CM} = 0.5V, \ V_{OUT} = V_{DD}/2, \ R_L = 1M\Omega \ to \ V_{DD}/2, \ T_{\pmb{A}} = +25^{\circ}\pmb{C}, \ unless \ otherwise \ noted. \ Note \ 2.$

| PARAMETER              | SYMBOL          | CONDITIONS                                    | MIN TYP MAX | UNITS |

|------------------------|-----------------|-----------------------------------------------|-------------|-------|

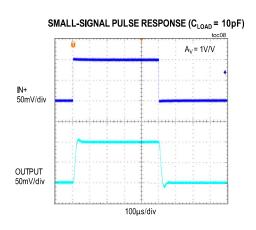

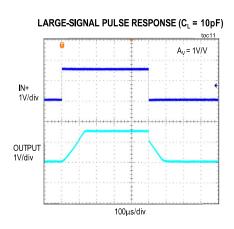

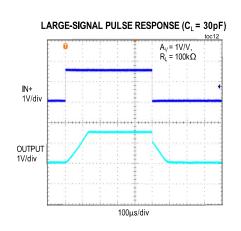

| Slew Rate              | SR              | $V_{OUT} = 1V_{P-P}$ step, $A_V = 1V/V$       | 12          | V/ms  |

| Settling Time          |                 | 100mV step, 0.1% settling, A <sub>V</sub> = 1 | 74          | μs    |

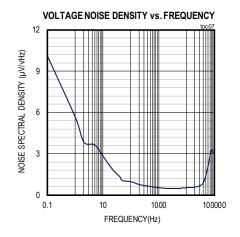

| Input Voltage Noise    | e <sub>n</sub>  | f = 1kHz                                      | 513         | nV/√H |

| Input Current Noise    | i <sub>n</sub>  | f = 1kHz                                      | 0.004       | pA/√H |

| Output Short-Circuit   |                 | Shorted to V <sub>SS</sub> (sourcing)         | 10          | mA    |

| Current                |                 | Shorted to V <sub>DD</sub> (sinking)          | 10          | mA    |

| Power-On Time          | t <sub>ON</sub> |                                               | 0.13        | ms    |

| Stable Capacitive Load | CL              | No sustained oscillations                     | 20          | pF    |

#### **Electrical Characteristics**

$V_{DD} = +3V, V_{SS} = 0V, V_{CM} = 0.5V, V_{OUT} = V_{DD}/2, R_L = 1M\Omega \text{ to } V_{DD}/2, \textbf{T}_{\textbf{A}} = +40^{\circ}\textbf{C} \text{ to } +125^{\circ}\textbf{C}, \text{ unless otherwise noted. Note 2.}$

| PARAMETER                                       | SYMBOL            | CONDITION                                                                                                                 | ONS                                                                      | MIN | TYP | MAX                     | UNITS |  |

|-------------------------------------------------|-------------------|---------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-----|-----|-------------------------|-------|--|

| Supply Voltage Range                            | V <sub>DD</sub>   | Guaranteed by PSRR tests                                                                                                  | 3                                                                        | 1.7 |     | 5.5                     | V     |  |

| Occasilis Occasint                              | ı                 | T <sub>A</sub> = -40°C to 85°C                                                                                            | T <sub>A</sub> = -40°C to 85°C                                           |     |     | 1.2                     |       |  |

| Supply Current                                  | I <sub>DD</sub>   | T <sub>A</sub> = -40°C to 125°C                                                                                           |                                                                          |     |     | 1.4                     | μA    |  |

| Input Offset Voltage                            | V <sub>OS</sub>   | T <sub>A</sub> = -40°C to 125°C                                                                                           |                                                                          |     |     | ±4.5                    | mV    |  |

| Input Offset Voltage<br>Temperature Coefficient | TCV <sub>OS</sub> |                                                                                                                           |                                                                          |     | 6.4 | 36.6                    | μV/°C |  |

| Input Bias Current (Note 3)                     | I <sub>B</sub>    |                                                                                                                           |                                                                          |     | 0.7 | 7                       | nA    |  |

| Input Common-Mode<br>Voltage Range              | V <sub>CM</sub>   | Guaranteed by the CMRR                                                                                                    | uaranteed by the CMRR test                                               |     |     | V <sub>DD</sub><br>-1.1 | V     |  |

| Common-Mode Rejection                           | CMRR              | DC, $(V_{SS} - 0.1) \le V_{CM} \le (V_{DD} - 1.1V)$<br>AC, $100 \text{mV}_{P-P} \text{ 1kHz}$ , with output at $V_{DD}/2$ |                                                                          | 70  |     |                         | dB    |  |

| Ratio                                           | CIVIRR            |                                                                                                                           |                                                                          |     | 63  |                         | 1 UB  |  |

| Power-Supply Rejection                          | PSRR              | $+1.7V \le V_{DD} \le +5.5V, -40^{\circ}$                                                                                 | $1.7V \le V_{DD} \le +5.5V$ , $-40^{\circ}C \le T_{A} \le +125^{\circ}C$ |     |     |                         | ٩D    |  |

| Ratio                                           | PSRR              | AC, 100mV <sub>P-P</sub> 1kHz, superimposed on V <sub>DD</sub>                                                            |                                                                          |     | 40  |                         | dB    |  |

| Large-Signal Voltage Gain                       | A <sub>VOL</sub>  | $V_{OUT}$ = 50mV to $V_{DD}$ - 50i                                                                                        | $V_{OUT}$ = 50mV to $V_{DD}$ - 50mV, $R_L$ = 1M $\Omega$                 |     |     |                         | dB    |  |

|                                                 | V                 | Swing high specified as V <sub>DD</sub> - V <sub>OUT</sub>                                                                | R <sub>L</sub> = 100kΩ                                                   |     | 8   |                         | mV    |  |

| Outrat Valtage Cuies                            | V <sub>OH</sub>   |                                                                                                                           | R <sub>L</sub> = 10kΩ                                                    |     | 70  |                         |       |  |

| Output Voltage Swing                            | -                 |                                                                                                                           | $R_L = 100k\Omega$                                                       |     | 8   |                         |       |  |

|                                                 | V <sub>OL</sub>   |                                                                                                                           | $R_L = 10k\Omega$                                                        |     | 70  |                         |       |  |

Note 2: All devices are production tested at T<sub>A</sub> = +25°C. All temperature limits are guaranteed by design.

Note 3: Guaranteed by design and bench characterization.

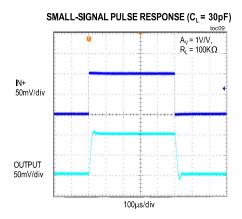

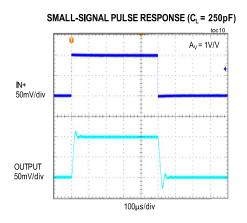

# **Typical Operating Characteristics**

$(V_{DD}$  = +3V,  $V_{SS}$  = 0V,  $V_{CM}$  = 0V,  $R_L$  = 100k $\Omega$  to  $V_{DD}/2$ ,  $T_A$  = +25°C, unless otherwise noted.)

#### INPUT BIAS CURRENTS vs. TEMPERATURE

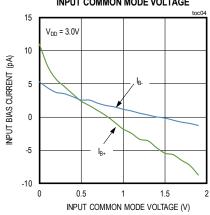

# INPUT BIAS CURRENTS vs. INPUT COMMON MODE VOLTAGE

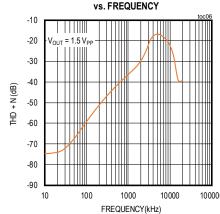

# TOTAL HARMONIC DISTORTION PLUS NOISE

# **Typical Operating Characteristics (continued)**

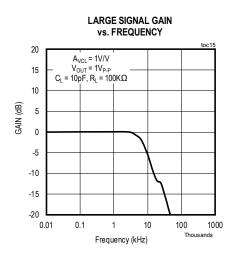

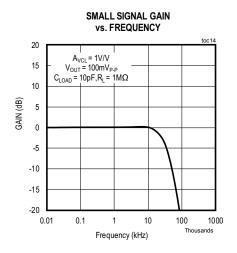

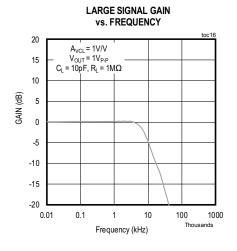

$(V_{DD} = +3V, V_{SS} = 0V, V_{CM} = 0V, R_L = 100k\Omega$  to  $V_{DD}/2, T_A = +25$ °C, unless otherwise noted.)

# **Typical Operating Characteristics (continued)**

$(V_{DD}$  = +3V,  $V_{SS}$  = 0V,  $V_{CM}$  = 0V,  $R_L$  = 100k $\Omega$  to  $V_{DD}/2$ ,  $T_A$  = +25°C, unless otherwise noted.)

#### **SMALL SIGNAL GAIN** vs. FREQUENCY 20 $\begin{aligned} A_{VCL} &= \ 1 \text{V/V} \\ V_{OUT} &= \ 100 \text{mV}_{P \cdot P} \\ C_L &= \ 10 \text{pF}, \ R_L = \ 100 \text{K}\Omega \end{aligned}$ 15 10 GAIN (dB) 5 0 -5 -10 -15 -20 0.01 0.1 100 1000 Thousands Frequency (kHz)

# **Pin Configurations**

# **Pin Description**

| BUMP (WLP) | 6-SOT23 | NAME            | FUNCTION                                                                                 |  |

|------------|---------|-----------------|------------------------------------------------------------------------------------------|--|

| A1         | 3       | IN+             | Non-Inverting Amplifier Input.                                                           |  |

| A2         | 4       | IN-             | Inverting Amplifier Input.                                                               |  |

| A3         | 1       | OUT             | Amplifier Output.                                                                        |  |

| B1         | 5       | NC              | No Connection. Internally connected.                                                     |  |

| B2         | 6       | V <sub>DD</sub> | Positive Power Supply Input.                                                             |  |

| В3         | 2       | V <sub>SS</sub> | Negative Power Supply Input. Connect V <sub>SS</sub> to 0V in single-supply application. |  |

www.maximintegrated.com Maxim Integrated | 7

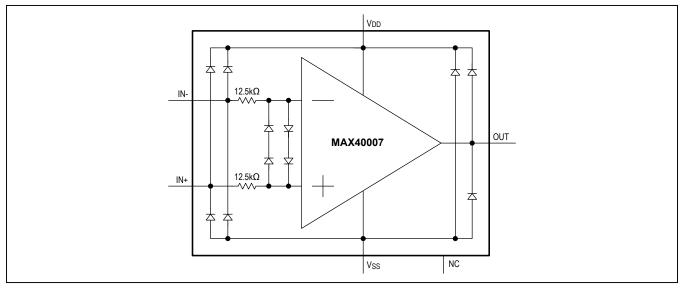

## **Functional (or Block) Diagram**

#### **Detailed Description**

The MAX40007 is an ultra-low-power op amp ideal for battery-powered applications and features a maximized ratio of GBW to supply current, low operating supply voltage, and low input bias current. The MAX40007 is ideal for general-purpose, low-current, low-voltage continuously powered portable applications. The MAX40007 consumes an ultra-low 700nA (typ) supply current and has a 0.3mV (typ) offset voltage. This device is unity-gain stable with a 20kHz GBW product, driving capacitive loads up to 20pF.

### **Applications Information**

#### **Ground Sensing**

The common-mode input range of the MAX40007 extends down to  $V_{SS}$ , and offers excellent common-mode rejection. This op amp is guaranteed not to exhibit phase reversal when either input is overdriven.

#### **Power Supplies and Layout**

The MAX40007 operates from a single +1.7V to +5.5V power supply. Bypass the power supplies with a  $0.1\mu F$  ceramic capacitor placed close to  $V_{DD}$  and  $V_{SS}$  pins. Adding a solid Ground plane improves performance generally by decreasing the noise at the op amp's inputs However, in very high impedance circuits, it may be worth removing the ground plane under the IN- pin to reduce the stray capacitance and help avoid reducing the phase margin. To further decrease stray capacitance, minimize PCB lengths and resistor leads, and place external components close to the amplifier's pins.

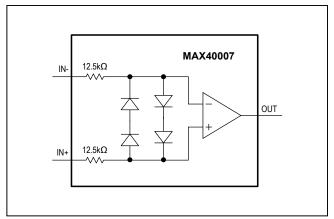

#### **Input Differential Voltage Protection**

The MAX40007's inputs are protected from large differential voltages by the network shown in Figure 1. This is done to prevent gradual degradation of the input offset voltage. In normal operation, the amplifier inputs are at almost the same voltage at all times so these components are transparent to normal operation. Using this amplifier as a comparator, however, is not recommended—the inputs will start to draw "bias current' when the differential voltage exceeds about 1V. While this will not damage the amplifier in any way, it is not usually a desirable feature for a comparator. Maxim does make comparators with similar speed and power performance as these amplifiers, such as the MAX40002/3/4/5.

Figure 1. Input Protection Scheme

#### **Stability**

This MAX40007 maintains stability in its minimum gain configuration while driving capacitive loads up to 20pF or so. Larger capacitive loading is achieved using the techniques described in the Capacitive Load Stability section below.

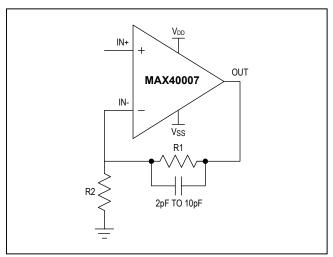

Although this amplifier is primarily designed for low-frequency applications, good layout can still be extremely important, especially if very high-value resistors are being used—as is likely in ultra-low-power circuitry. However, some stray capacitance may be unavoidable; and it may be necessary to add a 2pF to 10pF capacitor across the feedback resistor, as shown in Figure 2. Select the smallest

Figure 2. Compensation for Feedback Node Capacitance

# capacitor value that ensures stability so that BW and settling time are not significantly impacted.

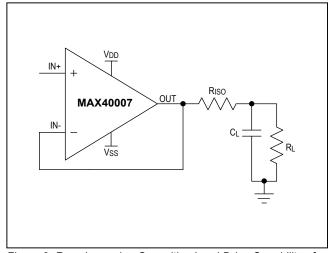

#### **Capacitive Load Stability**

Driving large capacitive loads can cause instability in amplifiers. The MAX40007 is stable with capacitive loads up to 20pF. Stability with higher capacitive loads can be achieved by adding an isolation resistor in series with the op-amp output as shown in <a href="Figure 2">Figure 2</a> below. This resistor improves the circuit's phase margin by isolating the load capacitor from the amplifier's inverting input. The graph in the <a href="Typical Operating Characteristics">Typical Operating Characteristics</a> gives the stable operation region for capacitive load versus isolation resistors.

Figure 3.  $R_{\rm ISO}$  Improving Capacitive Load Drive Capability of Op Amp

### **Ordering Information**

| PART |             | TEMP<br>RANGE   | PIN<br>PACKAGE | TOP<br>MARK |

|------|-------------|-----------------|----------------|-------------|

| MA   | X40007ANT+  | -40°C to +125°C | 6-WLP          | +2          |

| MA   | X40007AUT+* | -40°C to +125°C | 6-SOT23        | +ACUV       |

<sup>+</sup>Denotes a lead(Pb)-free/RoHS-compliant package.

# **Chip Information**

PROCESS: BICMOS

## **Package Information**

For the latest package outline information and land patterns (footprints), go to <a href="www.maximintegrated.com/packages">www.maximintegrated.com/packages</a>. Note that a "+", "#", or "-" in the package code indicates RoHS status only. Package drawings may show a different suffix character, but the drawing pertains to the package regardless of RoHS status.

| PACKAGE<br>TYPE | PACKAGE<br>CODE | OUTLINE<br>NO. | LAND<br>PATTERN NO.            |

|-----------------|-----------------|----------------|--------------------------------|

| 6-WLP           | N60D1+1         | 21-100086      | Refer to Application Note 1891 |

| 6-SOT23         | U6+1            | 21-0058        | 90-0175                        |

<sup>\*</sup>Future product—contact factory for availability.

# MAX40007

# Nanopower Op Amp in Ultra-Tiny WLP and SOT23 Packages

# **Revision History**

| REVISION<br>NUMBER | REVISION DATE | DESCRIPTION     | PAGES<br>CHANGED |

|--------------------|---------------|-----------------|------------------|

| 0                  | 12/16         | Initial release | _                |

For pricing, delivery, and ordering information, please contact Maxim Direct at 1-888-629-4642, or visit Maxim Integrated's website at www.maximintegrated.com.

Maxim Integrated cannot assume responsibility for use of any circuitry other than circuitry entirely embodied in a Maxim Integrated product. No circuit patent licenses are implied. Maxim Integrated reserves the right to change the circuitry and specifications without notice at any time. The parametric values (min and max limits) shown in the Electrical Characteristics table are guaranteed. Other parametric values quoted in this data sheet are provided for guidance.