# ISL85005DEM01Z and ISL85005ADEM01Z Demonstration Boards User Guide

### **Description**

The ISL85005 and ISL85005A are 4.5V to 18V input, 5A synchronous buck regulators for applications with input voltage from multi-cell batteries or regulated 5V and 12V power rails. These devices also provide an integrated bootstrap diode for the high-side gate driver to reduce the external parts count. The ISL85005DEM01Z and ISL85005ADEM01Z platforms allow quick demonstration of the high performance features of the ISL85005 and ISL85005A buck regulators.

### **Specifications**

These boards have been configured and optimized for the following operating conditions:

- · Input voltage ranges from 7V to 15V

- 5V nominal output voltage

- . Up to 5A output current capability

- Default internally set 500kHz switching frequency

- · Default internally set 2.3ms soft-start

- Operating temperature range: -40°C to +85°C

### **Key Features**

- Switch selectable EN (enabled/disabled)

- Selectable mode (DEM/Forced CCM) (ISL85005DEM01Z)

- · Internal and external compensation options

- Frequency synchronization option (ISL85005DEM01Z)

- Adjustable soft-start option (ISL85005ADEM01Z)

- · Small and compact design

#### **Related Literature**

- · For a full list of related documents please visit our website

- ISL85005 and ISL85005A product pages

### **Ordering Information**

| PART NUMBER     | DESCRIPTION                                            |

|-----------------|--------------------------------------------------------|

| ISL85005DEM01Z  | Small form-factor demonstration board for ISL85005FRZ  |

| ISL85005ADEM01Z | Small form-factor demonstration board for ISL85005AFRZ |

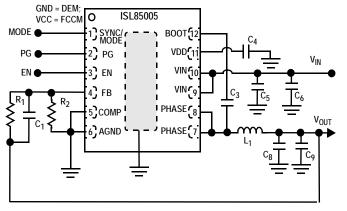

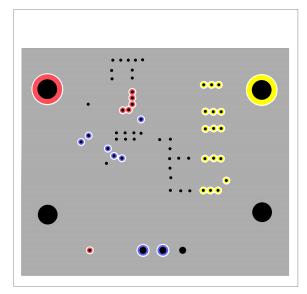

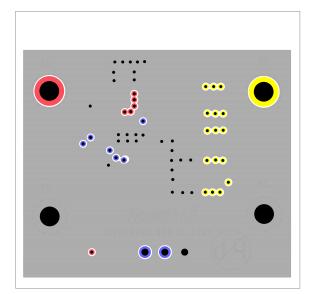

FIGURE 1A. ISL85005DEM01Z FIGURE 1. BLOCK DIAGRAM

FIGURE 1B. ISL85005ADEM01Z

## **Connector and Selection Jumper Descriptions**

The ISL85005DEM01Z and ISL85005ADEM01Z demonstration boards include I/O connectors and a selection jumper as shown in Table 1.

**TABLE 1. CONNECTORS AND JUMPER**

| REFERENCE<br>DESIGNATOR | DESCRIPTION                        |

|-------------------------|------------------------------------|

| J1                      | Selection Jumper for Enable (EN)   |

| J3                      | Input voltage positive connection  |

| J4                      | Input voltage return connection    |

| J5                      | Output voltage positive connection |

| J6                      | Output voltage return connection   |

#### **Quick Setup Guide**

Refer to the following Quick Setup Guide to configure and power-up the board for proper operation.

- Set the power supply voltage to 12V, and turn off the power supply. Connect the positive output of power supply to J3 (VIN) and the negative output to J4 (GND).

- Connect an electronic load to J5 (VOUT) for the positive connection and J6 (GND) for the negative connection.

- 3. Measure the output voltage (J5 and J6) with the voltmeter.

- 4. Place scope probes on VOUT and other test points of interest.

- 5. Set EN jumper (J1) to ON position.

- Set the load current to be 0.1A and turn on the power supply, the output voltage should be in regulation with a nominal 5V output.

- Slowly increase the load up to 5A while monitoring the output voltage which should remain in regulation with a nominal 5V output.

- 8. Slowly sweep VIN from 7V to 15V, the output voltage should remain in regulation with a nominal 5V output.

- 9. Decrease the input voltage to 0V to shut down the regulator.

## Operation Mode Selection (ISL85005DEMO1Z)

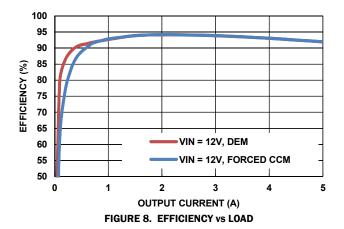

The ISL85005DEM01Z can be configured in either forced Continuous Conduction Mode (CCM) or Diode Emulation Mode (DEM):

- In the default configuration of ISL85005DEM01Z, SYNC/MODE (Pin 1) of ISL85005 is floating, the ISL85005 operates in forced CCM.

- To configure the ISL85005 in DEM, short the SYNC/MODE pin to GND by populating a  $0\Omega$  resistor for C<sub>SS</sub>. DEM enables automatic transition from CCM to DCM and higher efficiency at light-load conditions.

## Frequency Synchronization (ISL85005DEMO1Z)

The ISL85005 can be synchronized to an external clock with frequency ranges from 300kHz to 2MHz by applying the external clock to the SYNC/MODE pin on the ISL85005DEMO1Z demonstration board. The external clock should meet the specifications of the pulse width and voltage level described in the datasheet.

## Adjusting Soft-Start Time (ISL85005ADEMO1Z)

With the SS pin floating, the ISL85005A features an internally set 2.3ms of soft-start time. The soft-start time can be set to a desired value by connecting an external capacitor ( $C_{SS}$  on the ISL85005ADEM01Z demonstration board) between the SS pin and AGND. The capacitance can be calculated by <u>Equation 1</u>:

$$C_{SS}[nF] = 3.5 \cdot t_{SS}[ms] - 1.6nF$$

(EQ. 1)

## **Evaluating Other Output Voltages**

Both ISL85005DEM01Z and ISL85005ADEM01Z have a nominal 5V output voltage. The output voltages are programmable by an external resistor divider formed by  $R_1$  and  $R_2$  as shown in Figure 1 on page 1.  $R_1$  is usually chosen first, then the value for  $R_2$  can be calculated based on  $R_1$  and the desired output voltage using Equation 2.

$$R_2 = \frac{R_1 \cdot 0.8V}{V_{OUT} - 0.8V}$$

(EQ. 2)

### **PCB Layout Considerations**

The PCB layout is critical for proper operation of the ISL85005 and ISL85005A. The following guidelines should be followed to achieve good performance.

- Use a multilayer PCB structure to achieve optimized performance, a four-layer PCB is recommended for this design.

- Use a combination of bulk capacitors and smaller ceramic capacitors with lower ESL for the input capacitors and place them as close to the IC as possible.

- 3. Place the VDD decoupling capacitor close to the IC between VDD and GND. A 1µF ceramic capacitor is typically used.

- Place a bootstrap capacitor close to the IC between the BOOT and PHASE pins. A 0.1µF ceramic capacitor is typically used.

- Connect the feedback resistor divider between the output capacitor positive terminal and the AGND pin of the IC, and place the resistors close to the FB pin of the IC.

- 6. Connect the EPAD of the IC to the GND planes underneath using multiple thermal vias to improve thermal performance.

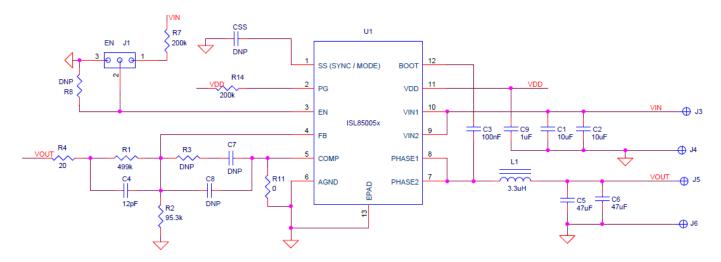

#### ISL85005xDEMO1Z Demonstration Board

FIGURE 2. TOP VIEW

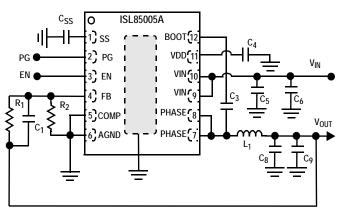

#### **Schematic**

FIGURE 3. ISL85005xDEM01Z SCHEMATIC

Submit Document Feedback 3 Intersil UG110.0 February 6, 2017

#### **User Guide 110**

### **Bill of Materials**

| MANUFACTURER<br>PART NUMBER       | REFERENCE<br>DESIGNATOR | QTY | DESCRIPTION                                                          | MANUFACTURER                |

|-----------------------------------|-------------------------|-----|----------------------------------------------------------------------|-----------------------------|

| ISL85005FRZ<br>(ISL85005DEM01Z)   | U1                      | 1   | IC-BUCK REGULATOR W/ SYNC/MODE PIN, 12PIN, DFN, 3x4, ROHS            | INTERSIL                    |

| ISL85005AFRZ<br>(ISL85005ADEM01Z) |                         | 1   | IC-BUCK REGULATOR W/ SS PIN, 12PIN, DFN, 3x4, ROHS                   | INTERSIL                    |

| GRM1555C1H120JA01D                | C4                      | 1   | CAP, SMD, 0402, 12pF, 50V, 5%, NPO, ROHS                             | MURATA                      |

|                                   | C7, C8, C <sub>SS</sub> | 0   | CAP, SMD, 0402, DNP-PLACE HOLDER, ROHS                               |                             |

| GRM188R71E104KA01D                | С3                      | 1   | CAP, SMD, 0603, 0.1µF, 25V, 10%, X7R, R0HS                           | MURATA                      |

| GRM188R61E105KA12D                | C9                      | 1   | CAP, SMD, 0603, 1µF, 25V, 10%, X5R, ROHS                             | MURATA                      |

| C1206X7R250-106KNE                | C1, C2                  | 2   | CAP, SMD, 1206, 10µF, 25V, 10%, X7R, ROHS                            | VENKEL                      |

| CL32A476KOJNNNE                   | C5, C6                  | 2   | CAP, SMD, 1210, 47µF, 16V, 10%, X5R, ROHS                            | SAMSUNG                     |

| 744314330                         | L1                      | 1   | COIL-PWR INDUCTOR, SMD, 6.9mm <sup>2</sup> , 3.3μH, 9A 9mΩ, WW, ROHS | WURTH ELEKTRONIK            |

| 1514-2                            | J3, J4, J5, J6          | 4   | CONN-TURRET, TERMINAL POST, TH, ROHS                                 | KEYSTONE                    |

| ERJ2RKF20R0                       | R4                      | 1   | RES, SMD, 0402, 20Ω, 1/16W, 1%, TF, ROHS                             | PANASONIC                   |

| CR0402-16W-00T                    | R11                     | 1   | RES, SMD, 0402, 0Ω, 1/16W, 5%, TF, ROHS                              | VENKEL                      |

| MCR01MZPF2003                     | R7, R14                 | 2   | RES, SMD, 0402, 200k, 1/16W, 1%, TF, ROHS                            | ROHM                        |

| CR0402-16W-4993FT                 | R1                      | 1   | RES, SMD, 0402, 499k, 1/16W, 1%, TF, ROHS                            | VENKEL                      |

| RC0402FR-0795K3L                  | R2                      | 1   | RES, SMD, 0402, 95.3k, 1/16W, 1%, TF, ROHS                           | YAGEO                       |

|                                   | R3, R8                  | 0   | RES, SMD, 0402, DNP, DNP, DNP, TF, ROHS                              |                             |

| 929950-00                         | Jumper                  | 1   | CONN-JUMPER, SHORTING, 2PIN, BLK, OPEN TOP, 2.54mmPITCH, ROHS        | 3M                          |

| PEC03SAAN                         | J1                      | 1   | 3 Positions Header, 100 mil (2.54mm) spacing, Through Hole Tin       | Sullins Connector Solutions |

| ISL85005xDEM01Z                   | РСВ                     | 1   | PWB-PCB, ISL85005xDEMO1Z, REVA, ROHS                                 | Any                         |

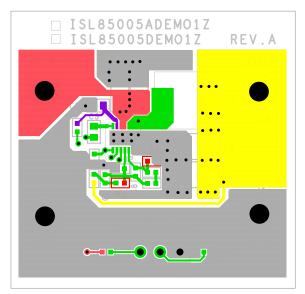

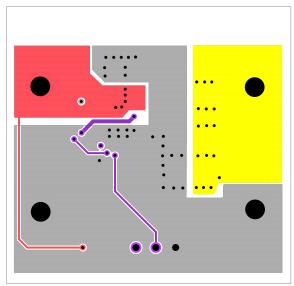

### ISL85005xDEMO1Z PCB Layout

FIGURE 4. TOP LAYER

FIGURE 5. LAYER 2

FIGURE 6. LAYER 3

FIGURE 7. BOTTOM LAYER

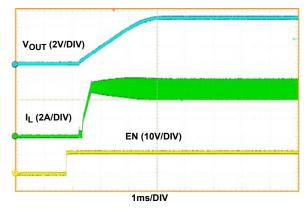

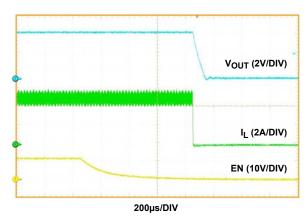

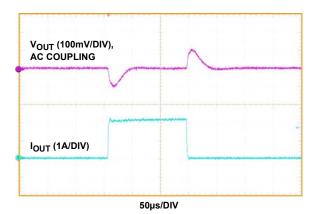

### $\textbf{Typical Performance Curves} \quad v_{\text{IN}} = \textbf{12V}, \ v_{\text{OUT}} = 5\text{V}, \ L = 3.3 \mu\text{H}, \ f_{\text{SW}} = 500 \text{kHz}, \ T_{\text{A}} = +25\,^{\circ}\text{C}, \ unless \ otherwise \ noted}.$

FIGURE 9. START-UP WITH EN,  $I_{OUT} = 5A$

FIGURE 10. SHUTDOWN WITH EN,  $I_{OUT} = 5A$

FIGURE 11. LOAD TRANSIENT, 0A ightarrow 2.5A ightarrow 0A, 2.5A/ $\mu s$

Intersil Corporation reserves the right to make changes in circuit design, software and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the document is current before proceeding.