## LDBL20

# 200 mA very low quiescent current linear regulator IC in (0.47x0.47) mm² STSTAMP™ package

Datasheet - production data

#### **Features**

- Input voltage from 1.5 to 5.5 V

- Ultra low dropout voltage (200 mV typ. at 200 mA load)

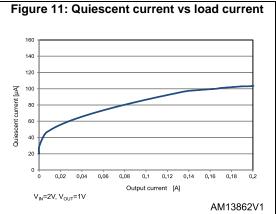

- Very low quiescent current (20 μA typ. at no-load, 0.03 μA typ. in off mode)

- Output voltage tolerance: ± 1.5% @ 25 °C

- 200 mA guaranteed output current

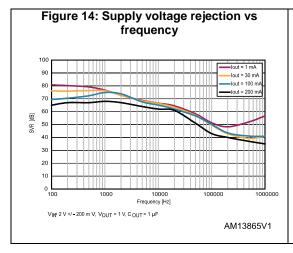

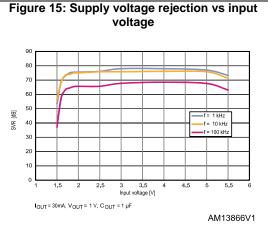

- High PSRR (80 dB@1 kHz, 50 db@ 100 kHz)

- Wide range of output voltages available on request: from 0.8 V up to 5.0 V in 50 mV step

- Logic-controlled electronic shutdown

- Internal soft-start

- Optional output voltage discharge feature

- Compatible with ceramic capacitor Cout = 0.47 μF

- Internal constant current and thermal protections

- Available in STSTAMP™ (0.47x0.47) mm² package

- Operating temperature range: -40 °C to 125 °C

### **Applications**

- Mobile phones

- Tablet

- Digital still cameras (DSC)

- Wearable devices

- Portable media players

### **Description**

The LDBL20 high accuracy voltage regulator provides 200 mA of maximum current from an input voltage ranging from 1.5 V to 5.5 V, with a typical dropout voltage of 200 mV.

It is available in the new STSTAMP™ package, allowing the maximum space saving.

The device is stabilized with a ceramic capacitor on the output. The ultra low drop voltage, low quiescent current and low noise features, together with the internal soft-start circuit, make the LDBL20 suitable for low power battery-operated applications.

An enable logic control function puts the LDBL20 in shutdown mode with a total current consumption lower than 0.2  $\mu$ A. Constant current and thermal protection are provided.

| Con | tents |

|-----|-------|

|-----|-------|

| 1  | Diagram            | ١                                            | 3  |  |  |  |  |

|----|--------------------|----------------------------------------------|----|--|--|--|--|

| 2  | Pin configuration4 |                                              |    |  |  |  |  |

| 3  |                    | application                                  |    |  |  |  |  |

| 4  | Maximu             | m ratings                                    | 6  |  |  |  |  |

| 5  | Electric           | al characteristics                           | 7  |  |  |  |  |

| 6  |                    | tion information                             |    |  |  |  |  |

|    | 6.1                | Soft-start function                          |    |  |  |  |  |

|    | 6.2                | Output discharge function                    | 9  |  |  |  |  |

|    | 6.3                | Input output capacitors                      | 9  |  |  |  |  |

| 7  | Typical            | characteristics                              | 10 |  |  |  |  |

| 8  | Recomn             | nendation on PCB assembly                    | 14 |  |  |  |  |

|    | 8.1                | PCB design recommendations                   | 14 |  |  |  |  |

|    | 8.2                | Stencil                                      | 14 |  |  |  |  |

|    | 8.3                | Solder paste                                 | 14 |  |  |  |  |

|    | 8.4                | Placement                                    | 14 |  |  |  |  |

|    | 8.5                | Reflow profile                               | 15 |  |  |  |  |

| 9  | Package            | e information                                | 16 |  |  |  |  |

|    | 9.1                | STSTAMP™ (0.47x0.47) mm² package information | 17 |  |  |  |  |

| 10 | Ordering           | g information                                | 19 |  |  |  |  |

|    | 10.1               | Marking information                          | 19 |  |  |  |  |

| 11 | Revisio            | n history                                    | 20 |  |  |  |  |

LDBL20 Diagram

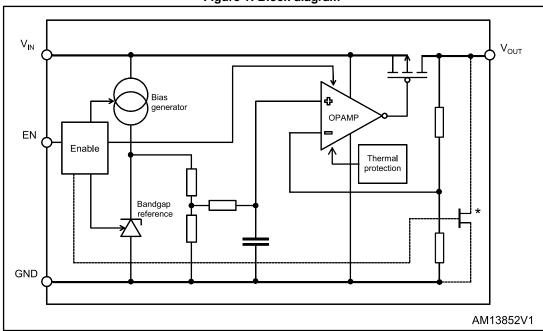

# 1 Diagram

Figure 1: Block diagram

The output discharge MOSFET is optional.

Pin configuration LDBL20

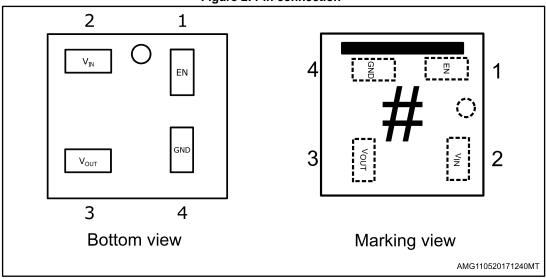

# 2 Pin configuration

Figure 2: Pin connection

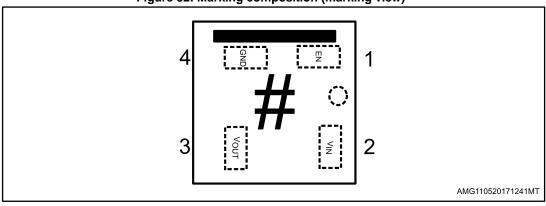

"#" indicates the marking digit. Refer to *Table 7: "Order code"*. The top horizontal bar identifies pin 1 on top right corner.

Table 1: Pin description

| Pin | Symbol | Function                                              |  |

|-----|--------|-------------------------------------------------------|--|

| 3   | OUT    | Output voltage                                        |  |

| 4   | GND    | Common ground                                         |  |

| 1   | EN     | Enable pin logic input: low = shutdown, high = active |  |

| 2   | IN     | Input voltage                                         |  |

LDBL20 Typical application

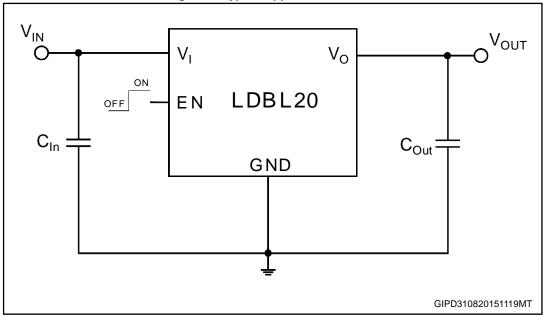

# 3 Typical application

Figure 3: Typical application circuits

Maximum ratings LDBL20

# 4 Maximum ratings

Table 2: Absolute maximum ratings

| Symbol           | Parameter                            | Value                          | Unit |

|------------------|--------------------------------------|--------------------------------|------|

| Vin              | Input voltage                        | - 0.3 to 7                     | V    |

| V <sub>OUT</sub> | Output voltage                       | - 0.3 to V <sub>IN</sub> + 0.3 | V    |

| VEN              | Enable input voltage                 | - 0.3 to 7                     | V    |

| Іоит             | Output current                       | Internally limited             | mA   |

| P <sub>D</sub>   | Power dissipation                    | Internally limited             | mW   |

| Tstg             | Storage temperature range            | - 40 to 150                    | °C   |

| T <sub>OP</sub>  | Operating junction temperature range | - 40 to 125                    | °C   |

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. All values are referred to GND.

Table 3: ESD performance

| Symbol | Parameter                 | Test conditions | Value | Unit |

|--------|---------------------------|-----------------|-------|------|

|        | SD ESD protection voltage | НВМ             | 4     | kV   |

| ESD    |                           | MM              | 400   | V    |

|        |                           | CDM             | 500   | V    |

**Table 4: Thermal performance**

| Symbol            | Parameter                           | Value | Unit |

|-------------------|-------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient | 230   | °C/W |

LDBL20 Electrical characteristics

### 5 Electrical characteristics

$T_J=25~^{\circ}C,~V_{IN}=V_{OUT(NOM)}$  + 1 V or 1.5 V, whichever is greater,  $C_{IN}=C_{OUT}=1~\mu\text{F},~I_{OUT}=1~m\text{A},~V_{EN}=V_{IN},~unless~otherwise~specified.}$

Table 5: LDBL20 electrical characteristics

| Symbol           | Parameter                                                                                                           | Test conditions                                                                   | Min. | Тур. | Max. | Unit       |

|------------------|---------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------|------|------|------|------------|

| Vin              | Operating input voltage                                                                                             |                                                                                   | 1.5  |      | 5.5  | V          |

| V <sub>оит</sub> | V goourgov                                                                                                          | I <sub>OUT</sub> = 1 mA,<br>T <sub>J</sub> = 25 °C                                | -1.5 |      | +1.5 | %          |

| 1001             | V <sub>OUT</sub> accuracy                                                                                           | I <sub>OUT</sub> = 1 mA,<br>-40 °C <t<sub>J&lt;125 °C</t<sub>                     | -3   |      | +3   | %          |

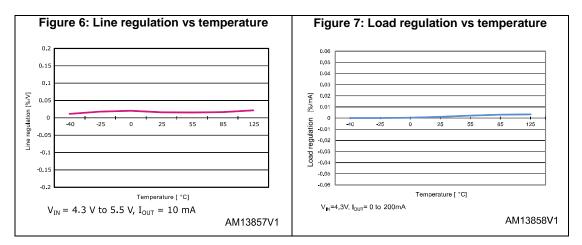

| ΔVουτ            | Static line regulation <sup>(1)</sup>                                                                               | $V_{OUT(NOM)}$ + 1 V $\leq$ V <sub>IN</sub> $\leq$ 5.5 V,<br>$I_{OUT}$ = 10 mA    |      | 0.02 |      | %/V        |

|                  | regulation                                                                                                          | -40 °C <tj<125 td="" °c<=""><td></td><td></td><td>0.2</td><td></td></tj<125>      |      |      | 0.2  |            |

| ΔVουτ            | Static load                                                                                                         | I <sub>OUT</sub> = 0 mA to 200 mA                                                 |      | 10   |      | mV         |

|                  | regulation                                                                                                          | -40 °C <t<sub>J&lt;125 °C</t<sub>                                                 |      |      | 0.01 | %/mA       |

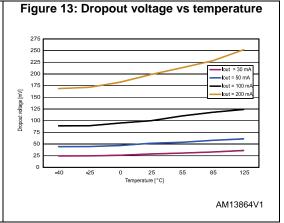

|                  |                                                                                                                     | louт = 30 mA,<br>Vouт = 2.8 V                                                     |      | 35   |      |            |

| VDROP            | Dropout voltage                                                                                                     | Iout = 200 mA,<br>Vout = 2.8 V<br>-40 °C <t<sub>J&lt;125 °C</t<sub>               |      | 200  | 350  | mV<br>350  |

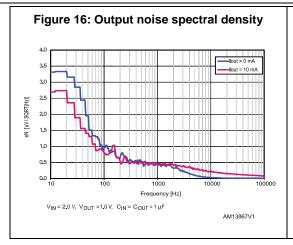

| ем               | Output noise voltage                                                                                                | 10 Hz to 100 kHz,<br>I <sub>OUT</sub> = 10 mA                                     |      | 45   |      | µVrms/Vout |

|                  | Supply voltage                                                                                                      | VIN = VOUT(NOM)+ 1 V +/- VRIPPLE VRIPPLE = 0.2 V Frequency = 1 kHz IOUT = 30 mA   |      | 80   |      |            |

| SVR              | rejection                                                                                                           | VIN = VOUT(NOM)+ 1 V +/- VRIPPLE VRIPPLE = 0.2 V Frequency = 100 kHz IOUT = 30 mA |      | 55   | 55   | dB         |

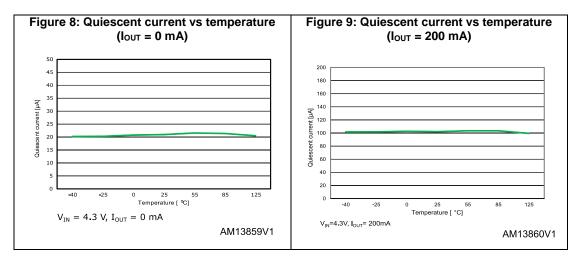

| ΙQ               | Quiescent                                                                                                           | Iout = 0 mA                                                                       |      | 20   | 40   | ^          |

| iQ               | current                                                                                                             | louт = 200 mA                                                                     |      | 100  |      | μΑ         |

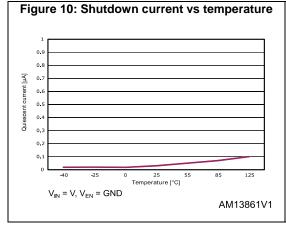

| Standby          | Standby current                                                                                                     | $V_{IN}$ input current in OFF mode: $V_{EN} = GND$                                |      | 0.03 | 0.2  | μΑ         |

| Isc              | Short-circuit current                                                                                               | R <sub>L</sub> = 0                                                                | 250  | 350  |      | mA         |

| Ron              | Output voltage<br>discharge<br>MOSFET                                                                               |                                                                                   |      | 100  |      | Ω          |

| Ven              | logic low $-40 ^{\circ}\text{C} < \text{T}_{\text{J}} < \text{Enable input}$ $V_{\text{IN}} = 1.5 ^{\circ}\text{V}$ | V <sub>IN</sub> = 1.5 V to 5.5 V<br>-40 °C <t<sub>J&lt;125 °C</t<sub>             |      |      | 0.4  | V          |

| VEN              |                                                                                                                     | V <sub>IN</sub> = 1.5 V to 5.5 V<br>-40 °C <t<sub>J&lt;125 °C</t<sub>             | 1    |      |      |            |

| Symbol             | Parameter                | Test conditions   | Min. | Тур. | Max. | Unit |

|--------------------|--------------------------|-------------------|------|------|------|------|

| len                | Enable pin input current | $V_{EN} = V_{IN}$ |      |      | 100  | nA   |

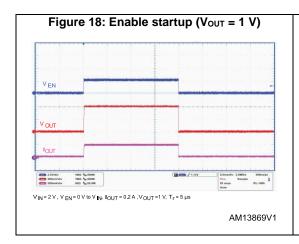

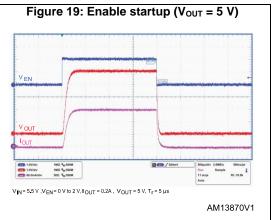

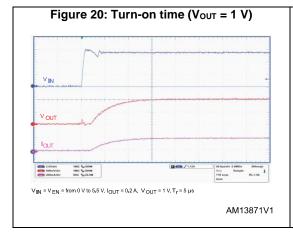

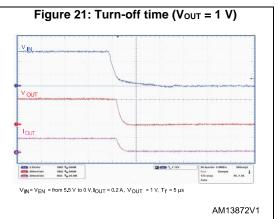

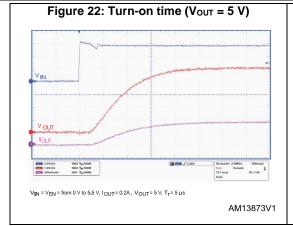

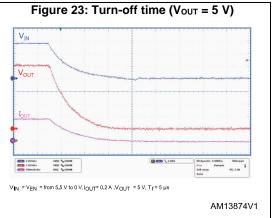

| Ton <sup>(2)</sup> | Turn-on time             |                   |      | 100  |      | μs   |

| Tshon              | Thermal shutdown         |                   |      | 160  |      | °C   |

|                    | Hysteresis               |                   |      | 20   |      |      |

| Соит               | Output capacitor         | Capacitance       | 0.47 |      | 22   | μF   |

#### Notes:

$<sup>^{(1)}</sup>$ Not applicable for Vout(nom) > 4.5 V

$<sup>^{(2)}</sup>$ Turn-on time is time measured between the enable input just exceeding VEN high value and the output voltage just reaching 95 % of its nominal value

### 6 Application information

#### 6.1 Soft-start function

The LDBL20 has an internal soft-start circuit. By increasing the startup time up to 100  $\mu$ s, without the need of any external soft-start capacitor, this feature keeps the regulator inrush current at startup under control.

### 6.2 Output discharge function

The LDBL20 integrates a MOSFET connected between V<sub>OUT</sub> and GND. This transistor is activated when the EN pin goes to low logic level and has the function to quickly discharge the output capacitor when the device is disabled by the user.

The device is available with or without the auto-discharge feature. See *Table 7: "Order code"*.

### 6.3 Input output capacitors

The LDBL20 requires external capacitors to assure the regulator control loop stability.

Any good quality ceramic capacitor can be used but, the X5R and the X7R are suggested since they guarantee a very stable combination of capacitance and ESR overtemperature.

Locating the input/output capacitors as closer as possible to the relative pins is recommended.

The LDBL20 requires an input capacitor with a minimum value of 1 µF.

This capacitor must be located as closer as possible to the input pin of the device and returned to a clean analog ground.

The control loop of the LDBL20 is designed to work with an output ceramic capacitor.

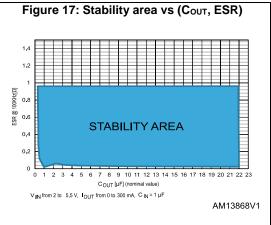

This capacitor must meet the requirements of minimum capacitance and equivalent series resistance (ESR), as shown in *Figure 17: "Stability area vs (COUT, ESR)"*. To assure stability, the output capacitor must maintain its ESR and capacitance in the stable region, over the full operating temperature range.

The LDBL20 shows stability with a minimum effective output capacitance of 220 nF.

However, to keep stability in all operating conditions (temperature, input voltage and load variations), a minimum output capacitor of  $0.47 \, \mu F$  is recommended.

The suggested combination of 1  $\mu$ F input and output capacitors offers a good compromise among the stability of the regulator, optimum transient response and total PCB area occupation.

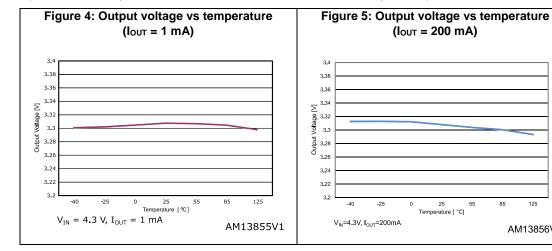

#### **Typical characteristics** 7

(C<sub>IN</sub> = C<sub>OUT</sub> = 1  $\mu$ F, V<sub>EN</sub> to V<sub>IN</sub>, T<sub>J</sub> = 25 °C unless otherwise specified)

AM13856V1

LDBL20 Typical characteristics

Figure 12: Quiescent current vs input voltage

Typical characteristics LDBL20

12/21

LDBL20 Typical characteristics

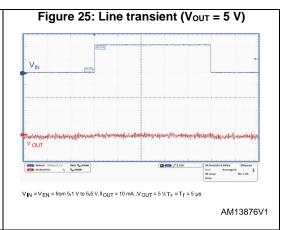

Figure 24: Line transient (V<sub>OUT</sub> = 1 V)

V<sub>IN</sub>

V<sub>IN</sub> = V<sub>EN</sub> = from 2 V to 3 V . I<sub>OUT</sub> = 10 mA . V<sub>OUT</sub> = 1 V. T<sub>I</sub> = T<sub>I</sub> = 5 µs

AM13875V1

### 8 Recommendation on PCB assembly

### 8.1 PCB design recommendations

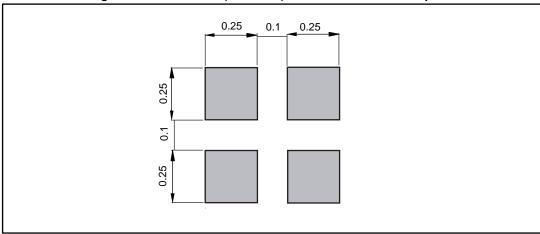

- PCB PAD design: non solder mask defined

- PCB pad size: see drawing in Figure 30: "STSTAMP™ (0.47x0.47) mm² recommended footprint"

- Solder mask opening: 50 µm between the edge of the pad and the edge of the solder mask

- To keep under control the solder paste amount, closed vias are recommended instead of open vias

- The position of tracks and open vias in the solder area should be well balanced. A symmetrical layout is recommended, to reduce the effect of tilt phenomena caused by asymmetrical solder paste amount due to the solder flowing away

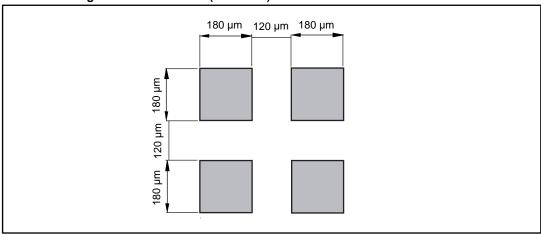

#### 8.2 Stencil

- Stencil aperture: see drawing in Figure 31: "STSTAMP™ (0.47x0.47) mm² recommended solder stencil"

- Stencil thickness: 75 μm

### 8.3 Solder paste

- 95.8% Sn, 3.5% Ag, 0.7% Cu solder paste

- Halide-free flux qualification ROL0 according to ANSI/J-STD-004

- "No clean" solder paste is recommended.

- Offers a high tack force to resist component movement during high speed

- Solder paste with fine particles: powder particle size is 20-45 μm.• type 4

#### 8.4 Placement

- Manual positioning is not recommended

- It is recommended to use the lead recognition capabilities of the placement system, not the outline centering

- Standard tolerance of ± 0.05 mm is recommended

- 3.5 N placement force is recommended. Too much placement force can lead to squeezed out solder paste and cause solder joints to short. Too low placement force can lead to insufficient contact between package and solder paste that could cause open solder joints or badly centered packages

- To improve the package placement accuracy, a bottom side optical control should be performed with a high resolution tool

- For assembly, a perfect supporting of the PCB (all the more on flexible PCB) is recommended during solder paste printing, pick and place and reflow soldering by using optimized tools

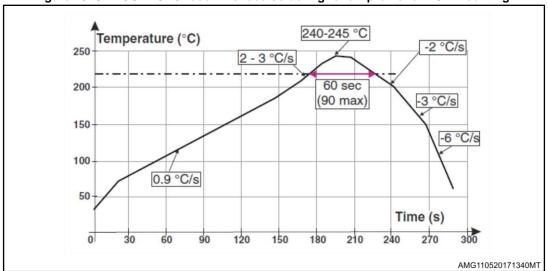

### 8.5 Reflow profile

Figure 28: ST ECOPACK® recommended soldering reflow profile for PCB mounting

Minimize air convection currents in the reflow oven to avoid component movement. Maximum soldering profile corresponds to the latest IPC/JEDEC J-STD-020.

Package information LDBL20

# 9 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK® packages, depending on their level of environmental compliance. ECOPACK® specifications, grade definitions and product status are available at: **www.st.com**. ECOPACK® is an ST trademark.

LDBL20 Package information

# 9.1 STSTAMP™ (0.47x0.47) mm² package information

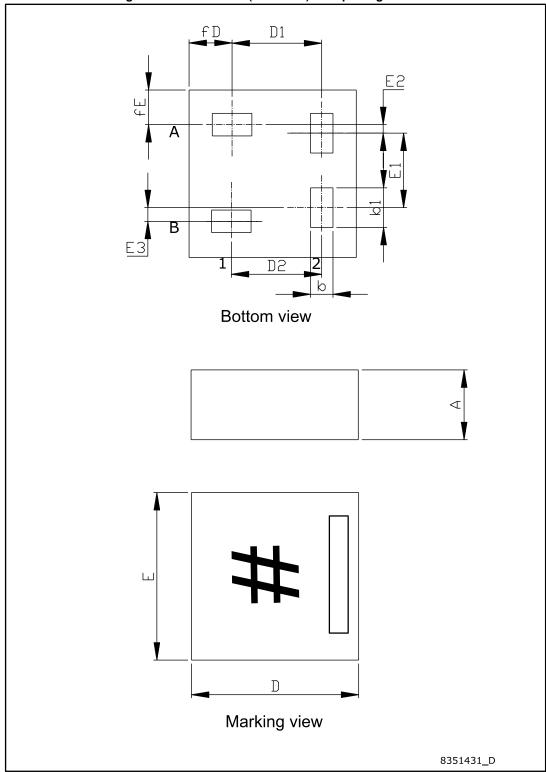

Figure 29: STSTAMP™ (0.47x0.47) mm² package outline

Table 6: STSTAMP™ (0.47x0.47) mm² mechanical data

| Dim  |       | mm    |       |

|------|-------|-------|-------|

| Dim. | Min.  | Тур.  | Max.  |

| А    | 0.18  | 0.200 | 0.220 |

| b    | 0.060 | 0.065 | 0.070 |

| b1   | 0.109 | 0.114 | 0.119 |

| Е    | 0.450 | 0.480 | 0.510 |

| E1   | 0.208 | 0.213 | 0.218 |

| E2   | 0.019 | 0.024 | 0.029 |

| E3   | 0.034 | 0.039 | 0.044 |

| D    | 0.450 | 0.480 | 0.510 |

| D1   | 0.252 | 0.257 | 0.262 |

| D2   | 0.255 | 0.260 | 0.265 |

| fE   | 0.095 | 0.101 | 0.106 |

| fD   | 0.106 | 0.111 | 0.116 |

Figure 30: STSTAMP™ (0.47x0.47) mm² recommended footprint

Figure 31: STSTAMP™ (0.47x0.47) mm² recommended solder stencil

LDBL20 Ordering information

# 10 Ordering information

Table 7: Order code

| Order code  | Output voltage (V) | Auto-discharge | Marking | Packing       |

|-------------|--------------------|----------------|---------|---------------|

| LDBL20D-18R | 1.8                |                | А       |               |

| LDBL20D-25R | 2.5                | Yes            | В       | Tape and reel |

| LDBL20D-33R | 3.3                |                | С       |               |

# 10.1 Marking information

Figure 32: Marking composition (marking view)

The symbol "#" indicates the marking digit, as per Table 7: "Order code".

Revision history LDBL20

# 11 Revision history

**Table 8: Document revision history**

| Date        | Revision | Changes                                                                                                                                                                                                     |

|-------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 10-Nov-2015 | 1        | Initial release                                                                                                                                                                                             |

| 02-Aug-2017 | 2        | Updated Section 2: "Pin configuration", Table 5: "LDBL20 electrical characteristics".  Added Section 8: "Recommendation on PCB assembly".  Updated Section 10: "Ordering information".  Minor text changes. |

#### **IMPORTANT NOTICE - PLEASE READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgement.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of Purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2017 STMicroelectronics - All rights reserved