# Half Bridge Gate Driver(Isolated High & Non-Isolated Low)

# NCD57200

The NCD57200 is a high voltage gate driver with one non-isolated low side gate driver and one galvanic isolated high or low side gate driver. It can directly drive two IGBTs in a half bridge configuration. Isolated high side driver can be powered with an isolated power supply or with Bootstrap technique from the low side power supply.

The galvanic isolation for the high side gate driver guarantees reliable switching in high power applications for IGBTs that operate up to 800 V, at high dv/dt. The optimized output stages provide a mean of reducing IGBT losses. Its features include two independent inputs with deadtime and interlock, accurate asymmetric UVLOs, and short and matched propagation delays. The NCD57200 operates with its  $V_{CC}/V_{B}$  up to 20 V.

#### **Features**

- High Peak Current Output (+1.9 A / -2.3 A)

- Low Output Voltage Drop for Enhanced IGBT Conduction

- Secured Output Low State without V<sub>DD/</sub>V<sub>B</sub>

- Floating Channel for Bootstrap Operation up to +800 V

- CMTI up to 50 kV / us

- Reliable Operation for V<sub>S</sub> Negative Swing to -800 V

- VDD & VBS Supply Range up to 20 V

- 3.3 V, 5 V, and 15 V Logic Input

- Asymmetric Under Voltage Lockout Thresholds for High Side and Low Side

- Matched Propagation Delay 90 ns

- Built-in 20 ns Minimum Pulse Width Filter (or Input Noise Filter)

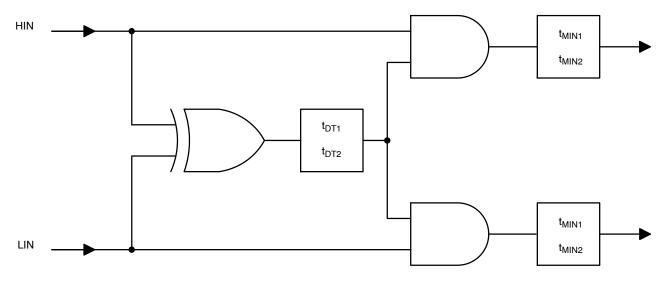

- Built-in 340 ns Dead-Time and High and Low Inputs Interlock

- Output in Phase with Input Signal

- This Device is Pb–Free, Halogen Free/BFR Free and is RoHS Compliant

#### **Typical Applications**

- Fans, Pumps

- Home Appliances

- Consumer Electronics

- General Purpose Half Bridge Applications

### ON Semiconductor®

www.onsemi.com

SOIC-8 NB CASE 751-07

#### **MARKING DIAGRAM**

NCD57200 = Specific Device Code

A = Assembly Location

L = Wafer Lot

Y = Year

W = Work Week

■ Pb-Free Package

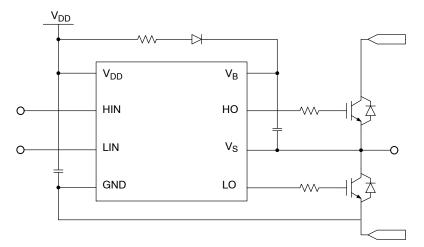

#### PIN CONNECTIONS

#### **ORDERING INFORMATION**

See detailed ordering and shipping information on page 8 of this data sheet.

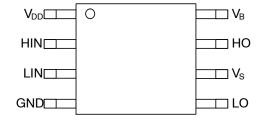

Figure 1. Simplified Block Diagram

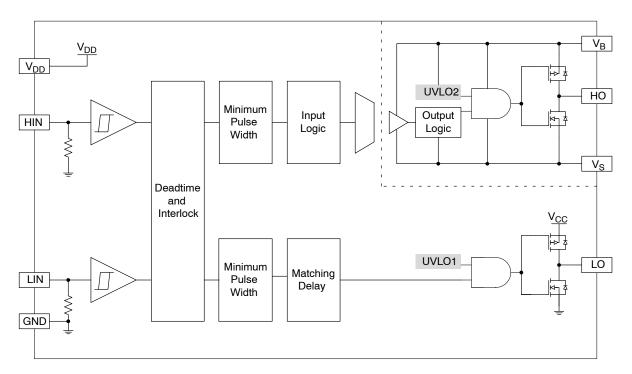

Figure 2. Simplified Application Schematics

**Table 1. FUNCTION DESCRIPTION**

| Pin Name       | No. | I/O   | Description                                                                                                                                                                                                                                                                                    |

|----------------|-----|-------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

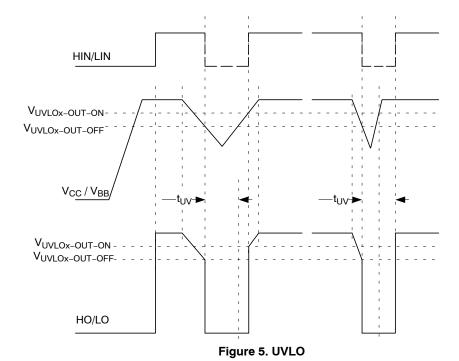

| $V_{DD}$       | 1   | Power | Low side and main power supply. A good quality bypassing capacitor is required from this pin to GND and should be placed close to the pins for best results.  The under voltage lockout (UVLO) circuit enables the device to operate at power                                                  |

|                |     |       | on when a typical supply voltage higher than $V_{UVLO1-OUT-ON}$ is present. Please see Figure 5 for more details. A filter time of typical 1.5 $\mu$ s helps to suppress noise on $V_{DD}$ pin.                                                                                                |

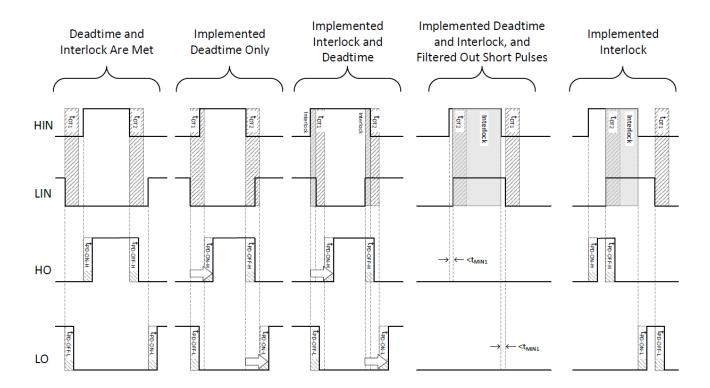

| HIN            | 2   | ı     | High side non-inverting gate driver input. It has an equivalent pull–down resistor of 125 k $\Omega$ to ensure that output is low in the absence of an input signal. A minimum positive or negative going pulse width is required at HIN before HO reacts.                                     |

|                |     |       | It adopts 3.3 V logic signal thresholds for input voltage up to $V_{DD}$ . There is deadtime and interlocking logic between HIN and LIN.                                                                                                                                                       |

| LIN            | 3   | I     | Low side non-inverting gate driver input. It has an equivalent pull–down resistor of 125 k $\Omega$ to ensure that output is low in the absence of an input signal. A minimum positive or negative going pulse width is required at LIN before LO reacts.                                      |

|                |     |       | It adopts 3.3 V logic signal thresholds for input voltage up to $V_{DD}$ . There is deadtime and interlocking logic between HIN and LIN.                                                                                                                                                       |

| GND            | 4   | Power | Logic ground and low side driver return.                                                                                                                                                                                                                                                       |

| LO             | 5   | 0     | Low side driver output that provides the appropriate drive voltage and source/<br>sink current to the IGBT gate. LO is actively pulled low during startup and under<br>UVLO1 condition. There is deadtime and interlocking logic to prevent unintended<br>HO and LO cross conduction.          |

| V <sub>S</sub> | 6   | Power | Bootstrap return or high side floating supply offset.                                                                                                                                                                                                                                          |

| НО             | 7   | 0     | Galvanic isolated high side driver output that provides the appropriate drive voltage and source/sink current to the IGBT gate. HO is actively pulled low during startup and under UVLO2 condition. There is deadtime and interlocking logic to prevent unintended HO and LO cross conduction. |

| V <sub>B</sub> | 8   | Power | Bootstrap or high side floating power supply. A good quality bypassing capacitor is required from this pin to $V_S$ and should be placed close to the pins for best results.                                                                                                                   |

|                |     |       | The under voltage lockout (UVLO) circuit enables the device to operate at power on when a typical supply voltage higher than $V_{\rm UVLO2-OUT-ON}$ is present. Please see Figure 5 for more details. A filter time of typical 1.5 $\mu$ s helps to suppress noise on $V_B$ pin.               |

Table 2. ABSOLUTE MAXIMUM RATINGS (Note 1) Over operating free-air temperature range unless otherwise noted

| Parameter                                          | Symbol              | Minimum             | Maximum              | Unit |

|----------------------------------------------------|---------------------|---------------------|----------------------|------|

| High-Side Offset Voltage                           | .,                  | -900                | 900                  | .,,  |

| High-Side Offset Voltage (t <sub>p</sub> < 500 ns) | V <sub>S</sub>      | -900                | 900                  |      |

| High-Side Supply Voltage                           | V                   | -900                | 900                  | V    |

| High-Side Supply Voltage (t <sub>p</sub> < 500 ns) | V <sub>B</sub>      | -900                | 900                  | _ V  |

| Low-Side and Logic-Fixed Supply Voltage            | V <sub>DD</sub>     | -0.3                | 25                   | V    |

| High-Side Floating Supply Voltage                  | V <sub>BS</sub>     | -0.3                | 25                   | V    |

| High-Side Floating Output Voltage V <sub>HO</sub>  | V <sub>HO</sub>     | V <sub>S</sub> -0.3 | V <sub>B</sub> +0.3  | ٧    |

| Low-Side Floating Output Voltage V <sub>LO</sub>   | V <sub>LO</sub>     | -0.3                | V <sub>DD</sub> +0.3 | V    |

| Logic Input Voltage (HIN, LIN)                     | V <sub>IN</sub>     | -0.3                | V <sub>DD</sub> +0.3 | V    |

| Allowable Offset Voltage Slew Rate                 | dV <sub>S</sub> /dt |                     | ±50                  | V/ns |

| Maximum Junction Temperature                       | TJ(max)             | -40                 | 150                  | °C   |

| Storage Temperature Range                          | TSTG                | -65                 | 150                  | °C   |

| ESD Capability, Human Body Model (Note 2)          | ESDHBM              |                     | ±4                   | kV   |

| ESD Capability, Charged Device Model (Note 2)      | ESDCDM              |                     | ±2                   | kV   |

| Moisture Sensitivity Level                         | MSL                 |                     | 1                    | -    |

| Lead Temperature Soldering Reflow                  | TSLD                |                     | 260                  | °C   |

| (SMD Styles Only), Pb-Free Versions (Note 3)       |                     |                     |                      |      |

Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.

1. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 2. This device series incorporates ESD protection and is tested by the following methods: ESD Human Body Model tested per AEC-Q100-002 (EIA/JESD22-A114).

- ESD Charged Device Model tested per AEC-Q100-011 (EIA/JESD22-C101).

- Latchup Current Maximum Rating: ≤ 100 mA per JEDEC standard: JESD78, 125°C.

- 3. For information, please refer to our Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **Table 3. THERMAL CHARACTERISTICS**

| Parameter                                                                                | Symbol | Value | Unit |

|------------------------------------------------------------------------------------------|--------|-------|------|

| Thermal Characteristics, SOIC-8 (Note 4)<br>Thermal Resistance, Junction-to-Air (Note 5) | Reja   | 167   | °C/W |

- 4. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

- 5. Values based on copper area of 100 mm2 (or 0.16 in2) of 1 oz copper thickness and FR4 PCB substrate.

Table 4. RECOMMENDED OPERATING RANGES (Note 6)

| Parameter                       | Symbol          | Min                   | Max                | Unit |

|---------------------------------|-----------------|-----------------------|--------------------|------|

| High-Side Supply Voltage        | V <sub>B</sub>  | V <sub>S</sub> +UVLO2 | V <sub>S</sub> +20 | V    |

| High-Side Supply Offset Voltage | V <sub>S</sub>  | -800                  | 800                | V    |

| High-Side (HO) Output Voltage   | V <sub>HO</sub> | V <sub>S</sub>        | V <sub>B</sub>     | V    |

| Low-Side (LO) Output Voltage    | V <sub>LO</sub> | GND                   | $V_{DD}$           | V    |

| Logic Input Voltage (HIN, LIN)  | V <sub>IN</sub> | GND                   | $V_{DD}$           | V    |

| Low-Side Supply Voltage         | V <sub>DD</sub> | UVLO1                 | 20                 | V    |

| Ambient Temperature             | T <sub>A</sub>  | -40                   | +125               | °C   |

Functional operation above the stresses listed in the Recommended Operating Ranges is not implied. Extended exposure to stresses beyond the Recommended Operating Ranges limits may affect device reliability.

6. Refer to ELECTRICAL CHARACTERISTICS and APPLICATION INFORMATION for Safe Operating Area.

$\begin{tabular}{ll} \textbf{Table 5. ELECTRICAL CHARACTERISTICS}$ $V_{DD} = V_{BS} = 15$ V. \\ For typical values $T_A = 25^{\circ}$C, for min/max values, $T_A$ is the operating ambient temperature range that applies, unless otherwise noted. \\ \end{tabular}$

| Parameter                                                            | Test Conditions                                                                                                                             | Symbol                                  | Min  | Тур  | Max        | Unit |

|----------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------|------|------|------------|------|

| VOLTAGE SUPPLY                                                       |                                                                                                                                             |                                         |      |      |            |      |

| V <sub>BS</sub> Supply Under Voltage<br>Output Enabled               |                                                                                                                                             | V <sub>UVLO2-OUT</sub><br>-ON           | 11   | 11.5 | 12         | V    |

| V <sub>BS</sub> Supply Under Voltage<br>Output Disabled              |                                                                                                                                             | V <sub>UVLO2</sub> OUT<br>OFF           | 10   | 10.5 | 11         | V    |

| V <sub>BS</sub> Supply Voltage Output<br>Enabled/Disabled Hysteresis |                                                                                                                                             | V <sub>UVLO2-HYST</sub>                 |      | 1.0  |            | V    |

| V <sub>DD</sub> Supply Under Voltage<br>Output Enabled               |                                                                                                                                             | V <sub>UVLO1</sub> OUT                  | 12   | 12.5 | 13         | V    |

| V <sub>DD</sub> Supply Under Voltage<br>Output Disabled              |                                                                                                                                             | V <sub>UVLO1-OUT</sub>                  | 11   | 11.5 | 12         | V    |

| V <sub>DD</sub> Supply Voltage Output<br>Enabled/Disabled Hysteresis |                                                                                                                                             | V <sub>UVLO1-HYST</sub>                 |      | 1.0  |            | V    |

| Leakage Current Between $V_{\mbox{\scriptsize S}}$ and GND           | $V_S = \pm 800 \text{ V}, T_A = 25^{\circ}\text{C}$<br>$V_S = \pm 800 \text{ V}, T_A = -40^{\circ}\text{C} \text{ to } 125^{\circ}\text{C}$ | I <sub>HV_LEAK1</sub>                   |      | 20   | 200<br>600 | nA   |

| Quiescent Current V <sub>BS</sub> Supply (V <sub>B</sub> Only)       | HO = Low                                                                                                                                    | I <sub>QBS1</sub>                       |      | 260  | 325        | μΑ   |

| Quiescent Current $V_{\rm BS}$ Supply (V <sub>B</sub> Only)          | HO = High                                                                                                                                   | I <sub>QBS2</sub>                       |      | 330  | 440        | μΑ   |

| Quiescent Current $V_{\rm DD}$ Supply ( $V_{\rm DD}$ Only)           | V <sub>LIN</sub> = Float, V <sub>HIN</sub> = 0 V,                                                                                           | I <sub>QDD1</sub>                       |      | 380  | 440        | μΑ   |

| Quiescent Current V <sub>DD</sub> Supply (V <sub>DD</sub> Only)      | V <sub>LIN</sub> = 3.3 V, V <sub>HIN</sub> = 0 V,                                                                                           | I <sub>QDD2</sub>                       |      | 440  | 500        | μΑ   |

| Quiescent Current $V_{\rm DD}$ Supply ( $V_{\rm DD}$ Only)           | V <sub>LIN</sub> = 0 V, V <sub>HIN</sub> = 3.3 V,                                                                                           | I <sub>QDD3</sub>                       |      | 2.4  | 3          | mA   |

| LOGIC INPUT                                                          | •                                                                                                                                           | •                                       |      | •    |            |      |

| Low Level Input Voltage                                              |                                                                                                                                             | V <sub>IL</sub>                         |      |      | 0.9        | V    |

| High Level Input Voltage                                             |                                                                                                                                             | V <sub>IH</sub>                         | 2.4  |      |            | V    |

| Logic "1" Input Bias Current                                         | V <sub>LIN</sub> = 3.3 V, V <sub>HIN</sub> = 3.3 V                                                                                          | I <sub>LIN1+</sub> , I <sub>HIN1+</sub> |      | 25   | 50         | μΑ   |

| Logic "1" Input Bias Current                                         | VLIN = 20 V, VHIN = 20 V,<br>VDD = VBS = 20 V                                                                                               | ILIN2+, IHIN2+                          |      | 100  | 150        | μΑ   |

| Logic "0" Input Bias Current                                         | V <sub>LIN</sub> = 0 V, V <sub>HIN</sub> = 0 V                                                                                              | I <sub>LIN</sub> -, I <sub>HIN</sub> -  |      | 40   | 100        | nA   |

| DRIVER OUTPUT                                                        |                                                                                                                                             |                                         |      |      |            |      |

| Output Low State                                                     | I <sub>SINK</sub> = 200 mA, T <sub>A</sub> = 25°C                                                                                           | V <sub>OL1</sub>                        |      | 0.2  | 0.3        | V    |

|                                                                      | I <sub>SINK</sub> = 200 mA,<br>T <sub>A</sub> = -40°C to 125°C                                                                              | V <sub>OL2</sub>                        |      |      | 0.5        |      |

| Output High State                                                    | I <sub>SRC</sub> = 200 mA, T <sub>A</sub> = 25°C                                                                                            | V <sub>OH1</sub>                        | 14.4 | 14.5 |            | V    |

|                                                                      | I <sub>SRC</sub> = 200 mA,<br>T <sub>A</sub> = -40°C to 125°C                                                                               | V <sub>OH2</sub>                        | 14   |      |            |      |

| Peak Driver Current, Sink                                            | V <sub>HO</sub> = V <sub>LO</sub> = 15 V                                                                                                    | I <sub>PK-SNK1</sub>                    |      | 2.3  |            | Α    |

| (Note 7)                                                             | V <sub>HO</sub> = V <sub>LO</sub> = 9 V<br>(near Miller Plateau)                                                                            | I <sub>PK-SNK2</sub>                    |      | 2.1  |            |      |

| Peak Driver Current, Source                                          | V <sub>HO</sub> = V <sub>LO</sub> = 0 V                                                                                                     | I <sub>PK-SRC1</sub>                    |      | 1.9  |            | Α    |

| (Note 7)                                                             | V <sub>HO</sub> = V <sub>LO</sub> = 9 V<br>(near Miller Plateau)                                                                            | I <sub>PK-SRC2</sub>                    |      | 1.5  |            |      |

Table 5. ELECTRICAL CHARACTERISTICS  $V_{DD}$  =  $V_{BS}$  = 15 V.

For typical values  $T_A = 25^{\circ}C$ , for min/max values,  $T_A$  is the operating ambient temperature range that applies, unless otherwise noted.

| Parameter                                                                                   | Test Conditions                                                                      | Symbol                                | Min | Тур  | Max | Unit |

|---------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------|-----|------|-----|------|

| IGBT SHORT CIRCUIT CLAMPING                                                                 |                                                                                      |                                       |     |      |     |      |

| Clamping Voltage (V <sub>HO</sub> – V <sub>B</sub> ) / (V <sub>LO</sub> – V <sub>DD</sub> ) | $I_{HO}$ = 100 mA, $I_{LO}$ = 100 mA<br>(pulse test, $t_{CLPmax}$ = 10 μs)           | V <sub>CLAMP</sub> -OUT               |     | 0.8  | 1.3 | V    |

| DYNAMIC CHARACTERISTIC                                                                      |                                                                                      |                                       |     |      |     |      |

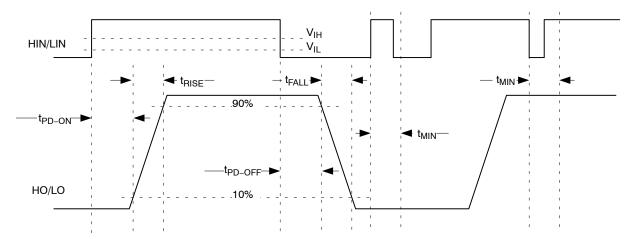

| HO High Propagation Delay                                                                   | C <sub>LOAD</sub> = 1 nF, V <sub>IH</sub> to 10% of Output<br>Change for PW > 150 ns | t <sub>PD-ON-H</sub>                  | 60  | 90   | 110 | ns   |

| HO Low Propagation Delay                                                                    | C <sub>LOAD</sub> = 1 nF, V <sub>IL</sub> to 90% of Output<br>Change for PW > 150 ns | t <sub>PD-OFF-H</sub>                 | 60  | 90   | 110 | ns   |

| Propagation Delay Distortion(HS)<br>(= t <sub>PD-ON</sub> - t <sub>PD-OFF</sub> )           | PW >150 ns                                                                           | t <sub>DISTORT-H</sub>                | -25 | 0    | 25  | ns   |

| LO High Propagation Delay                                                                   | C <sub>LOAD</sub> = 1 nF, V <sub>IH</sub> to 10% of Output<br>Change for PW > 150 ns | t <sub>PD-ON-L</sub>                  | 60  | 90   | 110 | ns   |

| LO Low Propagation Delay                                                                    | C <sub>LOAD</sub> = 1 nF, V <sub>IL</sub> to 90% of Output<br>Change for PW > 150 ns | t <sub>PD-OFF-L</sub>                 | 60  | 90   | 110 | ns   |

| Propagation Delay Distortion(LS)<br>(= t <sub>PD-ON</sub> - t <sub>PD-OFF</sub> )           | PW >150 ns                                                                           | <sup>t</sup> DISTORT-L                | -25 | 0    | 25  | ns   |

| High Prop Delay Distortion between High and Low Sides                                       | PW > 150 ns                                                                          | t <sub>DISTORT-HLH</sub>              | -25 | 0    | 25  | ns   |

| Low Prop Delay Distortion between<br>High and Low Sides                                     | PW > 150 ns                                                                          | t <sub>DISTORT-HLL</sub>              | -25 | 0    | 25  | ns   |

| Rise Time(HS) (see timing diagram)                                                          | C <sub>LOAD</sub> = 1 nF,<br>10% to 90% of Output Change                             | t <sub>RISE-H</sub>                   |     | 13   |     | ns   |

| Fall Time(HS) (see timing diagram)                                                          | C <sub>LOAD</sub> = 1 nF,<br>90% to 10% of Output Change                             | t <sub>FALL-H</sub>                   |     | 8    |     | ns   |

| Rise Time(LS) (see timing diagram)                                                          | C <sub>LOAD</sub> = 1 nF,<br>10% to 90% of Output Change                             | t <sub>RISE-L</sub>                   |     | 13   |     | ns   |

| Fall Time(LS) (see timing diagram)                                                          | C <sub>LOAD</sub> = 1 nF,<br>90% to 10% of Output Change                             | t <sub>FALL-L</sub>                   |     | 8    |     | ns   |

| Deadtime, HO Delays                                                                         | V <sub>LIN/HIN</sub> = 0 V and 3.3 V                                                 | t <sub>DT1</sub>                      |     | 340  |     | ns   |

| Deadtime, LO Delays                                                                         | V <sub>LIN/HIN</sub> = 0 V and 3.3 V                                                 | t <sub>DT2</sub>                      |     | 350  |     | ns   |

| Deadtime Matching                                                                           |                                                                                      | t <sub>MDT</sub>                      |     | 10   |     | ns   |

| Minimum Pulse Width Filtering Time                                                          | T <sub>A</sub> = 25°C                                                                | t <sub>MIN1</sub> , t <sub>MIN2</sub> | 10  |      | 40  | ns   |

| UVLO Fall Delay (HO and LO)                                                                 |                                                                                      | t <sub>UV1</sub>                      |     | 1300 |     | ns   |

| UVLO Rise Delay (HO and LO)                                                                 |                                                                                      | t <sub>UV2</sub>                      |     | 1100 |     | ns   |

Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.

7. Values based on design and/or characterization.

Figure 3. Propagation Delay, Rise and Fall Time

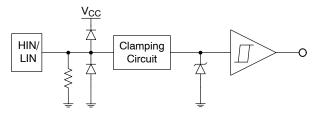

Figure 4. Input Pin Structure

Figure 6. Deadtime, Interlock and Output Minimum Pulse Width

Figure 7. Input Circuit

# **ORDERING INFORMATION**

| Device       | Package          | Shipping <sup>†</sup> |  |  |

|--------------|------------------|-----------------------|--|--|

| NCD57200DR2G | SOIC-8 (Pb-Free) | 2500 / Tape & Reel    |  |  |

<sup>†</sup>For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D.

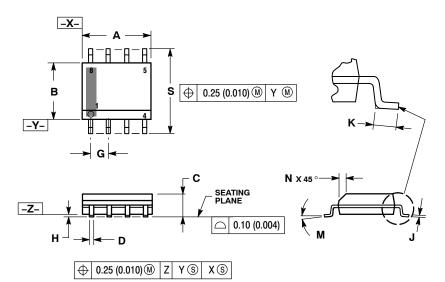

#### PACKAGE DIMENSIONS

#### SOIC-8 NB CASE 751-07 **ISSUE AK**

- DIMENSIONING AND TOLERANCING PER ANSI Y14.5M, 1982.

CONTROLLING DIMENSION: MILLIMETER.

- DIMENSION A AND B DO NOT INCLUDE MOLD PROTRUSION.

- MAXIMUM MOLD PROTRUSION 0.15 (0.006)

- PER SIDE.

DIMENSION D DOES NOT INCLUDE DAMBAR DIMENSION DOES NOT INCLUDE DAMBAR PROTRUSION. ALLOWABLE DAMBAR PROTRUSION SHALL BE 0.127 (0.005) TOTAL IN EXCESS OF THE D DIMENSION AT MAXIMUM MATERIAL CONDITION.

- 751–01 THRU 751–06 ARE OBSOLETE. NEW STANDARD IS 751–07.

|     | MILLIN | IETERS | INCHES    |       |  |

|-----|--------|--------|-----------|-------|--|

| DIM | MIN    | MAX    | MIN       | MAX   |  |

| Α   | 4.80   | 5.00   | 0.189     | 0.197 |  |

| В   | 3.80   | 4.00   | 0.150     | 0.157 |  |

| C   | 1.35   | 1.75   | 0.053     | 0.069 |  |

| D   | 0.33   | 0.51   | 0.013     | 0.020 |  |

| G   | 1.27   | 7 BSC  | 0.050 BSC |       |  |

| Н   | 0.10   | 0.25   | 0.004     | 0.010 |  |

| J   | 0.19   | 0.25   | 0.007     | 0.010 |  |

| K   | 0.40   | 1.27   | 0.016     | 0.050 |  |

| M   | 0 °    | 8 °    | 0 °       | 8 °   |  |

| N   | 0.25   | 0.50   | 0.010     | 0.020 |  |

| S   | 5.80   | 6.20   | 0.228     | 0.244 |  |

#### **SOLDERING FOOTPRINT\***

\*For additional information on our Pb-Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.

#### **GENERIC MARKING DIAGRAM\***

XXXXX = Specific Device Code = Assembly Location Α

= Wafer Lot = Year = Work Week W

= Pb-Free Package

XXXXXX XXXXXX AYWW AYWW Ŧ H **Discrete Discrete** (Pb-Free)

A A A A

XXXXXX = Specific Device Code = Assembly Location Α

WW = Work Week = Pb-Free Package

\*This information is generic. Please refer to device data sheet for actual part marking. Pb-Free indicator, "G" or microdot "■", may or may not be present. Some products may not follow the Generic Marking.

#### **STYLES ON PAGE 2**

#### SOIC-8 NB CASE 751-07 ISSUE AK

# **DATE 16 FEB 2011**

| STYLE 1: PIN 1. EMITTER 2. COLLECTOR 3. COLLECTOR 4. EMITTER 5. EMITTER 6. BASE 7. BASE 8. EMITTER                                                                 | STYLE 2:  PIN 1. COLLECTOR, DIE, #1 2. COLLECTOR, #1 3. COLLECTOR, #2 4. COLLECTOR, #2 5. BASE, #2 6. EMITTER, #2 7. BASE, #1 8. EMITTER, #1 | STYLE 3: PIN 1. DRAIN, DIE #1 2. DRAIN, #1 3. DRAIN, #2 4. DRAIN, #2 5. GATE, #2 6. SOURCE, #2 7. GATE, #1 8. SOURCE, #1                            | STYLE 4: PIN 1. ANODE 2. ANODE 3. ANODE 4. ANODE 5. ANODE 6. ANODE 7. ANODE 8. COMMON CATHODE                                                                           |

|--------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| STYLE 5: PIN 1. DRAIN 2. DRAIN 3. DRAIN 4. DRAIN 5. GATE 6. GATE 7. SOURCE 8. SOURCE                                                                               | STYLE 6: PIN 1. SOURCE 2. DRAIN 3. DRAIN 4. SOURCE 5. SOURCE 6. GATE 7. GATE 8. SOURCE                                                       | STYLE 7: PIN 1. INPUT 2. EXTERNAL BYPASS 3. THIRD STAGE SOURCE 4. GROUND 5. DRAIN 6. GATE 3 7. SECOND STAGE Vd 8. FIRST STAGE Vd                    | STYLE 8: PIN 1. COLLECTOR, DIE #1 2. BASE, #1 3. BASE, #2 4. COLLECTOR, #2 5. COLLECTOR, #2 6. EMITTER, #2 7. EMITTER, #1 8. COLLECTOR, #1                              |

| STYLE 9: PIN 1. EMITTER, COMMON 2. COLLECTOR, DIE #1 3. COLLECTOR, DIE #2 4. EMITTER, COMMON 5. EMITTER, COMMON 6. BASE, DIE #2 7. BASE, DIE #1 8. EMITTER, COMMON | STYLE 10: PIN 1. GROUND 2. BIAS 1 3. OUTPUT 4. GROUND 5. GROUND 6. BIAS 2 7. INPUT 8. GROUND                                                 | STYLE 11: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. DRAIN 2 7. DRAIN 1 8. DRAIN 1                                               | STYLE 12: PIN 1. SOURCE 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                                 |

| STYLE 13: PIN 1. N.C. 2. SOURCE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                              | STYLE 14: PIN 1. N-SOURCE 2. N-GATE 3. P-SOURCE 4. P-GATE 5. P-DRAIN 6. P-DRAIN 7. N-DRAIN 8. N-DRAIN                                        | STYLE 15: PIN 1. ANODE 1 2. ANODE 1 3. ANODE 1 4. ANODE 1 5. CATHODE, COMMON 6. CATHODE, COMMON 7. CATHODE, COMMON 8. CATHODE, COMMON               | STYLE 16: PIN 1. EMITTER, DIE #1 2. BASE, DIE #1 3. EMITTER, DIE #2 4. BASE, DIE #2 5. COLLECTOR, DIE #2 6. COLLECTOR, DIE #2 7. COLLECTOR, DIE #1 8. COLLECTOR, DIE #1 |

| STYLE 17: PIN 1. VCC 2. V2OUT 3. V1OUT 4. TXE 5. RXE 6. VEE 7. GND 8. ACC                                                                                          | STYLE 18: PIN 1. ANODE 2. ANODE 3. SOURCE 4. GATE 5. DRAIN 6. DRAIN 7. CATHODE 8. CATHODE                                                    | STYLE 19: PIN 1. SOURCE 1 2. GATE 1 3. SOURCE 2 4. GATE 2 5. DRAIN 2 6. MIRROR 2 7. DRAIN 1 8. MIRROR 1                                             | STYLE 20: PIN 1. SOURCE (N) 2. GATE (N) 3. SOURCE (P) 4. GATE (P) 5. DRAIN 6. DRAIN 7. DRAIN 8. DRAIN                                                                   |

| STYLE 21: PIN 1. CATHODE 1 2. CATHODE 2 3. CATHODE 3 4. CATHODE 4 5. CATHODE 5 6. COMMON ANODE 7. COMMON ANODE 8. CATHODE 6                                        | STYLE 22: PIN 1.                                                                                                                             | STYLE 23: PIN 1. LINE 1 IN 2. COMMON ANODE/GND 3. COMMON ANODE/GND 4. LINE 2 IN 5. LINE 2 OUT 6. COMMON ANODE/GND 7. COMMON ANODE/GND 8. LINE 1 OUT | STYLE 24: PIN 1. BASE 2. EMITTER 3. COLLECTOR/ANODE 4. COLLECTOR/ANODE 5. CATHODE 6. CATHODE 7. COLLECTOR/ANODE 8. COLLECTOR/ANODE                                      |

| STYLE 25: PIN 1. VIN 2. N/C 3. REXT 4. GND 5. IOUT 6. IOUT 7. IOUT 8. IOUT                                                                                         | STYLE 26: PIN 1. GND 2. dv/dt 3. ENABLE 4. ILIMIT 5. SOURCE 6. SOURCE 7. SOURCE 8. VCC                                                       | STYLE 27: PIN 1. ILIMIT 2. OVLO 3. UVLO 4. INPUT+ 5. SOURCE 6. SOURCE 7. SOURCE 8. DRAIN                                                            | STYLE 28: PIN 1. SW_TO_GND 2. DASIC_OFF 3. DASIC_SW_DET 4. GND 5. V_MON 6. VBULK 7. VBULK 8. VIN                                                                        |

| STYLE 29: PIN 1. BASE, DIE #1 2. EMITTER, #1 3. BASE, #2 4. EMITTER, #2 5. COLLECTOR, #2 6. COLLECTOR, #2 7. COLLECTOR, #1 8. COLLECTOR, #1                        | STYLE 30: PIN 1. DRAIN 1 2. DRAIN 1 3. GATE 2 4. SOURCE 2 5. SOURCE 1/DRAIN 2 6. SOURCE 1/DRAIN 2 7. SOURCE 1/DRAIN 2 8. GATE 1              |                                                                                                                                                     |                                                                                                                                                                         |

ON Semiconductor and the are trademarks of Semiconductor Components Industries, LLC dba ON Semiconductor or its subsidiaries in the United States and/or other countries. ON Semiconductor owns the rights to a number of patents, trademarks, copyrights, trade secrets, and other intellectual property. A listing of ON Semiconductor's product/patent coverage may be accessed at <a href="https://www.onsemi.com/site/pdf/Patent-Marking.pdf">www.onsemi.com/site/pdf/Patent-Marking.pdf</a>. ON Semiconductor reserves the right to make changes without further notice to any products herein. ON Semiconductor newsers on warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does ON Semiconductor assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. Buyer is responsible for its products and applications using ON Semiconductor products, including compliance with all laws, regulations and safety requirements or standards, regardless of any support or applications information provided by ON Semiconductor. "Typical" parameters which may be provided in ON Semiconductor data sheets and/or specifications can and do vary in different applications and actual performance may vary over time. All operating parameters, including "Typicals" must be validated for each customer application by customer's technical experts. ON Semiconductor does not convey any license under its patent rights nor the rights of others. ON Semiconductor products are not designed, intended, or authorized for use as a critical component in life support systems or any FDA Class 3 medical devices or medical devices with a same or similar classification in a foreign jurisdiction or any devices intended for implantation in the human body. Should Buyer purchase or use ON Semiconductor products for any such unintended or unauthorized application, Buyer shall indemn

#### **PUBLICATION ORDERING INFORMATION**

LITERATURE FULFILLMENT:

Email Requests to: orderlit@onsemi.com

ON Semiconductor Website: www.onsemi.com

TECHNICAL SUPPORT

North American Technical Support:

Voice Mail: 1 800-282-9855 Toll Free USA/Canada

Phone: 011 421 33 790 2910

t: Europe, Middle East and Africa Technical Support:

e USA/Canada Phone: 00421 33 790 2910

For additional information, please contact your local Sales Representative