Document Category: Datasheet

## UltraBK™ 4A DC-DC Converter Module

## **Product Description**

The MYTNC1R84RELA2RA is miniature UltraBK™ called "Ultra Block", an ultra-thin high efficiency integrated power solution that combines a 4A DC/DC converter with components.

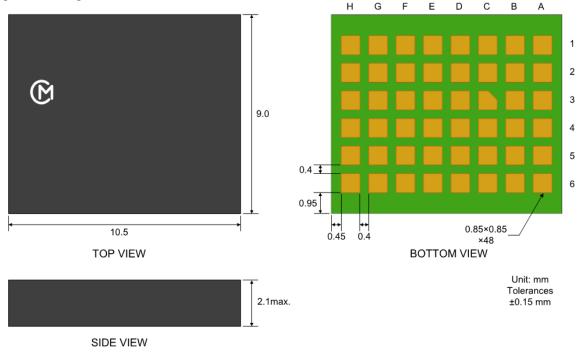

This totally integrated module provides up to 90.5% efficiency in a small and thin 10.5mm x 9.0mm x 2.1mm LGA package. Murata's easy-to-use module terminal design allows simple power layout and maximum efficiency by minimizing routing parasitic resistance.

- Wide input voltage 6.0V to 14.4V

- Output voltage 0.7V to 1.8V

- Efficiency up to 90.5%

- Up to 90.0% Efficiency with 12VIN/1.8VOUT/4A

- Up to 4A

- Ultra-thin/small 10.5 x 9.0 x 2.1mm LGA package

### **Features**

- Power-good output

- Over-current and Over-temperature protection

- Remote on/off control

- Output voltage sense

- I<sup>2</sup>C 6.0-compatible serial interface operating up to 1MHz.

## **Typical Applications**

- PCIe / server applications

- FPGA and DSP

- Datacom / telecom systems

- Distributed bus architectures (DBA)

- Programmable logic and mixed voltage systems

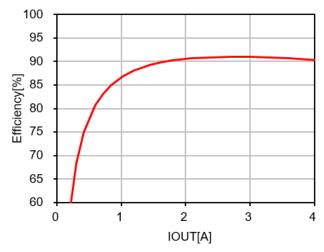

## **Efficiency**

Ta=25°C 12VIN 1.8VOUT

Figure 1. Efficiency Plot

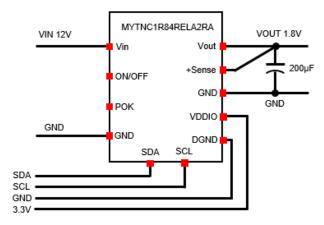

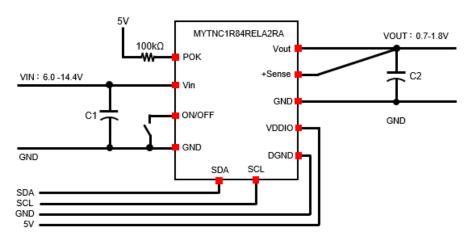

## **Simplified Application Circuit**

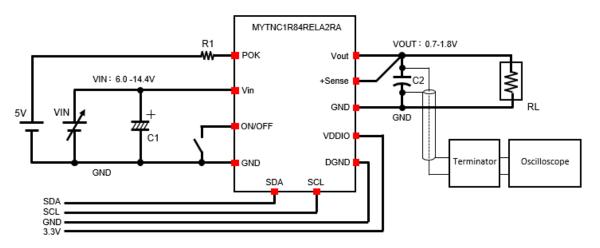

Figure 2. Simplified Circuit Diagram

Document Category: Datasheet

#### INNOVATOR IN ELECTRONICS

| Product Description                                                               | 1        |

|-----------------------------------------------------------------------------------|----------|

| Features                                                                          | 1        |

| Typical Applications                                                              | 1        |

| Efficiency                                                                        | 1        |

| Simplified Application Circuit                                                    | 1        |

| Absolute Maximum Ratings <sup>(1)(2)</sup>                                        | 3        |

| Recommended Operating Conditions <sup>(1)</sup>                                   | 3        |

| Package Thermal Characteristics(1)(2)                                             | 3        |

| Electrical Characteristics                                                        | 4        |

| Pin Configuration                                                                 | 7        |

| Pin Descriptions                                                                  | 7        |

| Functional Block Diagram                                                          | 8        |

| Typical Performance Characteristics                                               | 9        |

| Thermal Deratings (Reference Data)                                                | 10       |

| Output Voltage Range                                                              | 10       |

| Limitation of Input Voltage Slew rate                                             | 11       |

| Detailed Description                                                              | 11       |

| Output Voltage Remote Sense Function                                              | 11       |

| Soft start Function                                                               | 12       |

| Telemetry System                                                                  | 12       |

| I <sup>2</sup> C Interface Bus OverviewStandard-, Fast-, Fast-Mode Plus Protocol  | 13       |

| I <sup>2</sup> C Update Sequence                                                  | 14       |

| Register Map  Detailed Register Description                                       | 16       |

| Protections                                                                       |          |

| Over Current Protection and Short Circuit Protection  Over Temperature Protection | 23       |

| Soldering Guidelines                                                              |          |

| Pb-free Solder Processes                                                          |          |

| Dry Pack Information                                                              |          |

| Application Performance                                                           |          |

| Transient Performance                                                             |          |

| Test Circuit                                                                      |          |

| Component Selection                                                               |          |

| Input Fuse                                                                        | 29       |

| Input Capacitor  Output Capacitor                                                 | 29       |

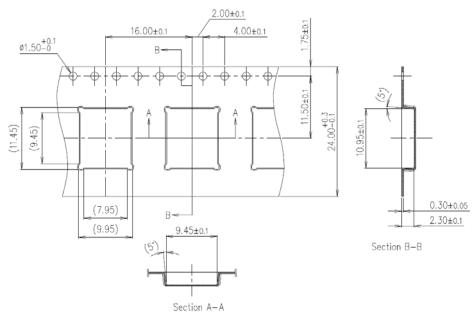

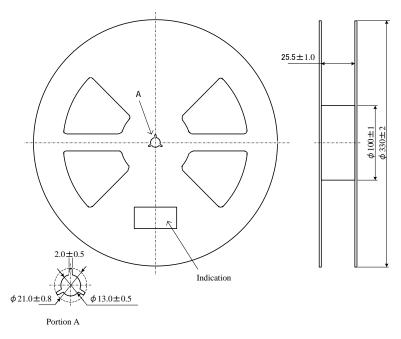

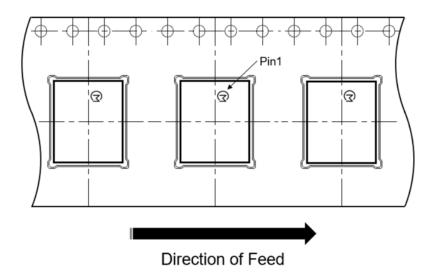

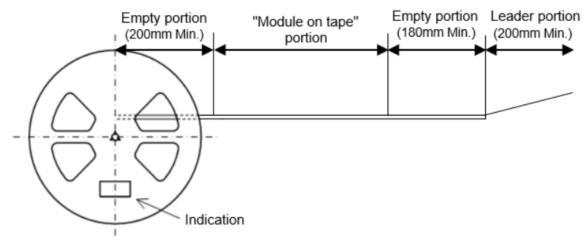

| Packaging Information                                                             |          |

| Moisture Sensitivity Level                                                        | 30       |

| Package Drawing                                                                   | 30       |

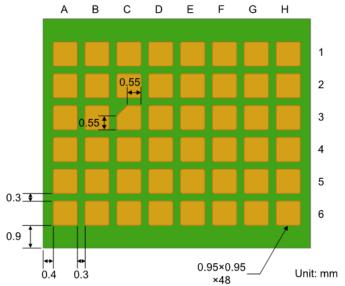

| Recommended Board Land Pattern (Top View) Top Marking Specification               | 30<br>31 |

| Application Circuit                                                               | 31       |

| Application Circuit Part List (Recommended)                                       | 31       |

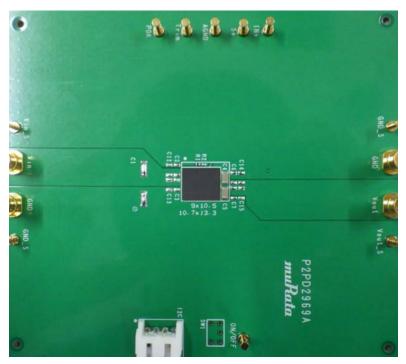

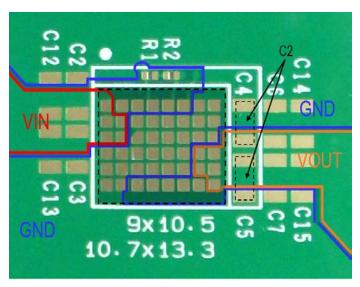

| Application Board Example                                                         | 32       |

## UltraBK<sup>™</sup> 4A DC-DC Converter Module

| 33 |

|----|

| 3  |

| 35 |

| 35 |

| 3! |

| 3! |

| 30 |

| 3  |

| 36 |

| 3  |

| 37 |

|    |

Document Category: Datasheet

# UltraBK™ 4A DC-DC Converter Module

## Absolute Maximum Ratings(1)(2)

| PARAMETER                                     | MIN  | MAX  | UNITS |

|-----------------------------------------------|------|------|-------|

| Vin, ON/OFF Pin <sup>(3)</sup>                | -0.3 | 16   | V     |

| POK Pin, SCL, SDA, VDDIO                      | -0.3 | 5.5  | V     |

| Storage Temperature                           | -40  | 125  | °C    |

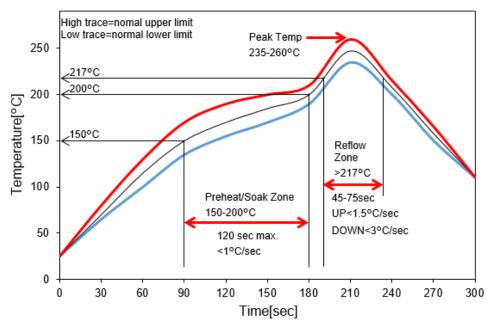

| Soldering / Reflow temperature <sup>(4)</sup> | -    | 260  | ô     |

| ESD Tolerance, HBM <sup>(5)</sup>             | -    | 1000 | V     |

#### Notes:

- (1) Stresses beyond those listed under absolute maximum ratings may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification are not implied. Exposure to absolute maximum rating conditions for extended periods may extremely reduce device reliability.

- (2) All voltages are with respect to GND plane.

- (3) Do NOT exceed more than 0.3V from Vin voltage.

- (4) Recommended Reflow profile is written in "Soldering Guidelines".

- (5) Human body model, per the JEDEC standard JS-001-2012.

**Table 1. Absolute Maximum Ratings**

## Recommended Operating Conditions(1)

| PARAMETER                          | MIN | MAX  | UNITS |

|------------------------------------|-----|------|-------|

| Input Voltage Range                | 6.0 | 14.4 | V     |

| Ambient Temperature <sup>(2)</sup> | -40 | 105  | °C    |

| Junction Temperature               | -40 | 120  | °C    |

| Load Current                       | 0   | 4    | Α     |

#### Notes:

- (1) This module should be operated inside the recommended operating conditions. This module has been designed and tested on the assumption that it will be used under the recommended operating conditions. Operating in not recommended condition may reduce reliability of the module.

- (2) See the temperature derating curves in the thermal deratings. However, do not condensate.

**Table 2. Recommended Operating Conditions**

## Package Thermal Characteristics(1)(2)

| PARAMETER |                                        | TYP  | UNITS |

|-----------|----------------------------------------|------|-------|

| Θjcb-1    | Junction-case-bottom at heat Junction1 | 10.0 | °C/W  |

| Θjcb-2    | Junction-case-bottom at heat Junction2 | 47.3 | °C/W  |

| Θjct-1    | Junction-case-top a heat Junction1     | 64.9 | °C/W  |

| Θjct-2    | Junction-case-top a heat Junction2     | 53.7 | °C/W  |

| Θја       | Junction-air                           | 19.9 | °C/W  |

#### Notes:

- (1) Package thermal characteristics and performance are acquire and reported in according to the JEDEC standard JESD51-12. See "Fig.40" below for more information on our measurement conditions.

- (2) Junction thermal resistance is a function not only of the internal parts, but it is also extremely sensitive to the environment which includes, but is not limited to, board thickness, number of layers, copper weight / routes, and air flow. Attention to the board layout is necessary to realize expected thermal performance.

**Table 3. Package Thermal Characteristics**

Document Category: Datasheet

## UltraBK<sup>™</sup> 4A DC-DC Converter Module

## **Electrical Characteristics**

VIN=12V, VOUT=1.8V, IOUT=4A, Ta=+25°C, unless otherwise noted. The Electrical Characteristics table is based on the test circuit in Figure 35.

| Figure 35.                                         | 0.415.01   |                                      |                     | T) (D  |      |       |

|----------------------------------------------------|------------|--------------------------------------|---------------------|--------|------|-------|

| PARAMETER                                          | SYMBOL     | CONDITIONS                           | MIN                 | TYP    | MAX  | UNITS |

| INPUT SUPPLY                                       | \ \/\L     |                                      |                     | 40     |      |       |

| Input Voltage <sup>(1)</sup>                       | VIN        |                                      | 6                   | 12     | 14.4 | V     |

| Input Voltage Start-up<br>Slew rate <sup>(3)</sup> | VINSR      |                                      | Note <sup>(2)</sup> | -      | 150  | V/ms  |

| VIN Under Voltage Lockout                          |            |                                      |                     |        |      |       |

| Threshold High <sup>(3)</sup>                      | VIUVH      |                                      | -                   | -      | 5.45 | V     |

| VIN Under Voltage Lockout                          | \ // I\ // |                                      | 4.5                 |        |      |       |

| Threshold Low <sup>(3)</sup>                       | VIUVL      |                                      | 4.5                 | -      | -    | V     |

| VIN Under Voltage Lockout                          | VIUVHYS    |                                      | -                   | 215    | _    | mV    |

| Hysteresis                                         |            |                                      | _                   | 210    | _    | 111 V |

| VIN Current Supply, Switching                      | IVINSW     | No Load                              | -                   | 25     | -    | mA    |

| VIN Current Supply, Shutdown                       | IVINSD     | VOUT=0V, ON/OFF=0V,                  | -                   | 160    | -    | μA    |

| Remote ON/OFF Control (ON/O                        | FF Pin)    |                                      | 1                   |        |      |       |

| Threshold High <sup>(3)</sup>                      | VTREH      | Logic ON by pull-up or open of       | 1.1                 | -      | -    | V     |

|                                                    |            | ON/OFF Pin Logic OFF by pull-down of |                     |        |      |       |

| Threshold Low <sup>(3)</sup>                       | VTREL      | ON/OFF Pin                           | -                   | -      | 0.4  | V     |

| 01//055 B: 1 1 0 (/2)                              |            | VIN=14.4V, ON/OFF=0V,                |                     |        |      |       |

| ON/OFF Pin Leakage Current <sup>(3)</sup>          | ILEN       | From Vin to ON/OFF                   | -                   | -      | 200  | μA    |

| CONVERTER                                          |            |                                      |                     |        |      |       |

|                                                    |            | VIN=12.0V, VOUT=1.8V,                | _                   | 90     | _    | %     |

| Efficiency                                         | EFF        | IOUT=4A                              | -                   | 90     | -    | /0    |

| Linciency                                          |            | VIN=12.0V, VOUT=1.2V,                | _                   | 88     | _    | %     |

| 0 0 11                                             |            | IOUT=4A                              |                     |        |      | ,,,   |

| Charge Pump Switching                              |            | Per a phase                          | -                   | 500    | -    | kHz   |

| Frequency Buck Converter Switching                 |            |                                      |                     |        |      |       |

| Frequency                                          |            | Per a phase                          | -                   | 1000   | -    | kHz   |

| Troquency                                          |            | VOUT=5% to 95% of VOUT               |                     |        |      |       |

| Start-up Time                                      |            | VSET1[7:0] = 01000110                | _                   | 6      | -    | msec  |

| •                                                  |            | SS[2:0] = 100                        |                     |        |      |       |

| POWER GOOD (POK Pin)                               |            |                                      |                     |        |      |       |

| POK Sink Current <sup>(3)</sup>                    |            | POK=0.4V                             | 4                   | -      | -    | mA    |

| POK Pin Leakage Current <sup>(3)</sup>             | ILPG       | POK=5V, POK=High                     | -                   | -      | 1    | μA    |

| POK & Output Under-Voltage                         |            | VOUT falling (fault)                 | -                   | 90     | -    |       |

| - Crea Surpar Sinasi Tollago                       |            | VOUT rising (good)                   | -                   | 95     | -    | % of  |

| POK & Output Over-Voltage                          |            | VOUT rising (fault)                  | -                   | 110    | -    | VOUT  |

| THERMAL SHUTDOWN                                   |            | VOUT falling (good)                  | -                   | 105    | -    |       |

|                                                    | TOD        | Object descent and a section of      |                     | 450    | 1    | 00    |

| Thermal Shutdown Threshold                         | TSD        | Shutdown operating                   | -                   | 150    | -    | °C    |

| Thermal Shutdown Hysteresis                        | TSDHYS     |                                      | -                   | 20     | -    | °C    |

| OUTPUT                                             | 1          | T                                    |                     |        |      |       |

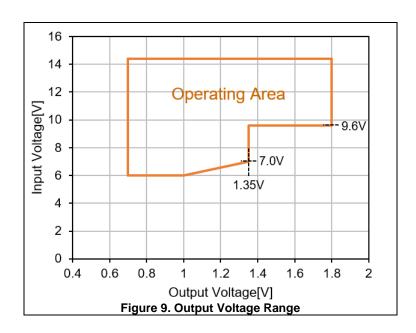

| 2                                                  |            | 9.6V ≤ VIN ≤ 14.4V                   | 0.7                 | -      | 1.8  | V     |

| Output Voltage <sup>(4)</sup>                      | VOUT       | 7.0V ≤ VIN ≤ 14.4V                   | 0.7                 | -      | 1.35 | V     |

|                                                    |            | 6.0V ≤ VIN ≤ 14.4V                   | 0.7                 |        | 1.0  | V     |

| Out 1 \ / -   1 A \ / 4 \/ 5 \                     |            | 6.0V ≤ VIN ≤ 14.4V                   |                     |        |      | 6,    |

| Output Voltage Accuracy (1)(5)                     |            | 0.7V ≤ VOUT ≤ 1.8V <sup>(4)</sup>    | -3                  | -      | +3   | %     |

| Output Current <sup>(1)</sup>                      | IOUT       | 0 ≤ IOUT≤ 4A                         | 0                   |        | 4    | ٨     |

| •                                                  | 1001       |                                      | 0                   | 11     |      | A     |

| Current Limit Inception                            | +          |                                      | -                   |        | -    | Α     |

| Current Limit Method                               | 1          | VINI main 4                          | 4                   | Hiccup |      | 0/    |

| Line Regulation <sup>(3)(5)</sup>                  | 1          | VIN=min. to max.                     | -1                  | -      | +1   | %     |

| Load Regulation <sup>(3)(5)</sup>                  |            | IOUT=min. to max.                    | -1                  | -      | +1   | %     |

Document Category: Datasheet

# UltraBK™ 4A DC-DC Converter Module

VIN=12V, VOUT=1.8V, IOUT=4A, Ta=+25°C, unless otherwise noted. The Electrical Characteristics table is based on the test circuit in Figure 35.

| igure 35. PARAMETER                                     | SYMBOL            | CONDITIONS                                                              |                      | MIN             | TYP  | MAX            | UNITS       |

|---------------------------------------------------------|-------------------|-------------------------------------------------------------------------|----------------------|-----------------|------|----------------|-------------|

| Dynamic Load Peak Deviation                             |                   | IOUT=50-100%, SF                                                        | R=1.0A/µs            | -               | ±3.0 | -              | %           |

| Ripple and Noise <sup>(3)(5)</sup> (20MHz bandwidth)    |                   | 6.0V ≤ VIN ≤ 14.4V<br>0.7V ≤ VOUT ≤ 1.8<br>0 ≤ IOUT≤ 4A                 | <b>/</b> (4)         | -               | ,    | 40             | mV<br>pk-pk |

|                                                         |                   |                                                                         | SS[2:0]<br>= 000     |                 |      | 600            |             |

| External Output Capacitance Range <sup>(3)</sup>        | COUT              | 6.0V≤ VIN≤14.4V<br>0.7V≤VOUT≤1.8V <sup>(4)</sup><br>0≤IOUT≤4A           | SS[2:0]<br>= 001     | 200             | -    | 1200           | μF          |

|                                                         |                   |                                                                         | Other than the above |                 |      | 2000           |             |

| TELEMETRY                                               |                   |                                                                         |                      |                 |      |                |             |

| Output Voltage Sense<br>Measurement Time                |                   | 12-bit ADC resolution                                                   | on                   |                 | 512  |                | μs          |

| Output Voltage Sense Refresh Rate                       |                   |                                                                         |                      |                 | 1.5  |                | ms          |

| Output Voltage Sense<br>Measurement Resolution          |                   |                                                                         |                      |                 | 1    |                | mV          |

| Output Voltage Sense<br>Measurement Accuracy            |                   |                                                                         |                      |                 | ±1   |                | %           |

| Average Output Current Sense                            |                   |                                                                         |                      |                 | 512  |                |             |

| Measurement Time                                        |                   | 8-bit ADC resolution                                                    | n                    |                 | 128  |                | μs          |

| Current Sense Amplifier Input<br>Offset Voltage         |                   |                                                                         |                      |                 | 400  | 2000           | μV          |

| Output Inductor DC resistance<br>Measurement Resolution | DCR               |                                                                         |                      |                 | 0.8  |                | mΩ          |

| Current Sense Amplifier Gain<br>Error                   |                   |                                                                         |                      |                 | 1    |                | %           |

| I <sup>2</sup> C SERIAL INTERFACE(SCL, S                | DA, VDDIO)        | •                                                                       |                      |                 |      | •              |             |

| VDDIO Supply Voltage                                    | V <sub>DDIO</sub> |                                                                         |                      | 1.08            |      | 5.5            | V           |

| SDA, SCL Input High Voltage                             | ViH               |                                                                         |                      | 0.7 x<br>VDDIO  |      |                | V           |

| SDA, SCL Input Low Voltage                              | VıL               |                                                                         |                      |                 |      | 0.3 x<br>VDDIO | V           |

| SDA, SCL Input Hysteresis                               | V <sub>H</sub> ys |                                                                         |                      | 0.05 x<br>VDDIO |      |                | V           |

| SDA, SCL Input Current                                  | ISCL, ISDA        |                                                                         |                      | -1              |      | 1              | μA          |

| SDA Output Low Level                                    | Vol               | ISDA = 20mA                                                             |                      |                 |      | 0.4            | V           |

| I <sup>2</sup> C Interface Initial Wait Time            |                   | Initial wait time from<br>high to 1st I <sup>2</sup> C comr<br>accepted | n EN logic<br>nand   | 1000            |      |                | μs          |

| MTP Non-Volatile Memory Write Cycle Time                |                   |                                                                         |                      |                 | 34   | 50             | ms          |

| SDA, SCL Pin Capacitance <sup>(3)</sup>                 | C <sub>I/O</sub>  |                                                                         |                      |                 |      | 10             | рF          |

| I <sup>2</sup> C INTERFACE TIMING CHARA                 | CTERISTICS        | FOR STANDARD MO                                                         | DDE AND FA           | AST MODE        | PLUS |                |             |

|                                                         |                   | Standard mode                                                           |                      |                 |      | 100            | kbits/s     |

| Serial Clock Frequency                                  | FscL              | Fast mode                                                               |                      |                 |      | 400            | kbits/s     |

|                                                         |                   | Fast mode plus                                                          |                      |                 |      | 1              | Mbits/s     |

|                                                         |                   | Standard mode                                                           |                      | 4.7             |      |                | μs          |

| Clock Low Period                                        | T <sub>LOW</sub>  | Fast mode                                                               |                      | 1.3             |      |                | μs          |

|                                                         |                   | Fast mode plus                                                          |                      | 0.5             |      |                | μs          |

|                                                         |                   | Standard mode                                                           |                      | 4               |      |                | μs          |

| Clock High Period                                       | T <sub>HIGH</sub> | Fast mode                                                               |                      | 600             |      |                | ns          |

|                                                         |                   | Fast mode plus                                                          |                      | 260             |      |                | ns          |

| BUS Free Time between a                                 | Т                 | Standard mode                                                           |                      | 4.7             |      |                | μs          |

| STOP a START Condition                                  | T <sub>BUF</sub>  | Fast mode                                                               |                      | 1.3             |      |                | μs          |

|                                                         |                   |                                                                         |                      |                 |      |                |             |

INNOVATOR IN ELECTRONICS

# **Preliminary**: MYTNC1R84RELA2RA

Document Category: Datasheet

## UltraBK<sup>™</sup> 4A DC-DC Converter Module

VIN=12V, VOUT=1.8V, IOUT=4A, Ta=+25°C, unless otherwise noted. The Electrical Characteristics table is based on the test circuit in Figure 35.

| PARAMETER                                 | SYMBOL              | CONDITIONS     | MIN                    | TYP | MAX  | UNITS |

|-------------------------------------------|---------------------|----------------|------------------------|-----|------|-------|

|                                           |                     | Fast mode plus | 0.5                    |     |      | μs    |

| Oatro Time for a Dancated                 |                     | Standard mode  | 4.7                    |     |      | μs    |

| Setup Time for a Repeated START Condition | T <sub>SU:STA</sub> | Fast mode      | 600                    |     |      | Ns    |

| START Condition                           |                     | Fast mode plus | 260                    |     |      | Ns    |

| Held Time for a Demonstrat                |                     | Standard mode  | 4                      |     |      | μs    |

| Hold Time for a Repeated START Condition  | T <sub>HD:STA</sub> | Fast mode      | 600                    |     |      | Ns    |

| START Condition                           |                     | Fast mode plus | 260                    |     |      | Ns    |

|                                           |                     | Standard mode  | 4                      |     |      | μs    |

| Setup Time of STOP condition              | T <sub>SU:STO</sub> | Fast mode      | 600                    |     |      | Ns    |

|                                           |                     | Fast mode plus | 260                    |     |      | Ns    |

|                                           |                     | Standard mode  | 250                    |     |      | Ns    |

| Data Setup Time                           | T <sub>SU:DAT</sub> | Fast mode      | 100                    |     |      | Ns    |

|                                           |                     | Fast mode plus | 50                     |     |      | Ns    |

|                                           |                     | Standard mode  | 0                      |     |      | μs    |

| Data Hold Time                            | T <sub>HD_DAT</sub> | Fast mode      | 0                      |     |      | ns    |

|                                           |                     | Fast mode plus | 0                      |     |      | ns    |

| D: T: (0DA 100)                           | T <sub>R</sub>      | Standard mode  |                        |     | 1000 | ns    |

| Rise Time of SDA and SCL signals          |                     | Fast mode      | 20                     |     | 300  | ns    |

| Signais                                   |                     | Fast mode plus |                        |     | 120  | ns    |

|                                           |                     | Standard mode  |                        |     | 300  |       |

| Fall time of SDA and SCL<br>Signals       | TF                  | Fast mode      | 20 x<br>VDDIO/<br>5.5V |     | 300  | ns    |

| Oignais                                   |                     | Fast mode plus | 20 x<br>VDDIO/<br>5.5V |     | 120  | ns    |

|                                           |                     | Standard mode  |                        |     | 3.45 | μs    |

| Data Valid Time                           | $T_{VD}$            | Fast mode      |                        |     | 900  | ns    |

|                                           |                     | Fast mode plus |                        |     | 450  | ns    |

|                                           |                     | Standard mode  |                        |     | 3.45 | μs    |

| Data Valid Acknowledge Time               | $T_{VDA}$           | Fast mode      |                        |     | 900  | ns    |

|                                           |                     | Fast mode plus |                        |     | 450  | ns    |

| Consoitive Lond for CDA and               |                     | Standard mode  |                        |     | 400  | pF    |

| Capacitive Load for SDA and SCL           | C <sub>BUS</sub>    | Fast mode      |                        |     | 400  | pF    |

|                                           |                     | Fast mode plus |                        |     | 550  | pF    |

#### Notes:

**Table 4. Electrical Characteristics**

<sup>(1)</sup> Min/Max specifications are 100% production tested at Ta=25 °C, unless otherwise noted. Limits over the operating range are guaranteed by design.

<sup>(2)</sup> See the section of "Limitation of Input Voltage slew rate".

<sup>(3)</sup> Guaranteed by design.

<sup>(4)</sup> See the Output Voltage Range of fig.9.

<sup>(5)</sup> Only statics state.

Document Category: Datasheet

UltraBK™ 4A DC-DC Converter Module

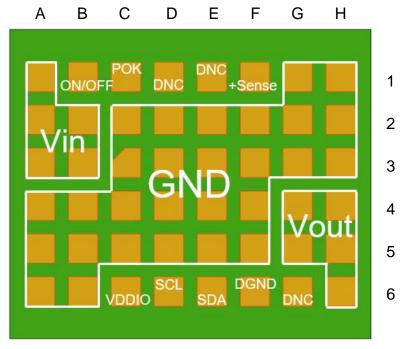

# Pin Configuration

Figure 3. Module Terminal (Top View)

# **Pin Descriptions**

| PIN NO.                                                     | NAME   | DESCRIPTION                                                                                                                                                                  |

|-------------------------------------------------------------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| A1-A3, B2-B3                                                | Vin    | Input Voltage pins. Apply input voltage between these pins and GND pins.                                                                                                     |

| A4-A6, B4-B6, C2-C5,<br>D2-D5,E2-E5, F2-F5,<br>G1-G3, H1-H3 | GND    | Ground pins. Connect to the GND plane.                                                                                                                                       |

| B1                                                          | ON/OFF | Remote ON/OFF pin. The pin is connected to Vin through the internal resistance.                                                                                              |

| C1                                                          | POK    | Power Good pin. The function is operated by internal opendrain FET.                                                                                                          |

| C6, D1, E1,                                                 | DNC    | Do not connect pins. Those pins must be left floating individually.                                                                                                          |

| D6                                                          | DGND   | Digital ground pin. Connect to I <sup>2</sup> C signal GND.                                                                                                                  |

| E6                                                          | SDA    | I <sup>2</sup> C Serial bus data input/output pin.                                                                                                                           |

| F6                                                          | SCL    | I <sup>2</sup> C Serial bus clock input pin.                                                                                                                                 |

| G4-G5, H4-H6                                                | Vout   | Output pins. Connect the output load between these pins and Ground pins. Place external bypass capacitors as close as possible to these pins to reduce parasitic inductance. |

| G6                                                          | VDDIO  | Digital I/O supply voltage for I <sup>2</sup> C interface.                                                                                                                   |

| F1                                                          | +Sense | Output Voltage Sensing pin. Connect to an output near the load to improve load regulation. This pin must be connected to output near the load, or at the module pins.        |

**Table 5. Pin Descriptions**

Document Category: Datasheet

UltraBK™ 4A DC-DC Converter Module

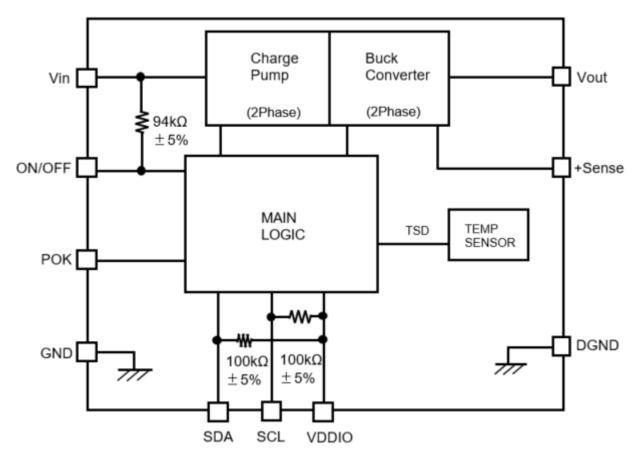

# **Functional Block Diagram**

Figure 4. Functional Block Diagram

Document Category: Datasheet

UltraBK™ 4A DC-DC Converter Module

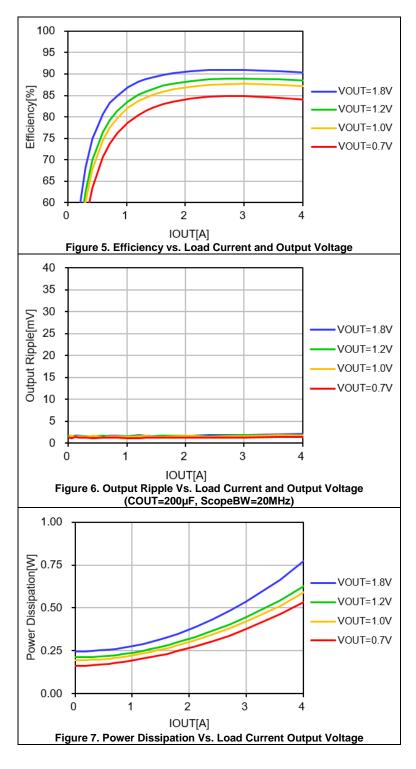

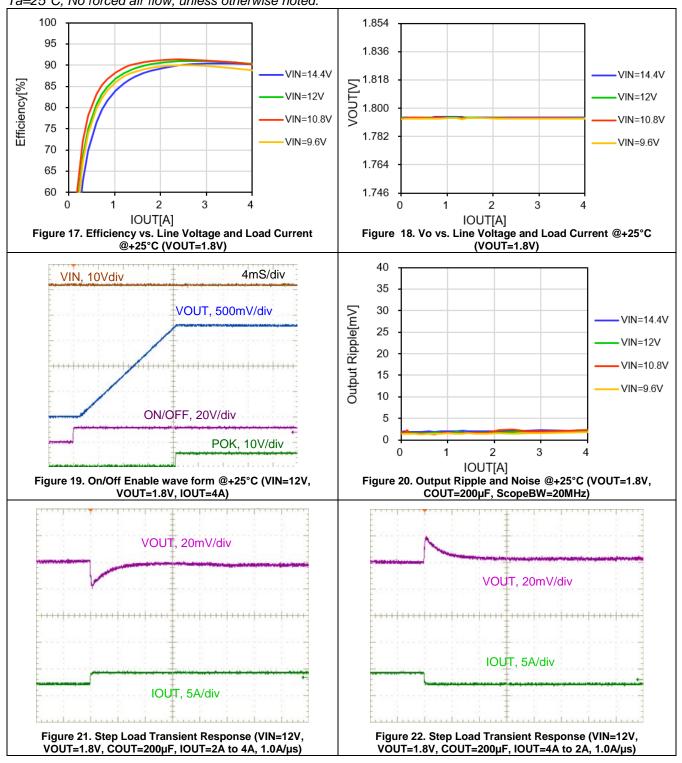

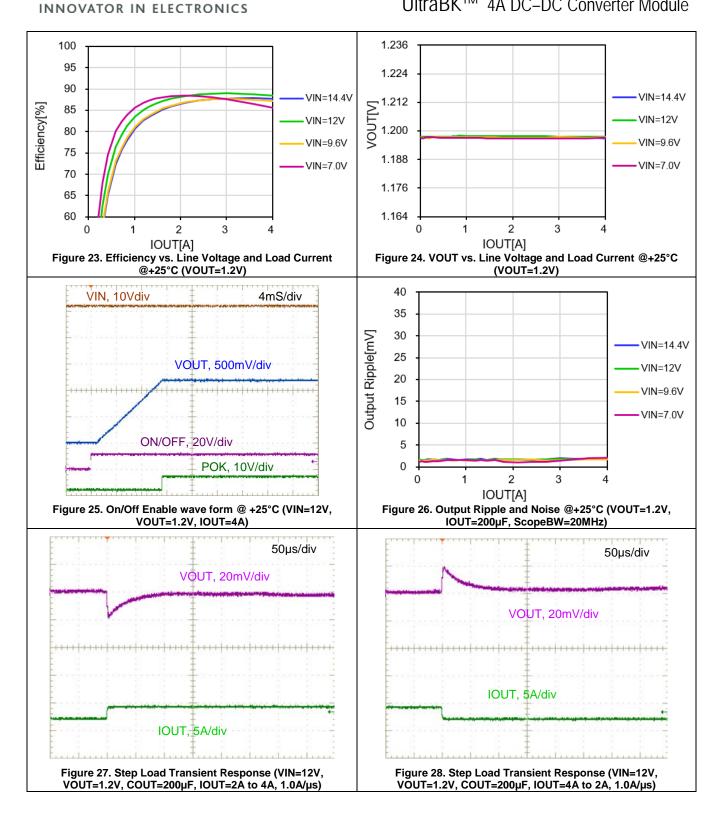

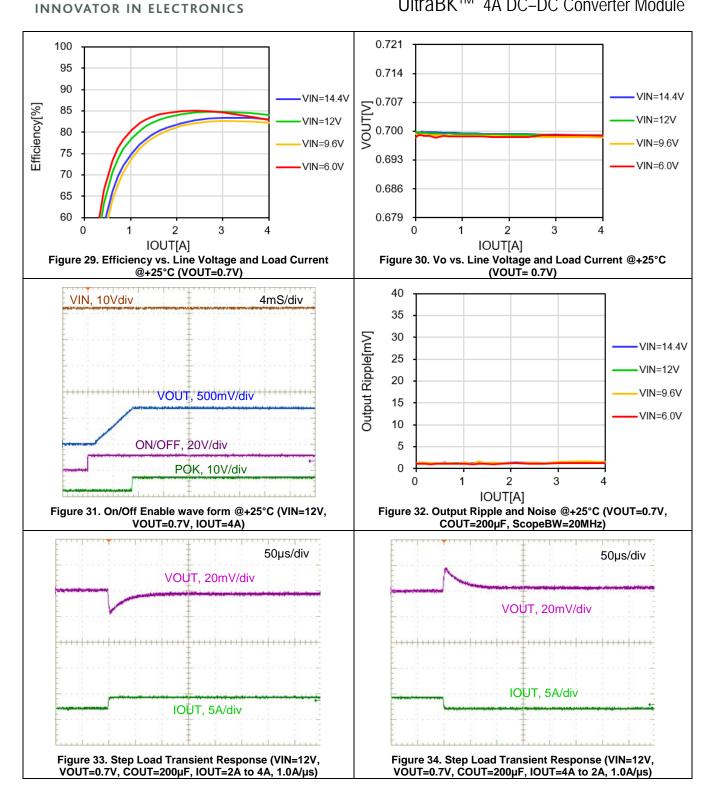

# **Typical Performance Characteristics** (VIN=12V Ta=25°C)

Document Category: Datasheet

UltraBK<sup>™</sup> 4A DC–DC Converter Module

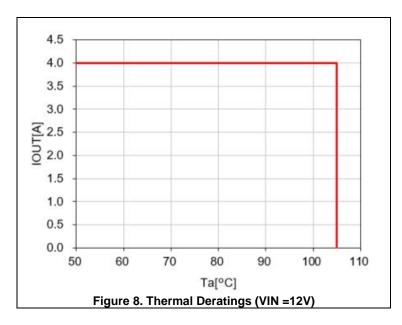

## Thermal Deratings (Reference Data)

Thermal deratings are evaluated in following condition.

- The product is mounted on 114.5mm x 101.5mm x 1.6mm (Layer1, 4: 2oz Layer2, 3: 1oz copper) FR-4 board.

- · No forced air flow.

Surface temperature of the product: 118.7°C max

## **Output Voltage Range**

Document Category: Datasheet

UltraBK<sup>™</sup> 4A DC-DC Converter Module

## Limitation of Input Voltage Slew rate

When starting the module with ramping Input Voltage up, the slew rate of the ramping should be managed for the proper operation. If Input Voltage ramping up is too steep, it would cause charge injection to the internal nodes via parasitic. The maximum slew rate of the Input Voltage ramp up when booting the module with Input Voltage is specified on the table 4 "Electronic Characteristics".

Similarly, if the VIN slew late is too low compare with VOUT slew rate, it could prevent expected start up behavior. To avoid hitting the maximum duty cycle operation, the VIN slew rate should satisfy either equation of (eq1) – (eq.6) in the follow table that determined by SS setting. VINSR\_L is minimum of input voltage startup slew rate and SS is soft start.

As a reference, estimated value of the slew rate and start-up time for each output voltage is written in the table.

|              |                                                     | CALCULATION EXAMPLE |                          |      |      |                                |         |  |  |

|--------------|-----------------------------------------------------|---------------------|--------------------------|------|------|--------------------------------|---------|--|--|

| SS<br>(V/ms) | SS VINSR EQUATION                                   |                     | VINSR_L (V/ms)           |      |      | VIN RISE TIME (0V to 12V) (ms) |         |  |  |

| (7/11/3/     |                                                     | 1.0VOUT             | 1.0VOUT 1.35VOUT 1.8VOUT |      |      | 1.35VOUT                       | 1.8VOUT |  |  |

| 1.867        | $VINSR \ge 11/15 \times VOUT - 0.41 \text{ (eq.1)}$ | 0.32                | 0.58                     | 0.91 | 37.5 | 20.7                           | 13.2    |  |  |

| 0.934        | $VINSR \ge 22/45 \times VOUT - 0.24 (eq.2)$         | 0.25                | 0.42                     | 0.64 | 48   | 28.6                           | 18.8    |  |  |

| 0.467        | $VINSR \ge 11/45 \times VOUT - 0.04 \text{ (eq.3)}$ | 0.2                 | 0.29                     | 0.4  | 60   | 41.4                           | 30      |  |  |

| 0.233        | $VINSR \ge 7/45 \times VOUT - 0.04 \text{ (eq.4)}$  | 0.12                | 0.17                     | 0.24 | 100  | 70.6                           | 50      |  |  |

| 0.117        | $VINSR \ge 1/15 \times VOUT + 0.01 \text{ (eq.5)}$  | 0.08                | 0.1                      | 0.13 | 150  | 120                            | 92.3    |  |  |

| 0.058        | $VINSR \ge 2/45 \times VOUT - 0.01 \text{ (eq.6)}$  | 0.03                | 0.02                     | 0.07 | 400  | 240                            | 171.4   |  |  |

| 0.029        | No minimum limitation                               | -                   |                          |      | -    |                                |         |  |  |

| 0.014        | No minimum limitation                               | -                   |                          |      |      | -                              |         |  |  |

Table.6 Minimum input voltage start-up slew rate and start-up time

## **Detailed Description**

The MYTNC1R84RELA2RA is a two-stage DCDC converter that is composed of a dual-phase charge pump-based DCDC converter and a dual-phase synchronous buck DCDC converter. The output voltage range supported from 0.7V to 1.8V (The output voltage range depend on the input voltage.) with load currents of up to 4A and up to 7.2W delivered to the external load. This module isn't designed for the parallel operation

## **Output Voltage Remote Sense Function**

The MYTNC1R84RELA2RA has a sense pin, +Sense, for this function. The function is capable of compensating for the voltage drop in the wiring by connecting the sense pin to the load point. The upper limit of the compensating by sense function depends on the maximum voltage allowed to the Vout pin (within range of the Output Voltage Accuracy). The sense trace should be as short as possible and shielded by the GND line or something else to reduce noise susceptibility.

The recommended sense line length is within 10cm for output voltage stability. Do NOT connect sense pin to the output of the additional LC filter that sits between the Vout pin and +Sense pin. If the remote sense is not needed, the +Sense pin should be shorted to the Vout pin.

#### Remote Enable Function

The MYTNC1R84RELA2RA has an enable input pin, ON/OFF, which is designed to be compatible with typical low voltage digital I/O levels so that it can be easily driven by an external controller. The ON/OFF pin logic is high active and connected to the VIN though internal resistors. So if external power sequencing or control is not required, the ON/OFF pin can be left open.

Document Category: Datasheet

## UltraBK<sup>™</sup> 4A DC-DC Converter Module

#### Soft start Function

The MYTNC1R84RELA2RA has an exquisite soft start function. This function prevents too large of an input rush current and output voltage overshoot. When the function is operating, the converter is controlled in discontinuous current mode (DCM), so the output ripple voltage may be larger than steady-state behavior which is in continuous current mode (CCM). If the input voltage drops and the operating state deviates from the operation area of fig.9, you should discharge the input voltage below the VIUVL and then restart.

This soft start function is also compatible with pre-bias start-up. However the converter cannot prevent reverse current except during soft start, so the output must NOT be connected to a circuit that has a voltage higher than the output voltage setting.

### **Power Good Operation**

MYTNC1R84RELA2RA has an open-drain "power good" pin, POK. The POK pin must be pulled up externally, though a resistor to a voltage of ≦5.5V. MYTNC1R84RELA2RA will hold the POK pin low during soft start, VOUT is outside of the regulation or when the fault condition is detected and being handled. Please note that the POK function will not work when the module is inactive. Therefore, the POK pin will be high impedance when VIN is below VIUVH or the module disabled.

The power good function is activated after soft start has finished. If the VOUT becomes within +5% to -5% of the target value, internal comparators detect the power good state and the power good signal becomes high. After that, if the VOUT rises or falls to outside of +10% or -10% of the target value, the power-good signal becomes low.

Power good function is a flag that indicates the output voltage status and internal protection status. If the POK pin isn't high for a long time from startup, there are some abnormal situation occur in inside the module or external environment.

So, we recommend monitoring POK pin and reset the module and output load in abnormal.

## **Telemetry System**

An ADC-based telemetry system is provided to monitor health of the MYTNC1R84RELA2RA and report status through the I<sup>2</sup>C interface for fault management and diagnostics. The following signals can be reported using the telemetry circuits: input voltage, output voltage, output current, and MYTNC1R84RELA2RA temperature. Typical parameters for temperature measurement function are as follows:

Resolution: 0.5°C Accuracy: ±3°C

Measurement time: 4ms

The telemetry register functionality is as follows:

- ADC presents a new value, which is latched internally and overwritten as new values come in.

- The read-only registers are updated with the latched values only when the upper byte is read.

- Reading a lower byte does not update the upper-lower byte combo value.

- Reading once returns the previous value; reading again returns the current value.

See the Electrical Characteristics table for additional information regarding telemetry.

The telemetry measurement temperature isn't the module surface temperature. The telemetry temperature is the measured value of the inside the module. So the telemetry temperature includes some error from the surface temperature.

Document Category: Datasheet

## UltraBK<sup>™</sup> 4A DC-DC Converter Module

### **Programming**

MYTNC1R84RELA2RA can be programmed through the I<sup>2</sup>C serial bus interface to configure certain system parameters. Those programable parameters are output voltage and soft start time. See the section of "Register Map" and "Detailed Register Description" for program to resister.

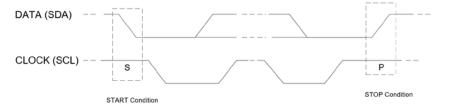

#### I<sup>2</sup>C Interface Bus Overview

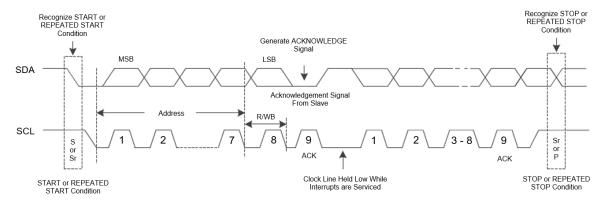

The I<sup>2</sup>C bus consists of a data line (SDA) and a clock line (SCL) with pull-up structures. When the bus is idle, both SDA and SCL lines are pulled high. All the I<sup>2</sup>C compatible devices connect to I<sup>2</sup>C bus through open drain I/O pins, SDA and SCL. A master device, usually a microcontroller or a digital signal processor, controls the bus. The master is responsible for generating the SCL signal and device addresses. The master also generates specific conditions that indicate the START and STOP of data transfer. An I<sup>2</sup>C slave device receives and/or transmits data on the bus under control of the master device.

MYTNC1R84RELA2RA operates as an I<sup>2</sup>C slave and supports the following data transfer modes, as defined in the I<sup>2</sup>C-Bus specification: Standard mode (100 Kbps) and fast mode (400 Kbps), and fast mode plus (1 Mbps). The interface adds flexibility to the power supply solution, enabling most functions to be programmed to new values depending on application requirements. Register contents remain intact as long as the VDD bias supply voltage remains above the under-voltage lockout threshold.

The data transfer protocol for standard and fast modes is exactly the same, therefore they are referred to as F/S-mode in this document. MYTNC1R84RELA2RA supports 7-bit addressing; 10-bit addressing and general call address are not supported. The device 7-bit address is defined as '0x30'.

### Standard-, Fast-, Fast-Mode Plus Protocol

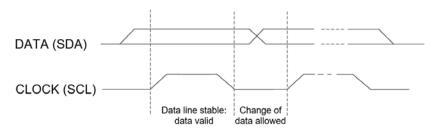

The master initiates data transfer by generating a start condition. The start condition is when a high-to-low transition occurs on the SDA line while SCL is high, as shown in Figure 10. All I<sup>2</sup>C-compatible devices should recognize a start condition.

Figure 10. START and STOP Conditions

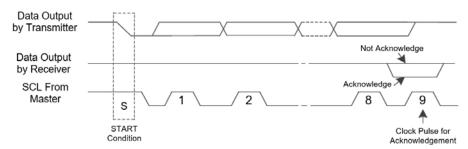

The master then generates the SCL pulses, and transmits the 7-bit address and the read/write direction bit R/W on the SDA line. During all transmissions, the master ensures that data is valid. A valid data condition requires the SDA line to be stable during the entire high period of the clock pulse (see Figure 11). All devices recognize the address sent by the master and compare it to their internal fixed addresses. Only the I<sup>2</sup>C slave device with a matching address generates an Acknowledge (see Figure 12) by pulling the SDA line low during the entire high period the ninth SCL cycle. Upon detecting this acknowledge, the master knows that communication link with an I<sup>2</sup>C slave has been established.

The master generates further SCL cycles to either transmit data to the I<sup>2</sup>C slave (R/W bit 1) or receive data from the I<sup>2</sup>C slave (R/W bit 0). In either case, the receiver needs to acknowledge the data sent by transmitter. So an acknowledge signal can either be generated by the master or by the I<sup>2</sup>C slave, depending on which one is the receiver. The 9-bit valid data sequences consisting of 8-bit data and 1-bit acknowledge can continue as long as necessary.

Document Category: Datasheet

## UltraBK<sup>™</sup> 4A DC-DC Converter Module

To signal the end of the data transfer, the master generates a stop condition by pulling the SDA line from low to high while the SCL line is high (see Figure 10). This releases the bus and stops the communication link with the addressed I<sup>2</sup>C slave. All I<sup>2</sup>C compatible devices must recognize the stop condition. Upon the receipt of a stop condition, all devices know that the bus is released, and they wait for a start condition followed by a matching address. Attempts to read data from register addresses not listed in this section will result in 0xFF being read out.

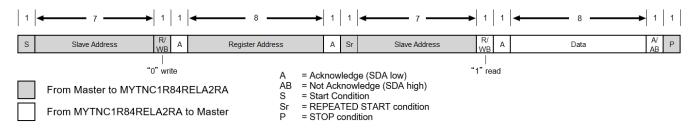

## I<sup>2</sup>C Update Sequence

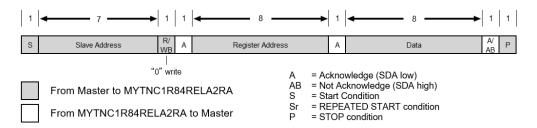

MYTNC1R84RELA2RA requires a start condition, a valid I<sup>2</sup>C address, a register address byte, and a data byte for a single update. After the receipt of each byte, MYTNC1R84RELA2RA device acknowledges by pulling the SDA line low during the high period of a single clock pulse. A valid I<sup>2</sup>C address selects the MYTNC1R84RELA2RA, which performs an update on the falling edge of the acknowledge signal that follows the LSB.

Figure 11. Bit Transfer on the Serial Interface

Figure 12. Acknowledge on the I<sup>2</sup>C Bus

Figure 13. Bus Protocol

**Document Category: Datasheet**

## UltraBK™ 4A DC-DC Converter Module

Figure 14. "Write" Data Transfer Format in Standard-, Fast, Fast-Plus Modes

Figure 15. "Read" Data Transfer Format in Standard-, Fast, Fast-Plus Modes

Document Category: Datasheet

# UltraBK™ 4A DC-DC Converter Module

## **Register Map**

l<sup>2</sup>C Slave Address: 0110000 (0x30) (1) Register Configuration Parameters

| VSET1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |  |  |  |  |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|--|--|--|--|

| DCR         0x02         0x00         DCR         Reserved(2)           CONFIG1         0x03         0x04         Reserved(2)         SS           RESERVED         0x04         0x00         Reserved(2)           RESERVED         0x05         0x8A         Reserved(2)           RESERVED         0x06         0x82         Reserved(2)           RESERVED         0x07         0x10         Reserved(2)           RESERVED         0x08         0x00         Reserved(2)           RESERVED         0x09         0x9F         Reserved(2)           RESERVED         0x0A         0x78         Reserved(2)           RESERVED         0x0B         0x78         Reserved(2) |                         |  |  |  |  |

| CONFIG1         0x03         0x04         Reserved(2)         SS           RESERVED         0x04         0x00         Reserved(2)           RESERVED         0x05         0x8A         Reserved(2)           RESERVED         0x06         0x82         Reserved(2)           RESERVED         0x07         0x10         Reserved(2)           RESERVED         0x08         0x00         Reserved(2)           RESERVED         0x09         0x9F         Reserved(2)           RESERVED         0x0A         0x78         Reserved(2)           RESERVED         0x0B         0x78         Reserved(2)                                                                         |                         |  |  |  |  |

| RESERVED         0x04         0x00         Reserved <sup>(2)</sup> RESERVED         0x05         0x8A         Reserved <sup>(2)</sup> RESERVED         0x06         0x82         Reserved <sup>(2)</sup> RESERVED         0x07         0x10         Reserved <sup>(2)</sup> RESERVED         0x08         0x00         Reserved <sup>(2)</sup> RESERVED         0x09         0x9F         Reserved <sup>(2)</sup> RESERVED         0x0A         0x78         Reserved <sup>(2)</sup> RESERVED         0x0B         0x78         Reserved <sup>(2)</sup>                                                                                                                          |                         |  |  |  |  |

| RESERVED         0x05         0x8A         Reserved(2)           RESERVED         0x06         0x82         Reserved(2)           RESERVED         0x07         0x10         Reserved(2)           RESERVED         0x08         0x00         Reserved(2)           RESERVED         0x09         0x9F         Reserved(2)           RESERVED         0x0A         0x78         Reserved(2)           RESERVED         0x0B         0x78         Reserved(2)                                                                                                                                                                                                                     |                         |  |  |  |  |

| RESERVED         0x06         0x82         Reserved(2)           RESERVED         0x07         0x10         Reserved(2)           RESERVED         0x08         0x00         Reserved(2)           RESERVED         0x09         0x9F         Reserved(2)           RESERVED         0x0A         0x78         Reserved(2)           RESERVED         0x0B         0x78         Reserved(2)                                                                                                                                                                                                                                                                                      |                         |  |  |  |  |

| RESERVED         0x07         0x10         Reserved <sup>(2)</sup> RESERVED         0x08         0x00         Reserved <sup>(2)</sup> RESERVED         0x09         0x9F         Reserved <sup>(2)</sup> RESERVED         0x0A         0x78         Reserved <sup>(2)</sup> RESERVED         0x0B         0x78         Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                   |                         |  |  |  |  |

| RESERVED         0x08         0x00         Reserved <sup>(2)</sup> RESERVED         0x09         0x9F         Reserved <sup>(2)</sup> RESERVED         0x0A         0x78         Reserved <sup>(2)</sup> RESERVED         0x0B         0x78         Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |  |

| RESERVED         0x09         0x9F         Reserved <sup>(2)</sup> RESERVED         0x0A         0x78         Reserved <sup>(2)</sup> RESERVED         0x0B         0x78         Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |  |  |  |  |

| RESERVED         0x0A         0x78         Reserved <sup>(2)</sup> RESERVED         0x0B         0x78         Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                         |  |  |  |  |

| RESERVED 0x0B 0x78 Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |  |  |  |  |

| RESERVED 0x0C 0x61 Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |  |  |  |  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                         |  |  |  |  |

| VOUT1_LSB         0x42         0x00         VOUT1         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         |  |  |  |  |

| VOUT1_MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                         |  |  |  |  |

| VIN 0x46 0x00 VIN                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                         |  |  |  |  |

| RESERVED 0x47 0x00 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |  |

| IOUTF1 0x48 0x00 IOUTF1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                         |  |  |  |  |

| IOUTP1_LSB         0x4A         0x00         IOUTP1         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |  |  |  |  |

| IOUTP1_MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |  |  |  |  |

| TEMP_LSB         0x4E         0x00         TEMP         Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                         |  |  |  |  |

| TEMP_MSB                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                         |  |  |  |  |

| MASTERFAULTS         0x54         0x00         Reserved         VOUT_ SHORT         VOUT_ OCP                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | OVER<br>TEMP            |  |  |  |  |

| RESERVED 0x55 0x00 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |                         |  |  |  |  |

| RESERVED 0x57 0x00 Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |  |  |  |  |

| RESERVED         0x58         0x00         Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                         |  |  |  |  |

| RESERVED 0x5A 0x00 Reserved                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | Reserved                |  |  |  |  |

| RESERVED 0x5B 0x00 Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | Reserved <sup>(2)</sup> |  |  |  |  |

| RESERVED 0x5C 0x00 Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |  |  |  |  |

| RESERVED 0x5D 0x00 Reserved <sup>(2)</sup>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                         |  |  |  |  |

| MTPWRITE 0x60 0x01 MTP_WRITE_CMD MTPWRI TEDNE Reserv                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                         |  |  |  |  |

| MTPUNLOCK 0x61 0x00 MTPUNLOCK_CMD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | /ed <sup>(2)</sup>      |  |  |  |  |

INNOVATOR IN ELECTRONICS

# **Preliminary**: MYTNC1R84RELA2RA

Document Category: Datasheet

## UltraBK<sup>™</sup> 4A DC-DC Converter Module

#### Note:

- (1) Excluding read/write bit. 01100000 (0x60) if including read/write bit.

- (2) Do not change these reserved bits. We guarantee operation of the module only when these reserved bit is the initial value.

#### Table 7. Register map

## **Detailed Register Description**

#### **Register VSET1**

| NAME  | ADDRESS | POR Value |

|-------|---------|-----------|

| VSET1 | 0x00    | 0x46      |

#### Bit Assignment

| 7          | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|------------|---|---|---|---|---|---|---|

| VSET1[7:0] |   |   |   |   |   |   |   |

#### Bit Description

| Field name | Bits  | Туре | POR      | Description                                                                                                                                                                                                                                                                                                      |

|------------|-------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| VSET1[7:0] | [7:0] | R/W  | 01000110 | VOUT1 = 2.55/256×bin2dec(VSET1<7:0>).  Program VOUT1 Output Voltage in 10mV steps: Do not exceed the specified limits of the output voltage range restricted by input voltage or the converter's maximum power rating when applying this register.  00h: 0mV 01h: 10mV 02h: 20mV 77h: 1.19V 78h: 1.2V 79h: 1.21V |

#### **Register VSET1**

| NAME | ADDRESS | POR Value |

|------|---------|-----------|

| DCR  | 0x02    | 0x00      |

#### Bit Assignment

| 7 | 6         | 5 | 4 | 3 | 2   | 1     | 0 |

|---|-----------|---|---|---|-----|-------|---|

|   | DCR [3:0] |   |   |   | Res | erved |   |

| Field name Bits Type POR Description |

|--------------------------------------|

|--------------------------------------|

Document Category: Datasheet

#### INNOVATOR IN ELECTRONICS

# UltraBK™ 4A DC-DC Converter Module

| DCR[3:0] | [7:4] | R/W | 0000 | DCR value for calculation of IOUT. The DCR value is written in test Production. |

|----------|-------|-----|------|---------------------------------------------------------------------------------|

|          |       |     |      |                                                                                 |

|          |       |     |      | 0000: 14.6 mΩ                                                                   |

|          |       |     |      | 0001: 15.4 mΩ                                                                   |

|          |       |     |      | 0010: 16.2 mΩ                                                                   |

|          |       |     |      | 0011: 17.0 mΩ                                                                   |

|          |       |     |      | 0100: 17.8 mΩ                                                                   |

|          |       |     |      | 0101: 18.6 mΩ                                                                   |

|          |       |     |      | 0110: 19.4 mΩ                                                                   |

|          |       |     |      | 0111: 20.2 mΩ                                                                   |

|          |       |     |      | 1000: 21.0 mΩ                                                                   |

|          |       |     |      | 1001: 21.8 mΩ                                                                   |

|          |       |     |      | 1010: 22.6 mΩ                                                                   |

|          |       |     |      | 1011: 23.4 mΩ                                                                   |

|          |       |     |      | 1100: 24.2 mΩ                                                                   |

|          |       |     |      | 1101: 25.0 mΩ                                                                   |

|          |       |     |      | 1110: 25.8 mΩ                                                                   |

|          |       |     |      | 1111: 26.6 mΩ                                                                   |

#### **Register CONFIG1**

| NAME    | ADDRESS | POR Value |

|---------|---------|-----------|

| CONFIG1 | 0x03    | 0x04      |