### 2.5 A Half-Bridge with integrated driver and level shifter

#### **Features**

- Integrated PMOS and NMOS complementary output bridge with 2.5 A current capability

- Integrated gate drivers

- Single control input with an integrated dead-time logic allows for optimized control and high efficiency

- Output current sensing and limitation

- Overtemperature protection

- Low quiescent current

- No external dead-time adjustment required

- Green product (RoHS compliant)

- AEC Qualified

- Grade 1 PG-TSON-10

- Grade 0 PG-TSDSO-14

# **Potential applications**

Core voltage regulation for AURIX<sup>™</sup> TC3xx microcontroller with the power management IC TLF3558x.

#### **Product validation**

Qualified for automotive applications. Product validation according to AEC-Q100/101.

# Description

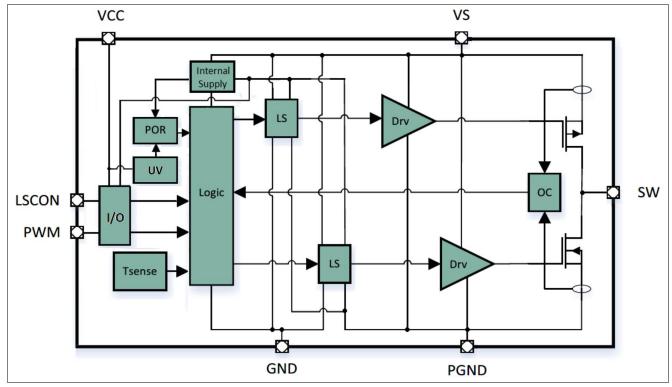

The TLF11251 is an integrated gate driver and half-bridge with a high-side P-channel MOSFET and a low-side N-channel MOSFET in a single package. The integrated level shifting stage allows for conversion of the input logic signals to the supply voltage level of the gate drivers. The input signal levels are CMOS compatible. The level shifter and the gate driver provide a dead-time generation to simplify the interface with the embedded core voltage regulator of the AURIX<sup>TM</sup> TC3xx microcontroller. The low propagation delay allows for use in closed loop control applications with limited requirements for timing. The output stage allows for a high switching frequency. The TLF11251 integrates protection features against overcurrent at high-side MOSFETs and low-side MOSFETs and against overtemperature events. Internal power-on reset releases the digital logic and ensures its operation for supply voltage within the specified range.

# 2.5 A Half-Bridge with integrated driver and level shifter

| Туре       | Package     | Marking  |

|------------|-------------|----------|

| TLF11251LD | PG-TSON-10  | 11251    |

| TLF11251EP | PG-TSDSO-14 | TLF11251 |

# 2.5 A Half-Bridge with integrated driver and level shifter

# Table of contents

| Block diagram                             | 4                                                                                                                                                                                                                                                                                                                                                                                              |

|-------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| -                                         |                                                                                                                                                                                                                                                                                                                                                                                                |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                |

|                                           |                                                                                                                                                                                                                                                                                                                                                                                                |

| Pin definitions and functions PG-TSDSO-14 |                                                                                                                                                                                                                                                                                                                                                                                                |

| General product characteristics           | 8                                                                                                                                                                                                                                                                                                                                                                                              |

| Absolute maximum ratings                  |                                                                                                                                                                                                                                                                                                                                                                                                |

| Functional range                          | 9                                                                                                                                                                                                                                                                                                                                                                                              |

| Thermal resistance                        | 10                                                                                                                                                                                                                                                                                                                                                                                             |

| Functional description                    | 11                                                                                                                                                                                                                                                                                                                                                                                             |

| Behavior of logical inputs                |                                                                                                                                                                                                                                                                                                                                                                                                |

| Control parameters                        | 12                                                                                                                                                                                                                                                                                                                                                                                             |

| Output stage                              | 14                                                                                                                                                                                                                                                                                                                                                                                             |

| Protection functions                      | 15                                                                                                                                                                                                                                                                                                                                                                                             |

| Undervoltage shutdown                     | 15                                                                                                                                                                                                                                                                                                                                                                                             |

| Overcurrent protection                    | 16                                                                                                                                                                                                                                                                                                                                                                                             |

| Overtemperature protection                | 17                                                                                                                                                                                                                                                                                                                                                                                             |

| Application information                   | 18                                                                                                                                                                                                                                                                                                                                                                                             |

| Typical application scenario              | 18                                                                                                                                                                                                                                                                                                                                                                                             |

| Further application information           | 19                                                                                                                                                                                                                                                                                                                                                                                             |

| Package information TLF11251              | 20                                                                                                                                                                                                                                                                                                                                                                                             |

| Revision history                          | 22                                                                                                                                                                                                                                                                                                                                                                                             |

|                                           | General product characteristics Absolute maximum ratings Functional range Thermal resistance  Functional description Behavior of logical inputs Control parameters Output stage Protection functions Undervoltage shutdown Overcurrent protection Overtemperature protection Application information Typical application scenario Further application information Package information TLF11251 |

Block diagram

# 1 Block diagram

Figure 1 Block diagram

Pin configuration

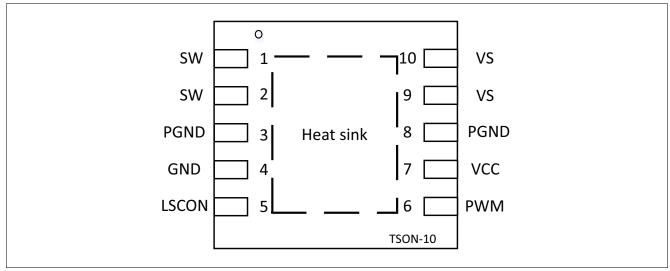

# 2 Pin configuration

# 2.1 Pin assignment PG-TSON-10

Figure 2 Pin configuration (TLF11251LD)

# 2.2 Pin definitions and functions PG-TSON-10

| Pin   | Symbol    | Function                                                                                                                                                                                                                                   |

|-------|-----------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1, 2  | SW        | Switch node; half-bridge drains, typically connected to the input of LC filter in buck circuits                                                                                                                                            |

| 3, 8  | PGND      | Power ground;<br>half-bridge low-side source                                                                                                                                                                                               |

| 4     | GND       | Ground;<br>Logical ground                                                                                                                                                                                                                  |

| 5     | LSCON     | Bridge control scheme; Defines low-side state during PWM input "high". Switch to "high": enable synchronous control of high-side and low-sidelow-side, based on PWM input state Switch to "low": disable low-side control                  |

| 6     | PWM       | Control input; Input for the logical signal that controls the state of the half-bridge transistors. Switch to "high": open high-side switch and close the low-side switch Switch to "low": close high-side switch and open low-side switch |

| 7     | VCC       | Supply voltage input; Supply voltage for the PWM and LSCON inputs; typically the same as the supply of microcontroller output pins                                                                                                         |

| 9, 10 | VS        | Supply voltage input; Provides supply to gate drivers, connected to half-bridge high-side source                                                                                                                                           |

| _     | Heat Sink | Connect to heat sink area and to GND and PGND                                                                                                                                                                                              |

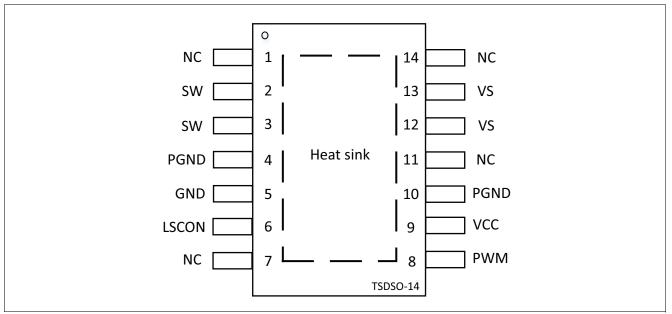

Pin configuration

# 2.3 Pin assignment PG-TSDSO-14

Figure 3 Pin configuration (TLF11251EP)

## 2.4 Pin definitions and functions PG-TSDSO-14

| Pin   | Symbol | Function                                                                                                                                                                                                                                   |

|-------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1     | NC     | Not connected; This pin is not connected internally. Leave open                                                                                                                                                                            |

| 2, 3  | SW     | Switch node; half-bridge drains, typically connected to the input of LC filter in buck circuits                                                                                                                                            |

| 4, 10 | PGND   | Power ground;<br>half-bridge low-side source                                                                                                                                                                                               |

| 5     | GND    | Ground;<br>Logical ground                                                                                                                                                                                                                  |

| 6     | LSCON  | Bridge control scheme; Defines low-side state during PWM input "high". Switch to "high": enable synchronous control of high-side and low-side, based on PWM input state Switch to "low": disable low-side control                          |

| 7     | NC     | Not connected; This pin is not connected internally. Leave open                                                                                                                                                                            |

| 8     | PWM    | Control input; Input for the logical signal that controls the state of the half-bridge transistors. Switch to "high": open high-side switch and close the low-side switch Switch to "low": close high-side switch and open low-side switch |

| 9     | VCC    | Supply voltage input; Supply voltage for the PWM and LSCON inputs; typically the same as the supply of microcontroller output pins                                                                                                         |

# 2.5 A Half-Bridge with integrated driver and level shifter

## Pin configuration

| Pin    | Symbol    | Function                                                                                         |

|--------|-----------|--------------------------------------------------------------------------------------------------|

| 11     | NC        | Not connected; This pin is not connected internally. Leave open                                  |

| 12, 13 | VS        | Supply voltage input; Provides supply to gate drivers, connected to half-bridge high-side source |

| 14     | NC        | Not connected; This pin is not connected internally. Leave open                                  |

| _      | Heat Sink | Connect to heat sink area and to GND and PGND                                                    |

**General product characteristics**

#### General product characteristics 3

#### 3.1 Absolute maximum ratings

#### Absolute maximum ratings1) Table 1

$T_i = -40$ °C to +150°C; all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                              | Symbol           |      | Value | s    | Unit | Note or Test Condition                     | Number   |  |

|----------------------------------------|------------------|------|-------|------|------|--------------------------------------------|----------|--|

|                                        |                  | Min. | Тур.  | Max. |      |                                            |          |  |

| Voltages                               |                  |      | 1     |      | -    |                                            | '        |  |

| Supply voltage VS                      | $V_{S}$          | -0.3 | -     | 7.0  | V    | -                                          | P_3.1.1  |  |

| Supply voltage VCC                     | $V_{\rm cc}$     | -0.3 | -     | 7.0  | V    | -                                          | P_3.1.2  |  |

| Switch node SW                         | $V_{\rm SW}$     | -0.3 | -     | 7.0  | V    | -                                          | P_3.1.3  |  |

| Input PWM                              | $V_{\text{PWM}}$ | -0.3 | -     | 7.0  | V    | -                                          | P_3.1.4  |  |

| Input LSCON                            | $V_{LSCON}$      | -0.3 | -     | 7.0  | V    | -                                          | P_3.1.5  |  |

| Currents                               |                  |      |       |      |      |                                            | •        |  |

| Continuous drain current high-<br>side | I <sub>DHS</sub> | -2.5 | _     | _    | А    | PWM = off                                  | P_3.1.6  |  |

| Continuous drain current low-<br>side  | I <sub>DLS</sub> | -    | _     | 2.5  | А    | PWM = on                                   | P_3.1.7  |  |

| Pulsed drain current high-side         | I <sub>DHS</sub> | -4.4 | -     | -    | A    | Valid during active overcurrent protection | P_3.1.8  |  |

| Pulsed drain current low-side          | I <sub>DLS</sub> | _    | _     | 4.4  | A    | Valid during active overcurrent protection | P_3.1.9  |  |

| Temperatures                           |                  |      |       |      |      |                                            |          |  |

| Junction temperature                   | T <sub>j</sub>   | -40  | _     | 150  | °C   | -                                          | P_3.1.10 |  |

| Storage temperature                    | $T_{\rm stg}$    | -55  | _     | 150  | °C   | -                                          | P_3.1.11 |  |

| ESD susceptibility                     |                  |      |       |      |      |                                            |          |  |

| ESD susceptibility all pins            | $V_{ESD}$        | -2   | -     | 2    | kV   | HBM <sup>2)</sup>                          | P_3.1.12 |  |

| ESD susceptibility all pins            | $V_{ESD}$        | -500 | _     | 500  | V    | CDM <sup>3)</sup>                          | P_3.1.13 |  |

| ESD susceptibility (corner pins)       | $V_{\rm ESD}$    | -750 | _     | 750  | ٧    | CDM <sup>3)</sup>                          | P_3.1.14 |  |

- 1) Not subject to production test, specified by design.

- 2) ESD susceptibility, HBM according to ANSI/ESDA/JEDEC JS001 (1.5 k $\Omega$ , 100 pF.)

- ESD susceptibility, Charged Device Model "CDM" according JEDEC JESD22-C101.

#### **Notes**

1. Stresses above the ones listed here may cause permanent damage to the device. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

### 2.5 A Half-Bridge with integrated driver and level shifter

#### **General product characteristics**

2. Integrated protection functions are designed to prevent IC destruction under fault conditions described in the data sheet. Fault conditions are considered as outside normal operating range. Protection functions are not designed for continuous repetitive operation.

#### **Functional range** 3.2

Table 2 **Functional range**

| Parameter                              | Symbol              |      | Value | s    | Unit | Note or                                                       | Number   |

|----------------------------------------|---------------------|------|-------|------|------|---------------------------------------------------------------|----------|

|                                        |                     | Min. | Тур.  | Max. |      | <b>Test Condition</b>                                         |          |

| Supply voltage range VS                | $V_{S,nom}$         | 3.5  | _     | 7.0  | V    | _                                                             | P_3.2.1  |

| Supply voltage range VCC               | $V_{\rm CC,nom}$    | 2.35 | _     | 7.0  | V    | _                                                             | P_3.2.2  |

| Supply voltage VS transient slew rate  |                     | -120 | -     | 120  | V/ms | 1)                                                            | P_3.2.3  |

| Supply voltage VCC transient slew rate | $dV_{CC}/dt$        | -120 | -     | 120  | V/ms | 1)                                                            | P_3.2.4  |

| Junction temperature                   | $T_{\rm j}$         | -40  | _     | 150  | °C   | AEC-Q100 Grade 1                                              | P_3.2.5  |

|                                        | T <sub>j</sub>      | -40  | -     | 175  | °C   | AEC-Q100 Grade 0<br>PG-TSDSO14 only                           | P_3.2.6  |

| Supply current total, normal operation | I <sub>C,norm</sub> | -    | -     | 35   | mA   | PWM input<br>@1.8MHz                                          | P_3.2.9  |

| Supply current total, no switching     | I <sub>C,ns</sub>   | _    | 200   | -    | μΑ   | VS < 5.8 V, V <sub>cc</sub> < 5.1<br>V, T <sub>j</sub> < 85°C | P_3.2.10 |

<sup>1)</sup> Not subject to production test, specified by design.

Note:

Within the functional or operating range, the IC operates as described in the circuit description. The electrical characteristics are specified within the conditions given in the Electrical Characteristics table.

### 2.5 A Half-Bridge with integrated driver and level shifter

#### **General product characteristics**

#### 3.3 Thermal resistance

Note:

This thermal data was generated in accordance with JEDEC JESD51 standards. For more information, go to www.jedec.org.

Table 3 Thermal resistance 1)

| Parameter                               | Symbol                   |      | Value | s    | Unit | Note or<br>Test Condition | Number   |

|-----------------------------------------|--------------------------|------|-------|------|------|---------------------------|----------|

|                                         |                          | Min. | Тур.  | Max. |      |                           |          |

| PG-TSON-10                              |                          |      |       | 1    |      |                           | 1        |

| Junction to case top - high-side        | $R_{\rm thJCT(HS)}$      | 51.6 | -     | 57.0 | K/W  | _                         | P_3.3.1  |

| Junction to case top - low-side         | R <sub>thJCT(LS)</sub>   | 64.5 | _     | 71.2 | K/W  | _                         | P_3.3.2  |

| Junction to case bottom - high-<br>side | R <sub>thJCB(HS)</sub>   | 6.3  | -     | 6.9  | K/W  | -                         | P_3.3.3  |

| Junction to case bottom - low-<br>side  | $R_{\mathrm{thJCB(LS)}}$ | 9.4  | -     | 10.4 | K/W  | -                         | P_3.3.4  |

| Junction to ambient                     | $R_{thJA}$               | -    | 54.5  | _    | K/W  | 2)                        | P_3.3.5  |

| PG-TSDSO-14                             |                          |      |       | 1    |      |                           | 1        |

| Junction to case top - high-side        | R <sub>thJCT(HS)</sub>   | 30.9 | -     | 34.1 | K/W  | _                         | P_3.3.6  |

| Junction to case top - low-side         | R <sub>thJCT(LS)</sub>   | 39.5 | -     | 43.7 | K/W  | _                         | P_3.3.7  |

| Junction to case bottom - high-<br>side | R <sub>thJCB(HS)</sub>   | 9.6  | -     | 10.6 | K/W  | -                         | P_3.3.8  |

| Junction to case bottom - low-<br>side  | $R_{\rm thJCB(LS)}$      | 13.4 | -     | 14.8 | K/W  | -                         | P_3.3.9  |

| Junction to ambient                     | $R_{thJA}$               | -    | 43.3  | _    | K/W  | 2)                        | P_3.3.10 |

<sup>1)</sup> Not subject to production test, specified by design.

<sup>2)</sup> Specified  $R_{thJA}$  value is according to Jedec JESD51-2,-5,-7 at natural convection on FR4 2s2p board; The product (chip + package) was simulated on a 76.2 × 114.3 × 1.5 mm<sup>3</sup> board with 2 inner copper layers (2 × 70  $\mu$ m Cu, 2 × 35  $\mu$ m Cu). Where applicable a thermal via array under the exposed pad contacted the first inner copper layer.

#### 2.5 A Half-Bridge with integrated driver and level shifter

**Functional description**

## 4 Functional description

The TLF11251 integrated driver and lever shifter simplifies the interface of microcontroller control outputs to the MOSFET half-bridge.

### 4.1 Behavior of logical inputs

A single PWM input controls the state of the half-bridge MOSFETs. The inverted logical scheme translates the PWM input state to the gate signal shifted to the output supply level, thus the high-side MOSFET is turned off during PWM logical ON state, and turned on during PWM logical OFF state. The built-in dead-time control circuitry prevents a shoot-through condition over the MOSFET bridge and improves system efficiency while used in buck power conversion circuits. No external dead-time adjustment is required.

In addition to the PWM input, the LSCON input determines the low-side MOSFET control scheme and allows for both synchronous as well as asynchronous operation in buck converter applications. Logical OFF state at the LSCON input turns off the low-side MOSFET independently of the PWM input signal, so that only the high-side MOSFET is controlled.

A permanent logical ON state at LSCON input allows both high-side and low-side operation according to PWM input state with the internal dead-time generation. The LSCON input can be pulled-up or connected directly to the VCC supply rail if such operation is required.

A toggling input signal at LSCON is recognized as a control request for synchronous low-side and high-side MOSFET switching. In this case the TLF11251 generates dead-time internally in accordance with the PWM input timing. Frequency detection at LSCON inputs detect toggling input signals within the acceptable range referred to as  $t_{\rm det}$ .

Table 4 Switching states

| LSCON                                              | PWM               | high-side MOSFET | low-side MOSFET |

|----------------------------------------------------|-------------------|------------------|-----------------|

| ON                                                 | ON <sup>1)</sup>  | Turned off       | Turned on       |

| ON                                                 | OFF <sup>2)</sup> | Turned on        | Turned off      |

| OFF                                                | ON                | Turned off       | Turned off      |

| OFF                                                | OFF               | Turned on        | Turned off      |

| Toggling ON/OFF <sup>3)</sup>                      | ON                | Turned off       | Turned on       |

|                                                    | OFF               | Turned on        | Turned off      |

| Toggling ON/OFF stop <sup>4)</sup>                 | ON                | Turned off       | Turned on       |

| $(< t_{fil})$                                      | OFF               | Turned on        | Turned off      |

| Toggling ON/OFF stop (> $t_{\rm fil}$ ); LSCON=ON  | ON                | Turned off       | Turned on       |

| Toggling ON/OFF stop (> $t_{\rm fil}$ ); LSCON=ON  | OFF               | Turned on        | Turned off      |

| Toggling ON/OFF stop (> $t_{\rm fil}$ ); LSCON=OFF | ON                | Turned off       | Turned off      |

| Toggling ON/OFF stop (> $t_{fil}$ ); LSCON=OFF     | OFF               | Turned on        | Turned off      |

<sup>1)</sup> ON: "high"

<sup>2)</sup> OFF: "low"

<sup>3)</sup> Toggling ON/OFF - detected ON/OFF switching with the frequency within the detection range  $t_{\text{det}}$  at LSCON input signal.

#### **Functional description**

4) Toggling ON/OFF stop - detected permanent ON or OFF state after the Toggling ON/OFF operation

The states described in **Table 4** are only valid for device input supplies within the operational range and when no protection features are active.

If the PWM pin is not connected, then the integrated weak pull-up ensures a defined level.

An additional pull-down resistor should be placed at LSCON input to keep the low-side MOSFET turned off during power-down in the case where the TLF11251 is controlled by an AURIX<sup>™</sup> TC3xx microcontroller. Please refer to Chapter 5 for more details.

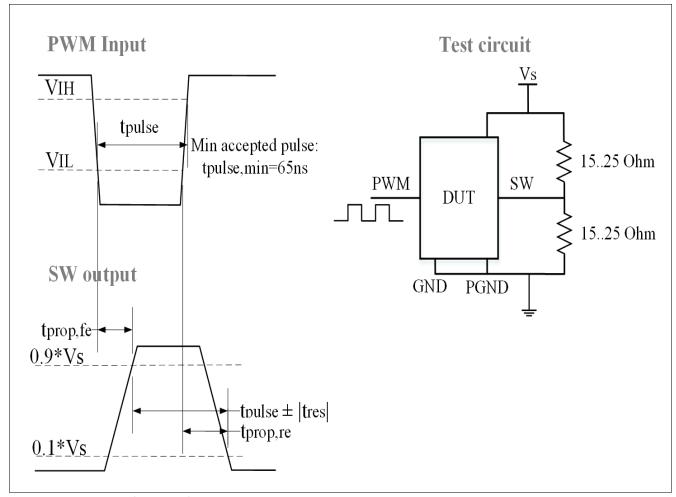

### 4.2 Control parameters

The TLF11251 provides a high frequency switching capability with a low propagation delay. The input stage and the drivers can react to fast changing PWM signals and provide a  $t_{\rm res}$  resolution to the duty time of the input signal with a pulse duration longer than  $t_{\rm pulse}$ . The low state pulse duration is limited to  $t_{\rm pulse,\,min.}$

The total propagation time  $t_{\rm prop}$  is the time from the "low"-to-"high" or "high"-to-"low" edge transition at the PWM input to the SW output level transitions to 10% or 90% of  $V_{\rm S}$  supply level accordingly. The internal dead-time generation provides optimal efficiency during switching phases and provides the state change of the switching node SW within the specified propagation delay.

The device is optimized for a switching frequency in a typical buck converter application in the range of 0.3 MHz to 2 MHz.

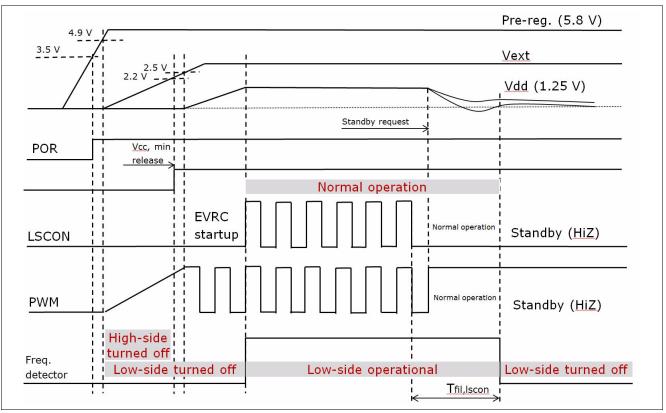

Figure 4 Control timing diagram

## 2.5 A Half-Bridge with integrated driver and level shifter

#### **Functional description**

### Table 5 Electrical characteristics: control parameters

$V_{\rm S}$  = 3.5 V to 7 V,  $V_{\rm cc}$  = 2.35 V to 7 V,  $T_{\rm j}$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                 | Symbol                 |                        | Values | 5                      | Unit | Note or                                                                         | Number   |

|-------------------------------------------|------------------------|------------------------|--------|------------------------|------|---------------------------------------------------------------------------------|----------|

|                                           |                        | Min.                   | Тур.   | Max.                   |      | Test Condition                                                                  |          |

| Propagation time, PWM falling edge        | $t_{prop,fe}$          | _                      | _      | 60                     | ns   | HS drain connected to resistive load. $V_{\rm CC}$ > 3.0 V, $V_{\rm S}$ > 4.5 V | P_4.2.1  |

| Propagation time, PWM rising edge         | t <sub>prop,re</sub>   | -                      | _      | 60                     | ns   | LS drain connected<br>to resistive load. $V_{CC}$ > 3.0 V, $V_{S}$ > 4.5 V      | P_4.2.2  |

| Minimum pulse width input                 | $t_{ m pulse,min}$     | 65                     | _      | _                      | ns   | 1)                                                                              | P_4.2.3  |

| Pulse resolution time                     | t <sub>res</sub>       | _                      | _      | 3                      | ns   | 1)                                                                              | P_4.2.4  |

| Dead-time "high"-to-"low"                 | t <sub>dead,hl</sub>   | _                      | 15     | _                      | ns   | 1)                                                                              | P_4.2.5  |

| Dead-time "low"-to-"high"                 | t <sub>dead,lh</sub>   | _                      | 18     | _                      | ns   | 1)                                                                              | P_4.2.6  |

| LSCON frequency detector, frequency range | f <sub>det,lscon</sub> | 0.72                   | -      | -                      | MHz  | _                                                                               | P_4.2.7  |

| LSCON frequency detector, filter time     | $t_{ m fil,lscon}$     | 3                      | _      | -                      | us   | 1)                                                                              | P_4.2.8  |

| Logic inputs                              |                        | ı                      |        | ı                      |      |                                                                                 | ,        |

| Input voltage "high"                      | $V_{IH}$               | 0.67 × V <sub>cc</sub> | -      | _                      | V    | CMOS function                                                                   | P_4.2.9  |

| Input voltage "low"                       | $V_{IL}$               | _                      | _      | 0.33 × V <sub>cc</sub> | V    | CMOS function                                                                   | P_4.2.10 |

| Input voltage hysteresis                  | $V_{IHYS}$             | 0.05                   | _      | _                      | V    | -                                                                               | P_4.2.11 |

| Input capacitance                         | C <sub>IN</sub>        | _                      | 10     | _                      | pF   | 1)                                                                              | P_4.2.12 |

<sup>1)</sup> Not subject to production test, specified by design.

### 2.5 A Half-Bridge with integrated driver and level shifter

### **Functional description**

### 4.3 Output stage

The P-N-channel output half-bridge of the TLF11251 can operate at high switching frequency up to 2 MHz nominal range, providing very low power dissipation while used in synchronous buck converter topology. The P-channel MOSFET is used as a high-side switch, which eliminates the need to use a charge pump circuitry and also improves the EMI performance. The output stage delivers a minimum output current of at least 2.5 A within the specified voltage and temperature range.

#### Table 6 Electrical characteristics: output stage

$V_S$  = 3.5 V to 7 V,  $V_{cc}$  = 2.35 V to 7 V,  $T_j$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                            | Symbol            |      | Values |      | Unit | Note or<br>Test Condition                                                                                          | Number  |

|--------------------------------------|-------------------|------|--------|------|------|--------------------------------------------------------------------------------------------------------------------|---------|

|                                      |                   | Min. | Тур.   | Max. |      |                                                                                                                    |         |

| ON state resistance high-<br>side    | R <sub>ONHS</sub> | _    |        | 100  | mΩ   | $T_{\rm j} <= 150 ^{\circ}\text{C},$<br>$I_{\rm d} = -2 \text{A},$<br>$V_{\rm s} = 5.8 \text{V}$                   | P_4.3.1 |

|                                      |                   | -    | -      | 70   | mΩ   | $I_{\rm d}^{(1)} T_{\rm j} <= 85^{\circ} {\rm C},$ $I_{\rm d}^{(1)} = -2 {\rm A},$ $V_{\rm s}^{(2)} = 5.8 {\rm V}$ | P_4.3.2 |

| ON state resistance low-side         | R <sub>ONLS</sub> | _    | -      | 105  | mΩ   | $T_{\rm j} <= 150 {\rm ^{\circ}C},$<br>$I_{\rm d} = 2 {\rm A},$<br>$V_{\rm s} = 5.8 {\rm V}$                       | P_4.3.3 |

|                                      |                   | _    | _      | 75   | mΩ   | $I_{\rm d}^{1)}T_{\rm j} <= 85^{\circ}{\rm C},$ $I_{\rm d} = 2 {\rm A},$ $V_{\rm s} = 5.8 {\rm V}$                 | P_4.3.4 |

| Body diode forward voltage high-side | V <sub>DFHS</sub> | _    | 0.67   | 0.95 | V    | I <sub>fw</sub> = 2 A                                                                                              | P_4.3.5 |

| Body diode forward voltage low-side  | $V_{DFLS}$        | _    | 0.72   | 0.91 | V    | I <sub>fw</sub> = 2 A                                                                                              | P_4.3.6 |

<sup>1)</sup> Not subject to production test, specified by design.

**Functional description**

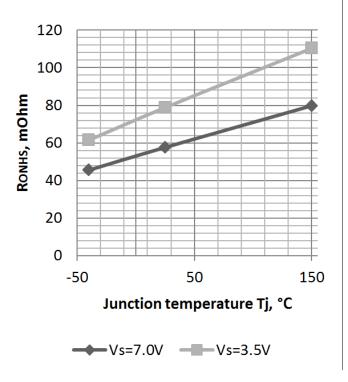

#### Maximum ON state resistance

ON state resistance high-side  $R_{ONHS}$  (PWM = "low"),  $versus T_j$  = -40,25,150°C

ON state resistance low-side  $R_{ONLS}$  (PWM = "high"), versus  $T_i$  = -40,25,150°C

#### 4.4 Protection functions

Integrated protection functions prevent the TLF11251 and the output circuitry from destruction as well as from operation under unspecified conditions. The implemented features consist of:

- high-side and low-side overcurrent detection and limitation

- undervoltage shutdown

- overtemperature protection

The TLF11251 reacts within the time specified for each protection feature. In all cases this is related to the state change of the half-bridge MOSFETs independent from the PWM input signal. The input logic reset release is ensured at  $V_{\rm S}$  voltage exceeding the minimum functional limit of 3.5 V, where protection functions are also operational. For the  $V_{\rm CC}$  voltage below  $V_{\rm CCUV}$ , the output half-bridge MOSFETs remain in the OFF state and the output switch node SW is floating.

### 4.4.1 Undervoltage shutdown

The TLF11251 monitors the input supply  $V_{\rm CC}$  for undervoltage conditions. If the output voltage drops below the  $V_{\rm ccuv}$  limit, then the TLF11251 turns off the high-side and low-side MOSFETs, so that the device is only operational within the specified supply limits. The voltage hysteresis circuitry  $V_{\rm ccuvh}$  protects from noise conditions.

**Functional description**

#### Table 7 Electrical characteristics: undervoltage shutdown

$V_S$  = 3.5 V to 7 V,  $T_j$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                             | Symbol             |      | Value | 5    | Unit | Note or                 | Number    |

|---------------------------------------|--------------------|------|-------|------|------|-------------------------|-----------|

|                                       |                    | Min. | Тур.  | Max. |      | Test Condition          |           |

| Undervoltage limit at $V_{CC}$ supply | V <sub>ccuv</sub>  | 1.95 | -     | 2.28 | V    | V <sub>CC</sub> falling | P_4.4.2.1 |

| Undervoltage detector hysteresis      | V <sub>ccuvh</sub> | 0.05 | -     | 0.1  | V    | _                       | P_4.4.2.2 |

| Undervoltage detector reaction time   | V <sub>uvr</sub>   | -    | -     | 3    | us   | 1)                      | P_4.4.2.3 |

<sup>1)</sup> Not subject to production test, specified by design.

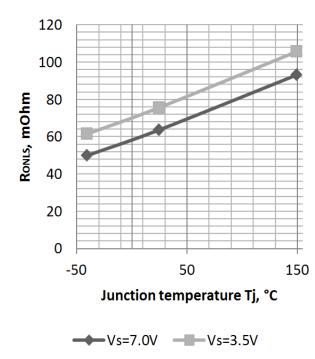

#### 4.4.2 Overcurrent protection

The overcurrent protection works in a cycle-by-cycle limitation mode. If the sensed input drain current exceeds the peak current limit  $I_{\rm oc,\ lim}$  during a switching cycle, then the TLF11251 turns off the high-side MOSFET and the switch node SW current starts to decay. If the overcurrent protection circuitry is active, then the TLF11251 limits the PWM input duty cycle for each cycle.

During startup or with  $V_{\rm CC}$  supply power cycle after the logic reset is released, the overcurrent protection remains inactive for the number of PWM pulses  $n_{\rm pwm,st}$  to avoid accidental activation due to start-up current overshoot.

Figure 5 Overcurrent protection function

#### 2.5 A Half-Bridge with integrated driver and level shifter

#### **Functional description**

#### Table 8 Electrical characteristics: overcurrent protection

$V_{\rm S}$  = 3.5 V to 7 V,  $V_{\rm cc}$  = 2.35 V to 7 V,  $T_{\rm j}$  = -40°C to +150°C, all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                                          | Symbol               | Values |      | Unit | Note or | Number                                      |           |

|----------------------------------------------------|----------------------|--------|------|------|---------|---------------------------------------------|-----------|

|                                                    |                      | Min.   | Тур. | Max. |         | Test Condition                              |           |

| Overcurrent sensing limit                          | I <sub>oc, lim</sub> | -4.4   | _    | -2.6 | Α       | -                                           | P_4.4.3.1 |

| Start-up protection inactive, number of PWM pulses | n <sub>pwm,st</sub>  | _      | _    | 5500 | -       | $V_{\rm CC}$ raising above $V_{\rm CC,min}$ | P_4.4.3.2 |

### 4.4.3 Overtemperature protection

If an overtemperature condition  $T_{\rm jOT}$  occurs the integrated temperature sensor disables the device by switching off the high-side and low-side MOSFETs. Only if both the temperature decreases by the hysteresis temperature d $T_{\rm j}$  and the temperature falls below  $T_{\rm jSO}$ , then the MOSFETs resume operation .

#### Table 9 Electrical characteristics: overtemperature protection

$V_S = 3.5 \text{ V}$  to 7 V,  $V_{cc} = 2.35 \text{ V}$  to 7 V,  $T_j = -40 ^{\circ}\text{C}$  to +150  $^{\circ}\text{C}$ , all voltages with respect to ground, positive current flowing into pin (unless otherwise specified)

| Parameter                            | Symbol           |      | Values |      |    | Note or        | Number    |

|--------------------------------------|------------------|------|--------|------|----|----------------|-----------|

|                                      |                  | Min. | Тур.   | Max. |    | Test Condition |           |

| Overtemperature shut-down            | $T_{\text{jOT}}$ | 175  | -      | 200  | °C | 1)             | P_4.4.4.1 |

| Switch on temperature                | $T_{\rm jSO}$    | _    | _      | 165  | °C | 1)             | P_4.4.4.2 |

| Overtemperature switch-on hysteresis | $dT_j$           | -    | 15     | -    | °C | 1)             | P_4.4.4.3 |

<sup>1)</sup> Not subject to production test, specified by design.

**Application information**

### 5 Application information

Note:

The following information is given as a hint for the implementation of the device only and shall not be regarded as a description or warranty of a certain functionality, condition or quality of the device.

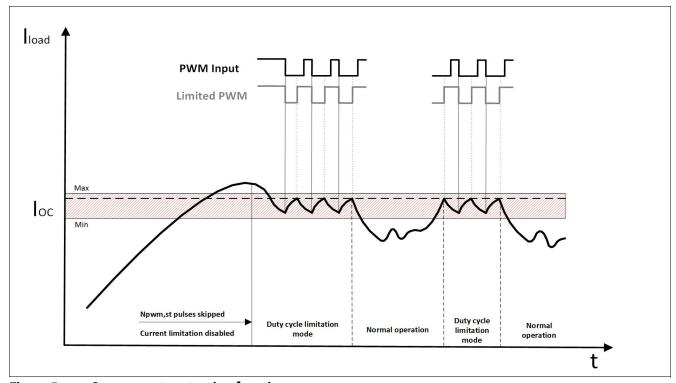

#### 5.1 Typical application scenario

In the target application scenario the TLF11251 is the counterpart for an AURIX<sup>TM</sup> TC3xx microcontroller for core voltage generation with the system power supply TLF35584. The device configuration allows connectivity with the half-bridge control output of the microcontroller's Embedded Voltage Regulator Core (EVRC) converter, which generates the core voltage  $V_{\rm dd}$ . The TLF11251 only supports power supply topologies that use different sources for the microcontroller pad supply domain  $V_{\rm ext}$  and the EVRC input  $V_{\rm S}$ , expecting different voltage levels. The system integrator must ensure that the  $V_{\rm S}$  voltage exceeds the  $V_{\rm CC}$  voltage during start-up, normal operation and power-down.

Figure 6 Application block diagram

As soon as the  $V_S$  supply voltage reaches 3.5 V during power-up, the internal logic reset will be released. During this phase the central function logic is operational. Only if the  $V_{CC}$  supply voltage is within the specified range, then the TLF11251 reacts to input signals LSCON and PWM as specified. However, the operational  $V_{CC}$  voltage minimum is specified at 2.35 V, which allows for early device readiness, even if the microcontroller is not yet operational.

The VGATEP output of the microcontroller controls the PWM signal, while the VGATEN output is connected to LSCON. The microcontroller typically starts in an open-loop mode, controlling only VGATEP and allowing for fast  $V_{\rm dd}$  voltage ramp-up and start-up. After ramp-up time, the EVRC starts to control the high-side and low-side MOSFETs of the half-bridge. The LSCON input detects this phase with the frequency detector. If the microcontroller is switched into power-down mode and if the high-side and low-side control signals are off, then the frequency detector recognizes it as a request to set the SW output floating. Hence it is highly

#### **Application information**

recommended to add a pull-down resistor for the LSCON signal in order to limit its possible variation during the power-down phase after the moment when the supply voltage reaches the hard reset limits of the microcontroller.

Figure 7 Start-up and ramp-down example flow<sub>B</sub>

Table 10 specify the required nominal values of the discrete components for proper operation.

Table 10 Nominal values of discrete components

| Component name     | Nominal value | Acceptable variation | Note                  |

|--------------------|---------------|----------------------|-----------------------|

| C <sub>VS</sub>    | 10 uF         | +/-30%               | Input capacitor       |

| $C_{\text{VDD}}$   | 22 uF         | +/-30%               | Output capacitor      |

| $L_{\text{VDD}}$   | 3.3 uH        | +/-30% (@1.8 MHz)    | Output inductor       |

| R <sub>LSCON</sub> | 6.2 kOhm      | +/-20%               | LSCON input pull-down |

### 5.2 Further application information

- Please contact us for information regarding the Pin Behavior Assessment

- For further information you may contact <a href="http://www.infineon.com/">http://www.infineon.com/</a>

Package information TLF11251

#### Package information TLF11251 6

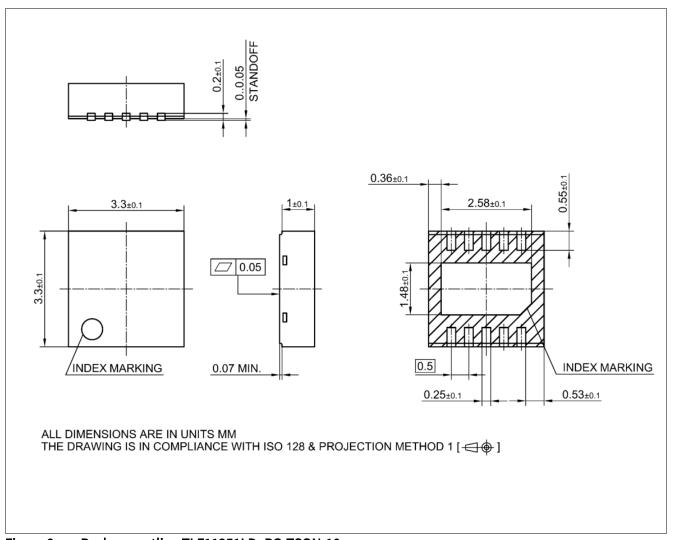

Package outline TLF11251LD- PG-TSON-10 Figure 8

#### Package information TLF11251

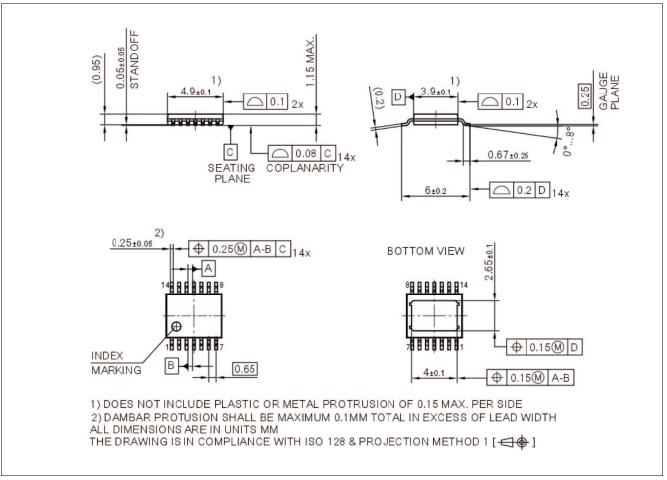

Figure 9 Package outline TLF11251EP - PG-TSDSO-14

#### **Green product (RoHS compliant)**

To meet the world-wide customer requirements for environmentally friendly products and to be compliant with government regulations the device is available as a green product. Green products are RoHS compliant (i.e Pb-free finish on leads and suitable for Pb-free soldering according to IPC/JEDEC J-STD-020).

# 2.5 A Half-Bridge with integrated driver and level shifter

**Revision history**

# 7 Revision history

## Table 11 Revision history

| Revision | Date       | Changes           |

|----------|------------|-------------------|

| 1.0      | 2020-01-23 | Initial datasheet |

#### **Trademarks**

All referenced product or service names and trademarks are the property of their respective owners.

Edition 2020-01-23 Published by Infineon Technologies AG 81726 Munich, Germany

© 2020 Infineon Technologies AG. All Rights Reserved.

Do you have a question about any aspect of this document?

Email: erratum@infineon.com

Document reference Z8F57382527

#### IMPORTANT NOTICE

The information given in this document shall in no event be regarded as a guarantee of conditions or characteristics ("Beschaffenheitsgarantie").

With respect to any examples, hints or any typical values stated herein and/or any information regarding the application of the product, Infineon Technologies hereby disclaims any and all warranties and liabilities of any kind, including without limitation warranties of non-infringement of intellectual property rights of any third party.

In addition, any information given in this document is subject to customer's compliance with its obligations stated in this document and any applicable legal requirements, norms and standards concerning customer's products and any use of the product of Infineon Technologies in customer's applications.

The data contained in this document is exclusively intended for technically trained staff. It is the responsibility of customer's technical departments to evaluate the suitability of the product for the intended application and the completeness of the product information given in this document with respect to such application.

For further information on technology, delivery terms and conditions and prices, please contact the nearest Infineon Technologies Office (www.infineon.com).

#### WARNINGS

Due to technical requirements products may contain dangerous substances. For information on the types in question please contact your nearest Infineon Technologies office.

Except as otherwise explicitly approved by Infineon Technologies in a written document signed by authorized representatives of Infineon Technologies, Infineon Technologies' products may not be used in any applications where a failure of the product or any consequences of the use thereof can reasonably be expected to result in personal injury.