# Product Change Notification / SYST-22ANYO783

# Date:

23-Dec-2020

# **Product Category:**

Hybrid Controllers

# PCN Type:

**Document Change**

# **Notification Subject:**

Data Sheet - MCP19114/MCP19115 Data Sheet

# Affected CPNs:

SYST-22ANYO783\_Affected\_CPN\_12232020.pdf SYST-22ANYO783\_Affected\_CPN\_12232020.csv

# **Notification Text:**

SYST-22ANYO783

Microchip has released a new Product Documents for the MCP19114/MCP19115 Data Sheet of devices. If you are using one of these devices please read the document located at MCP19114/MCP19115 Data Sheet.

# Notification Status: Final

**Description of Change:** The following is the list of modifications:

- 1. Updated the Electrical Characteristics table.

- 2. Updated Table 5-3, Table 5-5 and Table 5-7.

- 3. Updated Register 6-9 and Register 6-13.

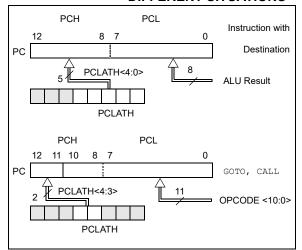

4. Updated Section 10.1.1.1 "RETLW Instruction" and Section 10.1.1.2 "Indirect Read with Files Select Register (FSR)".

5. Updated terminology throughout the document.

#### Impacts to Data Sheet: None

Reason for Change: To Improve Productivity

Change Implementation Status: Complete

Date Document Changes Effective: 23 Dec 2020

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

# **Attachments:**

MCP19114/ MCP19115 Data Sheet

Please contact your local Microchip sales office with questions or concerns regarding this notification.

# Terms and Conditions:

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our PCN home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the PCN FAQ section.

If you wish to <u>change your PCN profile, including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

Affected Catalog Part Numbers (CPN)

MCP19114-E/MJ MCP19114-E/MJV01 MCP19114-E/MJVAO MCP19114-E/MQ MCP19114-E/MQVAO MCP19114T-E/MJ MCP19114T-E/MJ253 MCP19114T-E/MJV01 MCP19114T-E/MJV02 MCP19114T-E/MJV03 MCP19114T-E/MJVAO MCP19114T-E/MQ MCP19114T-E/MQ001 MCP19114T-E/MQV01 MCP19114T-E/MQV04 MCP19114T-E/MQVAO MCP19115-E/MQ MCP19115T-E/MQ MCP19115T-E/MQV01 MCP19115T-E/MQV02 MCP19115T-E/MQV03 MCP19115T-E/MQVAO

# **Digitally Enhanced Power Analog Synchronous Low-Side PWM Controller**

#### Features

- Input Voltage: 4.5V to 42V

- Can be Configured with Multiple Topologies Including but not Limited to:

- Flyback

- Ćuk

- Boost

- SEPIC (Single-Ended Primary-Inductor Converter)

- Capable of Quasi-Resonant or Fixed-Frequency

Operation

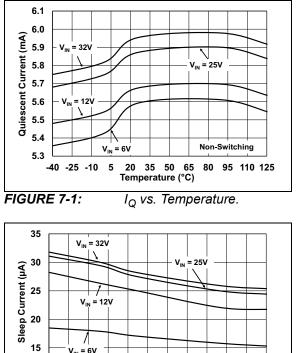

- · Low Quiescent Current: 5 mA Typical

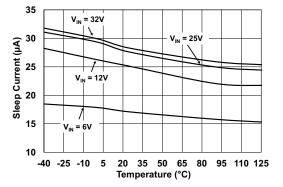

- Low Sleep Current: 30 µA Typical

- Low-Side Gate Drivers:

- +5V gate drive

- 0.5A sink/source current

- +10V gate drive

- 1A sink/source current

- Peak Current Mode Control

- Differential Remote Output Sense

- Multiple Output Systems:

- Main or Secondary

- AEC-Q100 Qualified

- Configurable Parameters:

- V<sub>REF</sub>, Precision I<sub>OUT</sub>/V<sub>OUT</sub> Set Point (DAC)

- Input Undervoltage Lockout (UVLO)

- Input Overvoltage Lockout (OVLO)

- Detection and protection

- Primary current leading edge blanking (0, 50 ns, 100 ns and 200 ns)

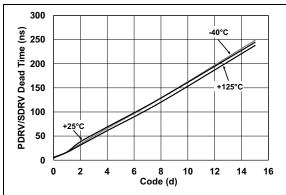

- Gate drive dead time (16 ns to 256 ns)

- Fixed switching frequency range: 31.25 kHz to 2.0 MHz

- Slope compensation

- Quasi-resonant configuration with built-in comparator and programmable offset voltage adjustment

- Primary current offset adjustment

- Configurable GPIO pin options

- Integrated Low-Side Differential Current Sense

Amplifier

- ±5% Current Regulation

- Thermal Shutdown

#### **Microcontroller Features**

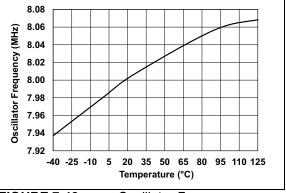

- Precision 8 MHz Internal Oscillator Block:

- Factory-calibrated to ±1%, typical

- Interrupt-Capable

- Firmware

- Interrupt-on-change pins

- Only 35 Instructions to Learn

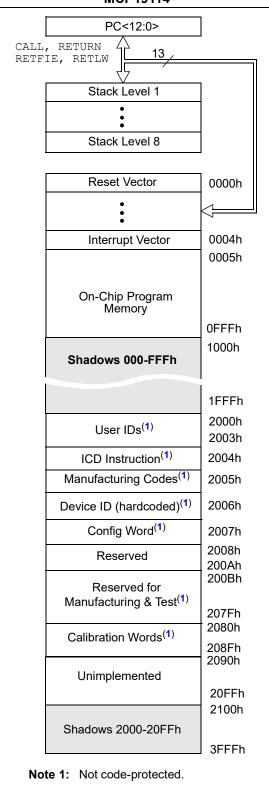

- 4096 Words On-Chip Program Memory

- High-Endurance Flash:

- 100,000 write Flash endurance

- Flash retention: >40 years

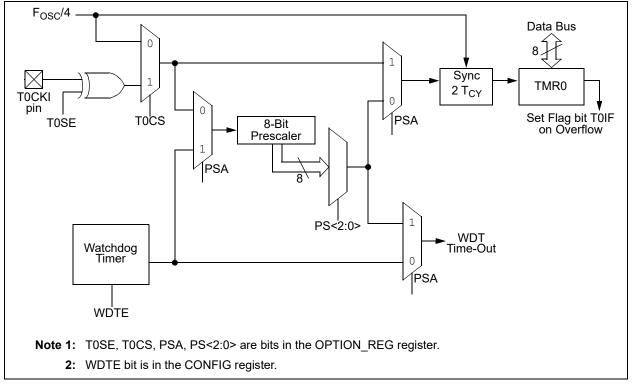

- Watchdog Timer (WDT) with Independent Oscillator for Reliable Operation

- Programmable Code Protection

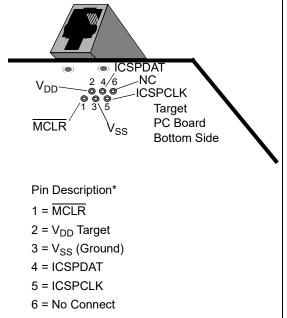

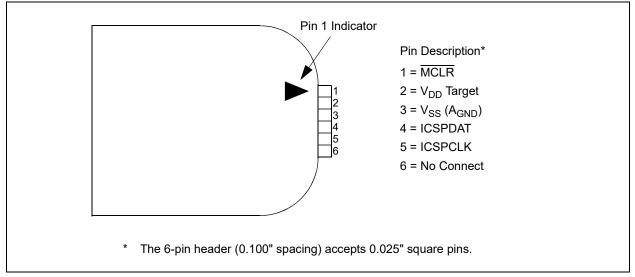

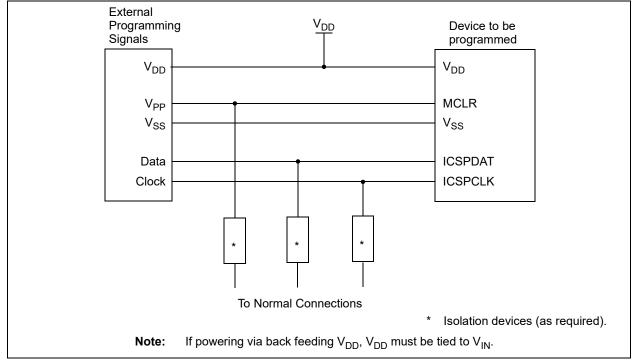

- In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>) via Two Pins

- · Eight I/O Pins and One Input-Only Pin

- Two open-drain pins

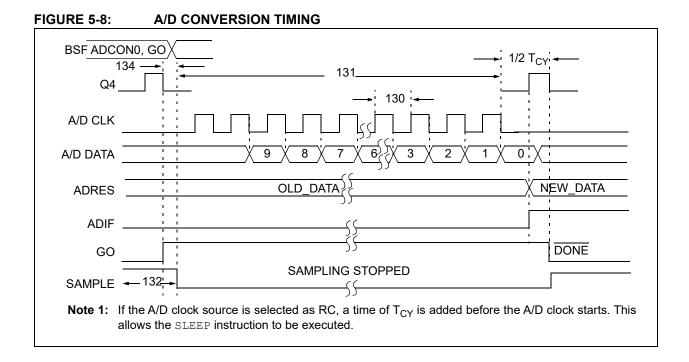

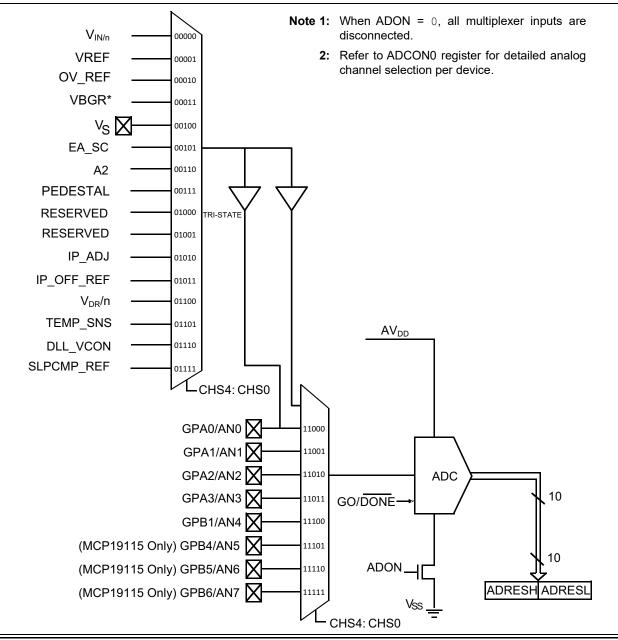

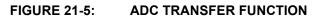

- Analog-to-Digital Converter (ADC):

- 10-bit resolution

- Five external channels

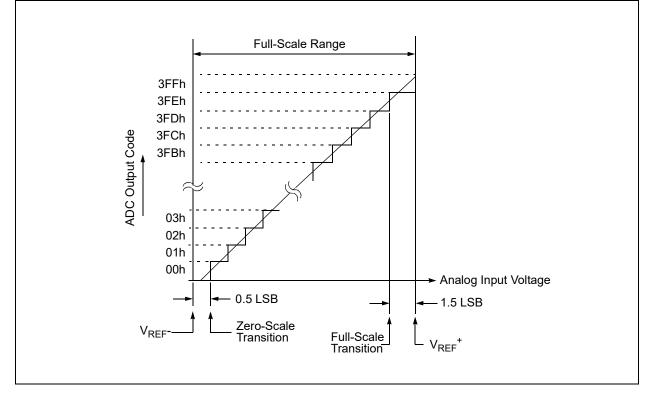

- Timer0: 8-bit Timer/Counter with 8-bit Prescaler

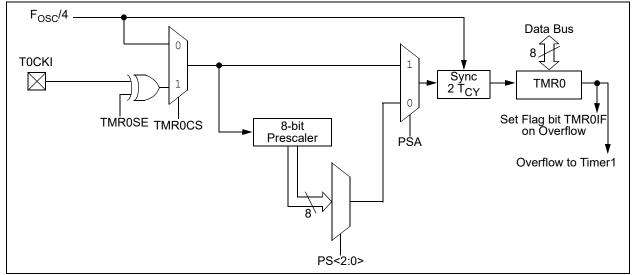

- Enhanced Timer1:

- 16-bit timer with prescaler

- Two selectable clock sources

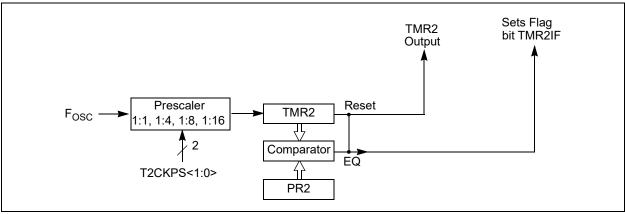

- Timer2: 8-Bit Timer with Prescaler

- 8-bit period register

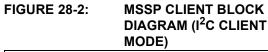

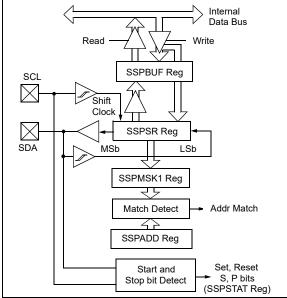

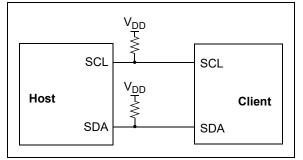

- I<sup>2</sup>C<sup>™</sup> Communication:

- 7-bit address masking

- Two dedicated address registers

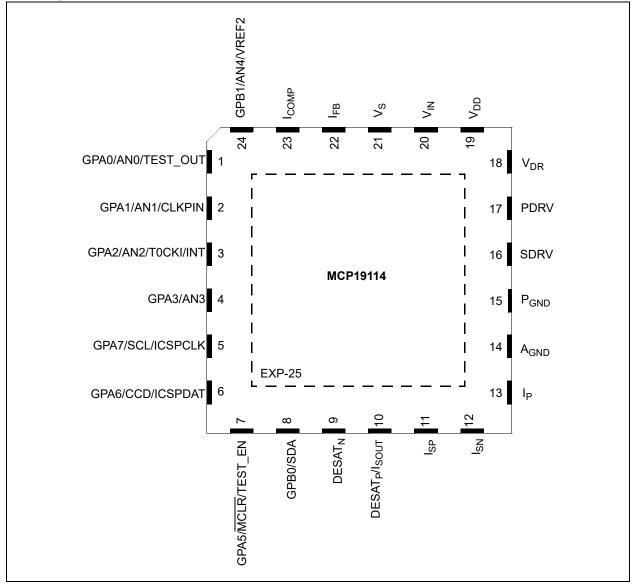

### Pin Diagram – 24-Pin QFN (MCP19114)

TABLE 1: 24-PIN SUMMARY

|                      | 24-FIN SUMMART |       |     |        |      |                    |                  |                  |                                                                        |

|----------------------|----------------|-------|-----|--------|------|--------------------|------------------|------------------|------------------------------------------------------------------------|

| 0/I                  | 24-Pin QFN     | ANSEL | A/D | Timers | MSSP | Interrupt          | Pull-Up          | Basic            | Additional                                                             |

| GPA0                 | 1              | Y     | AN0 | _      | _    | IOC                | Y                | —                | Analog/Digital Debug Output <sup>(1)</sup>                             |

| GPA1                 | 2              | Y     | AN1 | _      | _    | IOC                | Y                | _                | Sync Signal In/Out <sup>(2)</sup>                                      |

| GPA2                 | 3              | Y     | AN2 | TOCKI  | _    | IOC<br>INT         | Y                | —                | _                                                                      |

| GPA3                 | 4              | Y     | AN3 |        | —    | IOC                | Y                | —                | _                                                                      |

| GPA5                 | 7              | Ν     | —   |        | _    | IOC <sup>(4)</sup> | Y <sup>(5)</sup> | MCLR             | Test Enable Input                                                      |

| GPA6                 | 6              | Ν     | —   | —      | —    | IOC                | Y                | ICSPDAT          | Dual Capture Input/Single<br>Compare 1 Output                          |

| GPA7                 | 5              | Ν     | —   | _      | SCL  | IOC                | Ν                | ICSPCLK          | —                                                                      |

| GPB0                 | 8              | Ν     | _   |        | SDA  | IOC                | Ν                | _                |                                                                        |

| GPB1                 | 24             | Y     | AN4 | _      | _    | IOC                | Y                |                  | V <sub>REF2</sub> <sup>(3)</sup>                                       |

| DESAT <sub>N</sub>   | 9              | Ν     | —   |        | _    | —                  | —                | —                | DESAT Negative Input                                                   |

| DESAT <sub>P</sub> / | 10             | Ν     | —   | —      | _    | —                  | _                | —                | DESAT <sub>P</sub> Input or I <sub>SOUT</sub><br>Output <sup>(6)</sup> |

| I <sub>SP</sub>      | 11             | Ν     | —   | —      | _    | —                  | Y                | —                | Current Sense Amplifier Positive<br>Input                              |

| I <sub>SN</sub>      | 12             | Ν     | _   | _      | _    | —                  | _                | —                | Current Sense Amplifier<br>Negative Input                              |

| ۱ <sub>Р</sub>       | 13             | Ν     | —   | —      | —    | —                  | —                | —                | Primary Input Current Sense                                            |

| A <sub>GND</sub>     | 14             | Ν     | —   | —      | —    | —                  | —                | A <sub>GND</sub> | Small Signal Ground                                                    |

| P <sub>GND</sub>     | 15             | Ν     | —   | —      | _    | —                  | _                | P <sub>GND</sub> | Large Signal Ground                                                    |

| SDRV                 | 16             | Ν     | _   | —      | _    | —                  | —                | _                | Secondary LS Gate Drive<br>Output                                      |

| PDRV                 | 17             | Ν     | —   |        | —    | —                  | _                | —                | Primary LS Gate Drive<br>Output                                        |

| V <sub>DR</sub>      | 18             | Ν     | —   | _      | _    | —                  | _                | V <sub>DR</sub>  | Gate Drive Supply Voltage                                              |

| V <sub>DD</sub>      | 19             | Ν     | _   | _      | _    | —                  | _                | V <sub>DD</sub>  | V <sub>DD</sub> Output                                                 |

| V <sub>IN</sub>      | 20             | Ν     | —   |        |      | _                  | _                | V <sub>IN</sub>  | Input Supply Voltage                                                   |

| Vs                   | 21             | Ν     |     |        |      |                    | _                | _                | Output Voltage Sense                                                   |

| I <sub>FB</sub>      | 22             | Ν     | —   | —      | —    | —                  | _                | —                | Error Amplifier Feedback Input                                         |

| I <sub>COMP</sub>    | 23             | Ν     |     | _      | _    | —                  |                  | —                | Error Amplifier Output                                                 |

Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON register.

**2:** Selected when functioning as main or secondary by proper configuration of the MSC<1:0> bits in the MODECON register.

- **3:** V<sub>REF2</sub> output selected when configured as main by proper configuration of the MSC<1:0> bits in the MODECON register.

- 4: The IOC is disabled when MCLR is enabled.

- 5: Weak pull-up always enabled when MCLR is enabled, otherwise the pull-up is under user control.

- **6:** When RFB of MODECON<5> = 0, the internal feedback resistor and DESAT<sub>P</sub> input are enabled. When RFB = 1, I<sub>SOUT</sub> is enabled.

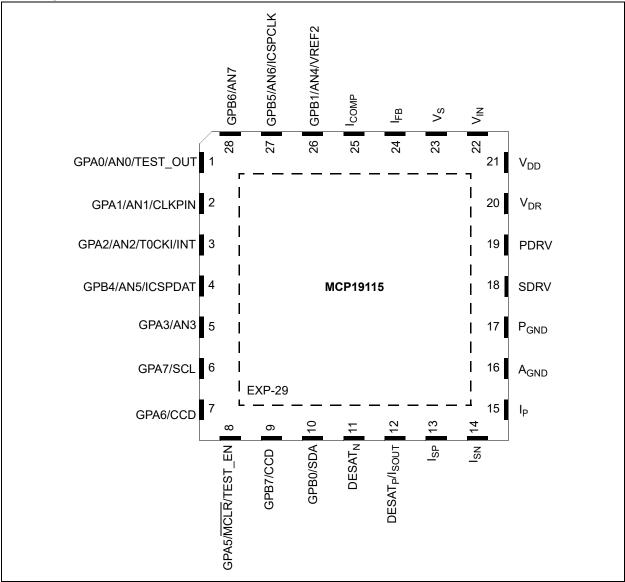

### Pin Diagram – 28-Pin QFN (MCP19115)

TABLE 2: 28-PIN SUMMARY

| TADLE Z.                                  | 2          |       | SUIVIIVIA |        |      |                    |                  |                  |                                                                        |

|-------------------------------------------|------------|-------|-----------|--------|------|--------------------|------------------|------------------|------------------------------------------------------------------------|

| 0/1                                       | 28-Pin QFN | ANSEL | A/D       | Timers | MSSP | Interrupt          | Pull-Up          | Basic            | Additional                                                             |

| GPA0                                      | 1          | Y     | AN0       | —      | _    | IOC                | Y                | _                | Analog/Digital Debug Output <sup>(1)</sup>                             |

| GPA1                                      | 2          | Y     | AN1       |        | _    | IOC                | Y                | _                | Sync Signal In/Out <sup>(2)</sup>                                      |

| GPA2                                      | 3          | Y     | AN2       | TOCKI  | _    | IOC<br>INT         | Y                | —                | —                                                                      |

| GPA3                                      | 5          | Y     | AN3       | _      | _    | IOC                | Y                | _                | —                                                                      |

| GPA5                                      | 8          | Ν     |           |        |      | IOC <sup>(4)</sup> | Y <sup>(5)</sup> | MCLR             | Test Enable Input                                                      |

| GPA6                                      | 7          | N     | _         | _      |      | IOC                | Y                | _                | Dual Capture Input/Single<br>Compare 1 Output                          |

| GPA7                                      | 6          | Ν     | —         | —      | SCL  | IOC                | Ν                | —                | —                                                                      |

| GPB0                                      | 10         | Ν     | —         | —      | SDA  | IOC                | Ν                | —                | —                                                                      |

| GPB1                                      | 26         | Y     | AN4       | —      | _    | IOC                | Y                | —                | V <sub>REF2</sub> <sup>(3)</sup>                                       |

| GPB4                                      | 4          | Y     | AN5       | —      | _    | IOC                | Y                | ICSPDAT          | —                                                                      |

| GPB5                                      | 27         | Y     | AN6       | —      | _    | IOC                | Y                | ICSPCLK          | —                                                                      |

| GPB6                                      | 28         | Y     | AN7       | _      |      | IOC                | Y                | _                | —                                                                      |

| GPB7                                      | 9          | Y     | _         | —      | _    | IOC                | Y                | —                | Single Compare2 Output                                                 |

| DESAT <sub>P</sub> /<br>I <sub>SOUT</sub> | 12         | N     | —         | —      | _    | —                  | _                | —                | DESAT <sub>P</sub> input or I <sub>SOUT</sub><br>Output <sup>(6)</sup> |

| DESAT <sub>N</sub>                        | 11         | Ν     |           | _      | _    |                    | _                |                  | DESAT Negative Input                                                   |

| I <sub>SP</sub>                           | 13         | N     | —         | —      | _    | —                  | Y                | —                | Current Sense Amplifier<br>Noninverting Input                          |

| I <sub>SN</sub>                           | 14         | N     | —         | —      | _    | —                  | _                | —                | Current Sense Amplifier<br>Inverting Input                             |

| l <sub>P</sub>                            | 15         | Ν     | _         | _      |      |                    |                  | _                | Primary Input Current Sense                                            |

| A <sub>GND</sub>                          | 16         | Ν     | _         | —      | _    |                    | _                | A <sub>GND</sub> | Small Signal Ground                                                    |

| P <sub>GND</sub>                          | 17         | Ν     | _         | —      | _    |                    | _                | P <sub>GND</sub> | Large Signal Ground                                                    |

| SDRV                                      | 18         | N     | —         | —      | _    | —                  | _                | —                | Secondary LS Gate Drive<br>Output                                      |

| PDRV                                      | 19         | Ν     | _         | —      | _    |                    | _                | —                | Primary LS Gate Drive Output                                           |

| V <sub>DR</sub>                           | 20         | Ν     |           | _      |      |                    |                  | V <sub>DR</sub>  | Gate Drive Supply Voltage                                              |

| V <sub>DD</sub>                           | 21         | Ν     |           | —      |      | _                  |                  | V <sub>DD</sub>  | V <sub>DD</sub> Output                                                 |

| V <sub>IN</sub>                           | 22         | Ν     | _         | _      | _    | _                  | _                | V <sub>IN</sub>  | Input Supply Voltage                                                   |

| V <sub>S</sub>                            | 23         | Ν     | _         |        | _    |                    |                  | _                | Output Voltage Sense                                                   |

| I <sub>FB</sub>                           | 24         | Ν     | _         | —      |      | _                  |                  | —                | Error Amplifier Feedback input                                         |

| I <sub>COMP</sub>                         | 25         | Ν     | —         | —      | _    | —                  | _                | —                | Error Amplifier Output                                                 |

|                                           |            |       |           |        |      |                    |                  |                  |                                                                        |

Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON register.

**2:** Selected when functioning as main or secondary by proper configuration of the MSC<1:0> bits in the MODECON register.

**3:** VREF2 output selected when configured as main by proper configuration of the MSC<1:0> bits in the MODECON register.

**4:** The IOC is disabled when  $\overline{\text{MCLR}}$  is enabled.

5: Weak pull-up always enabled when  $\overline{\text{MCLR}}$  is enabled, otherwise the pull-up is under user control.

6: When RFB of MODECON<6> = 0, the internal feedback resistor is enabled allow with DESAT<sub>P</sub> input. When RFB = 1,  $I_{SOUT}$  is enabled.

#### **Table of Contents**

| 1.0   | Device Overview                            | 9     |

|-------|--------------------------------------------|-------|

| 2.0   | Pin Description                            | 13    |

| 3.0   | Functional Description                     | 19    |

| 4.0   | Electrical Characteristics                 | 22    |

| 5.0   | Digital Electrical Characteristics         | 29    |

| 6.0   | Configuring the MCP19114/5                 | 37    |

| 7.0   | Typical Performance Curves                 |       |

| 8.0   | System Bench Testing                       | 57    |

| 9.0   | Device Calibration                         | 59    |

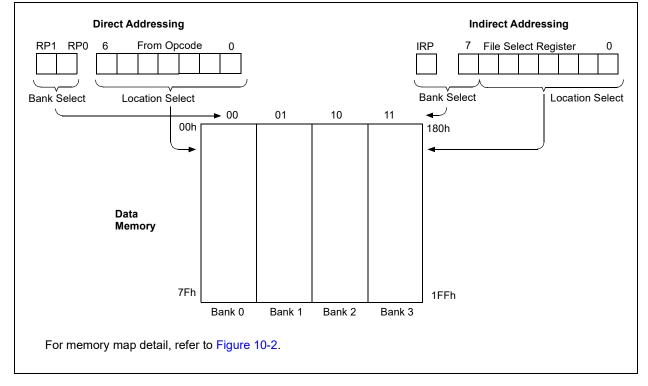

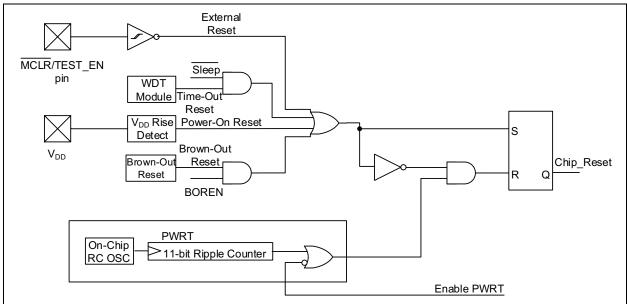

| 10.0  | Memory Organization                        | 69    |

| 11.0  | Device Configuration                       | 81    |

| 12.0  | Oscillator Modes                           | 83    |

| 13.0  | Resets                                     | 85    |

| 14.0  | Interrupts                                 |       |

| 15.0  | Power-Down Mode (Sleep)                    | . 101 |

| 16.0  | Watchdog Timer (WDT)                       | . 103 |

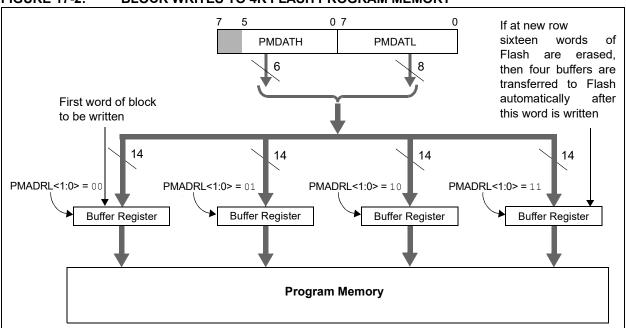

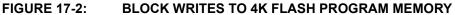

| 17.0  | Flash Program Memory Control               | . 105 |

| 18.0  | I/O Ports                                  | 111   |

| 19.0  | Interrupt-On-Change                        | . 121 |

| 20.0  | Internal Temperature Indicator Module      | . 125 |

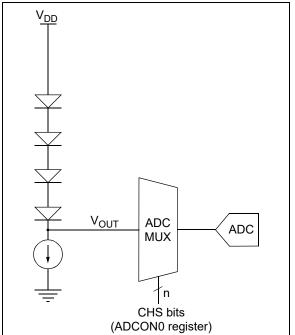

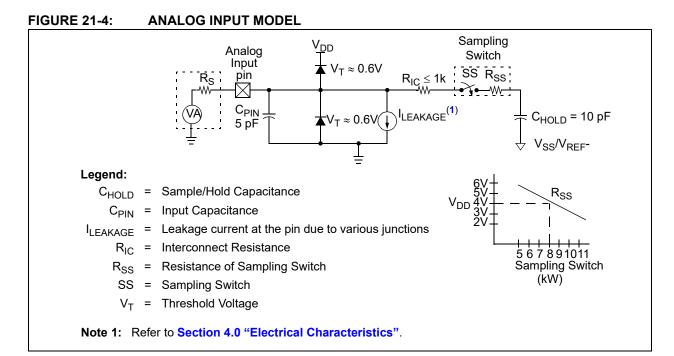

| 21.0  | Analog-to-Digital Converter (ADC) Module   | . 127 |

|       | Timer0 Module                              |       |

| 23.0  | Timer1 Module with Gate Control            | . 139 |

| 24.0  | Timer2 Module                              | . 143 |

| 25.0  | Enhanced PWM Module                        |       |

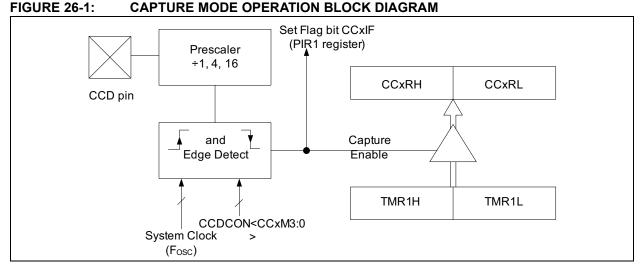

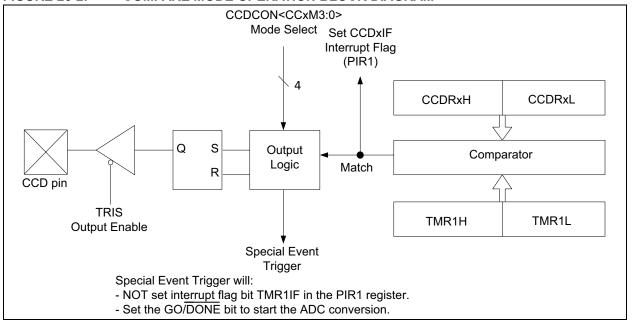

| 26.0  | Dual Capture/Compare (CCD) Module          | . 149 |

|       | PWM Control Logic                          |       |

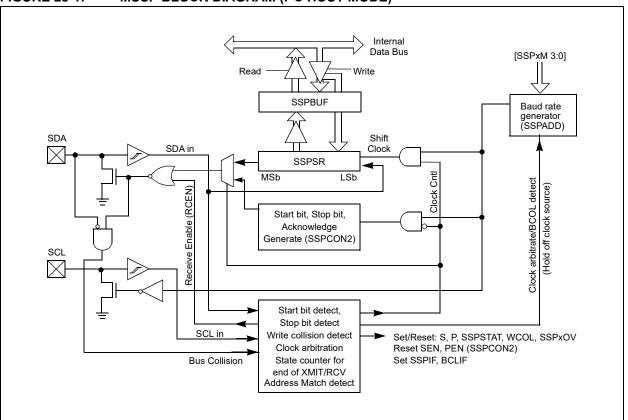

| 28.0  | HOST Synchronous Serial Port (MSSP) Module | . 155 |

| 29.0  | Instruction Set Summary                    | . 199 |

| 30.0  | In-Circuit Serial Programming™ (ICSP™)     | . 209 |

| 31.0  | Development Support                        | 211   |

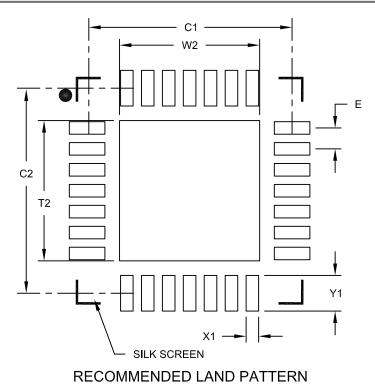

| 32.0  | Packaging Information                      | . 215 |

| Appe  | ndix A: Revision History                   | . 221 |

| Index |                                            | . 223 |

| The N | Aicrochip Web Site                         | . 229 |

| Custo | omer Change Notification Service           | . 229 |

| Custo | omer Support                               | . 229 |

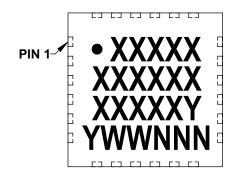

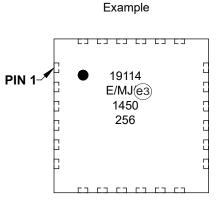

| Produ | uct Identification System                  | . 231 |

# TO OUR VALUED CUSTOMERS

It is our intention to provide our valued customers with the best documentation possible to ensure successful use of your Microchip products. To this end, we will continue to improve our publications to better suit your needs. Our publications will be refined and enhanced as new volumes and updates are introduced.

If you have any questions or comments regarding this publication, please contact the Marketing Communications Department via E-mail at docerrors@microchip.com. We welcome your feedback.

#### Most Current Data Sheet

To obtain the most up-to-date version of this data sheet, please register at our Worldwide Web site at:

#### http://www.microchip.com

You can determine the version of a data sheet by examining its literature number found on the bottom outside corner of any page. The last character of the literature number is the version number, (e.g., DS30000000A is version A of document DS30000000).

#### Errata

An errata sheet, describing minor operational differences from the data sheet and recommended workarounds, may exist for current devices. As device/documentation issues become known to us, we will publish an errata sheet. The errata will specify the revision of silicon and revision of document to which it applies.

To determine if an errata sheet exists for a particular device, please check with one of the following:

- Microchip's Worldwide Web site; http://www.microchip.com

- Your local Microchip sales office (see last page)

When contacting a sales office, please specify which device, revision of silicon and data sheet (include literature number) you are using.

#### **Customer Notification System**

Register on our web site at www.microchip.com to receive the most current information on all of our products.

NOTES:

# 1.0 DEVICE OVERVIEW

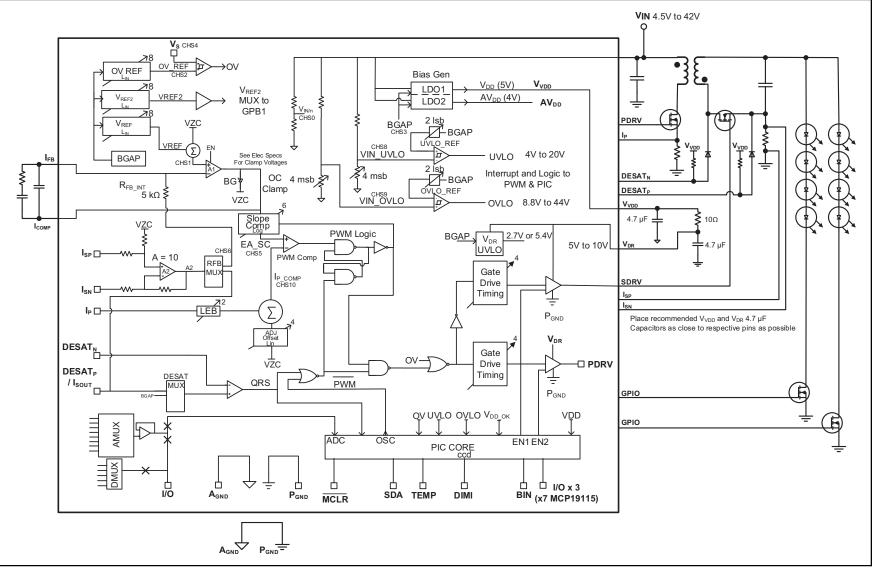

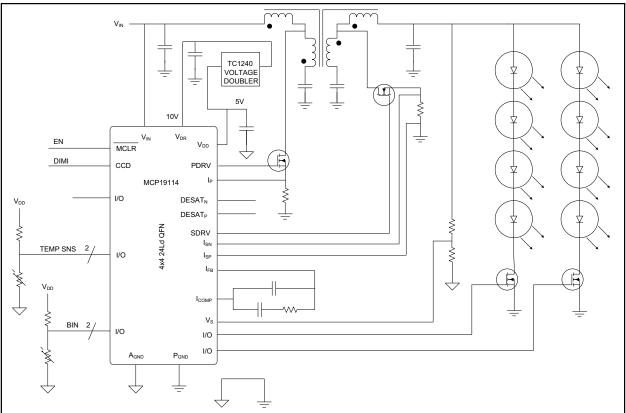

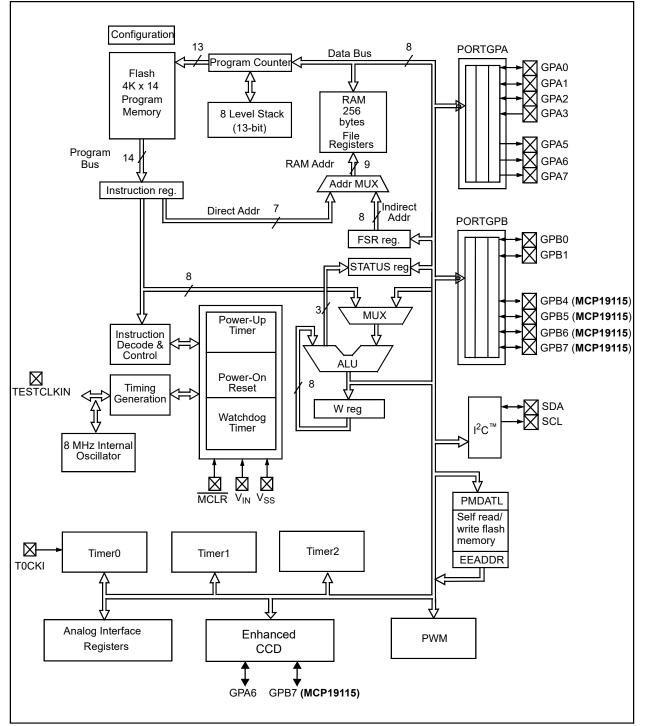

The MCP19114/5 are highly integrated, mixed-signal low-side synchronous controllers that operate from 4.5V to 42V. The family features an analog PWM controller with an integrated microcontroller core used for LED lighting systems, battery chargers and other low-side switch PWM applications. The devices feature an analog internal PWM controller similar to the MCP1631, and a standard PIC<sup>®</sup> microcontroller similar to the PIC12F617.

Complete customization of device operating parameters, start-up or shutdown profiles, protection levels and fault handling procedures are accomplished by setting digital registers using Microchip's MPLAB<sup>®</sup> X Integrated Development Environment software and one of Microchip's many in-circuit debugger and device programmers.

The MCP19114/5 mixed-signal low-side synchronous controllers feature integrated programmable input UVLO/OVLO, programmable output overvoltage (OV), two low-side gate drive outputs with independent programmable dead time, programmable leading edge blanking (four steps), programmable 6-bit slope compensation and an integrated internal programmable for fixed-frequency oscillator applications. An integrated 8-bit reference voltage (V<sub>REF</sub>) is used for setting output voltage or current. An internal comparator supports quasi-resonant applications. Additional Capture and Compare modules are integrated for additional control, including enhanced dimming capability. The MCP19114/5 devices contain two internal LDOs. A 5V LDO is used to power the internal processor and provide 5V externally. This 5V external output can be used to supply the gate drive. An analog filter between the V<sub>DD</sub> output and the V<sub>DR</sub> input is recommended when implementing a 5V gate drive supplied from V<sub>DD</sub>. Two 4.7 µF capacitors are recommended with one placed as close as possible to  $V_{\mbox{\scriptsize DD}}$  and one as close as possible to  $V_{DR}$ , separated by a 10 $\Omega$  isolation resistor. DO NOT exceed 10 µF on the V<sub>DD</sub>. An external supply is required to implement higher gate drive voltages. By utilizing Microchip's TC1240A voltage doubler supplied from  $V_{DD}$  to provide  $V_{DR}$ , a 10V gate drive can be achieved. A 4V LDO is used to power the internal analog circuitry. The two low-side drivers can be used to operate the power converter in bidirectional mode, enabling the "shaping" of LED dimming current in LED applications or developing bidirectional power converters for battery-powered applications.

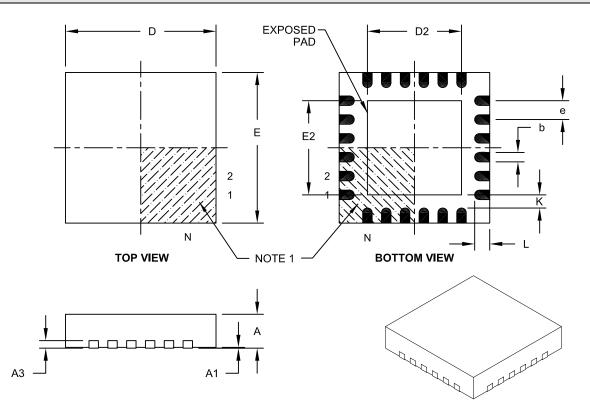

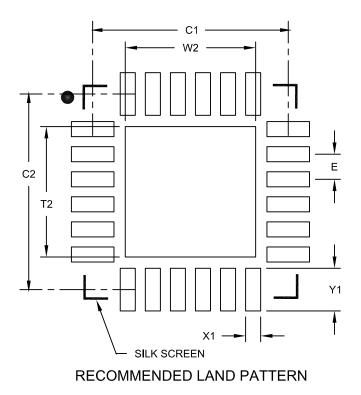

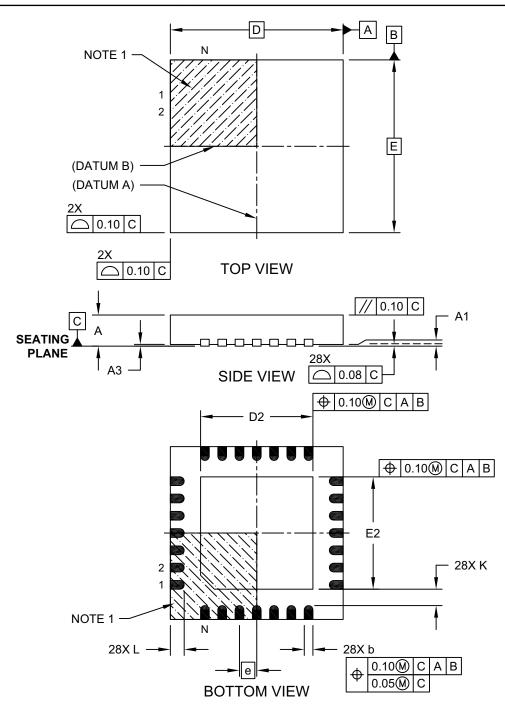

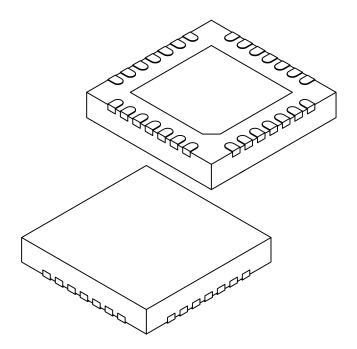

The MCP19114 is packaged in a 24-lead 4 mm x 4 mm QFN and offers an alternate-bonded 28-lead 5 mm x 5 mm QFN. The MCP19115 is packaged in a 28-lead 5 mm x 5 mm QFN.

The ability for system designers to configure application-specific features allows the MCP19114/5 to be offered in smaller packages than currently available in integrated devices today. The General Purpose Input/Output (GPIO) of the MCP19114/5 can be configured to offer a status output; a device enable, to control an external switch; a switching frequency synchronization output or input or even a device status or "heartbeat" indicator. This flexibility allows the MCP19114/5 packages and complete solutions to be smaller, thereby saving size and cost of the system printed circuit boards.

With integrated features like output current adjustment and dynamic output voltage positioning, the MCP19114/5 family has the best in-class performance and highest integration level currently available.

Power trains supported by this architecture include but are not limited to boost, flyback, quasi-resonant flyback, SEPIC, Ćuk, etc. Two low-side gate drivers are capable of sinking and sourcing 1A at 10V  $V_{DR}$ . With a 5V gate drive, the driver is capable of 0.5A sink and source. The user has the option to allow the VIN UVLO to shut down the drivers by setting the UVLOEN bit. When this bit is not set, the device drivers will ride through the UVLO condition and continue to operate until V<sub>DR</sub> reaches the gate drive UVLO value. This value is selectable at 2.7V or 5.4V and is always enabled. An internal reset for the microcontroller core is set to 2.0V. An internal comparator module is used to sense the desaturation of the flyback transformer to synchronize switching for quasi-resonant applications. The operating input voltage for normal device operation ranges from 4.5V to 42V with an absolute maximum of 44V. The maximum transient voltage is 48V for 500 ms. An I<sup>2</sup>C serial bus is used for device communications from the PWM controller to the system.

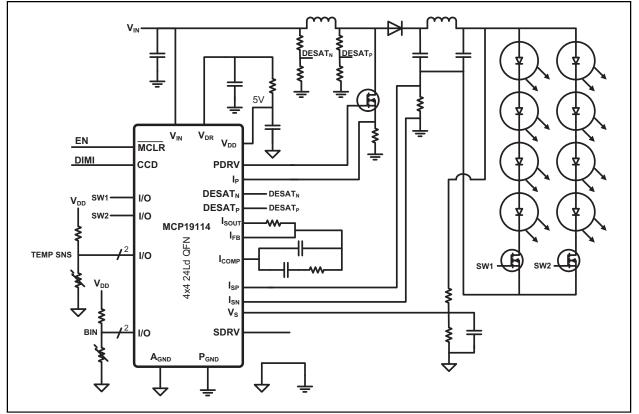

#### FIGURE 1-1:

#### MCP19114/5 FLYBACK SYNCHRONOUS QUASI-RESONANT BLOCK DIAGRAM

DS20005281C-page 10

**MCP19114/5**

FIGURE 1-3:

MCP19114 BOOST QUASI-RESONANT APPLICATION DIAGRAM

© 2014-2020 Microchip Technology Inc.

# 2.0 PIN DESCRIPTION

The 24-lead MCP19114 and 28-lead MCP19115 devices feature pins that have multiple functions associated with each pin. Table 2-1 provides a description of the different functions. Refer to **Section 2.1 "Detailed Pin Functional Description"** for more detailed information.

| Name               | Function | Input<br>Type     | Output<br>Type | Description                                                      |

|--------------------|----------|-------------------|----------------|------------------------------------------------------------------|

| GPA0/AN0/TEST_OUT  | GPA0     | TTL               | CMOS           | General-purpose I/O                                              |

|                    | AN0      | AN                | _              | A/D Channel 0 input                                              |

|                    | TEST_OUT | _                 | _              | Internal analog/digital signal multiplexer output <sup>(1)</sup> |

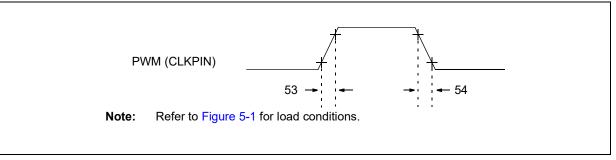

| GPA1/AN1/CLKPIN    | GPA1     | TTL               | CMOS           | General-purpose I/O                                              |

|                    | AN1      | AN                | _              | A/D Channel 1 input                                              |

|                    | CLKPIN   | ST                | CMOS           | Switching frequency clock input or output <sup>(2)</sup>         |

| GPA2/AN2/T0CKI/INT | GPA2     | ST                | CMOS           | General-purpose I/O                                              |

|                    | AN2      | AN                | —              | A/D Channel 2 input                                              |

|                    | T0CKI    | ST                | —              | Timer0 clock input                                               |

|                    | INT      | ST                | —              | External interrupt                                               |

| GPA3/AN3           | GPA3     | TTL               | CMOS           | General-purpose I/O                                              |

|                    | AN3      | AN                | —              | A/D Channel 3 input                                              |

| GPA5/MCLR          | GPA5     | TTL               | —              | General-purpose input only                                       |

|                    | MCLR     | ST                | _              | Main Clear with internal pull-up                                 |

| GPA6/CCD/ICSPDAT   | GPA6     | ST                | CMOS           | General-purpose I/O                                              |

|                    | ICSPDAT  | ST                | CMOS           | Serial Programming Data I/O                                      |

|                    | CCD      | ST                | CMOS           | Single Compare output. Dual Capture input                        |

| GPA7/SCL/ICSPCLK   | GPA7     | ST                | OD             | General-purpose open drain I/O                                   |

|                    | SCL      | I <sup>2</sup> C™ | OD             | l <sup>2</sup> C clock                                           |

|                    | ICSPCLK  | ST                | —              | Serial Programming Clock                                         |

| GPB0/SDA           | GPB0     | TTL               | OD             | General-purpose I/O                                              |

|                    | SDA      | I <sup>2</sup> C™ | OD             | I <sup>2</sup> C data input/output                               |

| GPB1/AN4/VREF2     | GPB1     | TTL               | CMOS           | General-purpose I/O                                              |

|                    | AN4      | AN                | —              | A/D Channel 4 input                                              |

|                    | VREF2    | —                 | AN             | VREF2 DAC Output <sup>(3)</sup>                                  |

| GPB4/AN5/ICSPDAT   | GPB4     | TTL               | CMOS           | General-purpose I/O                                              |

| (MCP19115 Only)    | AN5      | AN                |                | A/D Channel 5 input                                              |

|                    | ICSPDAT  | ST                | CMOS           | Primary Serial Programming Data I/O                              |

| GPB5/AN6/ICSPCLK   | GPB5     | TTL               | CMOS           | General-purpose I/O                                              |

| (MCP19115 Only)    | AN6      | AN                |                | A/D Channel 6 input                                              |

|                    | ISCPCLK  | ST                | _              | Primary Serial Programming Clock                                 |

TABLE 2-1: MCP19114/5 PINOUT DESCRIPTION

Legend:AN= Analog input or output CMOS= CMOS compatible input or outputOD = Open-DrainTTL= TTL compatible inputST= Schmitt Trigger input with CMOS levels $l^2C$ = Schmitt Trigger input with  $l^2C$

Note 1: The Analog/Digital Debug Output is selected through the control of the ABECON register.

2: Selected when functioning as main or secondary by proper configuration of the MSC<1:0> bits in the MODECON register.

3: VREF2 output selected when configured as main by proper configuration of the MSC<1:0> bits in the MODECON register.

| Name                                  | Function                              | Input<br>Type | Output<br>Type | Description                                                                                                                 |  |  |  |

|---------------------------------------|---------------------------------------|---------------|----------------|-----------------------------------------------------------------------------------------------------------------------------|--|--|--|

| GPB6/AN7                              | GPB6                                  | TTL           | CMOS           | General-purpose I/O                                                                                                         |  |  |  |

| ( <b>MCP19115</b> Only)               | AN7                                   | AN            | _              | A/D Channel 7 input                                                                                                         |  |  |  |

| GPB7/CCD                              | GPB7                                  | TTL           | CMOS           | General-purpose I/O                                                                                                         |  |  |  |

| ( <b>MCP19115</b> Only)               | CCD                                   | ST            | CMOS           | Single Compare output. Dual Capture input.                                                                                  |  |  |  |

| V <sub>IN</sub>                       | V <sub>IN</sub>                       |               | _              | Device input supply voltage                                                                                                 |  |  |  |

| V <sub>DD</sub>                       | V <sub>DD</sub>                       | —             | —              | Internal +5V LDO output pin                                                                                                 |  |  |  |

| V <sub>DR</sub>                       | V <sub>DR</sub>                       |               | _              | Gate drive supply voltage                                                                                                   |  |  |  |

| A <sub>GND</sub>                      | A <sub>GND</sub>                      |               | _              | Small signal quiet ground                                                                                                   |  |  |  |

| P <sub>GND</sub>                      | P <sub>GND</sub>                      |               |                | Large signal power ground                                                                                                   |  |  |  |

| PDRV                                  | PDRV                                  |               |                | Primary Low-Side MOSFET gate drive                                                                                          |  |  |  |

| SDRV                                  | SDRV                                  |               | _              | Secondary Low-Side MOSFET gate drive                                                                                        |  |  |  |

| I <sub>P</sub>                        | l <sub>P</sub>                        |               |                | Primary input current sense                                                                                                 |  |  |  |

| I <sub>SN</sub>                       | I <sub>SN</sub>                       | —             |                | Secondary current sense amplifier negative input                                                                            |  |  |  |

| I <sub>SP</sub>                       | I <sub>SP</sub>                       |               | _              | Secondary current sense amplifier positive input                                                                            |  |  |  |

| V <sub>S</sub>                        | Vs                                    |               |                | Sense voltage compared to overvoltage DAC                                                                                   |  |  |  |

| I <sub>FB</sub>                       | I <sub>FB</sub>                       | —             |                | Error amplifier feedback input                                                                                              |  |  |  |

| ICOMP                                 | I <sub>COMP</sub>                     | _             |                | Error amplifier output                                                                                                      |  |  |  |

| DESAT <sub>P</sub> /I <sub>SOUT</sub> | DESAT <sub>P</sub> /I <sub>SOUT</sub> | —             | —              | DESAT <sub>P</sub> : DESAT detect comparator positive input<br>I <sub>SOUT</sub> : Secondary current sense amplifier output |  |  |  |

| DESAT <sub>N</sub>                    | DESAT <sub>N</sub>                    | —             | —              | DESAT <sub>N</sub> : DESAT detect comparator negative input                                                                 |  |  |  |

Legend:AN= Analog input or output CMOS= CMOS compatible input or outputOD = Open-DrainTTL= TTL compatible inputST= Schmitt Trigger input with CMOS levels $I^2C$ = Schmitt Trigger input with I<sup>2</sup>C

**Note 1:** The Analog/Digital Debug Output is selected through the control of the ABECON register.

2: Selected when functioning as main or secondary by proper configuration of the MSC<1:0> bits in the MODECON register.

3: VREF2 output selected when configured as main by proper configuration of the MSC<1:0> bits in the MODECON register.

#### 2.1 Detailed Pin Functional Description

#### 2.1.1 GPA0 PIN

GPA0 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN0 is an input to the A/D. To configure this pin to be read by the A/D on channel 0, bits TRISA0 and ANSA0 must be set.

The ABECON register can be configured to set this pin to the TEST\_OUT function. It is a buffered output of the internal analog or digital signal multiplexers. Analog signals present on this pin are controlled by the ADCON0 register. Digital signals present on this pin are controlled by the ABECON register.

#### 2.1.2 GPA1 PIN

GPA1 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN1 is an input to the A/D. To configure this pin to be read by the A/D on channel 1, bits TRISA1 and ANSA1 must be set.

When the MCP19114/5 are configured as a main or secondary, this pin is configured to be the switching frequency synchronization input or output (CLKPIN).

#### 2.1.3 GPA2 PIN

GPA2 is a general-purpose ST input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN2 is an input to the A/D. To configure this pin to be read by the A/D on channel 2, bits TRISA2 and ANSA2 must be set.

When bit TOCS is set in the OPTION\_REG register, the TOCKI function is enabled. Refer to **Section 22.0 "Timer0 Module"** for more information.

GPA2 can also be configured as an external interrupt by setting the INTE bit. Refer to **Section 14.2** "GPA2/INT Interrupt" for more information.

#### 2.1.4 GPA3 PIN

GPA3 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPA. An internal weak pull-up and interrupt-on-change are also available.

AN3 is an input to the A/D. To configure this pin to be read by the A/D on channel 3, bits TRISA3 and ANSA3 must be set.

#### 2.1.5 GPA5 PIN

GPA5 is a general-purpose TTL input only pin. An internal weak pull-up and interrupt-on-change are also available.

For programming purposes, this pin is to be connected to the MCLR pin of the serial programmer. Refer to Section 30.0 "In-Circuit Serial Programming<sup>™</sup> (ICSP<sup>™</sup>)" for more information.

This pin is MCLR when the MCLRE bit is set in the CONFIG register.

#### 2.1.6 GPA6 PIN

GPA6 is a general-purpose CMOS output ST input pin whose data direction is controlled in TRISGPA.

ICSPDAT is a serial programming data I/O function. This can be used in conjunction with ICSPCLK to serial program the device.

GPA6 is part of the CCD Module. For more information, refer to Section 26.0 "Dual Capture/Compare (CCD) Module".

#### 2.1.7 GPA7 PIN

GPA7 is a true open drain general-purpose pin whose data direction is controlled in TRISGPA. There is no internal connection between this pin and device  $V_{DD}$ . This pin does not have a weak pull-up, but interrupt-on-change is available.

This pin is the primary ICSPCLK input. This can be used in conjunction with ICSPDAT to serial program the device.

When the MCP19114/5 is configured for  $I^2C$  communication, **Section 28.2** " $I^2C$  **Mode Overview**", GPA7 functions as the  $I^2C$  clock (SCL). This pin must be configured as an input to allow proper operation.

#### 2.1.8 GPB0 PIN

GPB0 is a true open-drain general-purpose pin whose data direction is controlled in TRISGPB. There is no internal connection between this pin and device  $V_{DD}$ . This pin does not have a weak pull-up, but interrupt-on-change is available. When the MCP19114/5 are configured for I<sup>2</sup>C communication, **Section 28.2** "I<sup>2</sup>C Mode Overview", GPB0 functions as the I<sup>2</sup>C data (SDA). This pin must be configured as an input to allow proper operation.

#### 2.1.9 GPB1 PIN

GPB1 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN4 is an input to the A/D. To configure this pin to be read by the A/D on channel 4, bits TRISB1 and ANSB1 must be set.

When the MCP19114/5 are configured as a main, this pin is configured to be the  $V_{REF2}$  DAC output.

#### 2.1.10 GPB4 PIN (MCP19115 ONLY)

GPB4 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN5 is an input to the A/D. To configure this pin to be read by the A/D on channel 5, bits TRISB4 and ANSB4 must be set.

ICSPDAT is the primary serial programming data I/O function. This is used in conjunction with ICSPCLK to serial program the device.

#### 2.1.11 GPB5 PIN (MCP19115 ONLY)

GPB5 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN6 is an input to the A/D. To configure this pin to be read by the A/D on channel 6, bits TRISB5 and ANSB5 must be set.

ICSPCLK is the primary serial programming clock function. This is used in conjunction with ICSPDAT to serial program the device.

#### 2.1.12 GPB6 PIN (MCP19115 ONLY)

GPB6 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

AN7 is an input to the A/D. To configure this pin to be read by the A/D on channel 7, bits TRISB6 and ANSB6 must be set.

#### 2.1.13 GPB7 PIN (MCP19115 ONLY)

GPB7 is a general-purpose TTL input or CMOS output pin whose data direction is controlled in TRISGPB. An internal weak pull-up and interrupt-on-change are also available.

GPB7 is part of the CCD Module. For more information, refer to Section 26.0 "Dual Capture/Compare (CCD) Module".

#### 2.1.14 DESAT<sub>N</sub> PIN

Internal comparator inverting input. Used during quasi-resonant operation for desaturation detection.

#### 2.1.15 DESAT<sub>P</sub>/I<sub>SOUT</sub> PIN

When using the internal comparator for desaturation detection during quasi-resonant operation, this pin connects to the comparator's noninverting input. The output of the remote sense current sense amplifier gets configured to utilize the 5 k $\Omega$  internal feedback resistor. When not utilizing the internal comparator and not configured to use the 5 k $\Omega$  internal feedback resistor, the current sense amplifier gets connected to this pin and is I<sub>SOUT</sub>.

#### 2.1.16 I<sub>SP</sub> PIN

The noninverting input to internal current sense amplifier, typically used to differentially remote sense secondary current. This pin can be internally pulled-up to  $V_{DD}$  by setting the <ISPUEN> bit in the PE1 register.

#### 2.1.17 I<sub>SN</sub> PIN

The inverting input to internal current sense amplifier, typically used to differentially remote sense secondary current.

#### 2.1.18 I<sub>P</sub> PIN

Primary input current sense for current mode control and peak current limit. For voltage mode control, this pin can be connected to an artificial ramp.

#### 2.1.19 A<sub>GND</sub> PIN

$A_{GND}$  is the small signal ground connection pin. This pin should be connected to the exposed pad on the bottom of the package.

#### 2.1.20 P<sub>GND</sub> PIN

Connect all large signal level ground returns to  $P_{GND}$ . These large-signal level ground traces should have a small loop area and minimal length to prevent coupling of switching noise to sensitive traces.

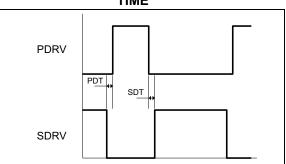

#### 2.1.21 SDRV PIN

The gate of the low-side secondary MOSFET is connected to SDRV. The PCB trace connecting SDRV to the gate must be of minimal length and appropriate width to handle the high-peak drive current and fast voltage transitions.

#### 2.1.22 PDRV PIN

The gate of the low-side primary MOSFET is connected to PDRV. The PCB tracing connecting PDRV to the gate must be of minimal length and appropriate width to handle the high-peak drive currents and fast voltage transitions.

#### 2.1.23 V<sub>DR</sub> PIN

The supply for the low-side drivers is connected to this pin and has an absolute maximum rating of +13.5V. This pin can be connected by an RC filter to the  $V_{DD}$  pin.

#### 2.1.24 V<sub>DD</sub> PIN

The output of the internal +5.0V regulator is connected to this pin. It is recommended that a 1.0  $\mu F$  minimum/ 10  $\mu F$  maximum bypass capacitor be connected between this pin and the GND pin of the device. The bypass capacitor should be physically placed close to the device.

#### 2.1.25 V<sub>IN</sub> PIN

Input power connection pin of the device. It is recommended that capacitance be placed between this pin and the GND pin of the device.

#### 2.1.26 V<sub>S</sub> PIN

Analog input connected to the noninverting input of the overvoltage comparator. Typically used as output voltage overvoltage protection. The inverting input of the overvoltage comparator is controlled by the OV REF DAC.

#### 2.1.27 I<sub>FB</sub> PIN

Error amplifier inverting feedback connection.

#### 2.1.28 I<sub>COMP</sub> PIN

Error amplifier output signal.

#### 2.1.29 EXPOSED PAD (EP)

It is recommended to connect the exposed pad to  $\mathsf{A}_{\text{GND}}.$

Note:Upon initial power-up, the device may apply<br/>a weak pull-up effect on GPIO pads that<br/>can be configured as analog inputs. Once<br/>the external capacitance on the 5V (V<sub>DD</sub>) is<br/>charged and the external 5V regulator<br/>exceeds the internal 4V regulator (AV<sub>DD</sub>)<br/>the pull-up effect is shut off. To prevent this<br/>parasitic power-up effect, a pull-down resis-<br/>tor of 10 kΩ maximum is recommended for<br/>GPIO with analog input capability. This<br/>applies to GPA0, GPA1, GPA2, GPA3,<br/>GPB1, GPB4 (MCP19115 only), GPBD<br/>(MCP19115 only), GPB6 (MCP19115 only).

NOTES:

# 3.0 FUNCTIONAL DESCRIPTION

#### 3.1 Linear Regulators

The operating input voltage for the MCP19114/5 ranges from 4.5V to 42V. There are two internal Low Dropout (LDO) voltage regulators. A 5V LDO is used to power the internal processor and provide a 5V output for external usage. A second LDO ( $AV_{DD}$ ) is a 4V regulator and is used to power the remaining analog internal circuitry. Using an LDO to power the MCP19114/5, the input voltage is monitored using a resistor divider. The MCP19114/5 also incorporate brown-out protection. Refer to Section 13.3 "Brown-Out Reset (BOR)" for details. The PIC core will reset at 2.0V V<sub>DD</sub>.

#### 3.2 Output Drive Circuitry

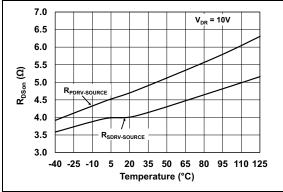

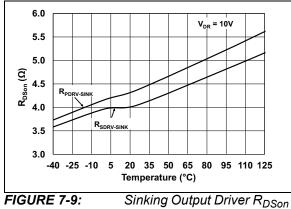

The MCP19114/5 integrate two low-side drivers used to drive the external low-side N-Channel power MOSFETs for synchronous applications, such as synchronous flyback and synchronous Ćuk converters. Both converter types can be configured for nonsynchronous control by replacing the synchronous FET with a diode. The flyback is also capable of quasi-resonant operation. The MCP19114/5 can also be configured as a Boost or SEPIC switch-mode power supply (SMPS). In Boost mode, nonsynchronous fixed-frequency or nonsynchronous quasi-resonant control can be utilized. This device can also be used as a SEPIC SMPS in fixed-frequency nonsynchronous mode. The low-side drive is capable of switching the MOSFET at high frequency in typical SMPS applications. The gate drive  $(V_{DR})$  can be supplied from 5V to 10V. The drive strength is capable of up to 1A sink/source with 10V gate drive and down to 0.5A sink/source with 5V gate drive. A programmable delay is used to set the gate turn-on dead time. This prevents overlap and shoot-through currents that can decrease the converter efficiency. Each driver shall have its own EN input controlled by the microcontroller core.

#### 3.3 Current Sense

The output current is differentially sensed by the MCP19114/5. In low-current applications, this helps maintain high system efficiency by minimizing power dissipation in current sense resistors. Differential current sensing also minimizes external ground shift errors. The internal differential amplifier has a typical gain of 10 V/V.

#### 3.4 Peak Current Mode

The MCP19114/5 is a peak current mode controlled device with the current sensing element in series with the primary side MOSFET. Programmable leading edge blanking can be implemented to blank current spikes resulting from turn on. The blank time is controlled from the ICLEBCON register.

Primary input current offset adjust is also available via user programmability, thus limiting peak primary input current. This offset adjustment is controlled by the ICOACON register.

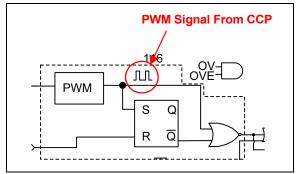

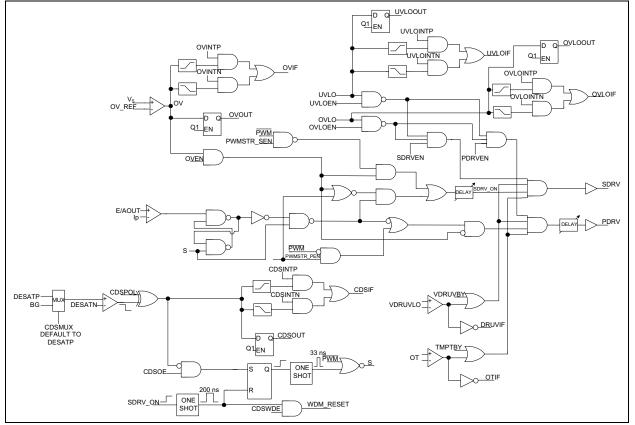

## 3.5 Magnetic Desaturation Detection

An internal comparator module is used to detect power train magnetic desaturation for quasi-resonant applications. The comparator output is used as a signal to synchronize the start of the next switching cycle. This operation differs from the traditional fixed-frequency application. The DESAT comparator output can be enabled and routed into the PWM circuitry or disabled for fixed-frequency applications. During Quasi-Resonant (QR) operation, the DESAT comparator output is enabled and combined with a pair of one-shot timers and a flip-flop to sustain PWM operation. Timer2 (TMR2) must be initialized and set to run at a frequency lower than the minimum QR operating frequency. When the CDSWDE bit is set in the DESATCON register, TMR2 serves as a watchdog.

An example of the order of events for a Flyback SMPS in synchronous QR operation is as follows:

The primary gate drive (PDRV) goes high. The output of the DESAT comparator is high. The primary current increases until Ip reaches the level of the Error Amp and causes PWM comparator output to go low. The PDRV goes low and the secondary gate drive (SDRV) goes high (after programmed dead time). This triggers the first one-shot to send a 200 ns pulse that resets the flip-flop and TMR2 (WDM RESET). The 200 ns one-shot pulse design is implemented to mask out any spurious transitions at the DESAT comparator output caused by switching noise. The SDRV stays high until the secondary winding completely runs out of energy, at which time the output capacitance begins to source current back through the winding and secondary MOSFET. The DESAT comparator detects this and its output goes low. This sets the flip-flop and triggers the second one-shot to send a 33 ns pulse to the control logic, causing the SDRV to go low and the PDRV to go high (after programmed dead time). The cycle then repeats. If, for any reason, the reset one-shot does not fire, the WDM RESET signal stays low and TMR2 is allowed to run until the PWM signal kicks off a new cycle.

The desaturation comparator module is controlled by the DESATCON register.

#### 3.6 Start-Up

To control the output current during start-up, the MCP19114/5 have the capability to monotonically increase system current, at the user's discretion. This is accomplished through the control of the reference voltage DAC ( $V_{REF}$ ). The entire start-up profile is under user control via software.

## 3.7 Driver Control Circuitry

The internal driver control circuitry of the MCP19114/5 is comprised of an error amplifier (EA), a high-speed comparator and a latch similar to the MCP1631.

The error amplifier generates the control voltage used by the high-speed PWM comparator. There is an internally generated reference voltage, V<sub>REF</sub>. The difference or error between this internal reference voltage and the actual feedback voltage is the control voltage. Some applications will implement parked times where the gate drives are not active. For example, when changing between LED strings and after voltage repositioning, the user can disable the gate drives and park the error amplifier output low. During the time when the EA is parked, its output will be clamped low (1 \* BG) such that it is in a known state when reactivated. Before the output switches are re-enabled, it may be necessary to re-enable the EA some time prior to enabling the output drivers. This prior-EA enable time will allow the EA to slew towards the intended target and prevent the secondary switch from turning on for an extensive period of time, unintentionally discharging the output capacitance and pullina the output voltage down. External compensation is used to stabilize the control system.

Since the MCP19114/5 are peak current mode controlled, the comparator compares the primary peak current waveform (I<sub>P</sub>) that is based upon the current flowing in the primary side with the error amplifier control output voltage. This error amplifier control output voltage also has user-programmable slope compensation subtracted from it. In fixed-frequency applications, the slope compensation signal is generated to be greater than 1/2 the down slope of the inductor current waveform and is controlled by the SLPCRCON register. Offset adjust ability is also available to set the peak current limit of the primary switch for overcurrent protection. The range of the slope compensation ramp is specified. When the current sense signal reaches the level of the control voltage minus slope compensation, the on cycle is terminated and the external switch is latched off until the beginning of the next cycle which begins at the next clock cycle.

To improve current regulation at low levels, a pedestal voltage (VZC) set to the BG (1.23V) is implemented. This virtual ground serves as the reference for the error amplifier (A1), slope compensation, current sense amplifier (A2) and the  $I_P$  offset adjustment.

An S-R latch (Set-Rest-Flip-Flop) is used to prevent the PWM circuitry from turning the external switch on until the beginning of the next clock cycle.

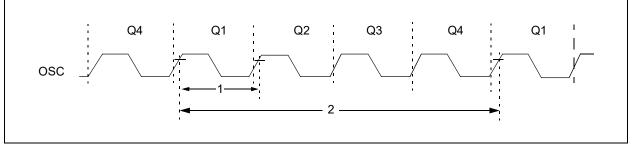

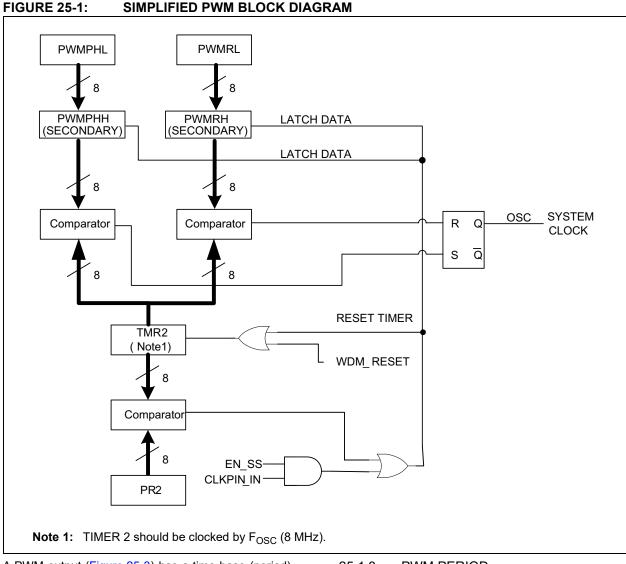

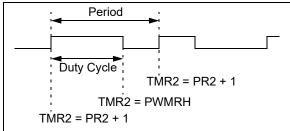

#### 3.8 Fixed PWM Frequency

The switching frequency of the MCP19114/5 while not controlled by the DESAT comparator output is generated by using a single edge of the 8 MHz internal clock. The user sets the MCP19114/5 switching frequency by configuring the PR2 register. The maximum allowable PDRV duty cycle is adjustable and is controlled by the PWMRL register. The programmable range of the switching frequency will be 31.25 kHz to 2 MHz. The available switching frequency below 2 MHz is defined as  $F_{SW} = 8$  MHz/N, where N is a whole number between  $4 \le N \le 256$ . Refer to Section 25.0 "Enhanced PWM Module" for details.

# 3.9 V<sub>REF</sub>

This reference is used to generate the voltage connected to the noninverting input of the error amplifier. The entire analog control loop is raised to a virtual ground pedestal equal to the Band Gap voltage (1.23V).

# 3.10 OV REF

This reference is used to set the output overvoltage set point. It is compared to the  $V_S$  input pin, which is typically proportional to the output voltage based on a resistor divider. OV protection, when enabled, can be set to a value for the protection of system circuitry or it can be used to "ripple" regulate the converter output voltage for repositioning purposes. For details, refer to Register 6-4.

#### 3.11 Independent Gate Drive with Programmable Delay

Two independent low-side gate drives are integrated for synchronous applications. Programmable delay has been implemented to improve efficiency and prevent shoot-through currents. Each gate drive has an independent enable input controlled by the PE1 register and programmable dead time controlled by the DEADCON register.

#### 3.12 Temperature Management

#### 3.12.1 THERMAL SHUTDOWN

To protect the MCP19114/5 from overtemperature conditions, a 150°C junction temperature thermal shutdown has been implemented. When the junction temperature reaches this limit, the device disables the output drivers. In Shutdown mode, both PDRV and SDRV outputs are disabled and the overtemperature flag (OTIF) is set in the PIR2 register. When the junction temperature is reduced by 20°C to 130°C, the MCP19114/5 can resume normal output drive switching.

#### 3.12.2 TEMPERATURE REPORTING

The MCP19114/5 have a second on-chip temperature monitoring circuit that can be read by the ADC through the analog test MUX. Refer to **Section 20.0 "Internal Temperature Indicator Module"** for details on this internal temperature monitoring circuit.

# 4.0 ELECTRICAL CHARACTERISTICS

# 4.1 ABSOLUTE MAXIMUM RATINGS †

| V <sub>IN</sub> - V <sub>GND</sub> (operating)<br>V <sub>IN</sub> (transient < 500 ms) | -0.3V to +44V                                          |

|----------------------------------------------------------------------------------------|--------------------------------------------------------|

| PDRV                                                                                   | (GND - 0.3V) to (V <sub>DR</sub> + 0.3V)               |

| SDRV                                                                                   | (GND - 0.3V) to (V <sub>DR</sub> + 0.3V)               |

| V <sub>DD</sub> Internally Generated                                                   | +6.5V                                                  |

| V <sub>DR</sub> Externally Generated                                                   |                                                        |

| Voltage on MCLR with respect to GND                                                    |                                                        |

| Maximum voltage: any other pin                                                         | +(V <sub>GND</sub> - 0.3V) to (V <sub>DD</sub> + 0.3V) |

| Maximum output current sunk by any single I/O pin                                      |                                                        |

| Maximum output current sourced by any single I/O pin                                   | 25 mA                                                  |

| Maximum current sunk by all GPIO                                                       | 90 mA                                                  |

| Maximum current sourced by all GPIO                                                    | 35 mA                                                  |

| Storage Temperature                                                                    | 65°C to +150°C                                         |

| Maximum Junction Temperature                                                           | +150°C                                                 |

| Operating Junction Temperature                                                         | 40°C to +125°C                                         |

| ESD protection on all pins (HBM)                                                       | 2.0 kV                                                 |

| CDM protection on corner pins                                                          | ±750V                                                  |

| CDM protection on other pins                                                           | ±500V                                                  |

**†** Notice: Stresses above those listed under "Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at those or any other conditions above those indicated in the operational listings of this specification is not implied. Exposure to maximum rating conditions for extended periods may affect device reliability.

| 4.2 | <b>Electrical Characteristics</b> |  |

|-----|-----------------------------------|--|

|     |                                   |  |

|             | ons: Unless otherw<br>e of -40°C to +125° |     | = 12V, F <sub>SW</sub> | <sub>/</sub> = 150 kHz | z, T <sub>A</sub> = +2 | 25°C. <b>Boldface</b> specifications |

|-------------|-------------------------------------------|-----|------------------------|------------------------|------------------------|--------------------------------------|

| Deveneeteve | <b>C</b> 1/100                            | Min | True                   | Max                    | Unite                  | Canditiona                           |

| Parameters                                         | Sym.                                                                | Min.  | Тур.  | Max.  | Units | Conditions                                                   |

|----------------------------------------------------|---------------------------------------------------------------------|-------|-------|-------|-------|--------------------------------------------------------------|

| Input                                              |                                                                     |       |       |       |       |                                                              |

| Input Voltage                                      | V <sub>IN</sub>                                                     | 4.5   | _     | 42    | V     |                                                              |

| Input Quiescent                                    | Ι <sub>Q</sub>                                                      | —     | 5     | 6.5   | mA    | V <sub>IN</sub> = 12V, Not switching                         |

| Current                                            |                                                                     | _     | 5     | 6.75  |       | V <sub>IN</sub> = 20V, Not switching                         |

| Shutdown Current                                   | I <sub>SHDN</sub>                                                   | —     | 30    | 150   | μA    | V <sub>IN</sub> = 12V<br>(Note 1)                            |

| Linear Regulator V <sub>DD</sub>                   | )                                                                   |       |       |       |       |                                                              |

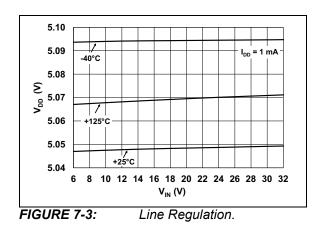

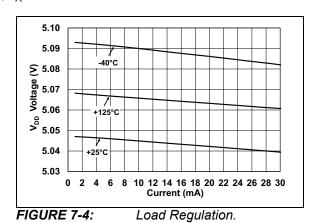

| Internal Circuitry Bias<br>Voltage                 | V <sub>DD</sub>                                                     | 4.75  | 5.0   | 5.5   | V     | V <sub>IN</sub> = 6.0V to 42V                                |

| Maximum External<br>V <sub>DD</sub> Output Current | I <sub>DD_OUT</sub>                                                 | 35    | _     | -     | mA    | V <sub>IN</sub> = 6.0V to 42V<br>(Note 4)                    |

| Line Regulation                                    | ΔV <sub>DD-OUT</sub> /<br>(V <sub>DD-OUT</sub> * ΔV <sub>IN</sub> ) | -0.1  | 0.002 | 0.1   | %/V   | (V <sub>DD</sub> + 1.0V) ≤ V <sub>IN</sub> ≤ 20V<br>(Note 4) |

| Load Regulation                                    | ΔV <sub>DD-OUT</sub> /<br>V <sub>DD-OUT</sub>                       | -0.65 | 0.1   | +0.65 | %     | I <sub>DD_OUT</sub> = 1 mA to 20 mA<br>(Note 4)              |

Note 1: Refer to Section 15.0 "Power-Down Mode (Sleep)".

- 2: These parameters are characterized, but not production tested.

- 3: Ensured by design, not production tested.

- 4: V<sub>DD</sub> is the voltage present at the V<sub>DD</sub> pin.

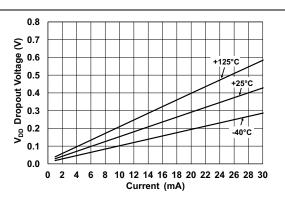

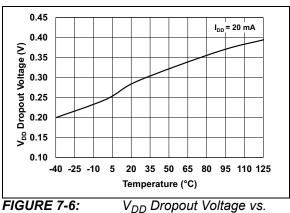

Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between V<sub>IN</sub> and V<sub>DD</sub>.

| apply over the T <sub>A</sub> range  | e of -40°C to +125                | <u>с.</u> | •    |      | <b>T</b> |                                                                                                                                                                        |

|--------------------------------------|-----------------------------------|-----------|------|------|----------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Parameters                           | Sym.                              | Min.      | Тур. | Max. | Units    | Conditions                                                                                                                                                             |

| Output Short-Circuit<br>Current      | I <sub>DD_SC</sub>                | _         | 50   | -    | mA       | V <sub>IN</sub> = (V <sub>DD</sub> + 1.0V)<br>(Note 4)                                                                                                                 |

| Dropout Voltage                      | V <sub>IN</sub> - V <sub>DD</sub> | —         | 0.3  | 0.5  | V        | I <sub>DD_OUT</sub> = 20 mA,<br>(Notes 4 and 5)                                                                                                                        |

| Power Supply<br>Rejection Ratio      | PSRR <sub>LDO</sub>               |           | 60   | _    | dB       | $\label{eq:states} \begin{array}{l} f \leq 1000 \text{ Hz}, \\ I_{DD\_OUT} = 25 \text{ mA} \\ C_{\text{IN}} = 0 \ \mu\text{F}, \ C_{DD} = 1 \ \mu\text{F} \end{array}$ |

| Linear Regulator AV <sub>D</sub>     | D                                 |           |      |      |          |                                                                                                                                                                        |

| Internal Analog<br>Supply Voltage    | AV <sub>DD</sub>                  |           | 4.0  | _    | V        |                                                                                                                                                                        |

| Band Gap Voltage                     | BG                                | —         | 1.23 | —    | V        | Trimmed at 1.0% tolerance                                                                                                                                              |

| Band Gap<br>Tolerance                | BG <sub>TOL</sub>                 | -2.5      | _    | +2.5 | %        |                                                                                                                                                                        |

| Input UVLO Voltage                   |                                   |           |      |      |          |                                                                                                                                                                        |

| UVLO Range                           | UVLO <sub>ON</sub>                | 4.0       | —    | 20   | V        | V <sub>IN</sub> Falling                                                                                                                                                |

| UVLO <sub>ON</sub> Trip<br>Tolerance | UVLO <sub>TOL</sub>               | -14       | _    | 14   | %        | V <sub>IN</sub> Falling<br>UVLO trip set to 9V<br>VINUVLO = 0x21h                                                                                                      |

| UVLO Hysteresis                      | UVLO <sub>HYS</sub>               | 1         | 4    | 8    | %        | Hysteresis is based upon<br>the UVLO <sub>ON</sub> setting<br>UVLO trip set to 9V<br>VINUVLO = 0x21h                                                                   |

| Resolution                           | nbits                             |           | 6    | _    | Bits     | Logarithmic Steps                                                                                                                                                      |

| UVLO Comparator                      |                                   |           |      |      |          |                                                                                                                                                                        |

| Input-to-Output Delay                | TD                                |           | 5    | _    | μs       | 100 ns rise time to 1V<br>overdrive on V <sub>IN</sub><br>V <sub>IN</sub> > UVLO to flag set                                                                           |

| Input OVLO Voltage                   |                                   |           | -    |      |          |                                                                                                                                                                        |

| OVLO Range                           | OVLO <sub>ON</sub>                | 8.8       |      | 44   | V        | V <sub>IN</sub> Rising                                                                                                                                                 |

| OVLO <sub>ON</sub> Trip<br>Tolerance | OVLO <sub>TOL</sub>               | -14       |      | 14   | %        | V <sub>IN</sub> Rising<br>OVLO trip set to 18V<br>VINOVLO = 0x1Fh                                                                                                      |

| OVLO Hysteresis                      | OVLO <sub>HYS</sub>               | 1         | 5    | 8    | %        | Hysteresis is based upon<br>the<br>OVLO <sub>ON</sub> setting<br>OVLO trip set to 18V<br>VINOVLO = 0x1Fh                                                               |

| Resolution                           | nbits                             |           | 6    | _    | Bits     | Logarithmic Steps                                                                                                                                                      |

Note 1: Refer to Section 15.0 "Power-Down Mode (Sleep)".

**2:** These parameters are characterized, but not production tested.

- **3:** Ensured by design, not production tested.

- **4**:  $V_{DD}$  is the voltage present at the  $V_{DD}$  pin.

**5:** Dropout voltage is defined as the input-to-output voltage differential at which the output voltage drops 2% below its nominal value measured at a 1V differential between V<sub>IN</sub> and V<sub>DD</sub>.

| Parameters                         | Sym.                   | Min. | Тур. | Max.   | Units | Conditions                                                                                       |

|------------------------------------|------------------------|------|------|--------|-------|--------------------------------------------------------------------------------------------------|

| OVLO Comparator                    |                        | •    | •    | ·      | •     | •                                                                                                |

| Input-to-Output Delay              | TD                     |      | 5    | _      | μs    | 100 ns rise time to 1V<br>overdrive on V <sub>IN</sub><br>V <sub>IN</sub> > OVLO to flag set     |

| Output OV DAC                      |                        |      |      |        |       |                                                                                                  |

| Resolution                         | nbits                  | _    | 8    | —      | Bits  | Linear DAC                                                                                       |

| Full Scale Range                   | FSR                    | 0    | _    | 2 * BG | V     |                                                                                                  |

| Tolerance                          | OVREF <sub>TOL</sub>   | -10  | —    | +10    | %     | Full Scale, Code = 0xFF                                                                          |

| Output OV Comparato                | or                     |      |      |        |       |                                                                                                  |

| OV Hysteresis                      | OV <sub>HYS</sub>      | —    | 50   | —      | mV    |                                                                                                  |

| Input Bias Current                 | I <sub>BIAS</sub>      |      | ±1   | _      | μA    |                                                                                                  |

| Common-Mode Input<br>Voltage Range | V <sub>CMR</sub>       | 0    | _    | 3.0    | V     | Note 3                                                                                           |

| Input-to-Output Delay              | TD                     | _    | 200  | _      | ns    | Note 3<br>100 ns rise time to 1V<br>overdrive on $V_S$<br>$V_S > OV$ to flag set                 |

| Voltage Reference DA               | C (V <sub>REF</sub> )  |      |      |        |       |                                                                                                  |

| Resolution                         | nbits                  | _    | 8    |        | V/V   | Linear DAC                                                                                       |

| Full-Scale Range                   | FSR                    | BG   | _    | 2 * BG | V     | Pedestal set to BG                                                                               |

| Voltage Reference DA               | C (V <sub>REF2</sub> ) |      |      |        |       |                                                                                                  |

| Resolution                         | nbits                  |      | 8    | _      | Bits  | Linear DAC                                                                                       |

| Full-Scale Range                   | FSR                    | 0    | _    | BG     | V     |                                                                                                  |

| Sink Current                       | I <sub>SINK</sub>      | -3   | _    | —      | mA    | $V_{REF2} = 0V,$<br>R <sub>L</sub> = 300 $\Omega$ to BG                                          |

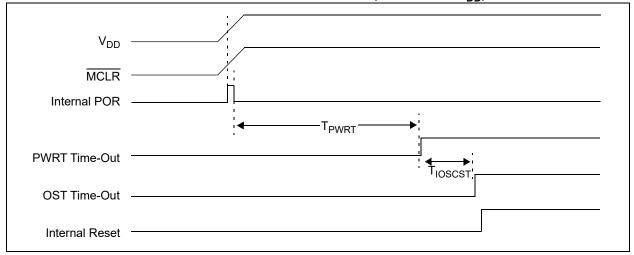

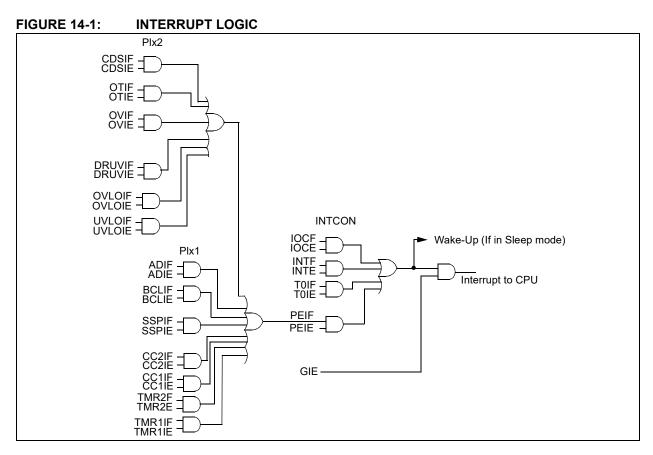

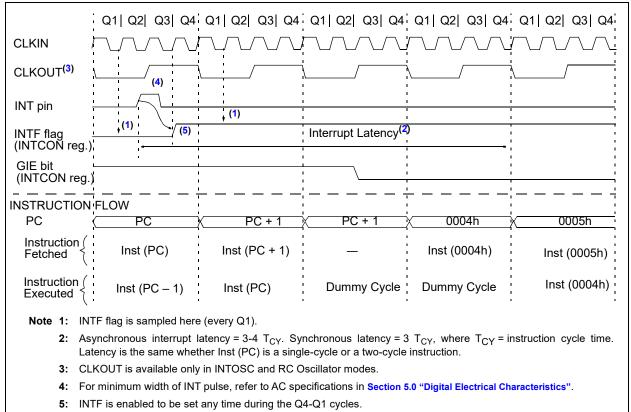

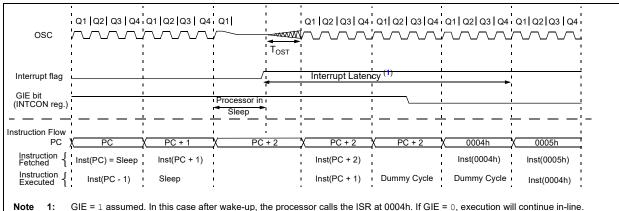

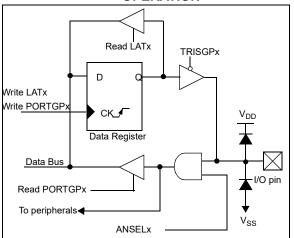

| Source Current                     | ISOURCE                | 3    | _    | —      | mA    | $V_{REF2} = BG,$<br>R <sub>L</sub> = 300 $\Omega$ to GND                                         |