### Product Change Notification / SYST-04RUVM685

### Date:

11-Dec-2020

### **Product Category:**

Interface- Controller Area Network (CAN)

### **PCN Type:**

**Document Change**

### **Notification Subject:**

Data Sheet - MCP2518FD Data Sheet

### **Affected CPNs:**

SYST-04RUVM685\_Affected\_CPN\_12112020.pdf SYST-04RUVM685\_Affected\_CPN\_12112020.csv

### **Notification Text:**

SYST-04RUVM685

Microchip has released a new Product Documents for the MCP2518FD Data Sheet of devices. If you are using one of these devices please read the document located at MCP2518FD Data Sheet.

**Notification Status: Final**

### **Description of Change:**

- 1) Added AEC-Q100 qualification to Special Features section.

- 2) Updated Table 3-1.

- 3) Updated Register 3-2.

- 4) Updated Register 3-4.

- 5) Updated Register 3-5.

- 6) Updated Register 3-7.

- 7) Updated Register 3-23.

- 8) Updated Section 3.3.1, RAM ECC.

- 9) Updated Section 4.1, SFR Access.

- 10) Updated Section 4.1.3, SFR WRITE WRITE.

- 11) Updated Table 7-6.

Impacts to Data Sheet: None

Reason for Change: To Improve Manufacturability

**Change Implementation Status:** Complete

**Date Document Changes Effective:** 11 Dec 2020

**NOTE:** Please be advised that this is a change to the document only the product has not been changed.

Markings to Distinguish Revised from Unrevised Devices: N/A

### **Attachments:**

MCP2518FD Data Sheet

Please contact your local Microchip sales office with questions or concerns regarding this notification.

### **Terms and Conditions:**

If you wish to <u>receive Microchip PCNs via email</u> please register for our PCN email service at our <u>PCN</u> home page select register then fill in the required fields. You will find instructions about registering for Microchips PCN email service in the <u>PCN FAQ</u> section.

If you wish to <u>change your PCN profile, including opt out</u>, please go to the <u>PCN home page</u> select login and sign into your myMicrochip account. Select a profile option from the left navigation bar and make the applicable selections.

### SYST-04RUVM685 - Data Sheet - MCP2518FD Data Sheet

Affected Catalog Part Numbers (CPN)

MCP2518FDT-E/QBB

MCP2518FDT-E/QBBV02

MCP2518FDT-E/QBBVAO

MCP2518FDT-E/SL

MCP2518FDT-E/SLVAO

MCP2518FDT-H/QBB

MCP2518FDT-H/QBBV01

MCP2518FDT-H/QBBVAO

MCP2518FDT-H/SL

MCP2518FDT-H/SLVAO

Date: Thursday, December 10, 2020

### **External CAN FD Controller with SPI Interface**

#### **Features**

#### **General**

- External CAN FD Controller with Serial Peripheral Interface (SPI)

- · Arbitration Bit Rate up to 1 Mbps

- · Data Bit Rate up to 8 Mbps

- · CAN FD Controller modes

- Mixed CAN 2.0B and CAN FD Mode

- CAN 2.0B Mode

- Conforms to ISO 11898-1:2015

#### Message FIFOs

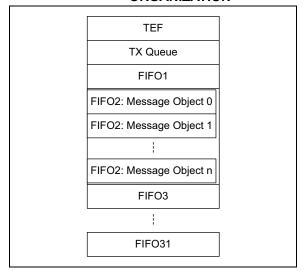

- 31 FIFOs, configurable as Transmit or Receive FIFOs

- One Transmit Queue (TXQ)

- · Transmit Event FIFO (TEF) with 32 bit time stamp

#### **Message Transmission**

- · Message transmission prioritization:

- Based on priority bit field

- Message with lowest ID gets transmitted first using the Transmit Queue (TXQ)

- Programmable automatic retransmission attempts: unlimited, 3 attempts or disabled

#### **Message Reception**

- · 32 Flexible Filter and Mask Objects

- Each object can be configured to filter either:

- Standard ID + first 18 data bits, or

- Extended ID

- · 32-bit Time Stamp

### **Special Features**

- VDD: 2.7 to 5.5V

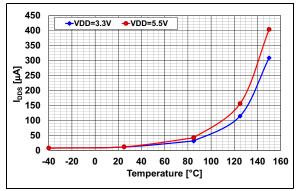

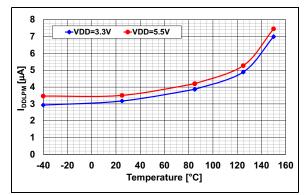

- Active Current: maximum 20 mA at 5.5 V, 40 MHz CAN clock

- Sleep Current: 15 μA, typical

- Low Power Mode current: maximum 10 μA from -40°C to +150°C

- · Message Objects are located in RAM: 2 KB

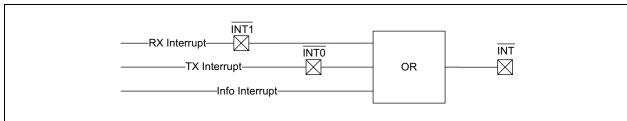

- Up to 3 Configurable Interrupt Pins

- · Bus Health Diagnostics and Error Counters

- Transceiver Standby Control

- Start of frame pin for indicating the beginning of messages on the bus

- AEC-Q100 Qualified

- · Temperature Ranges:

- Extended (E): -40°C to +125°C

- High (H): -40°C to +150°C

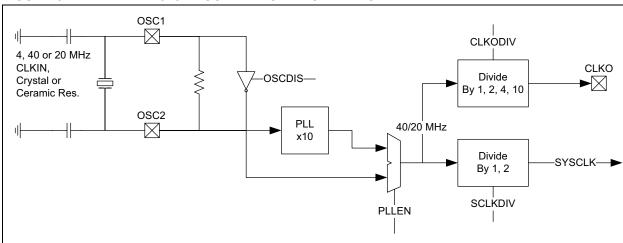

### **Oscillator Options**

- 40, 20 or 4 MHz Crystal or Ceramic Resonator; External Clock Input

- · Clock Output with Prescaler

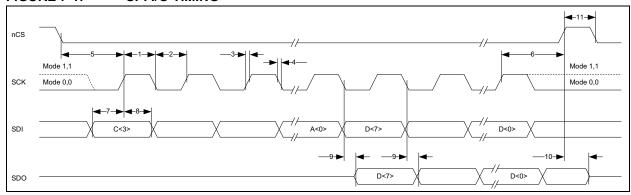

#### **SPI Interface**

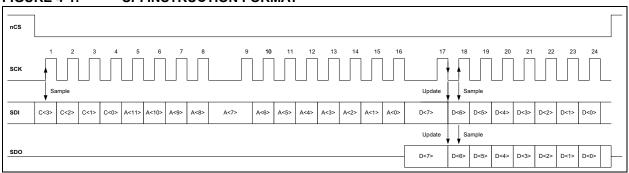

- Up to 20 MHz SPI clock speed

- Supports SPI Modes 0, 0 and 1, 1

- Registers and bit fields are arranged in a way to enable efficient access through SPI

#### **Safety Critical Systems**

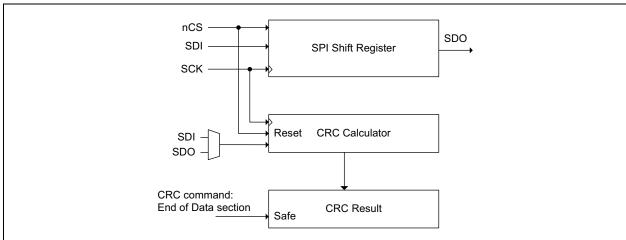

- SPI commands with CRC to detect noise on SPI interface

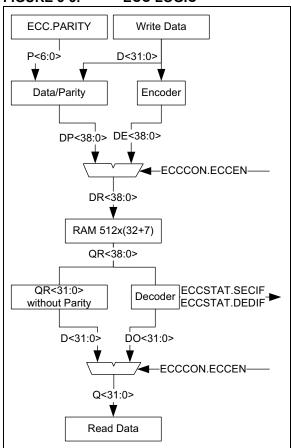

- · Error Correction Code (ECC) protected RAM

### **Additional Features**

- GPIO pins: INT0 and INT1 can be configured as general purpose I/O

- Open drain outputs: TXCAN, INT, INTO, and INT1 pins can be configured as push/pull or open drain outputs

- · ISO 26262 Functional Safety ready

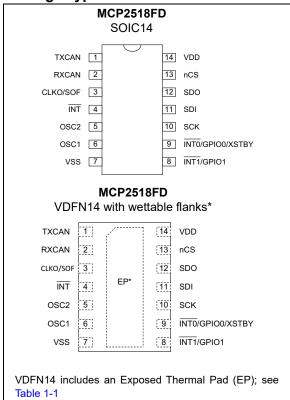

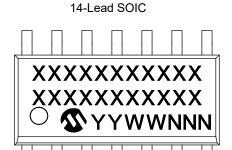

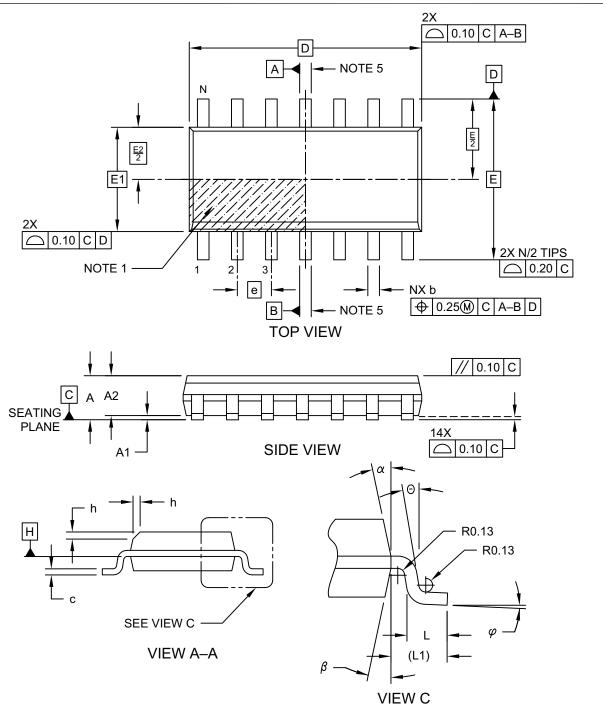

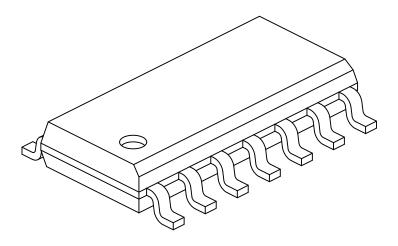

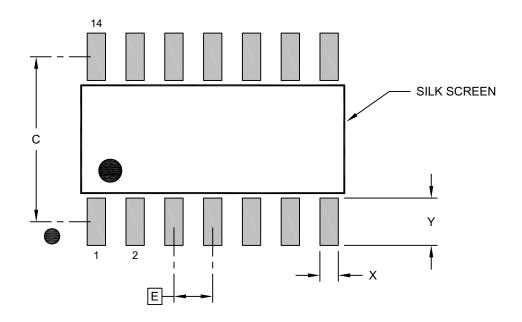

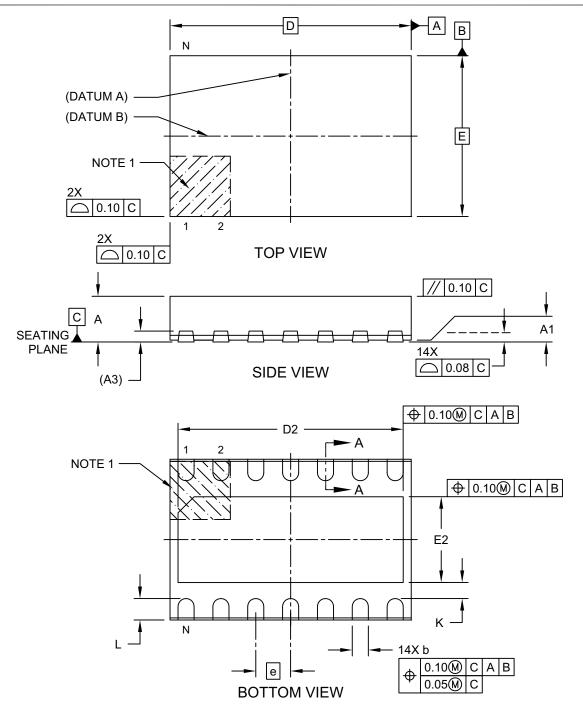

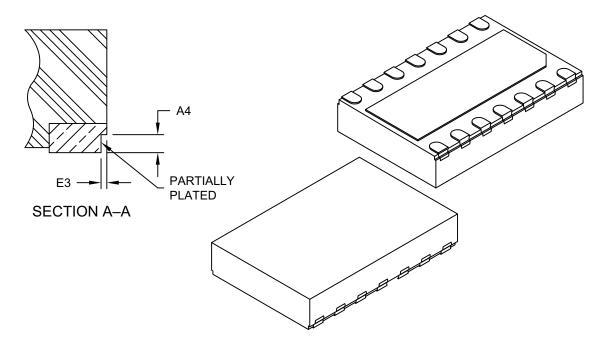

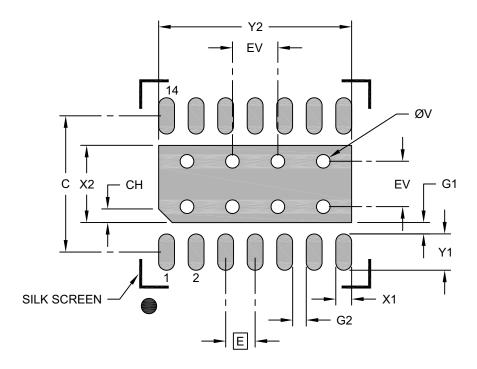

### **Package Types**

### 1.0 DEVICE OVERVIEW

The MCP2518FD device is a cost-effective and small-footprint CAN FD controller that can be easily added to a microcontroller with an available SPI interface. A CAN FD channel can be easily added to a microcontroller that is either lacking a CAN FD peripheral or does not have enough CAN FD channels.

MCP2518FD supports both CAN frames in the Classical format (CAN2.0B) and CAN Flexible Data Rate (CAN FD) format, as specified in ISO 11898-1:2015.

The MCP2518FD device was improved as follows:

- Added Low Power Mode (LPM), in order to reduce leakage current to 10  $\mu A$  over the full temperature range.

- Extended SEQ field in Transmit Message Object and Transmit Event FIFO Object from 7 to 23 bits.

- Added DEVID register to distinguish between future members of the device family.

- Switched to saw cut DFN package with wettable flanks

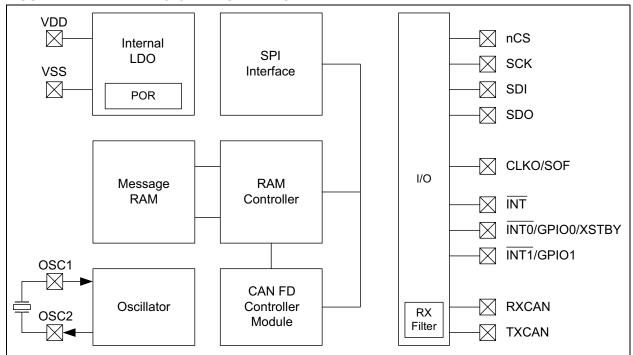

### 1.1 Block Diagram

Figure 1.1 shows the block diagram of the MCP2518FD device. MCP2518FD contains the following main blocks:

- The CAN FD Controller module implements the CAN FD protocol, and contains the FIFOs and Filters.

- The SPI interface is used to control the device by accessing Special Function Registers (SFR) and RAM.

- The RAM controller arbitrates the RAM accesses between the SPI and CAN FD Controller module.

- The Message RAM is used to store the data of the Message Objects.

- The oscillator generates the CAN clock.

- · The Internal LDO and POR circuit.

- The I/O control.

Note 1: This data sheet summarizes the features of the MCP2518FD device. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "MCP25xxFD Family Reference Manual".

FIGURE 1-1: MCP2518FD BLOCK DIAGRAM

### 1.2 Pinout Description

Table 1-1 describes the functions of the pins.

TABLE 1-1: MCP2518FD STANDARD PINOUT VERSION

| Pin Name             | SOIC | VDFN | Pin Type | Description                                                          |

|----------------------|------|------|----------|----------------------------------------------------------------------|

| TXCAN                | 1    | 1    | 0        | Transmit output to CAN FD transceiver                                |

| RXCAN                | 2    | 2    | I        | Receive input from CAN FD transceiver                                |

| CLKO/SOF             | 3    | 3    | 0        | Clock output/Start of Frame output                                   |

| ĪNT                  | 4    | 4    | 0        | Interrupt output (active low)                                        |

| OSC2                 | 5    | 5    | 0        | External oscillator output                                           |

| OSC1                 | 6    | 6    | I        | External oscillator input                                            |

| Vss                  | 7    | 7    | Р        | Ground                                                               |

| INT1/GPIO1           | 8    | 8    | I/O      | RX Interrupt output (active low)/GPIO                                |

| INT0/GPIO0/<br>XSTBY | 9    | 9    | I/O      | TX Interrupt output (active low)/GPIO/<br>Transceiver Standby output |

| SCK                  | 10   | 10   | I        | SPI clock input                                                      |

| SDI                  | 11   | 11   | I        | SPI data input                                                       |

| SDO                  | 12   | 12   | 0        | SPI data output                                                      |

| nCS                  | 13   | 13   | 1        | SPI chip select input                                                |

| VDD                  | 14   | 14   | Р        | Positive Supply                                                      |

| EP                   | -    | 15   | Р        | Exposed Pad; connect to Vss                                          |

**Legend:** P = Power, I = Input, O = Output

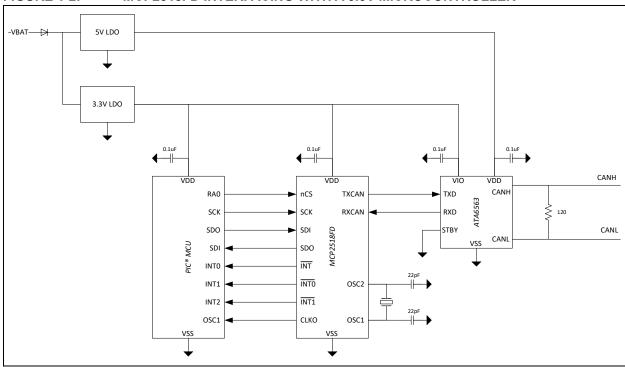

### 1.3 Typical Application

Figure 1-2 shows an example of a typical application of the MCP2518FD device. In this example, the microcontroller operates at 3.3V.

The MCP2518FD device interfaces directly with microcontrollers operating at 2.7V to 5.5V. In addition, the MCP2518FD device connects directly to high-speed CAN FD transceivers. There are no external level shifters required when connecting VDD of the MCP2518FD and the microcontroller to VIO of the transceiver.

The VDD of the CAN FD transceiver is connected to 5V.

The SPI interface is used to configure and control the CAN FD controller.

The MCP2518FD device signals interrupts to the microcontroller by using INT, INT0 and INT1. Interrupts need to be cleared by the microcontroller through SPI.

The CLKO pin provides the clock to the microcontroller.

FIGURE 1-2: MCP2518FD INTERFACING WITH A 3.3V MICROCONTROLLER

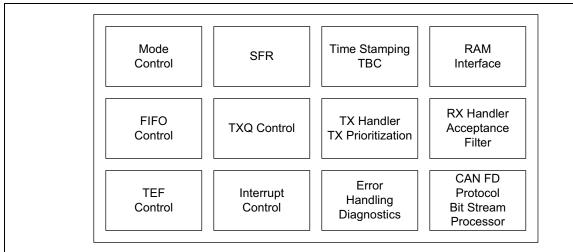

## 2.0 CAN FD CONTROLLER MODULE

Figure 2-1 shows the main blocks of the CAN FD Controller module:

- The CAN FD Controller module has multiple modes:

- Configuration

- Normal CAN FD

- Normal CAN 2.0

- Sleep (normal Sleep mode and Low Power Mode)

- Listen Only

- Restricted Operation

- Internal and External Loop back modes

- The CAN FD Bit Stream Processor (BSP) implements the Medium Access Control of the CAN FD protocol described in ISO 11898-1:2015. It serializes and de-serializes the bit stream, encodes and decodes the CAN FD frames, manages the medium access, acknowledges frames and detects and signals errors.

- The TX Handler prioritizes the messages that are requested for transmission by the Transmit FIFOs. It uses the RAM Interface to fetch the transmit data from RAM and provides it to the BSP for transmission.

- The BSP provides received messages to the RX Handler. The RX Handler uses the Acceptance Filter to filter out messages that shall be stored into Receive FIFOs. It uses the RAM Interface to store received data into RAM.

- Each FIFO can be configured either as a Transmit or Receive FIFO. The FIFO Control keeps track of the FIFO Head and Tail, and calculates the User Address. For a TX FIFO, the User Address points to the address in RAM where the data for the next transmit message shall be stored. For a RX FIFO, the User Address points to the address in RAM where the data of the next receive message shall be read. The User notifies the FIFO that a message was written to or read from RAM by incrementing the Head/Tail of the FIFO.

- The Transmit Queue (TXQ) is a special transmit FIFO that transmits the messages based on the ID of the messages stored in the queue.

- The Transmit Event FIFO (TEF) stores the message IDs of the transmitted messages.

- A free-running Time Base Counter is used to time stamp received messages. Messages in the TEF can also be time stamped.

- The CAN FD Controller module generates interrupts when new messages are received or when messages were transmitted successfully.

- The SFR are used to control and to read the status of the CAN FD Controller module.

Note 1: This data sheet summarizes the features of the CAN FD Controller module. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "MCP25xxFD Family Reference Manual".

### FIGURE 2-1: CAN FD CONTROLLER MODULE BLOCK DIAGRAM

### 3.0 MEMORY ORGANIZATION

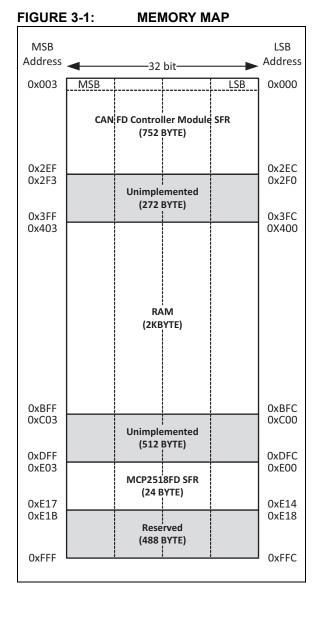

Figure 3-1 illustrates the main sections of the memory and its address ranges:

- MCP2518FD Special Function Registers

- · CAN FD Controller module SFR

- Message Memory (RAM)

The SFR are 32-bit wide. The LSB is located at the lower address, for example, the LSB of C1CON is located at address 0x000, while its MSB is located at address 0x003.

Table 3-1 lists the MCP2518FD specific registers. The first column contains the address of the SFR.

Table 3-2 lists the registers of the CAN FD Controller module. The first column contains the address of the SFR.

TABLE 3-1: MCP2518FD REGISTER SUMMARY

| Address            | Name    | •     | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |

|--------------------|---------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|

| E03                | OSC     | 31:24 | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

| E02                |         | 23:16 | 1                 | ı                 | ı                 | ı                 | _                 | ı                 | ı                | _                |  |

| E01                |         | 15:8  | 1                 | -                 | -                 | SCLKRDY           | _                 | OSCRDY            |                  | PLLRDY           |  |

| E00 <sup>(1)</sup> |         | 7:0   | _                 | CLKOE             | DIV[1:0]          | SCLKDIV           | LPMEN             | OSCDIS            | _                | PLLEN            |  |

|                    | IOCON   | 31:24 |                   | INTOD             | SOF               | TXCANOD           | _                 |                   | PM1              | PM0              |  |

|                    |         | 23:16 | -                 | _                 | _                 | _                 | _                 | -                 | GPIO1            | GPIO0            |  |

|                    |         | 15:8  | _                 | _                 | _                 | _                 | _                 | _                 | LAT1             | LAT0             |  |

| E04                |         | 7:0   | 1                 | XSTBYEN           | 1                 | 1                 | _                 | 1                 | TRIS1            | TRIS0            |  |

|                    | CRC     | 31:24 |                   |                   |                   | _                 | _                 |                   | FERRIE           | CRCERRIE         |  |

|                    |         | 23:16 | _                 | _                 | _                 | _                 | _                 | _                 | FERRIF           | CRCERRIF         |  |

|                    |         | 15:8  |                   | CRC[15:8]         |                   |                   |                   |                   |                  |                  |  |

| E08                |         | 7:0   |                   |                   |                   | CRC               | [7:0]             |                   |                  |                  |  |

|                    | ECCCON  | 31:24 | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |  |

|                    |         | 23:16 | I                 | I                 | I                 | 1                 | _                 | 1                 | 1                | _                |  |

|                    |         | 15:8  | 1                 |                   |                   |                   | PARITY[6:0]       |                   |                  |                  |  |

| E0C                |         | 7:0   | _                 | _                 | _                 | _                 | _                 | DEDIE             | SECIE            | ECCEN            |  |

|                    | ECCSTAT | 31:24 | _                 | _                 | _                 | _                 |                   | ERRADI            | DR[11:8]         |                  |  |

|                    |         | 23:16 |                   |                   |                   | ERRAD             | DR[7:0]           |                   |                  |                  |  |

|                    |         | 15:8  | -                 | _                 | _                 | _                 | _                 | 1                 | _                | _                |  |

| E10                |         | 7:0   | 1                 | 1                 | 1                 | 1                 | _                 | DEDIF             | SECIF            | _                |  |

|                    | DEVID   | 31:24 |                   | _                 | _                 | _                 | _                 |                   |                  | _                |  |

|                    |         | 23:16 | _                 | _                 | _                 | _                 | _                 | _                 | _                | _                |  |

|                    |         | 15:8  | _                 | _                 | _                 | _                 | _                 |                   | _                | _                |  |

| E14                |         | 7:0   |                   | ID[3:0] REV[3:0]  |                   |                   |                   |                   |                  |                  |  |

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

<sup>2:</sup> The bit fields in the IOCON register must be written using single data byte SFR WRITE instructions.

TABLE 3-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY

| Addr. | Name          |                 | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-------|---------------|-----------------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 03    | C1CON         | 31:24           |                   | TXBV              | /S[3:0]           |                   | ABAT              |                   | REQOP[2:0]       |                  |  |  |

| 02    |               | 23:16           |                   | OPMOD[2:0]        |                   | TXQEN             | STEF              | SERR2LOM          | ESIGM            | RTXAT            |  |  |

| 01    |               | 15:8            | _                 | _                 | _                 | BRSDIS            | BUSY              | WFT               | [1:0]            | WAKFIL           |  |  |

| 00[1] |               | 7:0             | _                 | PXEDIS            | ISOCRCEN          |                   | •                 | DNCNT[4:0]        |                  |                  |  |  |

|       | C1NBTCFG      | 31:24           |                   |                   |                   | BRF               | P[7:0]            |                   |                  |                  |  |  |

|       |               | 23:16           |                   |                   |                   | TSEC              | G1[7:0]           |                   |                  |                  |  |  |

|       |               | 15:8            |                   |                   |                   |                   | TSEG2[6:0]        |                   |                  |                  |  |  |

| 04    |               | 7:0             | _                 |                   |                   |                   | SJW[6:0]          |                   |                  |                  |  |  |

|       | C1DBTCFG      | 31:24           |                   |                   |                   | BRF               | P[7:0]            |                   |                  |                  |  |  |

|       |               | 23:16           |                   | _                 | _                 |                   |                   | TSEG1[4:0]        |                  |                  |  |  |

|       |               | 15:8            | _                 | _                 | _                 | _                 |                   | TSEG              | 2[3:0]           |                  |  |  |

| 08    |               | 7:0             | _                 | _                 | _                 | I                 |                   | SJW               | [3:0]            |                  |  |  |

|       | C1TDC         | 31:24           | -                 |                   | _                 | -                 | _                 | _                 | EDGFLTEN         | SID11EN          |  |  |

|       |               | 23:16           | _                 | _                 | _                 | _                 | _                 | _                 | TDCMC            | DD[1:0]          |  |  |

|       |               | 15:8            | _                 |                   |                   |                   | TDCO[6:0]         | •                 | •                |                  |  |  |

| 0C    |               | 7:0             | -                 | — — TDCV[5:0]     |                   |                   |                   |                   |                  |                  |  |  |

|       | C1TBC         | 31:24           |                   | TBC[31:24]        |                   |                   |                   |                   |                  |                  |  |  |

|       |               | 23:16           |                   | TBC[23:16]        |                   |                   |                   |                   |                  |                  |  |  |

|       |               | 15:8            |                   | TBC[15:8]         |                   |                   |                   |                   |                  |                  |  |  |

| 10    |               | 7:0             |                   |                   |                   | TBC               | [7:0]             |                   |                  |                  |  |  |

|       | C1TSCON       | 31:24           | _                 |                   | _                 | _                 | _                 | _                 | _                | _                |  |  |

|       |               | 23:16           | _                 | _                 | _                 | _                 | _                 | TSRES             | TSEOF            | TBCEN            |  |  |

|       |               | 15:8            | _                 | _                 | _                 | _                 | _                 | — TBCPRE[9:8]     |                  |                  |  |  |

| 14    |               | 7:0             |                   |                   |                   | TBCPI             | RE[7:0]           |                   | •                |                  |  |  |

|       | C1VEC         | 31:24           | _                 |                   |                   |                   | RXCODE[6:0]       |                   |                  |                  |  |  |

|       |               | 23:16           | _                 |                   |                   |                   | TXCODE[6:0]       |                   |                  |                  |  |  |

|       |               | 15:8            | _                 | _                 | _                 |                   |                   | FILHIT[4:0]       |                  |                  |  |  |

| 18    |               | 7:0             | _                 |                   |                   |                   | ICODE[6:0]        |                   |                  |                  |  |  |

|       | C1INT         | 31:24           | IVMIE             | WAKIE             | CERRIE            | SERRIE            | RXOVIE            | TXATIE            | SPICRCIE         | ECCIE            |  |  |

|       |               | 23:16           | _                 | _                 | _                 | TEFIE             | MODIE             | TBCIE             | RXIE             | TXIE             |  |  |

|       |               | 15:8            | IVMIF             | WAKIF             | CERRIF            | SERRIF            | RXOVIF            | TXATIF            | SPICRCIF         | ECCIF            |  |  |

| 1C    |               | 7:0             | _                 | _                 | _                 | TEFIF             | MODIF             | TBCIF             | RXIF             | TXIF             |  |  |

|       | C1RXIF        | 31:24           |                   |                   |                   | RFIF[             | 31:24]            |                   |                  |                  |  |  |

|       |               | 23:16           |                   |                   |                   | RFIF[             | 23:16]            |                   |                  |                  |  |  |

|       |               | 15:8            |                   |                   |                   | RFIF              | [15:8]            |                   |                  |                  |  |  |

| 20    |               | 7:0             |                   |                   |                   | RFIF[7:1]         |                   |                   |                  | _                |  |  |

|       | C1TXIF        | 31:24           |                   |                   |                   | TFIF[             | 31:24]            |                   |                  |                  |  |  |

|       |               | 23:16           |                   |                   |                   | TFIF[             | 23:16]            |                   |                  |                  |  |  |

|       |               | 15:8            |                   |                   |                   | TFIF              | [15:8]            |                   |                  |                  |  |  |

| 24    |               | 7:0             |                   |                   |                   | TFIF              | [7:0]             |                   |                  |                  |  |  |

|       | C1RXOVIF      | 31:24           |                   |                   |                   | RFOVI             | F[31:24]          |                   |                  |                  |  |  |

|       |               | 23:16           |                   |                   |                   | RFOVII            | F[23:16]          |                   |                  |                  |  |  |

|       |               | 15:8            |                   |                   |                   | RFOV              | IF[15:8]          |                   |                  |                  |  |  |

| 28    |               | 7:0             |                   |                   |                   | RFOVIF[7:1]       |                   |                   |                  | _                |  |  |

|       | C1TXATIF      | 31:24           |                   |                   |                   | TFATIF            | [31:24]           |                   |                  |                  |  |  |

|       |               | 23:16           |                   |                   |                   | TFATIF            | [23:16]           |                   |                  |                  |  |  |

|       |               | 15:8            |                   | _                 | _                 | TFATI             | F[15:8]           | _                 | _                | _                |  |  |

| 2C    |               | 7:0             |                   |                   |                   | TFAT              | IF[7:0]           |                   |                  |                  |  |  |

| N     | (. The Leaves | 7:0 TFATIF[7:0] |                   |                   |                   |                   |                   |                   |                  |                  |  |  |

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

<sup>2:</sup> Reserved register reads 0.

TABLE 3-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

| Addr.      | Name                    |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit 27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |

|------------|-------------------------|-------|-------------------|-------------------|-------------------|-------------------|----------------|-------------------|------------------|------------------|

|            | C1TXREQ                 | 31:24 | ***********       |                   |                   |                   | Q[31:24]       |                   |                  |                  |

|            | OTTAILL                 | 23:16 |                   |                   |                   |                   | Q[23:16]       |                   |                  |                  |

|            |                         | 15:8  |                   |                   |                   |                   | Q[15:8]        |                   |                  |                  |

| 30         |                         | 7:0   |                   |                   |                   |                   | Q[7:0]         |                   |                  |                  |

|            | C1TREC                  | 31:24 | _                 | _                 | _                 | _                 | _              | _                 | _                | _                |

|            |                         | 23:16 | _                 | _                 | TXBO              | TXBP              | RXBP           | TXWARN            | RXWARN           | EWARN            |

|            |                         | 15:8  |                   |                   |                   | TEC               | [7:0]          |                   | <u> </u>         |                  |

| 34         |                         | 7:0   |                   |                   |                   |                   | C[7:0]         |                   |                  |                  |

|            | C1BDIAG0                | 31:24 |                   |                   |                   |                   | CNT[7:0]       |                   |                  |                  |

|            |                         | 23:16 |                   |                   |                   |                   | CNT[7:0]       |                   |                  |                  |

|            |                         | 15:8  |                   |                   |                   | NTERR             | CNT[7:0]       |                   |                  |                  |

| 38         |                         | 7:0   |                   |                   |                   | NRERR             | CNT[7:0]       |                   |                  |                  |

|            | C1BDIAG1                | 31:24 | DLCMM             | ESI               | DCRCERR           |                   | DFORMERR       | _                 | DBIT1ERR         | DBIT0ERR         |

|            |                         | 23:16 | TXBOERR           | _                 | NCRCERR           | NSTUFERR          | NFORMERR       | NACKERR           | NBIT1ERR         | NBIT0ERR         |

|            |                         | 15:8  |                   |                   |                   | EFMSG             | CNT[15:8]      |                   |                  |                  |

| 3C         |                         | 7:0   |                   |                   |                   | EFMSG             | CNT[7:0]       |                   |                  |                  |

|            | C1TEFCON                | 31:24 | _                 | _                 | _                 |                   |                | FSIZE[4:0]        |                  |                  |

|            |                         | 23:16 | _                 |                   | _                 | _                 | _              | _                 | _                | _                |

|            |                         | 15:8  | _                 | _                 | _                 | _                 | _              | FRESET            | _                | UINC             |

| 40         |                         | 7:0   | _                 | _                 | TEFTSEN           | _                 | TEFOVIE        | TEFFIE            | TEFHIE           | TEFNEIE          |

|            | C1TEFSTA                | 31:24 | _                 |                   | _                 | _                 | _              | _                 | _                | _                |

|            |                         | 23:16 | _                 |                   | _                 | _                 | _              | -                 | _                | _                |

|            |                         | 15:8  | _                 |                   | _                 | _                 | _              | _                 | _                | _                |

| 44         |                         | 7:0   | _                 |                   | _                 | _                 | TEFOVIF        | TEFFIF            | TEFHIF           | TEFNEIF          |

|            | C1TEFUA                 | 31:24 |                   |                   |                   | TEFUA             | A[31:24]       |                   |                  |                  |

|            |                         | 23:16 |                   |                   |                   | TEFUA             | \[23:16]       |                   |                  |                  |

|            |                         | 15:8  |                   |                   |                   | TEFU              | A[15:8]        |                   |                  |                  |

| 48         |                         | 7:0   |                   |                   |                   | TEFU              | JA[7:0]        |                   |                  |                  |

|            | Reserved <sup>(2)</sup> | 31:24 |                   |                   |                   | Reserve           | ed[31:24]      |                   |                  |                  |

|            |                         | 23:16 |                   |                   |                   | Reserve           | ed[23:16]      |                   |                  |                  |

|            |                         | 15:8  |                   |                   |                   | Reserv            | ed[15:8]       |                   |                  |                  |

| 4C         |                         | 7:0   |                   |                   |                   | Reserv            | /ed[7:0]       |                   |                  |                  |

|            | C1TXQCON                | 31:24 |                   | PLSIZE[2:0]       |                   |                   |                | FSIZE[4:0]        |                  |                  |

|            |                         | 23:16 | _                 | TXAT              | [1:0]             |                   |                | TXPRI[4:0]        |                  |                  |

|            |                         | 15:8  | _                 | _                 | _                 | _                 | _              | FRESET            | TXREQ            | UINC             |

| 50         |                         | 7:0   | TXEN              | -                 | _                 | TXATIE            | _              | TXQEIE            | _                | TXQNIE           |

|            | C1TXQSTA                | 31:24 | _                 | _                 | _                 | _                 | _              | _                 | _                | _                |

|            |                         | 23:16 | _                 | _                 | _                 | _                 | _              | _                 | _                | _                |

|            |                         | 15:8  | _                 | _                 | _                 |                   |                | TXQCI[4:0]        |                  | ı                |

| 54         |                         | 7:0   | TXABT             | TXLARB            | TXERR             | TXATIF            | _              | TXQEIF            | _                | TXQNIF           |

|            | C1TXQUA                 | 31:24 |                   |                   |                   |                   | A[31:24]       |                   |                  |                  |

|            |                         | 23:16 |                   |                   |                   |                   | A[23:16]       |                   |                  |                  |

|            |                         | 15:8  |                   |                   |                   |                   | A[15:8]        |                   |                  |                  |

| 58<br>Note | 1. The lewer            | 7:0   |                   | hit register re   |                   |                   | JA[7:0]        |                   |                  |                  |

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

<sup>2:</sup> Reserved register reads 0.

TABLE 3-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

| IADL  |             |       |                                                                               | OLLLIN IVI                           | JOULE IX.         |                   |                   | . (00             | · ·              | Т                |  |  |

|-------|-------------|-------|-------------------------------------------------------------------------------|--------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| Addr. | Name        |       | Bit<br>31/23/15/7                                                             | Bit<br>30/22/14/6                    | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|       | C1FIFOCON1  | 31:24 |                                                                               | PLSIZE[2:0]                          |                   |                   |                   | FSIZE[4:0]        |                  |                  |  |  |

|       |             | 23:16 | _                                                                             | TXAT                                 | [1:0]             |                   |                   | TXPRI[4:0]        |                  |                  |  |  |

|       |             | 15:8  | _                                                                             | _                                    | _                 | _                 | _                 | FRESET            | TXREQ            | UINC             |  |  |

| 5C    |             | 7:0   | TXEN                                                                          | RTREN                                | RXTSEN            | TXATIE            | RXOVIE            | TFERFFIE          | TFHRFHIE         | TFNRFNIE         |  |  |

|       | C1FIFOSTA1  | 31:24 | _                                                                             | _                                    | _                 | _                 | _                 | _                 | _                | _                |  |  |

|       |             | 23:16 | _                                                                             | _                                    | _                 | _                 | _                 | _                 | _                | _                |  |  |

|       |             | 15:8  | _                                                                             | _                                    | _                 |                   |                   | FIFOCI[4:0]       |                  |                  |  |  |

| 60    |             | 7:0   | TXABT                                                                         | TXLARB                               | TXERR             | TXATIF            | RXOVIF            | TFERFFIF          | TFHRFHIF         | TFNRFNIF         |  |  |

|       | C1FIFOUA1   | 31:24 |                                                                               |                                      | L                 | FIFOU             | A[31:24]          |                   | <u> </u>         |                  |  |  |

|       |             | 23:16 |                                                                               |                                      |                   |                   | A[23:16]          |                   |                  |                  |  |  |

|       |             | 15:8  |                                                                               |                                      |                   |                   | A[15:8]           |                   |                  |                  |  |  |

| 64    |             | 7:0   |                                                                               |                                      |                   |                   | • •               |                   |                  |                  |  |  |

| 68    | C1FIFOCON2  | 31:0  |                                                                               | FIFOUA[7:0] same as C1FIFOCON1       |                   |                   |                   |                   |                  |                  |  |  |

| 6C    | C1FIFOCON2  | 31:0  |                                                                               | same as C1FIFOSTA1                   |                   |                   |                   |                   |                  |                  |  |  |

| 70    |             | 31:0  |                                                                               |                                      |                   |                   |                   |                   |                  |                  |  |  |

|       | C1FIFOUA2   |       |                                                                               | same as C1FIFOUA1 same as C1FIFOCON1 |                   |                   |                   |                   |                  |                  |  |  |

| 74    | C1FIFOCON3  | 31:0  |                                                                               |                                      |                   |                   |                   |                   |                  |                  |  |  |

| 78    | C1FIFOSTA3  | 31:0  |                                                                               |                                      |                   |                   | 1FIFOSTA1         |                   |                  |                  |  |  |

| 7C    | C1FIFOUA3   | 31:0  |                                                                               |                                      |                   |                   | 1FIFOUA1          |                   |                  |                  |  |  |

| 80    | C1FIFOCON4  | 31:0  |                                                                               |                                      |                   |                   | 1FIFOCON1         |                   |                  |                  |  |  |

| 84    | C1FIFOSTA4  | 31:0  |                                                                               | same as C1FIFOSTA1                   |                   |                   |                   |                   |                  |                  |  |  |

| 88    | C1FIFOUA4   | 31:0  |                                                                               |                                      |                   |                   | 1FIFOUA1          |                   |                  |                  |  |  |

| 8C    | C1FIFOCON5  | 31:0  |                                                                               |                                      |                   |                   | 1FIFOCON1         |                   |                  |                  |  |  |

| 90    | C1FIFOSTA5  | 31:0  |                                                                               |                                      |                   |                   | 1FIFOSTA1         |                   |                  |                  |  |  |

| 94    | C1FIFOUA5   | 31:0  |                                                                               |                                      |                   |                   | 1FIFOUA1          |                   |                  |                  |  |  |

| 98    | C1FIFOCON6  | 31:0  |                                                                               |                                      |                   |                   | 1FIFOCON1         |                   |                  |                  |  |  |

| 9C    | C1FIFOSTA6  | 31:0  |                                                                               |                                      |                   |                   | 1FIFOSTA1         |                   |                  |                  |  |  |

| A0    | C1FIFOUA6   | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| A4    | C1FIFOCON7  | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOCON1         |                   |                  |                  |  |  |

| A8    | C1FIFOSTA7  | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| AC    | C1FIFOUA7   | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| B0    | C1FIFOCON8  | 31:0  |                                                                               |                                      |                   | same as C´        | 1FIFOCON1         |                   |                  |                  |  |  |

| B4    | C1FIFOSTA8  | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| B8    | C1FIFOUA8   | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| BC    | C1FIFOCON9  | 31:0  |                                                                               |                                      |                   | same as C´        | 1FIFOCON1         |                   |                  |                  |  |  |

| C0    | C1FIFOSTA9  | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| C4    | C1FIFOUA9   | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| C8    | C1FIFOCON10 | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOCON1         |                   |                  |                  |  |  |

| CC    | C1FIFOSTA10 | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| D0    | C1FIFOUA10  | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| D4    | C1FIFOCON11 | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOCON1         |                   |                  |                  |  |  |

| D8    | C1FIFOSTA11 | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| DC    | C1FIFOUA11  | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| E0    | C1FIFOCON12 | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOCON1         |                   |                  |                  |  |  |

| E4    | C1FIFOSTA12 | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| E8    | C1FIFOUA12  | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| EC    | C1FIFOCON13 | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOCON1         |                   |                  | _                |  |  |

| F0    | C1FIFOSTA13 | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| F4    | C1FIFOUA13  | 31:0  |                                                                               |                                      |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| F8    | C1FIFOCON14 | 31:0  |                                                                               |                                      |                   |                   | 1FIFOCON1         |                   |                  |                  |  |  |

| FC    | C1FIFOSTA14 | 31:0  |                                                                               |                                      |                   |                   | 1FIFOSTA1         |                   |                  |                  |  |  |

| 100   | C1FIFOUA14  | 31:0  |                                                                               |                                      |                   |                   |                   |                   |                  |                  |  |  |

|       |             |       | same as C1FIFOUA1  te of the 32-bit register resides at the low-order address |                                      |                   |                   |                   |                   |                  |                  |  |  |

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

<sup>2:</sup> Reserved register reads 0.

TABLE 3-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

| Addr. | Name          |      | Bit<br>31/23/15/7 | Bit<br>30/22/14/6                                       | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|-------|---------------|------|-------------------|---------------------------------------------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| 104   | C1FIFOCON15   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 108   | C1FIFOSTA15   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 10C   | C1FIFOUA15    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 110   | C1FIFOCON16   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 114   | C1FIFOSTA16   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 118   | C1FIFOUA16    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 11C   | C1FIFOCON17   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 120   | C1FIFOSTA17   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 124   | C1FIFOUA17    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 128   | C1FIFOCON18   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 12C   | C1FIFOSTA18   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 130   | C1FIFOUA18    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 134   | C1FIFOCON19   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 138   | C1FIFOSTA19   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 13C   | C1FIFOUA19    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 140   | C1FIFOCON20   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 144   | C1FIFOSTA20   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 148   | C1FIFOUA20    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 14C   | C1FIFOCON21   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 150   | C1FIFOSTA21   | 31:0 |                   | same as C1FIFOSTA1                                      |                   |                   |                   |                   |                  |                  |  |  |

| 154   | C1FIFOUA21    | 31:0 |                   | same as C1FIFOUA1                                       |                   |                   |                   |                   |                  |                  |  |  |

| 158   | C1FIFOCON22   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 15C   | C1FIFOSTA22   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 160   | C1FIFOUA22    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 164   | C1FIFOCON23   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 168   | C1FIFOSTA23   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 16C   | C1FIFOUA23    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 170   | C1FIFOCON24   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 174   | C1FIFOSTA24   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 178   | C1FIFOUA24    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 17C   | C1FIFOCON25   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 180   | C1FIFOSTA25   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 184   | C1FIFOUA25    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 188   | C1FIFOCON26   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 18C   | C1FIFOSTA26   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 190   | C1FIFOUA26    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 194   | C1FIFOCON27   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 198   | C1FIFOSTA27   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 19C   | C1FIFOUA27    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 1A0   | C1FIFOCON28   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 1A4   | C1FIFOSTA28   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 1A8   | C1FIFOUA28    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 1AC   | C1FIFOCON29   | 31:0 |                   | same as C1FIFOCON1                                      |                   |                   |                   |                   |                  |                  |  |  |

| 1B0   | C1FIFOSTA29   | 31:0 |                   | same as C1FIFOSTA1                                      |                   |                   |                   |                   |                  |                  |  |  |

| 1B4   | C1FIFOUA29    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 1B8   | C1FIFOCON30   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 1BC   | C1FIFOSTA30   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 1C0   | C1FIFOUA30    | 31:0 |                   |                                                         |                   | same as C         | 1FIFOUA1          |                   |                  |                  |  |  |

| 1C4   | C1FIFOCON31   | 31:0 |                   |                                                         |                   | same as C1        | FIFOCON1          |                   |                  |                  |  |  |

| 1C8   | C1FIFOSTA31   | 31:0 |                   |                                                         |                   | same as C         | 1FIFOSTA1         |                   |                  |                  |  |  |

| 1CC   | C1FIFOUA31    | 31:0 | same as C1FIFOUA1 |                                                         |                   |                   |                   |                   |                  |                  |  |  |

| NI-4- | 4. The levier |      | 4                 | of the 32-bit register resides at the low-order address |                   |                   |                   |                   |                  |                  |  |  |

**Note 1:** The lower order byte of the 32-bit register resides at the low-order address.

2: Reserved register reads 0.

TABLE 3-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

| Made                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | IADL  |               | ,     |         | OLLLIN IVI | ODULL IX.         |      |                   | . (50             | ,          |  |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------|---------------|-------|---------|------------|-------------------|------|-------------------|-------------------|------------|--|--|

| 100                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Addr. | Name          |       |         |            | Bit<br>29/21/13/5 |      | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 |            |  |  |

| 15.8   FLTENT                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |       | C1FLTCON0     | 31:24 | FLTEN3  | _          | _                 |      |                   | F3BP[4:0]         |            |  |  |